# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **Hex Half-Bridge Driver**

The NCV7728 is a Hex Half-Bridge Driver with protection features designed specifically for automotive and industrial motion control applications. The NCV7728 has independent controls and diagnostics. The device can be operated in forward, reverse, brake, and high impedance states. The drivers are controlled via a 16 bit SPI interface and are daisy chain compatible.

### Features

- Low Quiescent Current Sleep Mode

- High-Side and Low-Side Drivers Connected in a Half-Bridge Configuration

- Integrated Freewheeling Protection (LS and HS)

- 0.55 A Peak Current

- $R_{DS(on)} = 1 \Omega (typ)$

- 5 MHz SPI Control

- Compliance with 5 V and 3. 3 V Systems

- Undervoltage and Overvoltage Lockout

- Discriminated Fault Reporting

- Overcurrent Protection

- Overtemperature Protection

- Under Load Detection (HS and LS)

- Daisy Chain Compatible with Multiple of 8 bit Devices

- 16-Bit Frame Detection

- These are Pb–Free Devices

#### **Typical Applications**

- Automotive

- Industrial

- DC Motor Management for HVAC Application

## **ON Semiconductor®**

http://onsemi.com

NCV7728 = Specific Device Code

- = Assembly Location

- WL = Wafer Lot YΥ

А

- = Year

- WW = Work Week

- G = Pb-Free Package

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 26 of this data sheet.

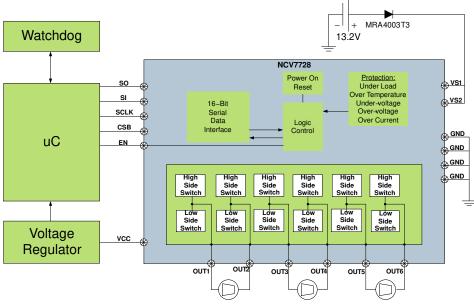

Shown below is a typical application for the NCV7728 configuration.

Figure 1. Typical Application

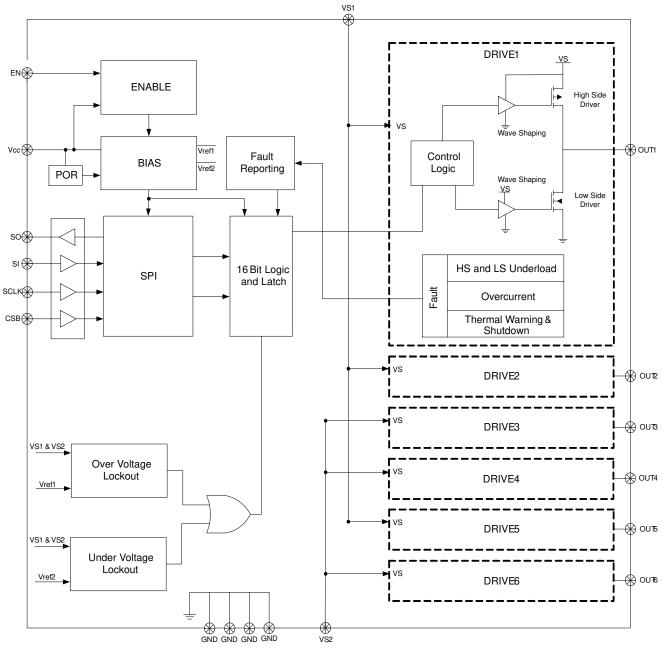

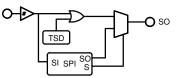

Figure 2. Block Diagram

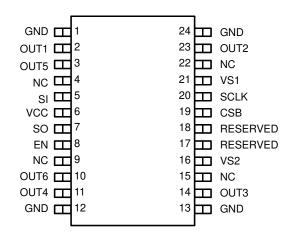

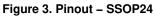

PACKAGE DESCRIPTION The pin-out for the Hex Half-Bridge in SSOP24 package is shown in the table below.

| Pin #<br>SSOP24 | Symbol   | Description                                                                                                                                   |

|-----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 1               | GND      | Ground. Shorted to pin 24 internally.                                                                                                         |

| 2               | OUT1     | Half Bridge Output 1                                                                                                                          |

| 3               | OUT5     | Half Bridge Output 5                                                                                                                          |

| 4               | NC       | No Connection. This pin should be isolated from any traces or via on the PCB board.                                                           |

| 5               | SI       | Serial Input. 16 bit serial communications input. 3.3 V/5 V (TTL) Compatible. Internally pulled down.                                         |

| 6               | VCC      | Power supply input for Logic.                                                                                                                 |

| 7               | SO       | Serial Output. 16 bit serial communications output. 3.3 V/5 V Complaint                                                                       |

| 8               | EN       | Enable. Input high wakes the IC up from a sleep mode. 3.3 V/5 V (TTL) Compatible. Internally pulled down.                                     |

| 9               | NC       | No Connection. This pin should be isolated from any traces or via on the PCB board.                                                           |

| 10              | OUT6     | Half Bridge Output 6                                                                                                                          |

| 11              | OUT4     | Half Bridge Output 4                                                                                                                          |

| 12              | GND      | Ground. Shorted to pin 13 internally.                                                                                                         |

| 13              | GND      | Ground. Shorted to pin 12 internally.                                                                                                         |

| 14              | OUT3     | Half Bridge Output 3                                                                                                                          |

| 15              | NC       | No Connection. This pin should be isolated from any traces or via on the PCB board.                                                           |

| 16              | VS2      | Voltage Power Supply input for the Drivers 3, 4 and 6. This pin must be connected to VS1 externally.                                          |

| 17              | Reserved | Reserved for internal use. This pin must be grounded.                                                                                         |

| 18              | Reserved | Reserved for internal use. This pin must be grounded.                                                                                         |

| 19              | CSB      | Chip Select Bar. Active low serial port operation. 3.3V/5V (TTL) Compatible. Internally pulled up.                                            |

| 20              | SCLK     | Serial Clock. Clock input for use with SPI communication. 3.3 V/5 V (TTL) Compatible. Internally pulled down.                                 |

| 21              | VS1      | Voltage Power Supply input for the Drivers 1, 2 and 5, all the pre-drivers and the charge pump. This pin must be connected to VS2 externally. |

| 22              | NC       | No Connection. This pin should be isolated from any traces or via on the PCB board.                                                           |

| 23              | OUT2     | Half Bridge Output 2                                                                                                                          |

| 24              | GND      | Ground. Shorted to pin 1 internally.                                                                                                          |

#### MAXIMUM RATINGS

| Rating                                                                                 | Symbol             | Value                     | Unit |

|----------------------------------------------------------------------------------------|--------------------|---------------------------|------|

| Power Supply Voltage (VS1, VS2)<br>(DC)<br>(AC), t < 500ms, lvsx > -2A                 | VsxdcMax<br>VSXac  | -0.3 to 40<br>-1.0        | V    |

| Output Pin OUTx<br>(DC)<br>(AC), t< 500ms, IOUTx > -1.1A<br>(AC), t< 500ms, IOUTx < 1A | VoutxDc<br>VoutxAc | -0.3 to 40<br>-1.0<br>1.0 | V    |

| Pin Voltage (Logic Input pins, SI, SCLK, CSB, SO, EN, V <sub>CC</sub> )                | VioMax             | -0.3 to 5.5               | V    |

| Output Current (OUT1, OUT2, OUT3, OUT4, OUT5, OUT6)                                    | loutxImax          | -2.0 to 2.0               | А    |

| Electrostatic Discharge, Human Body Model, VSx, OUTx (AEC-Q100-002)                    | Vesd4k             | 4.0                       | kV   |

| Electrostatic Discharge, Human Body Model, all other pins (AEC-Q100-002)               | Vesd2k             | 2.0                       | kV   |

| Electrostatic Discharge, Machine Model (AEC-Q100-003)                                  | Vesd200            | 200                       | V    |

| Short Circuit Reliability Characterization                                             | AECQ10x            | Grade A                   | -    |

| Operating Junction Temperature                                                         | Tj                 | -40 to 150                | °C   |

| Storage Temperature Range                                                              | Tstr               | -55 to 150                | °C   |

| Moisture Sensitivity Level (MAX 260°C Processing)                                      | MSL2               | 2                         | -    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### THERMAL INFORMATION (Note 1)

| Rating              | Symbol          | Value | Unit |

|---------------------|-----------------|-------|------|

| Junction to Ambient | $R_{\theta JA}$ | 96.4  | °C/W |

| Junction to Lead    | $R_{\psi JL}$   | 63    | °C/W |

Thermal Information is based on having 3 high side and 3 low side devices dissipating 80 mW each on a 2 layer board 0.062" thick FR4 board with 600 mm<sup>2</sup> copper spreader area. 2 oz copper is used for the copper spreader area and the ambient temperature is specified at 25°C.

## **RECOMMENDED OPERATING CONDITIONS**

|                              |        | Value |      |      |

|------------------------------|--------|-------|------|------|

| Rating                       | Symbol | Min   | Max  | Unit |

| Digital Supply Input Voltage | VccOp  | 3.15  | 5.25 | V    |

| Battery Supply Input Voltage | VsxOp  | 5.5   | 28   | V    |

| DC Output Current            | IxOp   | -     | 0.55 | A    |

| Junction Temperature         | TjOp   | -40   | 125  | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

**ELECTRICAL CHARACTERISTICS** (-40°C <  $T_J$  < 150°C, 5.5 V < VSx < 40 V, 3.15 V < V<sub>CC</sub> < 5.25 V, EN = V<sub>CC</sub>, unless otherwise specified)

| Characteristic                                       | Symbol              | Conditions                                                                                          | Min  | Тур  | Max  | Unit |

|------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------|------|------|------|------|

| GENERAL                                              |                     |                                                                                                     |      |      |      |      |

| Supply Current (VS1 + VS2)<br>Sleep Mode             | lqVsx85             | VS1 = VS2 = 13.2 V, V <sub>CC</sub> = 0 V –40°C to 85°C No Load                                     | _    | 1.0  | 2.5  | μΑ   |

| Supply Current (VS1 + VS2)<br>Active Mode            | lvsOp               | EN = V <sub>CC</sub> , 5.5 V < VSx < 28 V No Load                                                   | -    | 2.5  | 5.0  | mA   |

| Supply Current (V <sub>CC</sub> )<br>Sleep Mode      | lqV <sub>CC</sub>   | $CSB = V_{CC}, EN = SI = SCLK = 0 V$                                                                | _    | 1.0  | 2.5  | μA   |

| Active Mode                                          | IV <sub>CC</sub> Op | $(-40^{\circ}C \text{ to } 85^{\circ}C)$<br>EN = CSB = V <sub>CC</sub> , SI = SCLK = 0 V<br>No Load | -    | 1.5  | 3.0  | mA   |

| Total Sleep Mode Current<br>I(VS1) + I(VS2) + I(VCC) | IqTot               | Sleep Mode, -40°C to 85°C, No Load                                                                  | _    | 2    | 5    | μΑ   |

| V <sub>CC</sub> Power–On–Reset Threshold             | V <sub>CC</sub> por | V <sub>CC</sub> increasing                                                                          | _    | 2.55 | 2.9  | V    |

| VSx Undervoltage Detection<br>Threshold              | VsXuv               | VSx decreasing                                                                                      | 3.7  | 4.1  | 4.5  | V    |

| VSx Undervoltage Detection<br>Hysteresis             | VsXuHys             |                                                                                                     | 100  | -    | 450  | mV   |

| VSx Overvoltage Detection<br>Threshold               | VsXov               | VSx increasing                                                                                      | 32   | 36   | 40   | V    |

| VSx Overvoltage Detection<br>Hysteresis              | VsXoHys             |                                                                                                     | 1    | 2.5  | 4    | V    |

| THERMAL RESPONSE                                     |                     | ·                                                                                                   |      |      |      |      |

| Thermal Warning                                      | Twr                 | Not ATE tested                                                                                      | 120  | 140  | 170  | °C   |

| Thermal Warning Hysteresis                           | TwHy                | Not ATE tested                                                                                      | _    | 20   | -    | °C   |

| Thermal Shutdown                                     | Tsd                 | Not ATE tested                                                                                      | 150  | 175  | 200  | °C   |

| Thermal Shutdown Hysteresis                          | TsdHy               | Not ATE tested                                                                                      | -    | 20   | -    | °C   |

| OUTPUTS                                              | •                   | •                                                                                                   |      |      |      |      |

| Output High R <sub>DS(on)</sub> (source)             | RDSonHS             | $I_{out} = -500 \text{ mA}$                                                                         | _    | 1    | 2.25 | Ω    |

| Output Low R <sub>DS(on)</sub> (sink)                | RDSonLS             | l <sub>out</sub> = 500 mA                                                                           | -    | 1    | 2.0  | Ω    |

| Output Path R <sub>DS(HSx+LSx)</sub>                 | RDSonPath           | I <sub>out</sub> =   500  mA                                                                        | -    | -    | 4.0  | Ω    |

| Source Leakage Current                               | lsrcLkg13.2         | OUT(1–6) = 0 V, VSx = 13.2 V, V <sub>CC</sub> = 5 V,                                                | -1.0 | -    | -    | μA   |

|                                                      | lsrcLkg40           | -40°C to 85°C<br>OUT(1-6) = 0 V, VSx = 40 V, V <sub>CC</sub> = 5 V,<br>-40°C to 85°C                | -5.0 | -    | -    |      |

| Sink Leakage Current                                 | lsnkLkg13.2         | OUT(1–6) = VSx = 13.2 V, V <sub>CC</sub> = 5 V,                                                     | -    | - 1  | 1.0  | μA   |

|                                                      | lsnkLkg40           | -40°C to 85°C<br>OUT(1-6) = VSx = 40 V, V <sub>CC</sub> = 5 V,<br>-40°C to 85°C                     | -    | -    | 5.0  |      |

| Overcurrent Shutdown Threshold (Source)              | lsdSrc              | V <sub>CC</sub> = 5 V, VSx = 13.2 V                                                                 | -2.0 | -1.2 | -0.8 | A    |

| Overcurrent Shutdown Thresh-<br>old (Sink)           | IsdSnk              | V <sub>CC</sub> = 5 V, VSx = 13.2 V                                                                 | 0.8  | 1.2  | 2.0  | A    |

| Over Current Delay Timer                             | TdOc                |                                                                                                     | 10   | 25   | 50   | μs   |

| Under Load Detection Threshold (Low Side)            | luldLS              | V <sub>CC</sub> = 5 V, VSx = 13.2 V                                                                 | 2.0  | 11   | 20   | mA   |

| Under Load Detection Thresh-<br>old (High Side)      | luldHS              | V <sub>CC</sub> = 5 V, VSx = 13.2 V                                                                 | -20  | -11  | -2.0 | mA   |

| Under Load Detection Delay<br>Time                   | TdUld               | V <sub>CC</sub> = 5 V, VSx = 13.2 V                                                                 | 200  | 350  | 600  | μs   |

**ELECTRICAL CHARACTERISTICS** ( $-40^{\circ}C < T_J < 150^{\circ}C$ , 5.5 V < VSx < 40 V, 3.15 V < V<sub>CC</sub> < 5.25 V, EN = V<sub>CC</sub>, unless otherwise specified)

| Characteristic                                 | Symbol           | Conditions                       | Min | Тур | Max      | Unit |

|------------------------------------------------|------------------|----------------------------------|-----|-----|----------|------|

| BODY DIODE                                     |                  |                                  |     |     |          |      |

| Power Transistor Body Diode<br>Forward Voltage | VbdFwd           | lf = 500 mA                      | -   | 0.9 | 1.3      | V    |

| LOGIC INPUTS (EN, SI, SCLK                     | , CSB)           | •                                |     |     |          |      |

| Input Threshold<br>High<br>Low                 | VthInH<br>VthInL |                                  | 2.0 |     | _<br>0.6 | V    |

| Input Hysteresis (SI, SCLK, CSB)               | VthInHys         |                                  | 50  | 150 | 300      | mV   |

| Enable Hysteresis                              | VthENHys         |                                  | 150 | 400 | 800      | mV   |

| Input Pull-down Resistance<br>(EN, SI, SCLK)   | Rpdx             | EN = SI = SCLK = V <sub>CC</sub> | 50  | 125 | 200      | kΩ   |

| Input Pull-up Resistance<br>(CSB)              | RpuCSB           | CSB = 0 V                        | 50  | 125 | 250      | kΩ   |

| Input Capacitance                              | Cinx             | Not ATE tested                   | -   |     | 15       | pF   |

| LOGIC OUTPUT (SO)                              | 1                | •                                |     |     | •        |      |

| Output High                                    | VaaH             | 1                                | V   | 1   | ſ        | V    |

| Output High                  | VsoH       | I <sub>SOURCE</sub> = -1 mA                                | V <sub>CC</sub> –<br>0.6 | - | -   | V  |

|------------------------------|------------|------------------------------------------------------------|--------------------------|---|-----|----|

| Output Low                   | VsoL       | I <sub>SINK</sub> = 1.6 mA                                 | -                        | - | 0.4 | V  |

| Tri-state Leakage            | ItriStLkg  | CSB = 5 V                                                  | -5                       | - | 5   | μΑ |

| Tri-state Output Capacitance | ltriStCout | CSB = $V_{CC}$ , 0 V < $V_{CC}$ < 5.25 V<br>Not ATE tested | -                        | - | 15  | pF |

$\textbf{ELECTRICAL CHARACTERISTICS} (-40^{\circ}C < TJ < 150^{\circ}C, \ 5.5 \ V < VSx < 40 \ V, \ 3.15 < Vcc < 5.25 \ V, \ \text{EN} = Vcc, \ unless \ otherwise$ specified)

| Characteristic                                      | Symbol      | Conditions                                                          | Timing<br>Chart | Min        | Тур    | Max        | Unit |

|-----------------------------------------------------|-------------|---------------------------------------------------------------------|-----------------|------------|--------|------------|------|

| DRIVER OUTPUT TIMING SPE                            | CIFICATIONS |                                                                     |                 | -          |        |            |      |

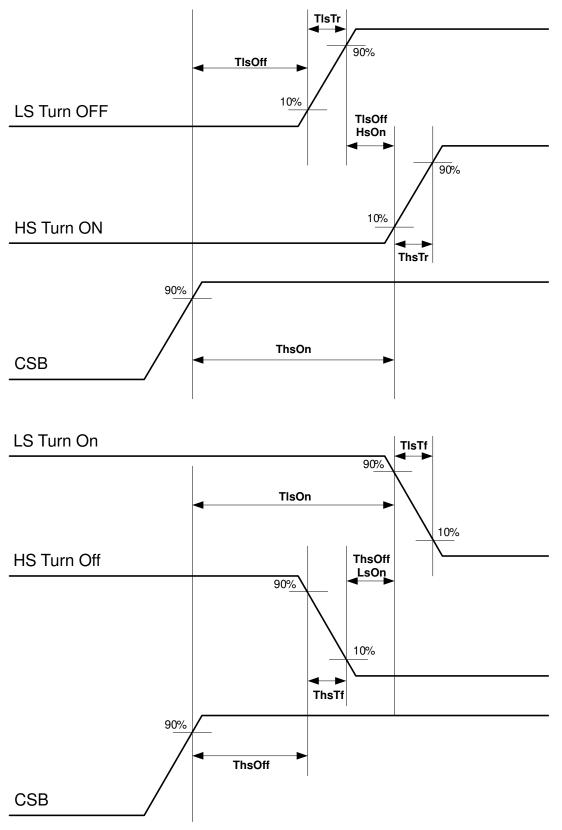

| High Side Turn On Time                              | ThsOn       | VSx = 13.2 V, $R_{load}$ = 39 $\Omega$                              |                 | _          | 7.5    | 13         | μs   |

| High Side Turn Off Time                             | ThsOff      | VSx = 13.2 V, $R_{load}$ = 39 $\Omega$                              |                 | _          | 3.0    | 6.0        | μs   |

| Low Side Turn On Time                               | TlsOn       | VSx = 13.2 V, $R_{load}$ = 39 $\Omega$                              |                 | _          | 6.5    | 13         | μs   |

| Low Side Turn Off Time                              | TIsOff      | VSx = 13.2 V, $R_{load}$ = 39 $\Omega$                              |                 | -          | 2.0    | 6.0        | μs   |

| High Side Rise Time                                 | ThsTr       | VSx =13.2 V, $R_{load}$ = 39 $\Omega$                               |                 | -          | 4.0    | 8.0        | μs   |

| High Side Fall Time                                 | ThsTf       | VSx = 13.2 V, $R_{load}$ = 39 $\Omega$                              |                 | -          | 2.0    | 4.0        | μs   |

| Low Side Rise Time                                  | TlsTr       | VSx = 13.2 V, $R_{load}$ = 39 $\Omega$                              |                 | -          | 1.0    | 3.0        | μs   |

| Low Side Fall Time                                  | TlsTf       | VSx = 13.2 V, $R_{load}$ = 39 $\Omega$                              |                 | -          | 1.0    | 3.0        | μs   |

| High Side Off to Low Side On<br>Non–Overlap Time    | ThsOffLsOn  | VSx = 13.2 V, $R_{load}$ = 39 $\Omega$                              |                 | 1.5        | -      | -          | μs   |

| Low Side Off to High Side On<br>Non–Overlap Time    | TIsOffHsOn  | VSx = 13.2 V, $R_{load}$ = 39 $\Omega$                              |                 | 1.5        | -      | -          | μs   |

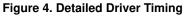

| SERIAL PERIPHERAL INTER                             | ACE         |                                                                     |                 | -          |        |            |      |

| SCLK Frequency                                      | Fclk        | V <sub>CC</sub> = 5 V<br>V <sub>CC</sub> = 3.15 V                   |                 | -          |        | 5.0<br>2.0 | MHz  |

| SCLK Clock Period                                   | TpClk       | V <sub>CC</sub> = 5 V<br>V <sub>CC</sub> = 3.15 V                   |                 | 200<br>500 | _<br>_ | _<br>_     | ns   |

| SCLK High Time                                      | TclkH       |                                                                     | 1               | 85         | -      | -          | ns   |

| SCLK Low Time                                       | TclkL       |                                                                     | 2               | 85         | -      | -          | ns   |

| SCLK Setup Time                                     | TclkSup     |                                                                     | 3<br>4          | 85<br>85   |        |            | ns   |

| SI Setup Time                                       | TsiSup      |                                                                     | 11              | 50         | -      | -          | ns   |

| SI Hold Time                                        | TsiH        |                                                                     | 12              | 50         | -      | -          | ns   |

| CSB Setup Time                                      | TcsbSup     |                                                                     | 5<br>6          | 100<br>100 | _<br>_ | _<br>_     | ns   |

| CSB High Time (Note 2)                              | TcsbH       |                                                                     | 7               | 5.0        | -      | -          | μs   |

| SO enable after CSB falling edge                    | TenSo       | V <sub>CC</sub> = 5 V                                               | 8               | -          | -      | 200        | ns   |

| SO disable after CSB rising edge                    | TdisSo      | V <sub>CC</sub> = 5 V                                               | 9               | -          | -      | 200        | ns   |

| SO Rise Time                                        | TsoR        | C <sub>load</sub> = 40 pF<br>Not ATE tested                         | -               | -          | 10     | 25         | ns   |

| SO Fall Time                                        | TsoF        | C <sub>load</sub> = 40 pF<br>Not ATE tested                         | -               | -          | 10     | 25         | ns   |

| SO Valid Time                                       | TsoV        | C <sub>load</sub> = 40 pF<br>SCLK ↑ to SO 50%,<br>Not ATE tested    | 10              | -          | 20     | 50         | ns   |

| EN Low Valid Time (Note 3)                          | TenL        | V <sub>CC</sub> = 5 V<br>EN going low 50% to<br>OUTx turing off 50% |                 | 10         | -      | -          | μs   |

| EN High to SPI Valid                                | TenHspiV    |                                                                     |                 | -          | -      | 100        | μs   |

| SRR Delay Between Two<br>Consecutive Frame (Note 4) | Tsrr        |                                                                     |                 | 150        | -      | -          | μs   |

2. This is the minimum time the user must wait between SPI commands.

3.

This is the minimum time the user must wait before bringing EN up. This is the minimum time the user must wait to send a SRR command between consecutive frames. If Tsrr time is not met the SRR request 4. is ignored.

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

## ELECTRICAL CHARACTERISTIC TIMING DIAGRAMS

Figure 5. Detailed SPI Timing

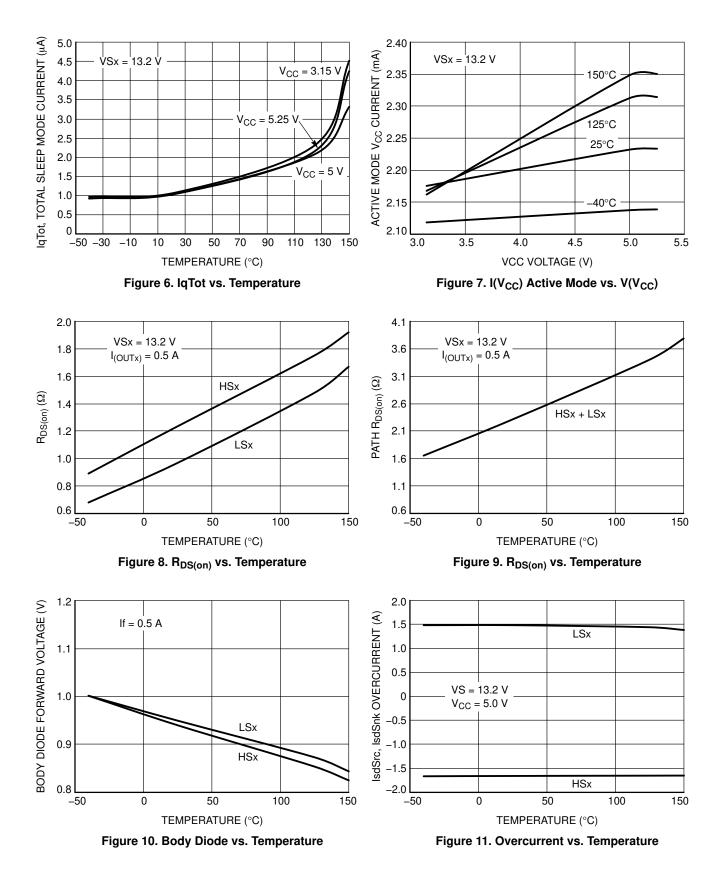

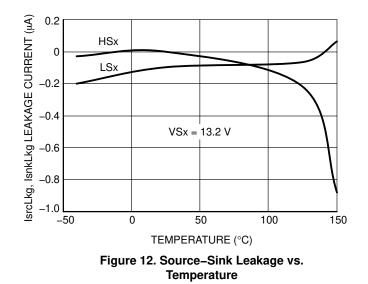

## **TYPICAL PERFORMANCE GRAPHS**

## **TYPICAL PERFORMANCE GRAPHS**

#### **OPERATING DESCRIPTION**

**SPI** Communication

#### **General Overview**

The NCV7728 is comprised of twelve DMOS power drivers (six PMOS High Side Driver and six NMOS Low Side Driver) configured as six half bridges that enables three independent Full Bridge operations. Each output drive is characterized for a max 550 mA DC load and has a typical 2 A surge capability (at VSx =13.2 V). Strict adherence to integrated circuit die temperature is necessary. Maximum die temperature is 150°C. This may limit the number of drivers enabled at one time. Output drive control and fault reporting is handled via the SPI (Serial Peripheral Interface) port.

An Enable function (EN) provides a low quiescent sleep current mode when the device is not being utilized. No data is stored when the device is in sleep mode. An internal pull down resistor is provided on the EN input to ensure the device is off if the input signal is lost. De–asserting the EN signal clears all the registers and resets the driver. When the EN signal is asserted the IC will proceed with the V<sub>CC</sub> POR cycle and brings the drivers into normal operation. 16-bit full duplex SPI communication has been implemented for the communication of this IC for device configurations, driver controls and reading the diagnostic data. In addition to the 16-bit diagnostic data, a pseudo bit (PRE\_15) can also be retrieved from the SO register. The part is required to be enabled (EN active high) for SPI communication. The inputs for the SPI are TTL logic compatible and are specified by the VthInH and VthInL thresholds. The active low CSB input has a pull up resistor and the remaining SPI inputs have pull-down resistors to bias them to a known state when SPI is not active.

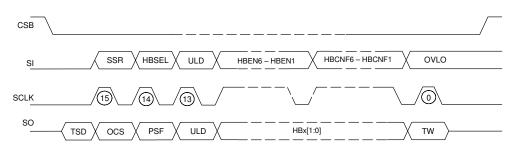

Reference the SPI communication frame format diagram in Figure 13 for the 16 bit SPI implementation. Tables 1 and 2 define the programming bits and diagnostic bits shown in Figure 13.

#### SPI COMMUNICATION FRAME FORMAT

Figure 13. SPI Communication Frame Format

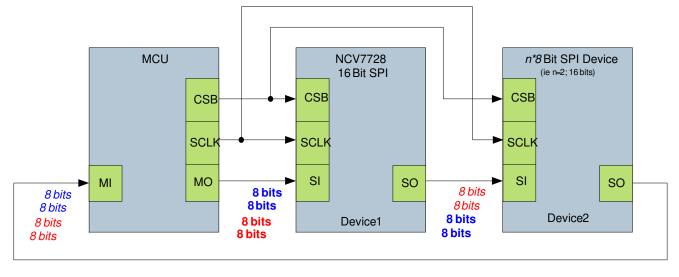

Communication is implemented as follows and is also illustrated in Figure 17:

- 1. SI and SCLK are set to low before the CSB cycle.

- 2. CSB goes low to allow serial data transfer.

- 3. SI data starting with the Most Significant bit (MSB) is shifted in first.

- 4. SI data is recognized on every falling edge of the clock.

- 5. Simultaneously, SO data from the previous frame starting with the MSB bit is shifted out on every rising edge of the clock.

- 6. The input data is compared to a 16 bit counter for the initial 16 bits shifted into SI for frame detection error scheme.

- 7. The sequential input bits are compared to a  $n \ge 8$  (n can take on the value of any integer) bit counter for daisy chain operations and are monitored by the frame detection error scheme.

- 8. CSB goes high and the most recent 16 bits clocked into SI are transferred to the data register given that there is no frame detection error. Otherwise the entire frame is ignored.

- 9. SO is tri-state when CSB is high.

### Table 1. SPI INPUT DATA FRAME

| Input Data |                           |                                                               |                      |  |  |

|------------|---------------------------|---------------------------------------------------------------|----------------------|--|--|

| Bit Number | Bit Name                  | Bit Description                                               | Bit Status           |  |  |

| 15         | SRR Status Reset Register |                                                               | 0 = No Reset         |  |  |

|            |                           | When Asserted All Latched Faults are Cleared (TSD, OCS & ULD) | 1 = Reset            |  |  |

| 14         | HBSEL (Note 5)            | Half Bridge Selection                                         | Reserved             |  |  |

| 13         | ULDSC                     | Under Load Detection Shutdown Control                         | 0 = Disable          |  |  |

|            |                           | Global Enable; Per Half Bridge Operation                      | 1 = Enable           |  |  |

| 12         | HBEN6                     | Half Bridge 6 Enable                                          | 0 = High Z           |  |  |

|            |                           |                                                               | 1 = Enabled          |  |  |

| 11         | HBEN5                     | Half Bridge 5 Enable                                          | 0 = High Z           |  |  |

|            |                           |                                                               | 1 = Enabled          |  |  |

| 10         | HBEN4                     | Half Bridge 4 Enable                                          | 0 = High Z           |  |  |

|            |                           |                                                               | 1 = Enabled          |  |  |

| 9          | HBEN3                     | Half Bridge 3 Enable                                          | 0 = High Z           |  |  |

|            |                           |                                                               | 1 = Enabled          |  |  |

| 8 HBEN2    | HBEN2                     | Half Bridge 2 Enable                                          | 0 = High Z           |  |  |

|            |                           |                                                               | 1 = Enabled          |  |  |

| 7          | HBEN1                     | Half Bridge 1 Enable                                          | 0 = High Z           |  |  |

|            |                           |                                                               | 1 = Enabled          |  |  |

| 6          | HBCNF6                    | Half Bridge 6 Configuration Control                           | 0 = LS6 ON & HS6 OFF |  |  |

|            |                           |                                                               | 1 = LS6 OFF & HS6 ON |  |  |

| 5          | HBCNF5                    | Half Bridge 5 Configuration Control                           | 0 = LS5 ON & HS5 OFF |  |  |

|            |                           |                                                               | 1 = LS5 OFF & HS5 ON |  |  |

| 4          | HBCNF4                    | Half Bridge 4 Configuration Control                           | 0 = LS4 ON & HS4 OFF |  |  |

|            |                           |                                                               | 1 = LS4 OFF & HS4 ON |  |  |

| 3          | HBCNF3                    | Half Bridge 3 Configuration Control                           | 0 = LS3 ON & HS3 OFF |  |  |

|            |                           |                                                               | 1 = LS3 OFF & HS3 ON |  |  |

| 2          | HBCNF2                    | Half Bridge 2 Configuration Control                           | 0 = LS2 ON & HS2 OFF |  |  |

|            |                           |                                                               | 1 = LS2 OFF & HS2 ON |  |  |

| 1          | HBCNF1                    | Half Bridge 1 Configuration Control                           | 0 = LS1 ON & HS1 OFF |  |  |

|            |                           |                                                               | 1 = LS1 OFF & HS1 ON |  |  |

| 0          | OVLO                      | Over Voltage Lock Out                                         | 0 = Disable          |  |  |

|            |                           | Global Effect                                                 | 1 = Enable           |  |  |

5. HBSEL enables bridge selection for the NCV7719 and NCV7720 devices. In the NCV7728 it is recommended to set the HBSEL to zero.

| Table 2. SPI OUTPUT | T DATA FRAME |

|---------------------|--------------|

|---------------------|--------------|

| Output Data |              |                                           |                                       |  |  |

|-------------|--------------|-------------------------------------------|---------------------------------------|--|--|

| Bit Number  | Bit Name     | Bit Description                           | Bit Status                            |  |  |

|             |              |                                           | 0 = No Fault                          |  |  |

| PRE_15      | TSD          | Latched Thermal Shutdown                  | 1 = Fault                             |  |  |

| 4.5         | 000          | Over Current Shutdown                     | 0 = No Fault                          |  |  |

| 15          | OCS          | Global Notification                       | 1 = Fault                             |  |  |

|             | DOF          | Power Supply Failure on VS1 and/or VS2    | 0 = No Fault                          |  |  |

| 14          | PSF          | Under Voltage and Over Voltage Monitoring | 1 = Fault                             |  |  |

| 10          |              | Under Load Detection                      | 0 = No Fault                          |  |  |

| 13          | ULD          | Global Notification                       | 1 = Fault                             |  |  |

| 12          | HB6          |                                           |                                       |  |  |

| 11          | [1:0]        | Half Bridge 6 Status                      |                                       |  |  |

| 10          | HB5<br>[1:0] |                                           |                                       |  |  |

| 9           |              | Half Bridge 5 Status                      |                                       |  |  |

| 8           | HB4          |                                           |                                       |  |  |

| 7           | [1:0]        | Half Bridge 4 Status                      | 0x00b – Output Disable<br>0x01b – OCS |  |  |

| 6           | HB3          |                                           | 0x10b – ULD<br>0x11b – Output Enabled |  |  |

| 5           | [1:0]        | Half Bridge 3 Status                      |                                       |  |  |

| 4           | HB2          |                                           | 7                                     |  |  |

| 3           | [1:0]        | Half Bridge 2 Status                      |                                       |  |  |

| 2           | 2 HB1        |                                           | 7                                     |  |  |

| 1 [1:0]     |              | Half Bridge 1 Status                      |                                       |  |  |

|             |              | Thermal Warning                           | 0 = No Fault                          |  |  |

| 0           | TW           | Global Notification                       | 1 = Fault                             |  |  |

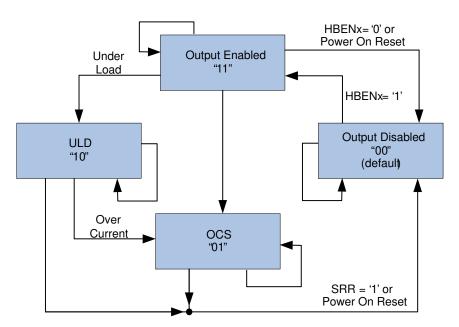

HBx[1:0] bits are priority encoded to provide the status information of each of the half-bridge outputs. Figure 14 shows the priority encoding state diagram for the HBx[1:0] bits.

Figure 14. SO HBx[1:0] Priority Encoding State Diagram

As seen from Figure 14 an over current event following an under load condition on the same half-bridge reports HBx = '10' then HBx = '01'. However, an over current preceding an under load fault only reports HBx = '01' since there are no direct path from the OCS state to the ULD state. Thus an over current shutdown fault must be cleared before an under load fault is reported on the same half-bridge.

HBx[1:0] bits are priority encoded to provide the status information of each of the half-bridge outputs. Thus an over current shutdown fault must be cleared before an under load fault is reported on the same half-bridge. The latched thermal shutdown (TSD) information is available on SO after CSB goes low until the first rising SCLK edge. The following procedures must be met for a true TSD reading:

- 1. SCLK and SI are low before the CSB cycle. Violating these conditions will results in an undetermined SPI behavior or/and an incorrect TSD reading.

- 2. CSB transitioning from high to low.

- 3. CSB setup time (TcsbSup) is satisfied and the data is captured before the first SCLK rising edge.

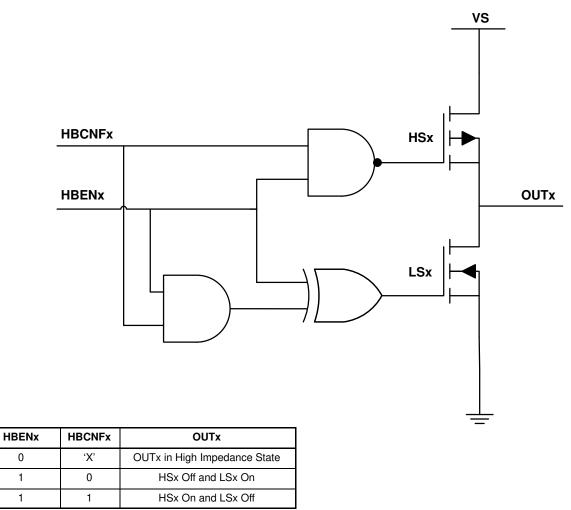

#### **Driver Control**

The NCV7728 has the flexibility of controlling each driver through the 16 bit SPI frame (Bits 12–1) and the logic

combination required for bridge control is defined in Figure 15.

'X' = Don't Care

The digital design insures that the high side and low side of the same half bridge will not be active at the same time. Thus the device self protects from a current shoot through condition. Delays (ThsOffLsOn and TlsOffHsOn) between the high side and low side switching are implemented for same reasons.

#### **Frame Detection**

To maintain the data integrity, the NCV7728 has 16 bit frame detection. A valid frame for a single CSB cycle requires 16 bits to be clocked into SI for the initial 16 bits and  $n \ge 8$  bits thereafter. In an instance of an invalid SPI frame the entire frame is ignored, but the previous states of the corresponding outputs are maintained.

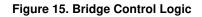

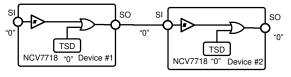

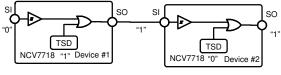

#### **Daisy Chain Operation**

Daisy chain communications between multiple of 8-bit SPI compatible IC's is possible by connection of the serial output pin (SO) to the input of the sequential IC (SI). The clock phase and clock polarity respect to the data must be the same for all the devices on the chain. Figure 16 illustrates the hardware configuration of NCV7728 daisy chained with a n\*8 bit (ie n = 2; 16 bit) SPI device. The progression of data from the MCU through the sequential devices is also shown. Strict adherence to the frame format illustrated in Figure 17 is required for the proper serial daisy chain operations.

Command Bits for the Device 2 Previous Diagnostic Bits from Device? Command Bits for Device 1 Previous Diagnostic Bits From Device1

#### Figure 16. Serial Daisy Chain

If Device 2 is a 16 bit IC, then a total of 32 bits must be generated from the MCU for a complete transport of data in the system. Monitoring of all the devices in the serial chain must be employed on a system level architecture. Thus, pre-cautious measure should be taken to avoid situations where not enough frames were sent to the devices, but the frames transmitted did not violate the internal frame detection counters. For these scenarios, invalid data is accepted by NCV7728 and possibly by other devices on the chain depending on their frame detection design. The data shifted in will be transferred to the data registers of the devices on the beginning of the chain and the devices at the end of the chain will get the previous diagnostic data of the preceding devices.

Figure 17. SPI Data Recognition and Frame Detection

The TSD bit is multiplexed with the SPI SO data and OR'd with the SI input (Figure 18) to allow for reporting in a serial daisy chain configuration in devices with the same SPI protocol. A TSD error bit as a "1" automatically propagates through the serial daisy chain circuitry from the SO output

of one device to the SI input of the next. This is shown in Figures 19 and 20; first as the daisy chained devices connected with no thermal shutdown latched fault (Figure 19) and subsequently with a TSD fault in device 1 propagating through to device 2 (Figure 20).

Figure 18. TSD SPI Link

Figure 19. Daisy Chain No TSD Fault

Figure 20. Daisy Chain TSD Error Propagation

#### **DEVICE PROTECTION, DIAGNOSTICS AND FAULT REPORTING**

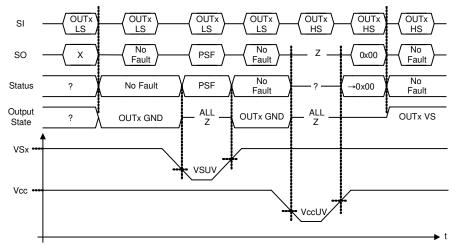

#### **Power Up/Down Control**

Each analog power pin (VS1 or VS2) powers their respective output drivers. After a device has powered up and the output drivers are allowed to turn on, the output drivers will not turn off until the voltage on the supply pins is reduced below the initial under voltage threshold, exceeds the over voltage threshold or if shut down by either a SPI command or a fault condition.

Internal power–up circuitry on the logic supply pin supports a smooth turn on transition. VCC power up resets the internal logic such that all output drivers will be off as power is applied. All the internal counters, SI and SO along with all the digital registers will be cleared on VCC POR. Exceeding the under voltage lockout threshold on VCC allows information to be input through the SPI port for turn on control. Logic information remains intact over the entire VS1 and VS2 voltage range.

#### **Under Voltage Shutdown**

An under voltage lockout circuit prevents the output drivers from turning on unintentionally. This control is provided by monitoring the voltages on the VS1, VS2 and VCC pins. A built–in hysteresis on the under voltage threshold is included to prevent an unknown region on the power pins; VCC, VS1 and VS2. When the VCC goes below the threshold, all outputs are turned off and the input and output registers are cleared.

An under voltage condition on the VSx pins will result in shutting off all the drivers and the status bit 14 (PSF) will be set. The SPI port remains active during a VSx under–voltage if proper VCC voltage is supplied. Also all driver states will be maintained in the logic circuitry with the valid VCC voltage. Once the input voltage VSx is above the under voltage threshold level the drivers will return to programmed operation and the PSF output register bit is cleared.

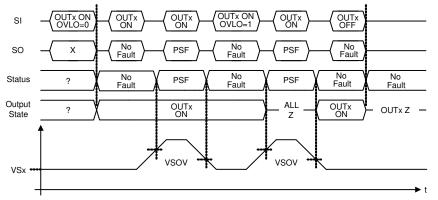

Under-voltage timing diagram is provided in Figure 21.

Figure 21. Under–Voltage Timing Diagram

### **Over Voltage Shutdown**

Over voltage shutdown circuitry monitors the voltage on the VS1 and VS2 pins, which permits a 40 V maximum. When the Over–voltage Threshold level has been breached on the VS1or VS2 supply input, the output bit 14 (PSF) will be set. Additionally, if the input bit 0 (OVLO) is asserted, all outputs will turn off. During an Over Voltage Lockout condition the turn on/off status is maintained in the logic circuitry. When proper input voltage levels are re–established, the programmed outputs will turn back on. Over–voltage shutdown can be disabled by using the SPI input bit 0 (OVLO = 0) to run through a load dump situation. It is highly recommended to operate the part with OVLO bit asserted to ensure that the drivers remain off during a load dump scenario.

The table below describes the driver status when enabling/disabling the over voltage lock out feature during normal and overvoltage situations.

| OVLO Input<br>Bit | VSx OVLO<br>Condition | Output Data Bit 14 Power Supply Fail (PSF) Status | OUTx Status                                              |

|-------------------|-----------------------|---------------------------------------------------|----------------------------------------------------------|

| 0                 | 0                     | ʻ0'                                               | Not in Overvoltage Outputs Unchanged                     |

| 0                 | 1                     | '1'<br>(Clears when VSx within Operating Range)   | In Overvoltage $\rightarrow$ Outputs Unchanged           |

| 1                 | 0                     | ʻ0'                                               | Not in Overvoltage Outputs Unchanged                     |

| 1                 | 1                     | '1'<br>(Clears when VSx within Operating Range)   | All Outputs Off (Remain off until VSx is out<br>of OVLO) |

Table 3. OVER-VOLTAGE LOCK OUT (OVLO)

Over-voltage timing diagram is provided in Figure 22.

Figure 22. Over–Voltage Timing Diagram

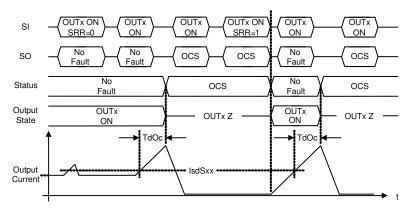

#### **Over Current Detection and Shutdown**

The NCV7728 offers over current shutdown protection on the OUTx pins by monitoring the current on the high side and low side drivers. If the over current threshold is breached, the corresponding output is latched off (HS and LS driver is latched off) after the specified shutdown time, TdOc. Upon over current shutdown, the serial output bit OCS will be set and the corresponding HBx[1:0] will be changed to "01" to denote a high power dissipation state. Devices can be turned back on via the SPI port once the OCS condition is cleared by setting the SRR to '1' on the next SPI command. The event triggering the over current shutdown condition must be resolved prior to clearing the OCS bit to avoid repetitive stress on the drivers. Failure to do so may result in non reversible fatal damage.

The SO data OCS shown on Figure 23 corresponds to both the global SO bit #15 and the HBx OCS encoding state '01'.

Note: high currents could cause a high rise in die temperature. Devices will turn off if the die temperature exceeds the thermal shutdown temperature.

Figure 23. Over-Current Timing Diagram

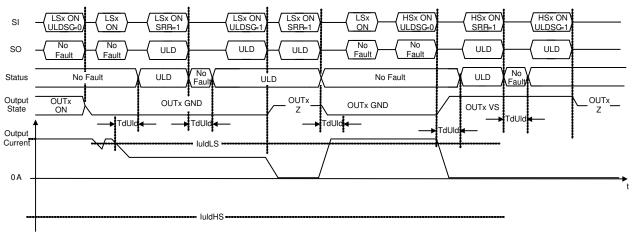

#### **Under Load Detection**

The under-load detection is employed on both the HS and LS drivers. A global output bit (ULD) reports under load fault if at least one of the channels detect an under load condition. When configured for either LS or HS operation, a minimum load current (IuldLS or |IuldHS| – this is the maximum open circuit detection threshold) is required when the drivers are turned on to avoid an under-load condition. If the under-load detection threshold has been breached longer than the specified under-load timer (TdUld), the ULD output bit is set to '1' and HBx[1:0] bits transitions to "10". Furthermore, if the Under-Load Detection Shutdown

Control (ULDSC bit # 13) input bit is set then the offending half-bridge output will be turned off (HS and LS drivers will be latched off). Otherwise the outputs remain active and the device configuration can be changed. The SO reporting is stored until the SRR clears the fault. Since an OCS fault has a higher priority over an under load fault, the HBx[1:0] under load fault state can be masked by an over current fault.

There is only one global under load timer for all the drivers. If the TdUld timer is already activated due to one under load, any subsequent under load delays will be the remainder of the TdUld timer.

| ULDSC Input<br>Bit 13 | OUTx ULD<br>Condition | Output Data Bit Under Load Detect Sta-<br>tus | OUTx Status                          |  |

|-----------------------|-----------------------|-----------------------------------------------|--------------------------------------|--|

| 0                     | 0                     | ʻ0'                                           | Unchanged                            |  |

| 0                     | 1                     | '1'<br>(Need SRR to reset)                    | Unchanged                            |  |

| 1                     | 0                     | ʻ0'                                           | Unchanged                            |  |

| 1                     | 1                     | '1' (Need SRR to reset)                       | OUTx Latches off (Need SRR to reset) |  |

Table 4. UNDER-LOAD DRIVER STATUS

The ULD SO data provided in the under load timing diagram in Figure 24 reflects the global ULD SO bit #13 and the HBx ULD encoding state '10'.

Figure 24. LS Under–load Timing Diagram

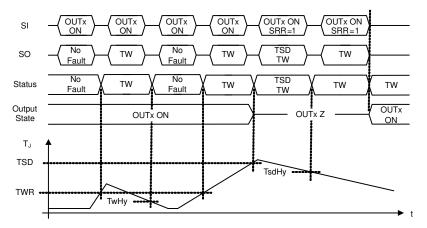

#### Thermal Warning and Thermal Shutdown

The NCV7728 provides individual thermal sensors for each half-bridge. Moreover, the sensor reports over temperature warning level and an over temperature shutdown level. The TW status bit (output bit 0) will be set if the temperature exceeds the over temperature warning level, but the drivers will remain active. Once the IC temperature fall below the thermal warning threshold the TW flag is automatically clearly. If any of the individual thermal sensors detects a thermal shutdown level then the drivers on the offending half bridge are latched off. The TSD (PRE\_15) bit is set to capture a thermal shutdown event. A valid SPI command with SRR and temperature below the Tsd threshold are required to clear the latched fault. Since thermal warning precedes an over temperature shutdown, software polling of this bit will allow load control and possible prevention of over temperature shutdown conditions.

Figure 25. Thermal Warning and Shutdown Timing Diagram

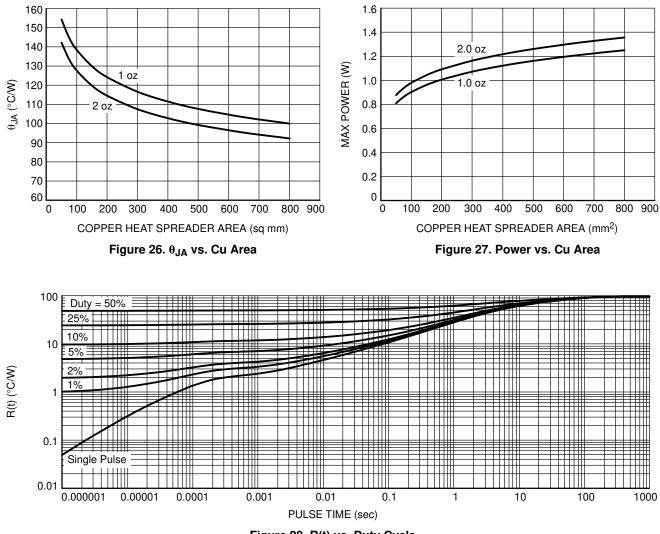

## **Thermal Performance**

Figure 28. R(t) vs. Duty Cycle

### Fault Handling

At an event of a driver latched off fault, the offending half-bridge driver is disabled and the half-bridge configuration is defaulted to zero (HBENx =0, HBCNFx = 0). The user is required to clear the output register fault and to resend the proper SPI frame to turn on the drivers. A driver

that is locked out during a fault conditions auto recovers to the previous programmed state when the fault is resolved. A latched fault flag on the serial output doesn't always translate an output latched off fault.

The summary of all fault conditions, the driver status and the clear requirements are provided in Table 5.

#### Table 5. FAULT SUMMARY

| Fault                                               | Fault Memory<br>Serial Output Bit | Driver<br>Condition During Fault                                                                       | Driver<br>Condition after Parameters<br>Within Specified Limits                                        | Output Register Clear<br>Requirement                                                            |

|-----------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Under Load<br>(ULDSC = 0)                           | Latched                           | Outputs Unchanged.<br>Allowed to turn/ remain on                                                       | Allowed to turn/remain on                                                                              | Valid SPI frame with<br>SRR set to 1                                                            |

| Under Load<br>(ULDSC = 1)                           | Latched (Note 6)                  | Offending Half–Bridge is<br>Latched Off (LS and HS)                                                    | Offending Half-Bridge is<br>Latched Off<br>(LS and HS)                                                 | Valid SPI frame with<br>SRR set to 1                                                            |

| Over Current                                        | Latched (Note 6)                  | Offending Output is<br>Latched Off<br>(LS and HS)                                                      | Offending Output is Latched<br>Off<br>(LS and HS)                                                      | Valid SPI frame with<br>SRR set to 1                                                            |

| Thermal Warning                                     | Non-Latched                       | Outputs Unchanged.<br>Allowed to turn/ remain on<br>provided that device is not<br>in thermal shutdown | Allowed to turn/remain on                                                                              | Temp below (thermal<br>warning temp –<br>hysteresis)                                            |

| Thermal Shutdown                                    | Latched (Note 6)                  | Offending Half–Bridge<br>Drivers are Latched Off<br>(LS and HS)                                        | Offending Half-Bridge is<br>Latched Off (LS and HS)                                                    | Valid SPI frame with<br>SRR set to 1.<br>Temperature blow<br>(thermal shutdown –<br>hysteresis) |

| VS Power Supply<br>Fail (Over–Voltage:<br>OVLO = 0) | Non-Latched                       | Outputs Unchanged.<br>Allowed to<br>turn/ remain on                                                    | Allowed to turn/remain on                                                                              | VS below (Over Voltage<br>Threshold – hysteresis)                                               |

| VS Power Supply<br>Fail (Over-Voltage:<br>OVLO = 1) | Non-Latched                       | All Drivers are Locked<br>Out.<br>Outx → High Z                                                        | Previous Half–Bridge status<br>and driver configuration is<br>maintained. Allowed to<br>turn/remain on | Auto Recovers if the VS<br>voltage is below<br>overvoltage threshold                            |

| VS Power Supply<br>Fail (Under<br>Voltage)          | Non-Latched                       | All Drivers are Locked<br>Out.<br>Outx → High Z                                                        | Previous Half–Bridge status<br>and driver configuration is<br>maintained. Allowed to<br>turn/remain on | Auto Recovers if the VS<br>voltage is above the<br>Under Voltage<br>threshold                   |

6. Latched conditions are cleared via the SPI SRR input bit = 1, by cycling the EN pin or with a power-on reset of V<sub>CC</sub>.