# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Bidirectional voltage-level translator for open-drain and push-pull applications

Rev. 5 — 19 February 2014

**Product data sheet**

### 1. General description

The NVT2003/04/06 is a family of bidirectional voltage level translators operational from 1.0 V to 3.6 V (V<sub>ref(A)</sub>) and 1.8 V to 5.5 V (V<sub>ref(B)</sub>), which allow bidirectional voltage translations between 1.0 V and 5 V without the need for a direction pin in open-drain or push-pull applications. Bit widths ranging from 3-bit to 6-bit are offered for level translation application with transmission speeds < 33 MHz for an open-drain system with a 50 pF capacitance and a pull-up of 197  $\Omega$ .

When the An or Bn port is LOW, the clamp is in the ON-state and a low resistance connection exists between the An and Bn ports. The low ON-state resistance ( $R_{on}$ ) of the switch allows connections to be made with minimal propagation delay. Assuming the higher voltage is on the Bn port when the Bn port is HIGH, the voltage on the An port is limited to the voltage set by VREFA. When the An port is HIGH, the Bn port is pulled to the drain pull-up supply voltage ( $V_{pu(D)}$ ) by the pull-up resistors. This functionality allows a seamless translation between higher and lower voltages selected by the user without the need for directional control.

When EN is HIGH, the translator switch is on, and the An I/O are connected to the Bn I/O, respectively, allowing bidirectional data flow between ports. When EN is LOW, the translator switch is off, and a high-impedance state exists between ports. The EN input circuit is designed to be supplied by  $V_{ref(B)}$ . To ensure the high-impedance state during power-up or power-down, EN must be LOW.

All channels have the same electrical characteristics and there is minimal deviation from one output to another in voltage or propagation delay. This is a benefit over discrete transistor voltage translation solutions, since the fabrication of the switch is symmetrical. The translator provides excellent ESD protection to lower voltage devices, and at the same time protects less ESD-resistant devices.

### 2. Features and benefits

- Provides bidirectional voltage translation with no direction pin

- Less than 1.5 ns maximum propagation delay

- Allows voltage level translation between:

- ◆ 1.0 V  $V_{ref(A)}$  and 1.8 V, 2.5 V, 3.3 V or 5 V  $V_{ref(B)}$

- 1.2 V V<sub>ref(A)</sub> and 1.8 V, 2.5 V, 3.3 V or 5 V V<sub>ref(B)</sub>

- 1.8 V V<sub>ref(A)</sub> and 3.3 V or 5 V V<sub>ref(B)</sub>

- 2.5 V V<sub>ref(A)</sub> and 5 V V<sub>ref(B)</sub>

- 3.3 V V<sub>ref(A)</sub> and 5 V V<sub>ref(B)</sub>

- Low 3.5 Ω ON-state connection between input and output ports provides less signal distortion

- 5 V tolerant I/O ports to support mixed-mode signal operation

- High-impedance An and Bn pins for EN = LOW

- Lock-up free operation

- Flow through pinout for ease of printed-circuit board trace routing

- ESD protection exceeds 3.5 kV HBM per JESD22-A114 and 1000 V CDM per JESD22-C101

- Packages offered: TSSOP10, HXSON12, DHVQFN16, HVQFN16, TSSOP16

## 3. Ordering information

#### Table 1.Ordering information

| Type number | Topside | Number  | Package  |                                                                                                                                           |          |

|-------------|---------|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------|----------|

|             | marking | of bits | Name     | Description                                                                                                                               | Version  |

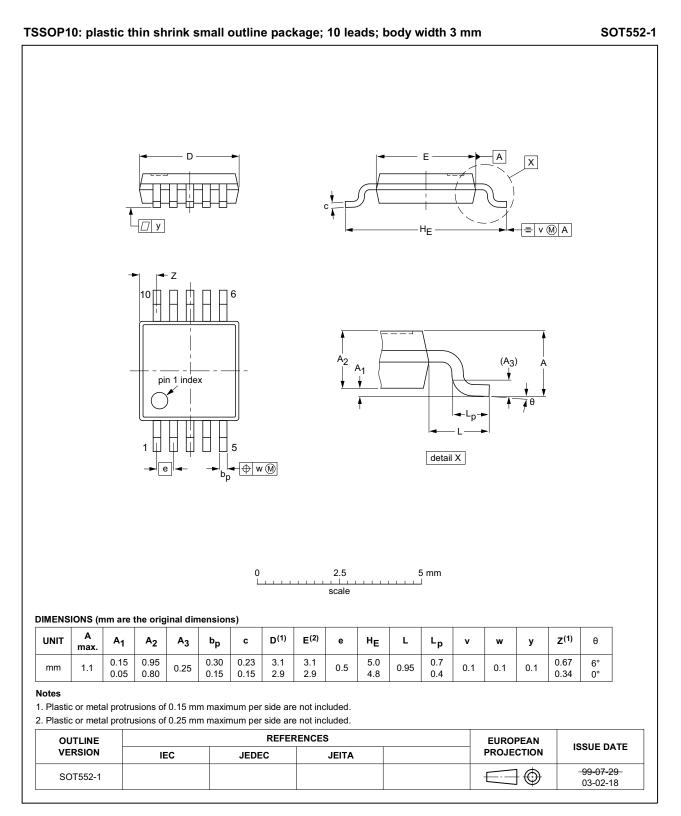

| NVT2003DP   | N2003   | 3       | TSSOP10  | plastic thin shrink small outline package; 10 leads;<br>body width 3 mm                                                                   | SOT552-1 |

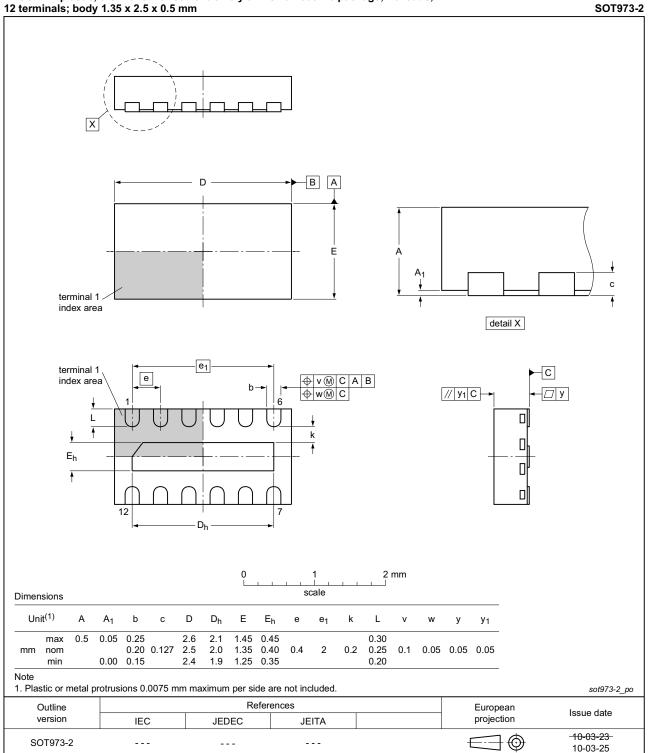

| NVT2004TL   | N4      | 4       | HXSON12  | plastic, thermal enhanced extremely thin small outline package; no leads; 12 terminals; body $1.35 \times 2.5 \times 0.5$ mm              | SOT973-2 |

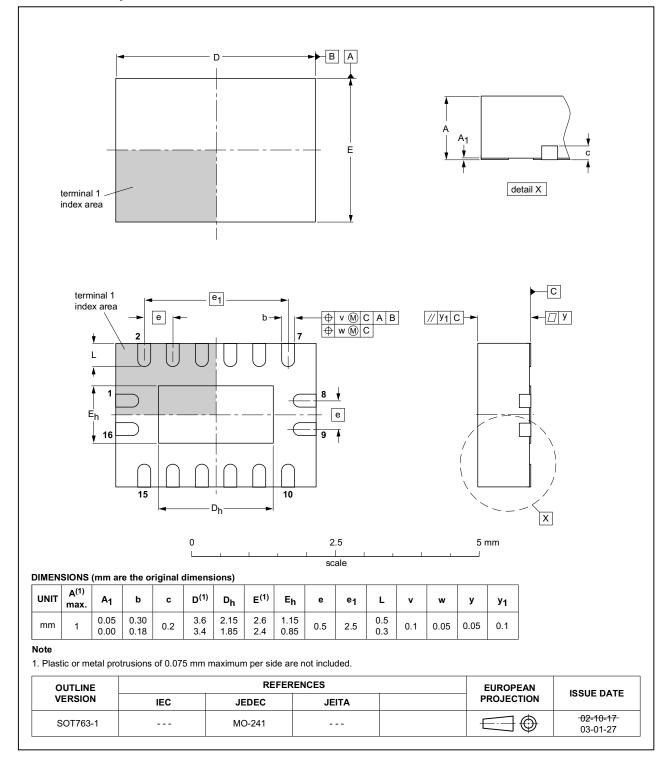

| NVT2006BQ   | N2006   | 6       | DHVQFN16 | plastic dual in-line compatible thermal enhanced very thin quad flat package; no leads;16 terminals; body $2.5 \times 3.5 \times 0.85$ mm | SOT763-1 |

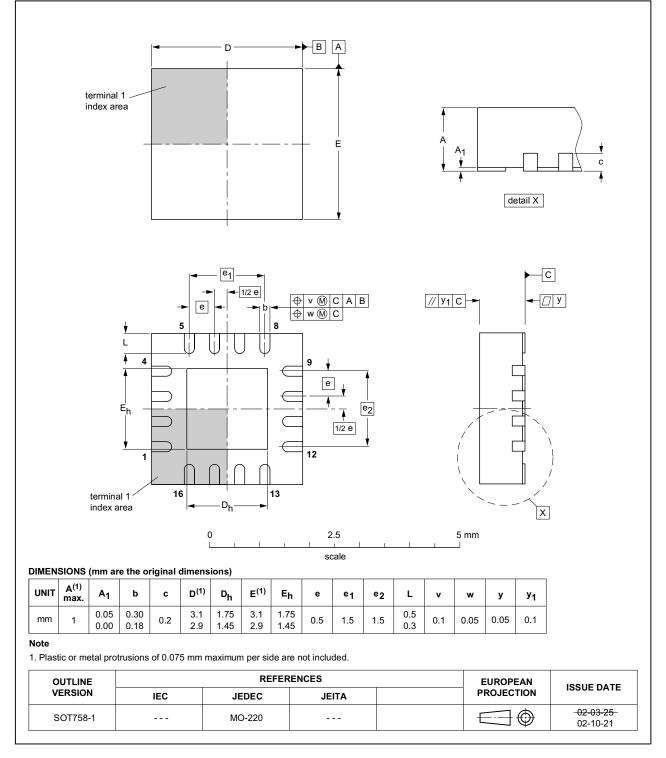

| NVT2006BS   | N06     | 6       | HVQFN16  | plastic thermal enhanced very thin quad flat package; no leads; 16 terminals; body $3 \times 3 \times 0.85$ mm                            | SOT758-1 |

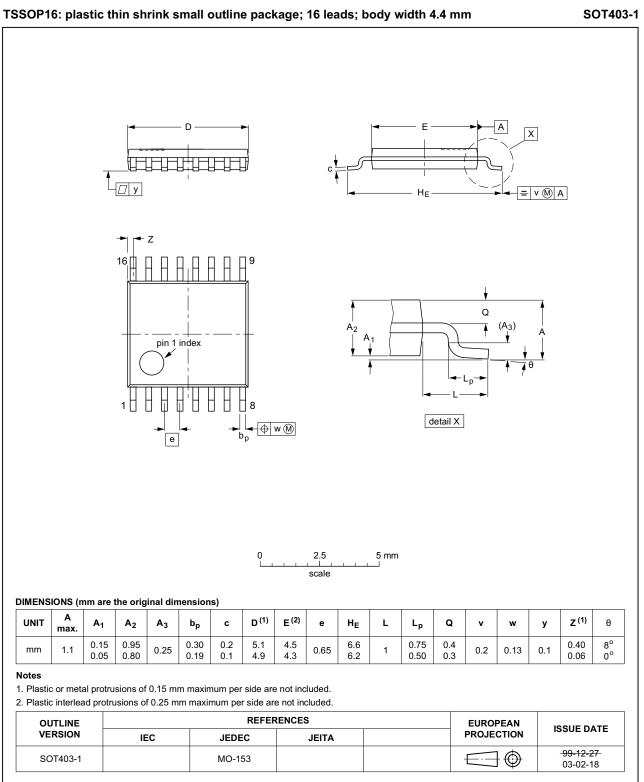

| NVT2006PW   | NVT2006 | 6       | TSSOP16  | plastic thin shrink small outline package; 16 leads; body width 4.4 mm                                                                    | SOT403-1 |

### 3.1 Ordering options

| Table 2. Ord | ering options            |          |                                      |                           |                                                    |

|--------------|--------------------------|----------|--------------------------------------|---------------------------|----------------------------------------------------|

| Type number  | Orderable<br>part number | Package  | Packing method                       | Minimum<br>order quantity | Temperature                                        |

| NVT2003DP    | NVT2003DP,118            | TSSOP10  | Reel 13" Q1/T1<br>*Standard mark SMD | 2500                      | $T_{amb} = -40 \ ^{\circ}C \ to \ +85 \ ^{\circ}C$ |

| NVT2004TL    | NVT2004TL,115            | HXSON12  | Reel 7" Q1/T1<br>*Standard mark SMD  | 4000                      | $T_{amb} = -40 \ ^{\circ}C \ to \ +85 \ ^{\circ}C$ |

| NVT2006BQ    | NVT2006BQ,115            | DHVQFN16 | Reel 7" Q1/T1<br>*Standard mark SMD  | 3000                      | $T_{amb} = -40 \ ^{\circ}C \ to \ +85 \ ^{\circ}C$ |

| NVT2006BS    | NVT2006BS,118            | HVQFN16  | Reel 13" Q1/T1<br>*Standard mark SMD | 6000                      | $T_{amb} = -40 \text{ °C to } +85 \text{ °C}$      |

| NVT2006PW    | NVT2006PW,118            | TSSOP16  | Reel 13" Q1/T1<br>*Standard mark SMD | 2500                      | $T_{amb}$ = -40 °C to +85 °C                       |

|              |                          |          |                                      |                           |                                                    |

NVT2003\_04\_06

Product data sheet

**Bidirectional voltage-level translator**

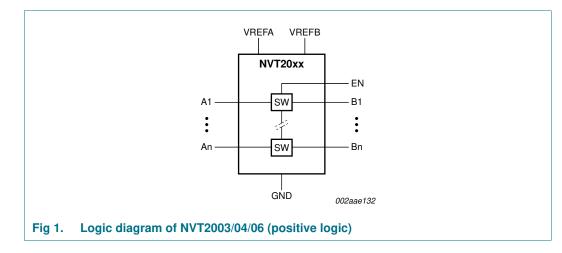

## 4. Functional diagram

### 5. Pinning information

5.1 Pinning

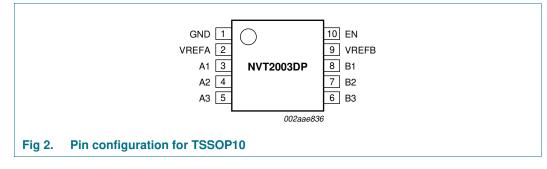

#### 5.1.1 3-bit in TSSOP10 package

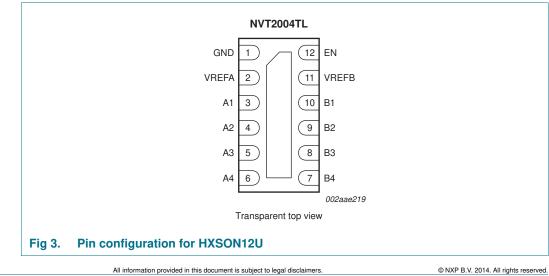

#### 5.1.2 4-bit in HXSON12 package

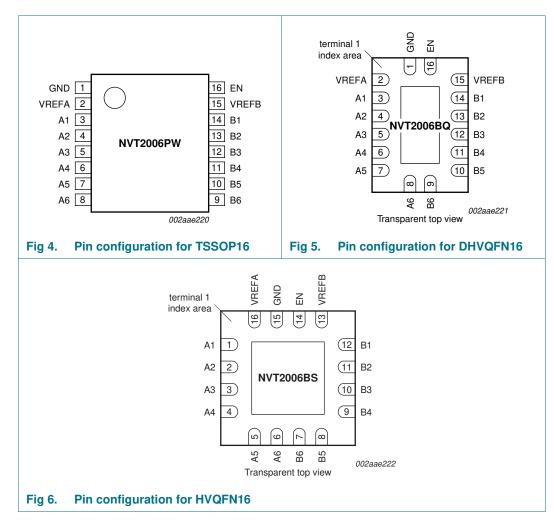

#### 5.1.3 6-bit in TSSOP16, DHVQFN16 and HVQFN16 packages

.

**Bidirectional voltage-level translator**

### 5.2 Pin description

| Symbol | Pin description<br>Pin |                          |                          |              | Description                                                               |

|--------|------------------------|--------------------------|--------------------------|--------------|---------------------------------------------------------------------------|

| Symbol | NVT2003DP[1]           | NVT2004TL <sup>[2]</sup> | NVT2006BQ,               | NVT2006BS[3] |                                                                           |

|        |                        |                          | NVT2006PW <sup>[3]</sup> |              |                                                                           |

| GND    | 1                      | 1                        | 1                        | 15           | ground (0 V)                                                              |

| VREFA  | 2                      | 2                        | 2                        | 16           | low-voltage side reference<br>supply voltage for An                       |

| A1     | 3                      | 3                        | 3                        | 1            | low-voltage side; connect to VREFA                                        |

| A2     | 4                      | 4                        | 4                        | 2            | through a pull-up resistor                                                |

| A3     | 5                      | 5                        | 5                        | 3            |                                                                           |

| A4     | -                      | 6                        | 6                        | 4            |                                                                           |

| A5     | -                      | -                        | 7                        | 5            |                                                                           |

| A6     | -                      | -                        | 8                        | 6            |                                                                           |

| B1     | 8                      | 10                       | 14                       | 12           | high-voltage side; connect to VREFB                                       |

| B2     | 7                      | 9                        | 13                       | 11           | through a pull-up resistor                                                |

| B3     | 6                      | 8                        | 12                       | 10           |                                                                           |

| B4     | -                      | 7                        | 11                       | 9            |                                                                           |

| B5     | -                      | -                        | 10                       | 8            |                                                                           |

| B6     | -                      | -                        | 9                        | 7            |                                                                           |

| VREFB  | 9                      | 11                       | 15                       | 13           | high-voltage side reference<br>supply voltage for Bn                      |

| EN     | 10                     | 12                       | 16                       | 14           | switch enable input; connect to VREFB and pull-up through a high resistor |

[1] 3-bit NVT2003 available in TSSOP10 package.

[2] 4-bit NVT2004 available in HXSON12 package.

[3] 6-bit NVT2006 available in TSSOP16, DHVQFN16, HVQFN16 packages.

## 6. Functional description

Refer to Figure 1 "Logic diagram of NVT2003/04/06 (positive logic)".

#### 6.1 Function table

Table 4. Function selection (example)

| əl. |

|-----|

|     |

| Input EN <sup>[1]</sup> | Function   |

|-------------------------|------------|

| Н                       | An = Bn    |

| L                       | disconnect |

EN is controlled by the V<sub>ref(B)</sub> logic levels and should be at least 1 V higher than V<sub>ref(A)</sub> for best translator operation.

**Bidirectional voltage-level translator**

## 7. Application design-in information

The NVT2003/04/06 can be used in level translation applications for interfacing devices or systems operating at different interface voltages with one another. The NVT2003/04/06 is ideal for use in applications where an open-drain driver is connected to the data I/Os. The NVT2003/04/06 can also be used in applications where a push-pull driver is connected to the data I/Os.

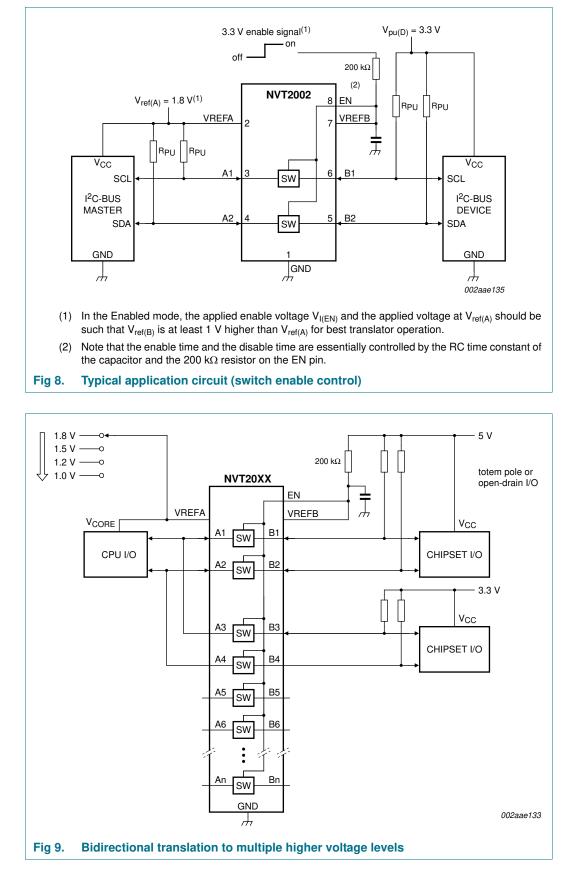

### 7.1 Enable and disable

The NVT20xx has an EN input that is used to disable the device by setting EN LOW, which places all I/Os in the high-impedance state.

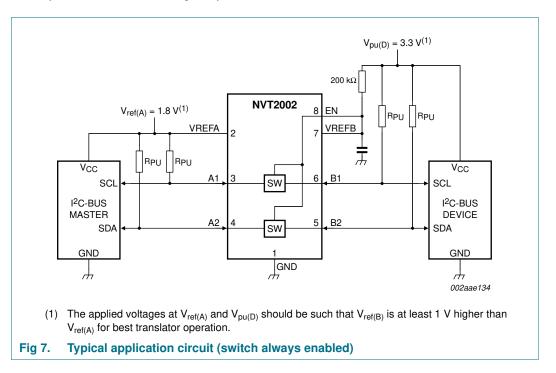

## Table 5.Application operating conditionsRefer to Figure 7.

|                       | <u></u>                 |                          |                    |                      |     |      |

|-----------------------|-------------------------|--------------------------|--------------------|----------------------|-----|------|

| Symbol                | Parameter               | Conditions               | Min                | Typ <mark>[1]</mark> | Max | Unit |

| V <sub>ref(B)</sub>   | reference voltage (B)   |                          | $V_{ref(A)} + 0.6$ | 2.1                  | 5   | V    |

| $V_{I(EN)}$           | input voltage on pin EN |                          | $V_{ref(A)} + 0.6$ | 2.1                  | 5   | V    |

| V <sub>ref(A)</sub>   | reference voltage (A)   |                          | 0                  | 1.5                  | 4.4 | V    |

| I <sub>sw(pass)</sub> | pass switch current     |                          | -                  | 14                   | -   | mA   |

| I <sub>ref</sub>      | reference current       | transistor               | -                  | 5                    | -   | μA   |

| T <sub>amb</sub>      | ambient temperature     | operating in<br>free-air | -40                | -                    | +85 | °C   |

[1] All typical values are at  $T_{amb} = 25 \ ^{\circ}C$ .

#### **Bidirectional voltage-level translator**

**Bidirectional voltage-level translator**

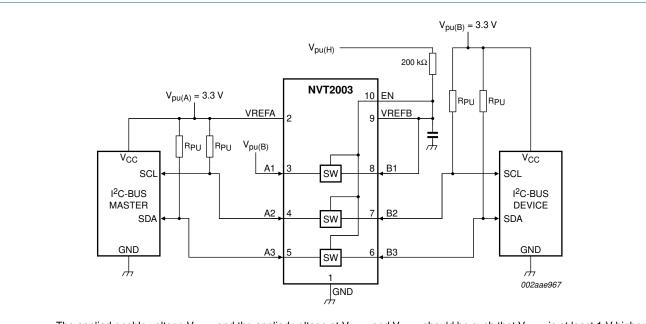

### 7.2 Bidirectional translation

For the bidirectional clamping configuration (higher voltage to lower voltage or lower voltage to higher voltage), the EN input must be connected to VREFB and both pins pulled to HIGH side  $V_{pu(D)}$  through a pull-up resistor (typically 200 k $\Omega$ ). This allows VREFB to regulate the EN input. A filter capacitor on VREFB is recommended. The master output driver can be totem pole or open-drain (pull-up resistors may be required) and the slave device output can be totem pole or open-drain (pull-up resistors are required to pull the Bn outputs to  $V_{pu(D)}$ ). However, if either output is totem-pole, data must be unidirectional or the outputs must be 3-stateable and be controlled by some direction-control mechanism to prevent HIGH-to-LOW contentions in either direction. If both outputs are open-drain, no direction control is needed.

The reference supply voltage (V<sub>ref(A)</sub>) is connected to the processor core power supply voltage. When VREFB is connected through a 200 k $\Omega$  resistor to a 3.3 V to 5.5 V V<sub>pu(D)</sub> power supply, and V<sub>ref(A)</sub> is set between 1.0 V and (V<sub>pu(D)</sub> – 1 V), the output of each An has a maximum output voltage equal to VREFA, and the output of each Bn has a maximum output voltage equal to V<sub>pu(D)</sub>.

## 7.3 Bidirectional level shifting between two different power domains nominally at the same potential

The less obvious application for the NVT2003 is for level shifting between two different power domains that are nominally at the same potential, such as a 3.3 V system where the line crosses power supply domains that under normal operation would be at 3.3 V, but one could be at 3.0 V and the other at 3.6 V, or one could be experiencing a power failure while the other domain is trying to operate. One of the NVT2003 three channel transistors is used as a second reference transistor with its B side connected to a voltage supply that is at least 1 V (and preferably 1.5 V) above the maximum possible for either V<sub>pu(A)</sub> or V<sub>pu(B)</sub>. Then if either pull-up voltage is at 0 V, the channels are disabled, and otherwise the channels are biased such that they turn OFF at the lower pull-up voltage, and if the two pull-up voltages are equal, the channel is biased such that it just turns OFF at the common pull-up voltage.

#### **Bidirectional voltage-level translator**

The applied enable voltage  $V_{pu(H)}$  and the applied voltage at  $V_{ref(A)}$  and  $V_{ref(B)}$  should be such that  $V_{ref(H)}$  is at least 1 V higher than  $V_{ref(A)}$  and  $V_{ref(B)}$  for best translator operation.

Fig 10. Bidirectional level shifting between two different power domains

### 7.4 How to size pull-up resistor value

Sizing the pull-up resistor on an open-drain bus is specific to the individual application and is dependent on the following driver characteristics:

- · The driver sink current

- The V<sub>OL</sub> of driver

- The  $V_{\text{IL}}$  of the driver

- Frequency of operation

The following tables can be used to estimate the pull-up resistor value in different use cases so that the minimum resistance for the pull-up resistor can be found.

<u>Table 6, Table 7</u> and <u>Table 8</u> contain suggested minimum values of pull-up resistors for the PCA9306 and NVT20xx devices with typical voltage translation levels and drive currents. The calculated values assume that both drive currents are the same.  $V_{OL} = V_{IL} = 0.1 \times V_{CC}$  and accounts for a  $\pm 5$  %  $V_{CC}$  tolerance of the supplies,  $\pm 1$  % resistor values. It should be noted that the resistor chosen in the final application should be equal to or larger than the values shown in <u>Table 6</u>, <u>Table 7</u> and <u>Table 8</u> to ensure that the pass voltage is less than 10 % of the  $V_{CC}$  voltage, and the external driver should be able to sink the total current from both pull-up resistors. When selecting the minimum resistor value in <u>Table 6</u>, <u>Table 7</u> or <u>Table 8</u>, the drive current strength that should be chosen should be the lowest drive current seen in the application and account for any drive strength current scaling with output voltage. For the GTL devices, the resistance table should be recalculated to account for the difference in ON resistance and bias voltage limitations between  $V_{CC(B)}$  and  $V_{CC(A)}$ .

#### **Bidirectional voltage-level translator**

| A-side |                            | B-side                     |                               |                                    |                                    |                                    |  |

|--------|----------------------------|----------------------------|-------------------------------|------------------------------------|------------------------------------|------------------------------------|--|

|        | 1.2 V                      | 1.5 V                      | 1.8 V                         | 2.5 V                              | 3.3 V                              | 5.0 V                              |  |

| 1.0 V  | R <sub>pu(A)</sub> = 750 Ω | R <sub>pu(A)</sub> = 845 Ω | R <sub>pu(A)</sub> = 976 Ω    | $R_{pu(A)} = none$                 | $R_{pu(A)} = none$                 | $R_{pu(A)} = none$                 |  |

|        | $R_{pu(B)} = 750 \ \Omega$ | $R_{pu(B)} = 845 \ \Omega$ | $R_{pu(B)} = 976 \ \Omega$    | $R_{pu(B)} = 887 \ \Omega$         | $R_{pu(B)} = 1.18 \ k\Omega$       | $R_{pu(B)} = 1.82 \text{ k}\Omega$ |  |

| 1.2 V  |                            | $R_{pu(A)} = 931 \ \Omega$ | $R_{pu(A)} = 1.02 \ k\Omega$  | $R_{pu(A)} = none$                 | $R_{pu(A)} = none$                 | $R_{pu(A)} = none$                 |  |

|        |                            | $R_{pu(B)} = 931 \ \Omega$ | $R_{pu(B)}$ = 1.02 k $\Omega$ | $R_{pu(B)} = 887 \ \Omega$         | $R_{pu(B)} = 1.18 \ k\Omega$       | $R_{pu(B)} = 1.82 \ k\Omega$       |  |

| 1.5 V  |                            |                            | $R_{pu(A)} = 1.1 \ k\Omega$   | $R_{pu(A)} = none$                 | $R_{pu(A)} = none$                 | $R_{pu(A)} = none$                 |  |

|        |                            |                            | $R_{pu(B)} = 1.1 \ k\Omega$   | $R_{pu(B)} = 866 \ \Omega$         | $R_{pu(B)} = 1.18 \text{ k}\Omega$ | $R_{pu(B)} = 1.78 \text{ k}\Omega$ |  |

| 1.8 V  |                            |                            |                               | $R_{pu(A)} = 1.47 \text{ k}\Omega$ | $R_{pu(A)} = none$                 | $R_{pu(A)} = none$                 |  |

|        |                            |                            |                               | $R_{pu(B)} = 1.47 \text{ k}\Omega$ | $R_{pu(B)} = 1.15 \text{ k}\Omega$ | $R_{pu(B)} = 1.78 \text{ k}\Omega$ |  |

| 2.5 V  |                            |                            |                               |                                    | $R_{pu(A)} = 1.96 \text{ k}\Omega$ | $R_{pu(A)} = none$                 |  |

|        |                            |                            |                               |                                    | $R_{pu(B)} = 1.96 \text{ k}\Omega$ | $R_{pu(B)} = 1.78 \ k\Omega$       |  |

| 3.3 V  |                            |                            |                               |                                    |                                    | $R_{pu(A)} = none$                 |  |

|        |                            |                            |                               |                                    |                                    | $R_{pu(B)} = 1.74 \text{ k}\Omega$ |  |

#### Table 6. Pull-up resistor minimum values, 3 mA driver sink current for PCA9306 and NVT20xx

| Table 7. Pull-up resistor minimum values, 10 mA driver sink current for PCA9306 and NV12000 | Table 7. | Pull-up resistor minimum values, 10 mA driver sink current for PCA9306 and NVT20xx |

|---------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------|

| A-side |                            |                            | B-e                        | side                       |                            |                            |

|--------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|

|        | 1.2 V                      | 1.5 V                      | 1.8 V                      | 2.5 V                      | 3.3 V                      | 5.0 V                      |

| 1.0 V  | $R_{pu(A)} = 221 \Omega$   | R <sub>pu(A)</sub> = 255 Ω | $R_{pu(A)} = 287 \ \Omega$ | $R_{pu(A)} = none$         | $R_{pu(A)} = none$         | $R_{pu(A)} = none$         |

|        | $R_{pu(B)} = 221 \ \Omega$ | $R_{pu(B)} = 255 \ \Omega$ | $R_{pu(B)} = 287 \ \Omega$ | $R_{pu(B)} = 267 \ \Omega$ | $R_{pu(B)} = 357 \ \Omega$ | $R_{pu(B)} = 549 \ \Omega$ |

| 1.2 V  |                            | $R_{pu(A)} = 274 \ \Omega$ | $R_{pu(A)} = 309 \ \Omega$ | $R_{pu(A)} = none$         | $R_{pu(A)} = none$         | $R_{pu(A)} = none$         |

|        |                            | $R_{pu(B)} = 274 \ \Omega$ | $R_{pu(B)} = 309 \ \Omega$ | $R_{pu(B)} = 267 \ \Omega$ | $R_{pu(B)} = 357 \ \Omega$ | $R_{pu(B)} = 549 \ \Omega$ |

| 1.5 V  |                            |                            | $R_{pu(A)} = 332 \ \Omega$ | $R_{pu(A)} = none$         | $R_{pu(A)} = none$         | $R_{pu(A)} = none$         |

|        |                            |                            | $R_{pu(B)} = 332 \ \Omega$ | $R_{pu(B)} = 261 \ \Omega$ | $R_{pu(B)} = 348 \ \Omega$ | $R_{pu(B)} = 536 \ \Omega$ |

| 1.8 V  |                            |                            |                            | $R_{pu(A)} = 442 \ \Omega$ | $R_{pu(A)} = none$         | $R_{pu(A)} = none$         |

|        |                            |                            |                            | $R_{pu(B)} = 442 \ \Omega$ | $R_{pu(B)} = 348 \ \Omega$ | $R_{pu(B)} = 536 \ \Omega$ |

| 2.5 V  |                            |                            |                            |                            | $R_{pu(A)} = 590 \ \Omega$ | $R_{pu(A)} = none$         |

|        |                            |                            |                            |                            | $R_{pu(B)} = 590 \ \Omega$ | $R_{pu(B)} = 523 \ \Omega$ |

| 3.3 V  |                            |                            |                            |                            |                            | $R_{pu(A)} = none$         |

|        |                            |                            |                            |                            |                            | $R_{pu(B)} = 523 \ \Omega$ |

**NXP Semiconductors**

#### **Bidirectional voltage-level translator**

|        |                            | ,                          |                            |                            |                            |                            |  |

|--------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|--|

| A-side |                            | B-side                     |                            |                            |                            |                            |  |

|        | 1.2 V                      | 1.5 V                      | 1.8 V                      | 2.5 V                      | 3.3 V                      | 5.0 V                      |  |

| 1.0 V  | R <sub>pu(A)</sub> = 147 Ω | $R_{pu(A)} = 169 \ \Omega$ | R <sub>pu(A)</sub> = 191 Ω | $R_{pu(A)} = none$         | $R_{pu(A)} = none$         | $R_{pu(A)} = none$         |  |

|        | $R_{pu(B)} = 147 \ \Omega$ | $R_{pu(B)} = 169 \ \Omega$ | $R_{pu(B)} = 191 \ \Omega$ | $R_{pu(B)} = 178 \ \Omega$ | $R_{pu(B)} = 237 \ \Omega$ | $R_{pu(B)} = 365 \ \Omega$ |  |

| 1.2 V  |                            | $R_{pu(A)} = 182 \ \Omega$ | $R_{pu(A)} = 205 \ \Omega$ | $R_{pu(A)} = none$         | $R_{pu(A)} = none$         | $R_{pu(A)} = none$         |  |

|        |                            | $R_{pu(B)} = 182 \ \Omega$ | $R_{pu(B)} = 205 \ \Omega$ | $R_{pu(B)} = 178 \ \Omega$ | $R_{pu(B)} = 237 \ \Omega$ | $R_{pu(B)} = 365 \ \Omega$ |  |

| 1.5 V  |                            |                            | $R_{pu(A)} = 221 \ \Omega$ | $R_{pu(A)} = none$         | $R_{pu(A)} = none$         | $R_{pu(A)} = none$         |  |

|        |                            |                            | $R_{pu(B)} = 221 \ \Omega$ | $R_{pu(B)} = 174 \ \Omega$ | $R_{pu(B)} = 232 \ \Omega$ | $R_{pu(B)} = 357 \ \Omega$ |  |

| 1.8 V  |                            |                            |                            | $R_{pu(A)} = 294 \ \Omega$ | $R_{pu(A)} = none$         | $R_{pu(A)} = none$         |  |

|        |                            |                            |                            | $R_{pu(B)} = 294 \ \Omega$ | $R_{pu(B)} = 232 \ \Omega$ | $R_{pu(B)} = 357 \ \Omega$ |  |

| 2.5 V  |                            |                            |                            |                            | $R_{pu(A)} = 392 \ \Omega$ | $R_{pu(A)} = none$         |  |

|        |                            |                            |                            |                            | $R_{pu(B)} = 392 \ \Omega$ | $R_{pu(B)} = 357 \ \Omega$ |  |

| 3.3 V  |                            |                            |                            |                            |                            | $R_{pu(A)} = none$         |  |

|        |                            |                            |                            |                            |                            | $R_{pu(B)} = 348 \Omega$   |  |

#### Table 8. Pull-up resistor minimum values, 15 mA driver sink current for PCA9306 and NVT20xx

**NXP Semiconductors**

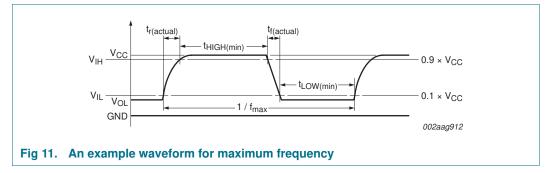

#### 7.5 How to design for maximum frequency operation

The maximum frequency is limited by the minimum pulse width LOW and HIGH as well as rise time and fall time. See Equation 1 as an example of the maximum frequency. The rise and fall times are shown in Figure 11.

$$f_{max} = \frac{1}{t_{LOW(min)} + t_{HIGH(min)} + t_{r(actual)} + t_{f(actual)}}$$

(1)

The rise and fall times are dependent upon translation voltages, the drive strength, the total node capacitance ( $C_{L(tot)}$ ) and the pull-up resistors ( $R_{PU}$ ) that are present on the bus. The node capacitance is the addition of the PCB trace capacitance and the device capacitance that exists on the bus. Because of the dependency of the external components, PCB layout and the different device operating states the calculation of rise and fall times is complex and has several inflection points along the curve.

The main component of the rise and fall times is the RC time constant of the bus line when the device is in its two primary operating states: when device is in the ON state and it is low-impedance, the other is when the device is OFF isolating the A-side from the B-side.

A description of the fall time applied to either An or Bn output going from HIGH to LOW is as follows. Whichever side is asserted first, the B-side down must discharge to the  $V_{CC(A)}$  voltage. The time is determined by the pull-up resistor, pull-down driver strength and the

NVT2003 04 06

#### **Bidirectional voltage-level translator**

capacitance. As the level moves below the V<sub>CC(A)</sub> voltage, the channel resistance drops so that both A and B sides equal. The capacitance on both sides is connected to form the total capacitance and the pull-up resistors on both sides combine to the parallel equivalent resistance. The R<sub>on</sub> of the device is small compared to the pull-up resistor values, so its effect on the pull-up resistance can be neglected and the fall is determined by the driver pulling the combined capacitance and pull-up resistor currents. An estimation of the actual fall time seen by the device is equal to the time it takes for the B-side to fall to the V<sub>CC(A)</sub> voltage and the time it takes for both sides to fall from the V<sub>CC(A)</sub> voltage to the V<sub>IL</sub> level.

A description of the rise time applied to either An or Bn output going from LOW to HIGH is as follows. When the signal level is LOW, the R<sub>on</sub> is at its minimum, so the A and B sides are essentially one node. They will rise together with an RC time constant that is the sum of all the capacitance from both sides and the parallel of the resistance from both sides. As the signal approaches the V<sub>CC(A)</sub> voltage, the channel resistance goes up and the waveforms separate, with the B side finishing its rise with the RC time constant of the B side. The rise to V<sub>CC(A)</sub> is essentially the same for both sides.

There are some basic guidelines to follow that will help maximize the performance of the device:

- Keep trace length to a minimum by placing the NVT device close to the processor.

- The signal round trip time on trace should be shorter than the rise or fall time of signal to reduce reflections.

- The faster the edge of the signal, the higher the chance for ringing.

- The higher drive strength controlled by the pull-up resistor (up to 15 mA), the higher the frequency the device can use.

The system designer must design the pull-up resistor value based on external current drive strength and limit the node capacitance (minimize the wire, stub, connector and trace length) to get the desired operation frequency result.

### 8. Limiting values

#### Table 9. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Over operating free-air temperature range.

| Symbol              | Parameter                      | Conditions           | Min                 | Max  | Unit |

|---------------------|--------------------------------|----------------------|---------------------|------|------|

| V <sub>ref(A)</sub> | reference voltage (A)          |                      | -0.5                | +6   | V    |

| V <sub>ref(B)</sub> | reference voltage (B)          |                      | -0.5                | +6   | V    |

| VI                  | input voltage                  |                      | -0.5 <sup>[1]</sup> | +6   | V    |

| V <sub>I/O</sub>    | voltage on an input/output pin |                      | -0.5 <sup>[1]</sup> | +6   | V    |

| I <sub>ch</sub>     | channel current (DC)           |                      | -                   | 128  | mA   |

| I <sub>IK</sub>     | input clamping current         | V <sub>1</sub> < 0 V | -50                 | -    | mA   |

| I <sub>OK</sub>     | output clamping current        |                      | [2] -50             | +50  | mA   |

| T <sub>stg</sub>    | storage temperature            |                      | -65                 | +150 | °C   |

[1] The input and input/output negative voltage ratings may be exceeded if the input and input/output clamp current ratings are observed.

[2] Low duty cycle pulses, not DC because of heating.

## 9. Recommended operating conditions

| Table 10.             | Operating conditions           |                       |     |     |     |      |

|-----------------------|--------------------------------|-----------------------|-----|-----|-----|------|

| Symbol                | Parameter                      | Conditions            |     | Min | Max | Unit |

| V <sub>I/O</sub>      | voltage on an input/output pin | An, Bn                |     | 0   | 5.5 | V    |

| V <sub>ref(A)</sub>   | reference voltage (A)          | VREFA                 | [1] | 0   | 5.4 | V    |

| V <sub>ref(B)</sub>   | reference voltage (B)          | VREFB                 | [1] | 0   | 5.5 | V    |

| V <sub>I(EN)</sub>    | input voltage on pin EN        |                       |     | 0   | 5.5 | V    |

| I <sub>sw(pass)</sub> | pass switch current            |                       |     | -   | 64  | mA   |

| T <sub>amb</sub>      | ambient temperature            | operating in free-air |     | -40 | +85 | °C   |

$\label{eq:Vref} [1] \quad V_{ref(A)} \leq V_{ref(B)} - 1 \ V \ \text{for best results in level shifting applications.}$

### **10. Static characteristics**

#### Table 11. Static characteristics

$T_{amb} = -40 \ ^{\circ}C \ to +85 \ ^{\circ}C$ , unless otherwise specified.

| Symbol              | Parameter                          | Conditions                                                                     | Min                | Typ <mark>[1]</mark> | Мах               | Unit |

|---------------------|------------------------------------|--------------------------------------------------------------------------------|--------------------|----------------------|-------------------|------|

| V <sub>IK</sub>     | input clamping voltage             | $I_I = -18 \text{ mA}; V_{I(EN)} = 0 \text{ V}$                                | -                  | -                    | -1.2              | V    |

| I <sub>IH</sub>     | HIGH-level input current           | $V_{I} = 5 V; V_{I(EN)} = 0 V$                                                 | -                  | -                    | 5                 | μA   |

| $C_{i(\text{EN})}$  | input capacitance on pin EN        | $V_I = 3 V \text{ or } 0 V$                                                    | -                  | 12                   | -                 | pF   |

| $C_{io(off)}$       | off-state input/output capacitance | An, Bn; V <sub>O</sub> = 3 V or 0 V;<br>V <sub>I(EN)</sub> = 0 V               | -                  | 5                    | 7                 | pF   |

| C <sub>io(on)</sub> | on-state input/output capacitance  | An, Bn; V <sub>O</sub> = 3 V or 0 V;<br>V <sub>I(EN)</sub> = 3 V               | -                  | 11.5                 | 13 <mark>2</mark> | pF   |

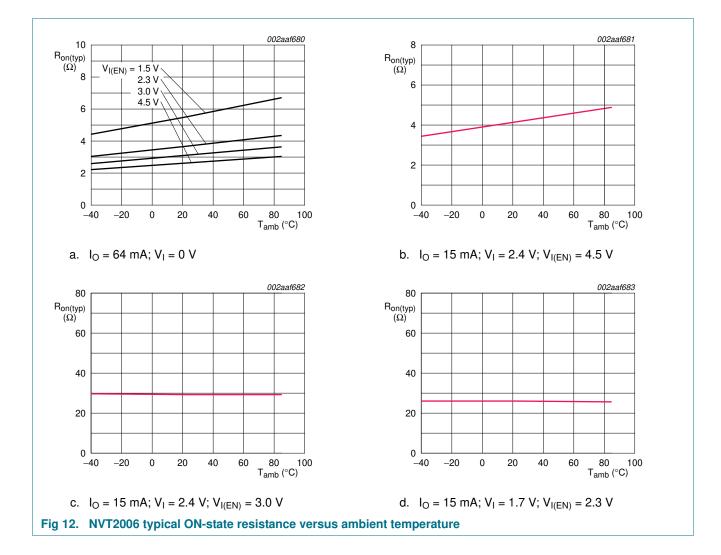

| R <sub>on</sub>     | ON-state resistance                | An, Bn; V_I = 0 V; I_O = 64 mA; V_{I(EN)} = 4.5 V                              | <u>[3][4][5]</u> 1 | 2.4                  | 5.0               | Ω    |

|                     |                                    | $V_{I} = 2.4 \text{ V}; I_{O} = 15 \text{ mA};$<br>$V_{I(EN)} = 4.5 \text{ V}$ | <u>[3][4]</u> _    | 4.8                  | 7.5               | Ω    |

[1] All typical values are at  $T_{amb} = 25 \ ^{\circ}C$ .

[2] Not production tested, maximum value based on characterization data of typical parts.

[3] Measured by the voltage drop between the An and Bn terminals at the indicated current through the switch. ON-state resistance is determined by the lowest voltage of the two terminals.

[4] See curves in Figure 12 for typical temperature and  $V_{I(EN)}$  behavior.

[5] Guaranteed by design.

#### **Bidirectional voltage-level translator**

14 of 33

Max

Unit

**Bidirectional voltage-level translator**

### **11. Dynamic characteristics**

### 11.1 Open-drain drivers

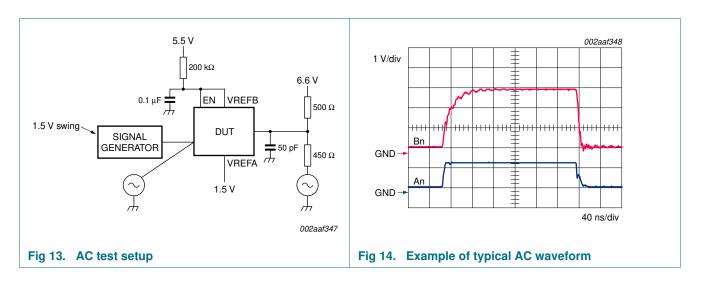

**Table 12.** Dynamic characteristics for open-drain drivers  $T_{amb} = -40 \ ^{\circ}C \ to \ +85 \ ^{\circ}C; \ V_{U(EN)} = V_{ref(B)}; \ unless \ otherwise \ specified$

|        | ,         | $E_{EN} = V_{ref(B)}$ ; unless otherwise speci- |     |     |

|--------|-----------|-------------------------------------------------|-----|-----|

| Symbol | Parameter | Conditions                                      | Min | Тур |

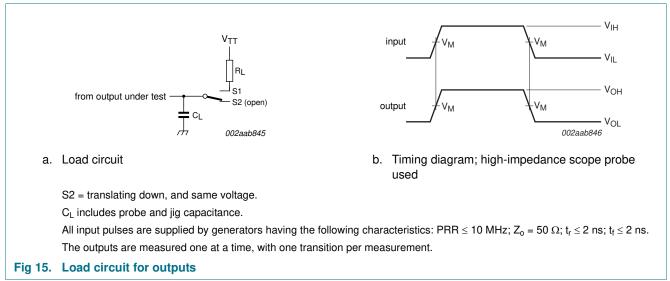

| Figure 15        |                               |                                   |     |                                    |    |  |

|------------------|-------------------------------|-----------------------------------|-----|------------------------------------|----|--|

| t <sub>PLH</sub> | LOW to HIGH propagation delay | from (input) Bn<br>to (output) An | [1] | $R_{on} \times (C_L + C_{io(on)})$ | ns |  |

| t <sub>PHL</sub> | HIGH to LOW propagation delay | from (input) Bn<br>to (output) An |     | $R_{on} \times (C_L + C_{io(on)})$ | ns |  |

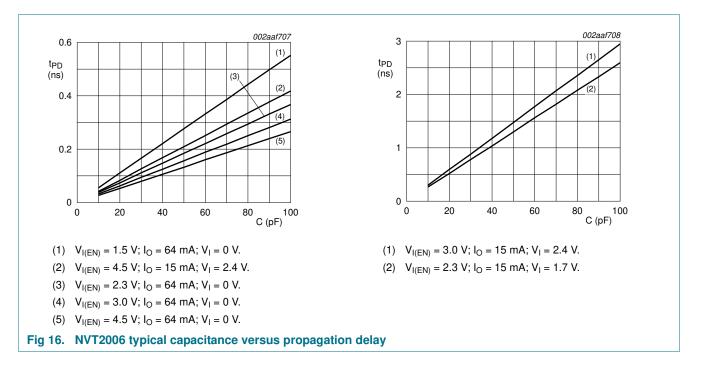

[1] See graphs based on  $R_{on}$  typical and  $C_{io(on)} + C_L = 50$  pF.

### **12. Performance curves**

$t_{PLH}$  up-translation is typically dominated by the RC time constant, i.e.,  $C_{L(tot)} \times R_{PU} = 50 \text{ pF} \times 197 \Omega = 9.85 \text{ ns}$ , but the  $R_{on} \times C_{L(tot)} = 50 \text{ pF} \times 5 \Omega = 0.250 \text{ ns}$ .

$t_{PHL}$  is typically dominated by the external pull-down driver +  $R_{on}$ , which is typically small compared to the  $t_{PLH}$  in an up-translation case.

Enable/disable times are dominated by the RC time constant on the EN pin since the transistor turn off is on the order of ns, but the enable RC is on the order of ms.

Fall time is dominated by the external pull-down driver with only a slight  $\ensuremath{\mathsf{R}_{\text{on}}}$  addition.

Rise time is dominated by the  $R_{PU} \times C_L$ .

Skew time within the part is virtually non-existent, dominated by the difference in bond wire lengths, which is typically small compared to the board-level routing differences.

Maximum data rate is dominated by the system capacitance and pull-up resistors.

### 13. Package outline

#### Fig 17. Package outline SOT552-1 (TSSOP10)

All information provided in this document is subject to legal disclaimers.

**Bidirectional voltage-level translator**

HXSON12: plastic, thermal enhanced extremely thin small outline package; no leads; 12 terminals; body 1.35 x 2.5 x 0.5 mm

#### Fig 18. Package outline SOT973-2 (HXSON12)

All information provided in this document is subject to legal disclaimers.

DHVQFN16: plastic dual in-line compatible thermal enhanced very thin quad flat package; no leads; 16 terminals; body 2.5 x 3.5 x 0.85 mm SOT763-1

#### Fig 19. Package outline SOT763-1 (DHVQFN16)

#### HVQFN16: plastic thermal enhanced very thin quad flat package; no leads; 16 terminals; body 3 x 3 x 0.85 mm

SOT758-1

#### Fig 20. Package outline SOT758-1 (HVQFN16)

All information provided in this document is subject to legal disclaimers.

**Bidirectional voltage-level translator**

Fig 21. Package outline SOT403-1 (TSSOP16)

All information provided in this document is subject to legal disclaimers.

#### **Bidirectional voltage-level translator**

### 14. Soldering of SMD packages

This text provides a very brief insight into a complex technology. A more in-depth account of soldering ICs can be found in Application Note *AN10365 "Surface mount reflow soldering description"*.

#### 14.1 Introduction to soldering

Soldering is one of the most common methods through which packages are attached to Printed Circuit Boards (PCBs), to form electrical circuits. The soldered joint provides both the mechanical and the electrical connection. There is no single soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and Surface Mount Devices (SMDs) are mixed on one printed wiring board; however, it is not suitable for fine pitch SMDs. Reflow soldering is ideal for the small pitches and high densities that come with increased miniaturization.

### 14.2 Wave and reflow soldering

Wave soldering is a joining technology in which the joints are made by solder coming from a standing wave of liquid solder. The wave soldering process is suitable for the following:

- Through-hole components

- Leaded or leadless SMDs, which are glued to the surface of the printed circuit board

Not all SMDs can be wave soldered. Packages with solder balls, and some leadless packages which have solder lands underneath the body, cannot be wave soldered. Also, leaded SMDs with leads having a pitch smaller than ~0.6 mm cannot be wave soldered, due to an increased probability of bridging.

The reflow soldering process involves applying solder paste to a board, followed by component placement and exposure to a temperature profile. Leaded packages, packages with solder balls, and leadless packages are all reflow solderable.

Key characteristics in both wave and reflow soldering are:

- · Board specifications, including the board finish, solder masks and vias

- · Package footprints, including solder thieves and orientation

- · The moisture sensitivity level of the packages

- Package placement

- Inspection and repair

- Lead-free soldering versus SnPb soldering

#### 14.3 Wave soldering

Key characteristics in wave soldering are:

- Process issues, such as application of adhesive and flux, clinching of leads, board transport, the solder wave parameters, and the time during which components are exposed to the wave

- · Solder bath specifications, including temperature and impurities

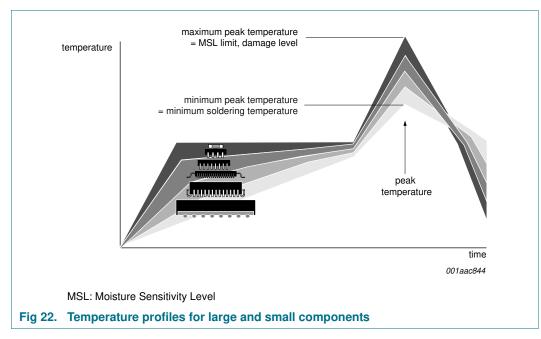

#### 14.4 Reflow soldering

Key characteristics in reflow soldering are:

- Lead-free versus SnPb soldering; note that a lead-free reflow process usually leads to higher minimum peak temperatures (see <u>Figure 22</u>) than a SnPb process, thus reducing the process window

- Solder paste printing issues including smearing, release, and adjusting the process window for a mix of large and small components on one board

- Reflow temperature profile; this profile includes preheat, reflow (in which the board is heated to the peak temperature) and cooling down. It is imperative that the peak temperature is high enough for the solder to make reliable solder joints (a solder paste characteristic). In addition, the peak temperature must be low enough that the packages and/or boards are not damaged. The peak temperature of the package depends on package thickness and volume and is classified in accordance with Table 13 and 14

#### Table 13. SnPb eutectic process (from J-STD-020D)

| Package thickness (mm) | Package reflow temperature (°C) |       |  |

|------------------------|---------------------------------|-------|--|

|                        | Volume (mm <sup>3</sup> )       |       |  |

|                        | < 350                           | ≥ 350 |  |

| < 2.5                  | 235                             | 220   |  |

| ≥ 2.5                  | 220                             | 220   |  |

#### Table 14. Lead-free process (from J-STD-020D)

| Package thickness (mm) | Package reflow temperature (°C) |             |        |  |

|------------------------|---------------------------------|-------------|--------|--|

|                        | Volume (mm <sup>3</sup> )       |             |        |  |

|                        | < 350                           | 350 to 2000 | > 2000 |  |

| < 1.6                  | 260                             | 260         | 260    |  |

| 1.6 to 2.5             | 260                             | 250         | 245    |  |

| > 2.5                  | 250                             | 245         | 245    |  |

Moisture sensitivity precautions, as indicated on the packing, must be respected at all times.

Studies have shown that small packages reach higher temperatures during reflow soldering, see Figure 22.

**Bidirectional voltage-level translator**

For further information on temperature profiles, refer to Application Note *AN10365 "Surface mount reflow soldering description"*.

NVT2003\_04\_06

Product data sheet

**Bidirectional voltage-level translator**

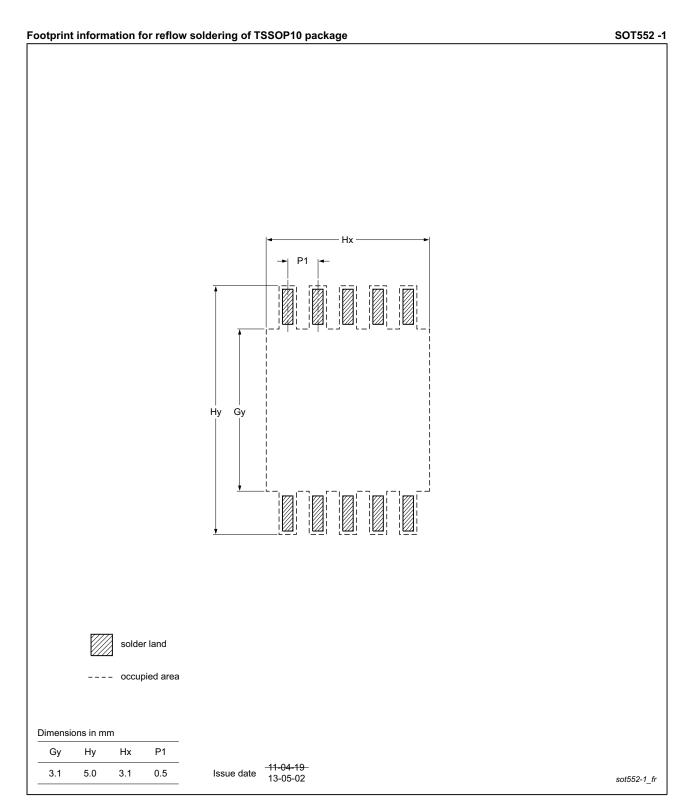

## 15. Soldering: PCB footprints

#### Fig 23. PCB footprint for SOT552-1 (TSSOP10); reflow soldering

All information provided in this document is subject to legal disclaimers.