Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# DUAL SYNCHRONOUS PWM CONTROLLER WITH NMOS LDO **CONTROLLER & 5V BIAS REGULATOR**

PRELIMINARY DATA SHEET

Pb Free Product

# **DESCRIPTION**

The NX2601 controller IC is a triple controller with a dual channel synchronous Buck controller IC and an LDO controller designed for multiple converters such as PCIe graphic card applications .The two synchronous PWM controllers are 180 degree out of phase which reduces the input ripple current, allowing to reduce the # of input capacitors. Another main feature of the part is that it can operate from single 12V supply while maintaining a regulated 5V supply for the biasing and the internal drivers. Other features of NX2601 are: programmable frequency from 200kHz to 1MHz, independent digital soft start and enable pins for each controller which allows for different power sequencing, Adaptive driver provides optimized ef- ■ ficiency while maintain sufficient deadband, Vcc undervoltage lock out and current limiting using an Rdson of the external MOSFET with HICCUP feature.

### **FEATURES**

- Two channel PWM with out of phase operation

- Individual digital soft start for two PWM output and LDO controller

- Bus voltage operation from 2V to 25V

- Hiccup Current limit by sensing Rdson of MOSFET

- Adjustable frequency up to 1Mhz per channel

- Adaptive deadband time

- Three enable pin available allows for independent power sequencing

- MLPQ-32L package offers small size

- Pb-free and RoHS compliant

### APPLICATIONS

- PCI Graphic Card on board converters

- Vddq Supply in mother board applications

- On board DC to DC such as 12V to 3.3V, 2.5V or 1.8V

- FPGA and Set Top Box Applications

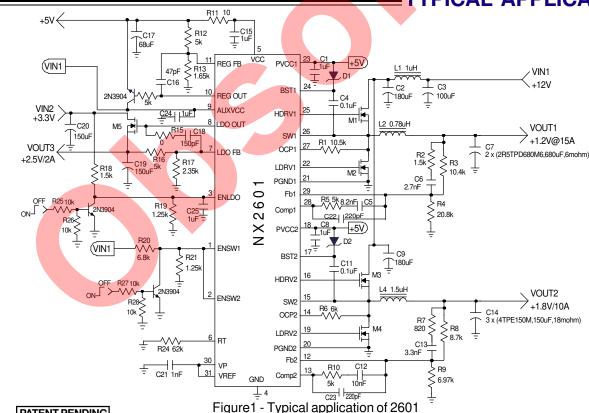

## TYPICAL APPLICATION

PATENT PENDING

# ORDERING INFORMATION

| Device     | Temperature | Package  | Frequency      | Pb-Free |

|------------|-------------|----------|----------------|---------|

| NX2601CMTR | 0 to 70°C   | MLPQ-32L | 200kHz to 1MHz | Yes     |

# **ABSOLUTE MAXIMUM RATINGS**

| Vcc,PVcc & BST to SW voltage         | 6.5V             |

|--------------------------------------|------------------|

| BST Voltage                          | 35V              |

| SW                                   | 5V(Note1) to 35V |

| AUXVCC                               | 35V              |

| All other pins                       | GND to Vcc+0.3V  |

| Storage Temperature Range            | 65°C to 150°C    |

| Operating Junction Temperature Range | 40°C to 125°C    |

CAUTION: Stresses above those listed in "ABSOLUTE MAXIMUM RATINGS", may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

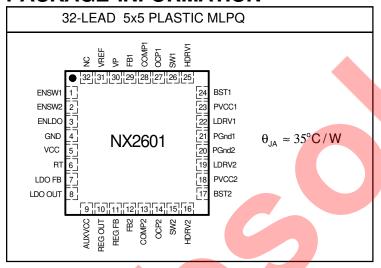

# **PACKAGE INFORMATION**

# **ELECTRICAL SPECIFICATIONS**

Unless otherwise specified, these specifications apply over Vcc = 5V,  $V_{BST}$ - $V_{SW}$ =5V, ENSW1=HIGH, ENSW2=HIGH, ENLDO=HIGH, and  $T_A$  = 0 to 70°C. Typical values refer to  $T_A$  = 25°C. Low duty cycle pulse testing is used which keeps junction and case temperatures equal to the ambient temperature.

| PARAMETER                              | SYM                   | TEST CONDITION             | MIN | TYP   | MAX | UNITS |

|----------------------------------------|-----------------------|----------------------------|-----|-------|-----|-------|

| Reference Voltage                      |                       |                            |     |       |     |       |

| FB Voltage                             | $V_{REF}$             | 4.5 < Vcc < 5.5            |     | 0.800 |     | V     |

| FB Voltage Line Regulation             |                       |                            |     | 0.4   |     | %     |

| Vcc Supply Voltage                     |                       |                            |     |       |     |       |

| Vcc Voltage Range                      | V <sub>cc</sub>       |                            | 4.5 | 5.0   | 5.5 | V     |

| Vcc Static Supply Current              | I <sub>CC_STA</sub>   | Outputs not switching      |     | 2.0   |     | mA    |

| Vcc Dynamic Supply                     | I <sub>CC_DYN</sub>   | Freq=600kHz,               |     | 8     |     | mA    |

| Current                                |                       | C <sub>LOAD</sub> = 3300pF |     |       |     |       |

| V <sub>BST</sub> Voltage Range         | $V_{_{\mathrm{BST}}}$ |                            | 4.5 | 5.0   | 5.5 | V     |

| V <sub>BST</sub> Static Supply Current | I <sub>BST_STA</sub>  | Outputs not switching      |     | 2.0   |     | mA    |

| V <sub>BST</sub> Dynamic Supply        | I <sub>BST_DYN</sub>  | Freq = 600KHz,             |     | TBD   |     | mA    |

| Current                                |                       | $C_{LOAD} = 3300pF$        |     |       |     |       |

| PARAMETER                             | SYM                    | TEST CONDITION                                         | MIN  | TYP  | MAX | UNITS |

|---------------------------------------|------------------------|--------------------------------------------------------|------|------|-----|-------|

| Under Voltage Lockout                 |                        |                                                        |      |      |     |       |

| UVLO Threshold - Vcc                  | V <sub>CC_UVLO</sub>   | Supply Ramping Up                                      |      | 4    |     | V     |

| UVLO Hysteresis - Vcc                 | V <sub>CC_HYST</sub>   | Supply Ramping Down                                    |      | 0.2  |     | V     |

| UVLO Threshold - V <sub>AUXVcc</sub>  | V <sub>AUX UVLO</sub>  |                                                        |      | 7    |     | V     |

| UVLO Hysteresis - V <sub>AUXVcc</sub> | V <sub>AUX HYST</sub>  | Supply Ramping Down                                    |      | 0.7  |     | V     |

| Error Amplifiers                      | AUX HYSI               | cappi) i amping zowii                                  |      | 0.7  |     |       |

| Open Loop Gain                        |                        |                                                        |      | 65   |     | dB    |

| Input Bias Current                    |                        |                                                        |      | 0.3  |     | uA    |

| Input Offset Voltage                  |                        |                                                        |      | 0.0  |     | mV    |

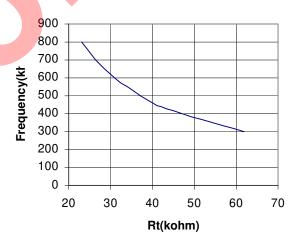

| Oscillator                            |                        |                                                        |      |      |     |       |

| Frequency                             | F <sub>s</sub>         | Rt=30k,measured at the output drive                    |      | 600  |     | KHz   |

| Ramp Amplitude                        | $V_{\text{RAMP}}$      |                                                        |      | 1    |     | V     |

| EN & SS                               |                        |                                                        |      |      |     |       |

| Soft Start Time                       | $T_{ss}$               | Fs=600KHz                                              |      | 3.41 |     | mS    |

| Enable Threshold Voltage              |                        |                                                        |      | 1.25 |     | V     |

| Enable Hysterises                     |                        | Enable ramp up                                         |      | 100  |     | mV    |

| LDO Controller                        |                        |                                                        |      |      |     |       |

| LDO FB Voltage                        |                        | LDOOUT=LDOFB                                           |      | 0.8  |     | V     |

| FB Pin Bias Current                   |                        |                                                        | -0.2 | 0    |     | μΑ    |

| LDO_out Output Voltage High           |                        | AUXVCC=24V,LDO FB=0.7V<br>I <sub>O_SOUBCE</sub> =1.4mA | 22   | 23.5 |     | V     |

| LDO_out Output Voltage Low            |                        | AUXVCC=24V,LDO FB=0.9V<br>I <sub>O SINK</sub> =1.4mA   |      | 0.2  |     | V     |

| Open Loop Gain                        |                        | GBNT(Note2)                                            | 50   |      |     | dB    |

| 5V AUX REG                            |                        |                                                        |      |      |     |       |

| REG FB Voltage                        |                        | REGOUT=REGEB                                           |      | 1.25 |     | V     |

| FB Pin Bias Current                   |                        | DEGOUTEDEGED                                           | -0.2 | 0    |     | μΑ    |

| REG_out Output Voltage                |                        | AUXVCC=24V,REG FB=1.1V                                 | 22   | 23.5 |     | V     |

| High                                  |                        | I <sub>O SOUBCE</sub> =1.4mA                           |      |      |     |       |

| REG_out Output Voltage                |                        | I <sub>o SOURCE</sub> =1.4mA<br>AUXVCC=24V,REG FB=1.4V |      | 0.2  |     | V     |

| Low                                   |                        | I <sub>o sink</sub> =1.4mA                             |      |      |     |       |

| Open Loop Gain                        |                        | GBNT(Note2)                                            | 50   |      |     | dB    |

| High Side driver                      |                        |                                                        |      |      |     |       |

| (CL=3300pF)                           |                        |                                                        |      |      |     |       |

| Output Impedance, Sourcing            | R <sub>source—H</sub>  |                                                        |      | 0.85 |     | ohm   |

| Current                               | 300100 11              |                                                        |      |      |     |       |

| Output Impedance , Sinking            | R <sub>sink—H</sub>    |                                                        |      |      |     |       |

| Current                               | J 11                   |                                                        |      | 0.65 |     | ohm   |

| Rise Time                             | T <sub>HDRV RISE</sub> | 10% to 90%                                             |      | 25   |     | ns    |

| Fall Time                             | T <sub>HDRV FALL</sub> | 90% to 10%                                             |      | 20   |     | ns    |

| Deadband Time                         | T <sub>DEAD_LH</sub>   | LDRV going Low to HDRV going High, 10% to 10%          |      | 30   |     | ns    |

| PARAMETER                  | SYM                     | TEST CONDITION                                 | MIN | TYP  | MAX | UNITS |

|----------------------------|-------------------------|------------------------------------------------|-----|------|-----|-------|

| Low Side driver            |                         |                                                |     |      |     |       |

| (CL=3300pF)                |                         |                                                |     |      |     |       |

| Output Impedance, Sourcing | R <sub>source—L</sub>   |                                                |     |      |     |       |

| Current                    | 300100 E                |                                                |     | 0.85 |     | ohm   |

| Output Impedance, Sinking  | $R_{\text{sink}\!-\!L}$ |                                                |     |      |     |       |

| Current                    | <b>.</b>                |                                                |     | 0.5  |     | ohm   |

| Rise Time                  | T <sub>LDRV BISE</sub>  | 10% to 90%                                     |     | 25   |     | ns    |

| Fall Time                  |                         | 90% to 10%                                     |     | 20   |     | ns    |

| Deadband Time              | T <sub>DEAD_HL</sub>    | SW going Low to LDRV going<br>High, 10% to 10% |     | 20   |     | ns    |

Note 1: 500ns transient. This pin can withstand -2V DC.

Note 2: This parameter is guaranteed by design but not tested in production (GBNT).

5

# **PIN DESCRIPTIONS**

| PIN# | PIN SYMBOL | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                |  |  |

|------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1    | ENSW1      | A resistor divider is connected from the respective switcher BUS voltages to these pins that holds off the controllers soft start until this threshold is reached. An                                                                                                                                          |  |  |

| 2    | ENSW2      | external low cost MOSFET or NPN transisitor can be connected to this pin texternal enable control.                                                                                                                                                                                                             |  |  |

| 3    | ENLDO      | A resistor divider is connected from the LDO bus voltage to this pin that holds off the LDO soft start until this threshold is reached. An external low cost MOSFET can be connected to this pin for external enable control.                                                                                  |  |  |

| 4    | GND        | Analog ground.                                                                                                                                                                                                                                                                                                 |  |  |

| 5    | VCC        | IC's supply voltage. This pin biases the internal logic circuits. A high freq 1uF ceramic capacitor is placed as close as possible to and connected to this pin and ground pin.                                                                                                                                |  |  |

| 6    | RT         | Oscillator's frequency can be set by using an external resistor from this pin to GND. This frequency is the master clock frequency which is internally divided by two to set each controller frequency.                                                                                                        |  |  |

| 7    | LDO FB     | LDO controller feedback input. If the LDOFB pin is pulled below 0.5*Vref, an internal comparator after certain delay and pulls down LDOOUT pin and initiates the HICCUP circuitry. During the startup this latch is not activated, allowing the LDOFB pin to come up and follow the Soft started Vref voltage. |  |  |

| 8    | LDO OUT    | LDO controller output. This pin is controlling the gate of an external NCH MOSFET. The maximum rating of this pin is 16V.                                                                                                                                                                                      |  |  |

| 9    | AUXVCC     | This pin is the supply voltage for the LDO controller as well as the 5V regulator controller that regulates the voltage at Vcc derived from the BUS voltage. The maximum voltage applied to this pin is 30V.                                                                                                   |  |  |

| 10   | REGOUT     | The output of the 5V regulator controller that drives a low current low cost external BIPOLAR transistor or an external MOSFET to regulate the voltage at Vcc pin derived from BUS voltage. This eliminates an otherwise external regulator needed in applications where 5V is not available.                  |  |  |

| 11   | REGFB      | Feedback pin of the 5V regulator controller. A resistor divider is connected from the output of the 5V regulator to this pin to complete the loop.                                                                                                                                                             |  |  |

| 12   | FB2        | This pin is the error amplifiers inverting input. These pins are connected via resistor dividers to the output of the switching regulators to set the output DC                                                                                                                                                |  |  |

| 29   | FB1        | voltage.                                                                                                                                                                                                                                                                                                       |  |  |

| 13   | COMP2      | These pins are the outputs of error amplifiers and are used to compensate the respective voltage control feedback loops.                                                                                                                                                                                       |  |  |

| 28   | COMP1      | - Copositio Foliago Control Tocabacit Toopo.                                                                                                                                                                                                                                                                   |  |  |

# **PIN DESCRIPTIONS**

| PIN# | PIN SYMBOL     | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                              |

|------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14   | OCP2           | This pin is connected to the drain of the external low side MOSFET and is the input of the over current protection(OCP) comparator. An internal current source which equals 1.25V divided by Rt resistor is flown to the external resistor which sets the OCP voltage across the Rdson of the low side MOSFET. Current limit |

| 27   | OCP1           | point is this voltage divided by the Rds-on. Once this threshold is reached the Hdrv and Ldrv pins are switched low and an internal hiccup circuit is set that recycles the soft start circuit after 2048 switching cycles.                                                                                                  |

| 15   | SW2            | These pins are connected to source of high side FETs and provide return path for the high side drivers. They are also used to hold the bw side drivers bw until this                                                                                                                                                         |

| 26   | SW1            | pin is brought low by the action of high side t <mark>urning off. IDRVs</mark> can <mark>onl</mark> y go high if<br>SW is below 1V threshold.                                                                                                                                                                                |

| 16   | HDRV2          | High side gate driveroutputs.                                                                                                                                                                                                                                                                                                |

| 25   | HDRV1          |                                                                                                                                                                                                                                                                                                                              |

| 17   | BST2           | This pin supplies voltage to high side FET driver. A high fieq 1 uF ceram is capacitoris placed as close as possible to and connected to these pins and respected                                                                                                                                                            |

| 24   | BST1           | SW pins.                                                                                                                                                                                                                                                                                                                     |

| 18   | PVCC2          | Supply voltage for the low side fet drivers. A high fiequency luff ceram is cap must be connected from this pin to the PGND 1 and PGND 2 pin as abset as possible to                                                                                                                                                         |

| 23   | PVCC1          | the pins.                                                                                                                                                                                                                                                                                                                    |

| 19   | LDRV2          | Low side gate driveroutputs.                                                                                                                                                                                                                                                                                                 |

| 22   | LDRV1          |                                                                                                                                                                                                                                                                                                                              |

| 20   | PGND2<br>PGND1 | Powerg <mark>round</mark> pin forlow side drivers.                                                                                                                                                                                                                                                                           |

| 30   | VP             | This pin is the firstenoram plifernon-inverting input. This pin should be connected either to an external reference voltage (tracking application) or to the internal reference voltage provided by this device.                                                                                                             |

| 31   | VREF           | Reference voltage available A 100pF capacitorcan be connected from this pin to GND . This pin is held by until internal VocUVIO and the ENSW 1 pin are good, allowing it to soft start.                                                                                                                                      |

| 32   | NC             |                                                                                                                                                                                                                                                                                                                              |

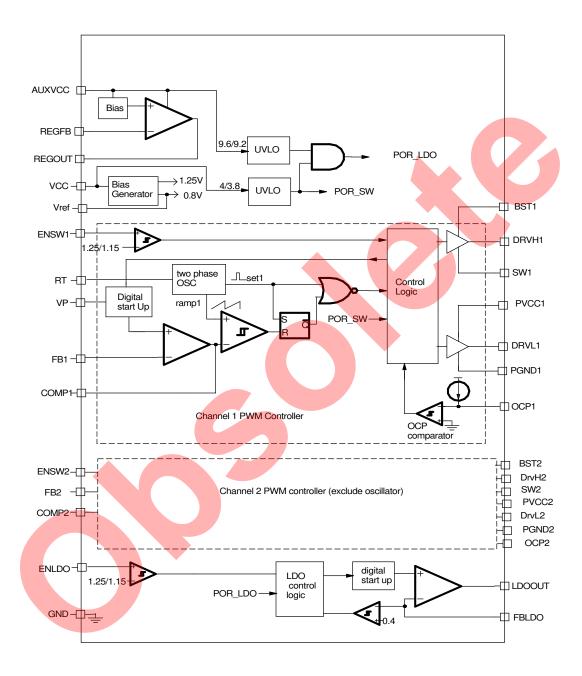

# **BLOCK DIAGRAM**

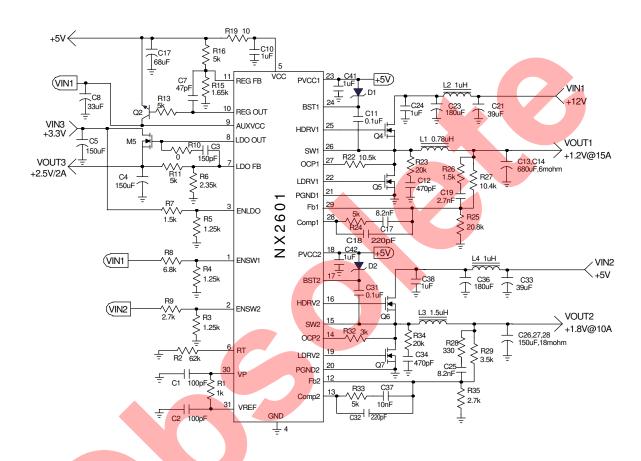

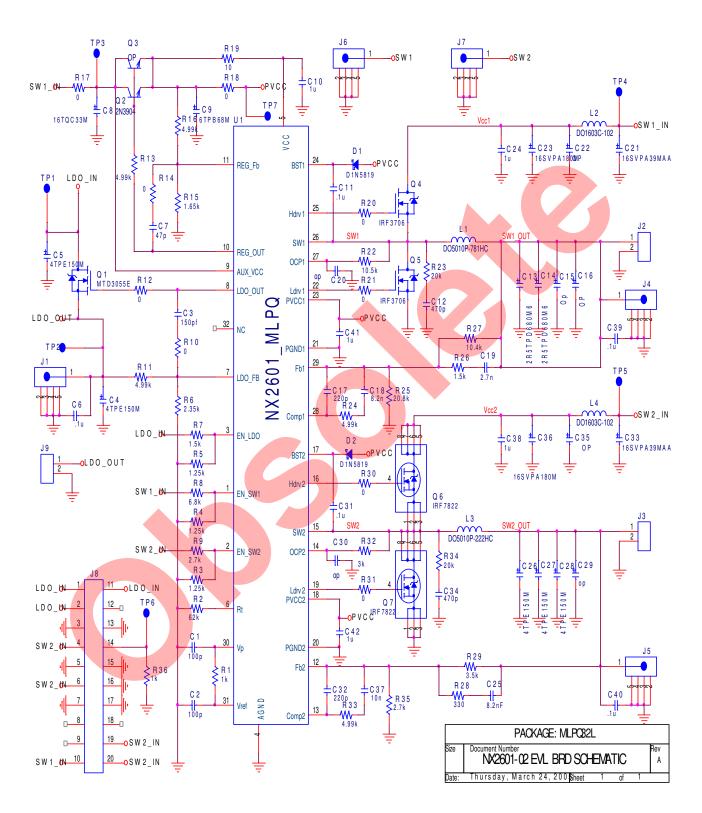

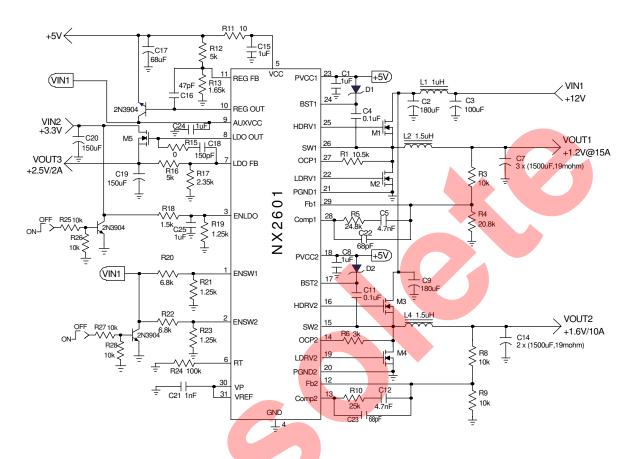

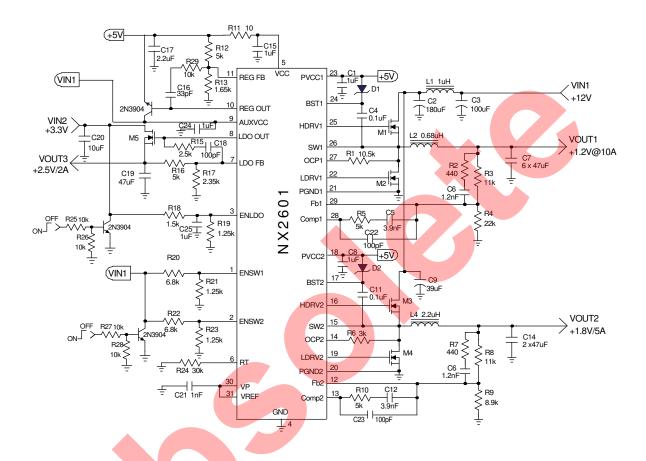

**Simplified Demo board schematic**

Figure 2 - Demo board schematic based on ORCAD

11861 Western Avenue, Garden Grove, CA. 92841, 800-877-6458, 714-898-8121, Fax: 714-893-2570

| Item numb | Quantity |                          | Value         | Manufacture             |

|-----------|----------|--------------------------|---------------|-------------------------|

| 1         | 2        | C2,C1                    | 100p          |                         |

| 2         |          | C3                       | 150pf         |                         |

| 3         |          | C4,C5,C26,C27,C28        | 4TPE150M      | SANYO                   |

| 4         |          | C6,C11,C31,C39,C40       | .1u           | 07.11.10                |

| 5         |          | C7                       | 47p           |                         |

| 6         |          | C8                       | 16TQC33M      | SANYO                   |

| 7         |          | C9                       | 6TPB68M       | SANYO                   |

| 8         |          |                          |               | SANTO                   |

| 9         |          | C10,C24,C38,C41,C42      | 1u            |                         |

|           |          | C12,C34                  | 470p          | CANIVO                  |

| 10        |          | C14,C13                  | 2R5TPD680M6   | SANYO                   |

| 11        | 9        | Q3,R14,C15,C16,C20,C22,  | OP            |                         |

|           |          | C29,C30,C35              |               |                         |

| 12        |          | C17,C32                  | 220p          |                         |

| 13        |          | C18                      | 8.2n          |                         |

| 14        |          | C19                      | 2.7n          |                         |

| 15        | 2        | C21,C33                  | 16SVPA39MAA   | SANYO                   |

| 16        | 2        | C36,C23                  | 16SVPA180M    | SANYO                   |

| 17        | 1        | C25                      | 8.2nF         |                         |

| 18        |          | C37                      | 10n           |                         |

| 19        |          | D1,D2                    | D1N5819       |                         |

| 20        |          | J1,J4,J5,J6,J7           | SCOPE TP      | Tektronics              |

| 21        |          | J2,J3,J9                 | CON2          | TORETOTIOS              |

| 22        |          | J8                       | CON20B        |                         |

| 23        |          | L1                       | DO5010P-781HC | Coiloraft               |

| 24        |          | L2,L4                    | DO1603C-102   | Coliciali               |

| 25        |          | L3                       | DO5010P-222HC |                         |

|           |          |                          |               |                         |

| 26        | 1        | Q1                       | MTD3055E      |                         |

| 27        |          | Q2                       | 2N3904        |                         |

| 28        |          | Q4,Q5                    | IRF3706       | International Rectifier |

| 29        |          | Q7,Q6                    | IRF7822       | International Rectifier |

| 30        |          | R1                       | 1k            |                         |

| 31        |          | R2                       | 62k           |                         |

| 32        |          | R3,R4,R5                 | 1.25k         |                         |

| 33        | 1        | R6                       | 2.35k         |                         |

| 34        |          | R7,R26                   | 1.5k          |                         |

| 35        | 1        | R8                       | 6.8k          |                         |

| 36        | 2        | R35,R9                   | 2.7k          |                         |

| 37        |          | R10,R12,R17,R18,R20,R21, | 0             |                         |

|           |          | R30,R31                  |               |                         |

| 38        | 5        | R11,R13,R16,R24,R33      | 4.99k         |                         |

| 39        |          | R15                      | 1.65k         |                         |

| 40        |          | R19                      | 10            |                         |

| 41        |          | R22                      | 10.5k         |                         |

| 42        |          | R34,R23                  | 20k           |                         |

| 43        |          | R25                      | 20.8k         |                         |

| 43        |          | R27                      | 10.4k         |                         |

|           |          |                          |               |                         |

| 45        |          | R28                      | 330           |                         |

| 46        |          | R29                      | 3.5k          |                         |

| 47        |          | R32                      | 3k            |                         |

| 48        |          | R36                      | 10k           |                         |

| 49        | 7        | TP1,TP2,TP3,TP4,TP5,TP6, | TP            |                         |

|           |          | TP7                      |               |                         |

| 50        | 1        | U1                       | NX2601_MLPQ   | NEXSEM INC.             |

#### **Demoboard waveforms**

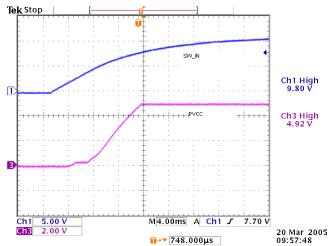

Figure 3 - Start up waveform of VCC by internal regulator. Ch1(AUXVCC), Ch3(VCC&PVCC)

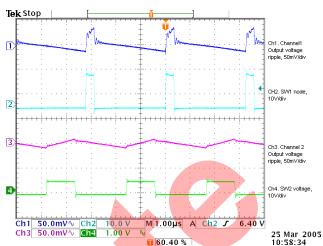

Figure 6 - Output ripple for power output CH1 and CH2

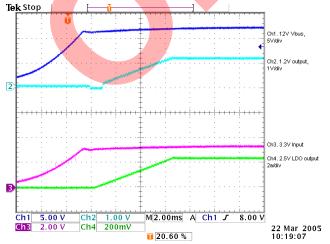

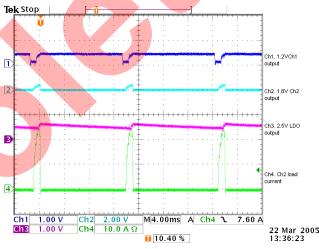

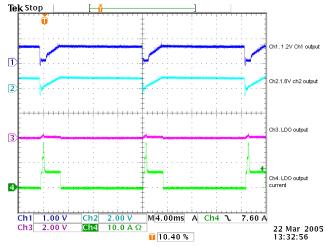

Figure 4 - Soft start for Channel 1 1.2V and chanel 2 1.8V output

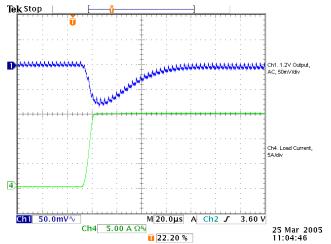

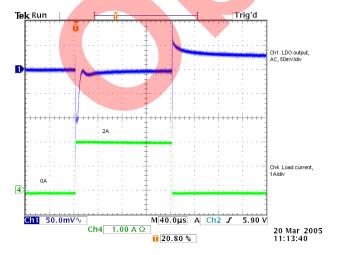

Figure 7-Transient response for first channel 1.2V output

Figure 5 - Soft start for Channel 1 1.2V and LDO output

Figure 8 - Transient reponse for Channel 1. (zoomed)

### **Demo Board Waveforms (Cont')**

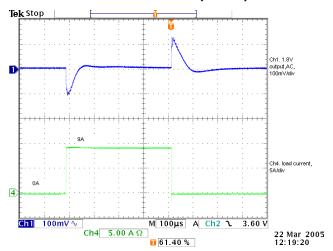

Figure 9 - Ch2 1.8V output transient 0 to 9A.

Tek Stop

Figure 10 - Ch2 1.8V transient (zoomed)

Figure 13 - Ch2 is in short. All channels are in hiccup.

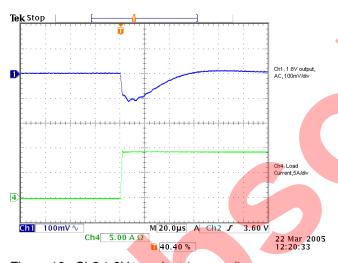

Figure 11 - Transient response for 2.5V LDO output

Figure 14 - LDO in short. All channels go into hiccup.

## **APPLICATION INFORMATION**

## **Symbol Used In Application Information:**

V<sub>IN</sub> - Input voltage

Vout - Output voltage Iout - Output current

$\Delta V_{\text{RIPPLE}}$  - Output voltage ripple

Fs - Switching frequency

$\Delta$ IRIPPLE - Inductor current ripple

### **Design Example**

Power stage design requirements:

VIN=12V

**V**out=1.2V

**І**оит =15А

$\Delta V_{RIPPLE} <= 20 mV$

$\Delta V_{TRAN} <= 100 \text{mV}$  @ 15A step

Fs=300kHz

### **Output Inductor Selection**

The selection of inductor value is based on inductor ripple current, power rating, working frequency and efficiency. Larger inductor value normally means smaller ripple current. However if the inductance is chosen too large, it brings slow response and higher cost. Usually the ripple current ranges from 20% to 40% of the output current. This is a design freedom which can be decided by design engineer according to various application requirements. The inductor value can be calculated by using the following equations:

$$L_{OUT} = \frac{V_{IN} - V_{OUT}}{\Delta I_{RIPPLE}} \times \frac{V_{OUT}}{V_{IN}} \times \frac{1}{F_{S}}$$

$$I_{RIPPLE} = K \times I_{OUTPLIT}$$

...(1)

I<sub>RIPPLE</sub> = K × I<sub>OUTPUT</sub>

where k is between 0.2 to 0.4.

Select k=0.3, then

$$L_{OUT} = \frac{12V - 1.2V}{0.3 \times 15A} \times \frac{1.2V}{12V} \times \frac{1}{300 \text{kHz}}$$

$L_{OUT} = 0.8uH$

Choose Lout=0.78uH, then coilcraft inductor DO5010P-781HC is a good choice.

Current Ripple is calculated as

$$\begin{split} \Delta I_{\text{RIPPLE}} &= \frac{V_{\text{IN}} - V_{\text{OUT}}}{L_{\text{OUT}}} \times \frac{V_{\text{OUT}}}{V_{\text{IN}}} \times \frac{1}{F_{\text{S}}} \\ &= \frac{12V - 1.2V}{0.78\text{uH}} \times \frac{1.2V}{12V} \times \frac{1}{300\text{kHz}} = 4.6\text{A} \end{split} \qquad ...(2)$$

### **Output Capacitor Selection**

Output capacitor is basically decided by the amount of the output voltage ripple allowed during steady state(DC) load condition as well as specification for the load transient. The optimum design may require a couple of iterations to satisfy both condition.

#### **Based on DC Load Condition**

The amount of voltage ripple during the DC load condition is determined by equation(3).

$$\Delta V_{RIPPLE} = ESR \times \Delta I_{RIPPLE} + \frac{\Delta I_{RIPPLE}}{8 \times F_{s} \times C_{OUT}} \dots (3)$$

Where ESR is the output capacitors' equivalent series resistance,C<sub>OUT</sub> is the value of output capacitors.

Typically when large value capacitors are selected such as Aluminum Electrolytic, POSCAP and OSCON types are used, the amount of the output voltage ripple is dominated by the first term in equation(3) and the second term can be neglected.

For this example, POSCAP are chosen as output capacitors, the ESR and inductor current typically determines the output voltage ripple.

$$ESR_{desire} = \frac{\Delta V_{RIPPLE}}{\Delta I_{PIRPLE}} = \frac{20mV}{4.6A} = 4.3m\Omega \qquad ...(4)$$

If low ESR is required, for most applications, multiple capacitors in parallel are better than a big capacitor. For example, for 20mV output ripple, POSCAP 2R5TPD680M6 with  $6m\Omega$  are chosen.

$$N = \frac{E S R_{E} \times \Delta I_{RIPPLE}}{\Delta V_{RIPPLE}} \qquad ...(5)$$

Number of Capacitor is calculated as

$$N = \frac{6m\Omega\!\times\!4.6A}{20mV}$$

N = 1.38

The number of capacitor has to be round up to a integer. Choose N = 2.

If ceramic capacitors are chosen as output capacitors, both terms in equation (3) need to be evaluated to determine the overall ripple. Usually when this type of capacitors are selected, the amount of capacitance per single unit is not sufficient to meet the transient specification, which results in parallel configuration of multiple capacitors.

#### **Based On Transient Requirement**

Typically, the output voltage droop during transient is specified as

$$\Delta V_{droop} < \Delta V_{tran}$$

@step load  $\Delta I_{STEP}$

During the transient, the voltage droop during the transient is composed of two sections. One section is dependent on the ESR of capacitor, the other section is a function of the inductor, output capacitance as well as input, output voltage. For example, for the overshoot when load from high load to light load with a  $\Delta I_{\text{STEP}}$  transient load, if assuming the bandwidth of system is high enough, the overshoot can be estimated as the following equation.

$$\Delta V_{\text{overshoot}} = ESR \times \Delta I_{\text{step}} + \frac{V_{\text{OUT}}}{2 \times L \times C_{\text{OUT}}} \times \tau^2 \qquad ... (6)$$

where  $\tau$  is the a function of capacitor, etc.

$$\tau = \begin{cases} 0 & \text{if } L \leq L_{\text{crit}} \\ \frac{L \times \Delta I_{\text{step}}}{V_{\text{OUT}}} - ESR \times C_{\text{OUT}} & \text{if } L \geq L_{\text{crit}} \end{cases} \dots (7)$$

where

$$L_{crit} = \frac{ESR \times C_{OUT} \times V_{OUT}}{\Delta I_{step}} = \frac{ESR_E \times C_E \times V_{OUT}}{\Delta I_{step}} \dots (8)$$

where  ${\sf ESR_E}$  and  ${\sf C_E}$  represents ESR and capacitance of each capacitor if multiple capacitors are used in parallel.

The above equation shows that if the selected output inductor is smaller than the critical inductance, the voltage droop or overshoot is only dependent on the ESR of output capacitor. For low frequency capacitor such as electrolytic capacitor, the product of ESR and capacitance is high and  $L \! \leq \! L_{\rm crit}$  is true. In that case, the transient spec is likely to dependent on the ESR of capacitor.

For most cases, the output capacitors are mul-

tiple capacitor in parallel. The number of capacitors can be calculated by the following

$$N = \frac{ESR_E \times \Delta I_{step}}{\Delta V_{tran}} + \frac{V_{OUT}}{2 \times L \times C_E \times \Delta V_{tran}} \times \tau^2 \quad ...(9)$$

where

$$\tau = \begin{cases} 0 & \text{if} \quad L \leq L_{\text{crit}} \\ \frac{L \times \Delta I_{\text{step}}}{V_{\text{OUT}}} - ESR_E \times C_E & \text{if} \quad L \geq L_{\text{crit}} & \dots \text{(10)} \end{cases}$$

For example, assume voltage droop during transient is 100mV for 15A load step.

If the POSCAP 2R5TPD680M6 (680uF, 6mohm ESR) is used, the crticial inductance is given as

$$L_{crit} = \frac{ESR_E \times C_E \times V_{OUT}}{\Delta I_{step}} = \frac{6m\Omega \times 680\mu F \times 1.2V}{15A} = 0.33\mu H$$

The selected inductor is 0.78uH which is bigger than critical inductance. In that case, the output voltage transient not only dependent on the ESR, but also capacitance.

number of capacitors is

$$\tau = \frac{L \times \Delta I_{\text{step}}}{V_{\text{OUT}}} - ESR_E \times C_E$$

$$= \frac{0.78 \mu H \times 15A}{1.2V} - 6m\Omega \times 680 \mu F = 5.67 us$$

$$\begin{split} N &= \frac{ESR_E \times \Delta I_{step}}{\Delta V_{tran}} + \frac{V_{OUT}}{2 \times L \times C_E \times \Delta V_{tran}} \times \tau^2 \\ &= \frac{6m\Omega \times 15A}{100mV} + \frac{1.2V}{2 \times 0.78 \mu H \times 680 \mu F \times 100mV} \times (5.67us)^2 \\ &= 1.3 \end{split}$$

The number of capacitors has to satisfied both ripple and transient requirement. Overall, we can choose N=2.

It should be considered that the proposed equation is based on ideal case, in reality, the droop or overshoot is typically more than the calculation. The equation gives a good start. For more margin, more capacitors have to choose after the test. Typically, for high

frequency capacitor such as high quality POSCAP especially ceramic capacitor, 20% up 100% (for ceramic) more capacitors have to be chosen since the ESR of capacitors is so low that the PCB parasitics can affect the results tremendously. More capacitors have to be selected to compensate these parasitic parameters.

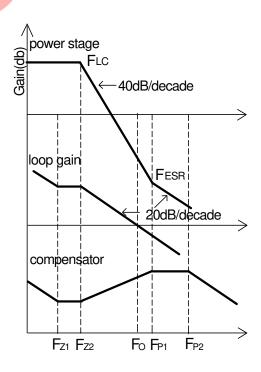

### **Compensator Design**

Due to the double pole generated by LC filter of the power stage, the power system has 180° phase shift, and therefore, is unstable by itself. In order to achieve accurate output voltage and fast transient response, compensator is employed to provide highest possible bandwidth and enough phase margin.ldeally,the Bode plot of the closed loop system has crossover frequency between 1/10 and 1/5 of the switching frequency, phase margin greater than 50° and the gain crossing 0db with -20db/decade. Power stage output capacitors usually decide the compensator type. If electrolytic capacitors are chosen as output capacitors, type II compensator can be used to compensate the system, because the zero caused by output capacitor ESR is lower than crossover frequency. Otherwise type III compensator should be chosen.

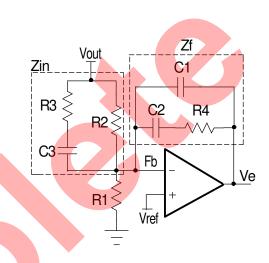

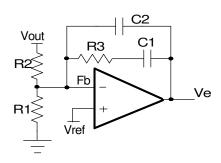

#### A. Type III compensator design

For low ESR output capacitors, typically such as Sanyo OSCON and POSCAP, the frequency of ESR zero caused by output capacitors is higher than the cross-over frequency. In this case, it is necessary to compensate the system with type III compensator. The following figures and equations show how to realize the type III compensator by voltage mode amplifier.

$$F_{z_1} = \frac{1}{2 \times \pi \times R_4 \times C_2} \qquad ...(11)$$

$$F_{z2} = \frac{1}{2 \times \pi \times (R_2 + R_3) \times C_3}$$

...(12)

$$F_{P1} = \frac{1}{2 \times \pi \times R_3 \times C_3} \qquad ...(13)$$

$$F_{P2} = \frac{1}{2 \times \pi \times R_4 \times \frac{C_1 \times C_2}{C_1 + C_2}} \qquad ...(14)$$

where  $F_{Z1}$ ,  $F_{Z2}$ ,  $F_{P1}$  and  $F_{P2}$  are poles and zeros in the compensator. Their locations are shown in figure 15.

The transfer function of type III compensator is given by:

$$\frac{V_{\text{e}}}{V_{\text{OUT}}} = \frac{1}{sR_2 \times (C_2 + C_1)} \times \frac{(1 + sR_4 \times C_2) \times \left[1 + s(R_2 + R_3) \times C_3\right]}{(1 + sR_4 \times \frac{C_2 \times C_1}{C_2 + C_1}) \times \left(1 + sR_3 \times C_3\right)}$$

Figure 15 - Type III compensator and its bode plot

The crossover frequency usually is selected as  $F_{LC} < F_O < F_{ESR,}$  and  $F_O < = 1/10 \sim 1/5 F_s$  for type III compensator.

1.Calculate the location of LC double pole  $F_{\rm LC}$  and ESR zero  $\,F_{\rm ESR}$  .

$$\begin{aligned} F_{LC} &= \frac{1}{2 \times \pi \times \sqrt{L_{OUT} \times C_{OUT}}} \\ &= \frac{1}{2 \times \pi \times \sqrt{0.78 uH \times 1320 uF}} \\ &= 4.89 kHz \end{aligned}$$

$$F_{ESR} = \frac{1}{2 \times \pi \times ESR \times C_{OUT}}$$

$$= \frac{1}{2 \times \pi \times 3m\Omega \times 1360uF}$$

$$= 39kHz$$

2.Set R<sub>2</sub> equal to10.4kΩ.

$$R_{1} {=} \frac{R_{2} {\times} V_{\text{REF}}}{V_{\text{OUT}} {-} V_{\text{REF}}} {=} \frac{10.4 k\Omega {\times} 0.8 V}{1.2 V {-} 0.8 V} {=} 20.8 k\Omega$$

Choose  $R_1 = 20.8k\Omega$ .

- 3. Set zero  $F_{Z2} = F_{LC}$  and  $F_{p1} = F_{ESR}$  .

- 4. Calculate  $R_4$  and  $C_3$  with the crossover frequency smaller than  $1/10\sim 1/5$  of the swithing frequency. Set  $F_0=25 \text{kHz}$ .

$$C_{3} = \frac{1}{2 \times \pi \times R_{2}} \times (\frac{1}{F_{z2}} - \frac{1}{F_{p1}})$$

$$= \frac{1}{2 \times \pi \times 10.4 \text{k}\Omega} \times (\frac{1}{4.89 \text{kHz}} - \frac{1}{39 \text{kHz}})$$

$$= 2.8 \text{nF}$$

Choose C<sub>3</sub>=2.7nF.

$$R_{4} = \frac{V_{OSC}}{V_{in}} \times \frac{2 \times \pi \times F_{O} \times L}{C_{3}} \times C_{out}$$

$$= \frac{1V}{12V} \times \frac{2 \times \pi \times 25 \text{kHz} \times 0.8 \text{uH}}{2.7 \text{nF}} \times 1360 \text{uF}$$

$$= 5.3 \text{k}\Omega$$

Choose R<sub>4</sub>=5k

5. Calculate  $C_2$  with zero  $F_{z1}$  at 75% of the LC double pole by equation (11).

$$C_{2} = \frac{1}{2 \times \pi \times F_{z_{1}} \times R_{4}}$$

$$= \frac{1}{2 \times \pi \times 0.75 \times 4.89 \text{kHz} \times 5 \text{k}\Omega}$$

$$= 8.8 \text{nF}$$

Choose C<sub>2</sub>=8.2nF

6. Calculate  $C_1$  by equation (14) with pole  $F_{p2}$  at half the swithing frequency.

$$C_{1} = \frac{1}{2 \times \pi \times R_{4} \times F_{P2}}$$

$$= \frac{1}{2 \times \pi \times 5k\Omega \times 150kHz}$$

$$= 212pF$$

Choose C<sub>1</sub>=220pF

7. Calculate R<sub>3</sub> by equation (13).

$$R_{3} = \frac{1}{2 \times \pi \times F_{P1} \times C_{3}}$$

$$= \frac{1}{2 \times \pi \times 39 \text{kHz} \times 2.7 \text{nF}}$$

$$= 1.5 \text{k}\Omega$$

Choose  $R_{3} = 1.5 \text{k}\Omega$ .

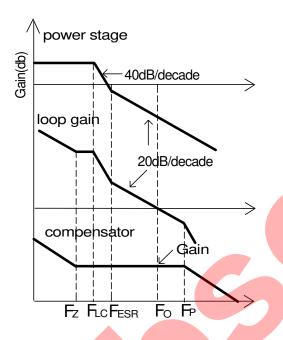

#### B. Type II compensator design

If the electrolytic capacitors are chosen as power stage output capacitors, usually the Type II compensator can be used to compensate the system.

Type II compensator can be realized by simple RC circuit as shown in figure  $16.R_3$  and  $C_1$  introduce a zero to cancel the double pole effect.  $C_2$  introduces a pole to suppress the switching noise. The following equations show the compensator pole zero location and constant gain.

Gain=

$$\frac{R_3}{R_2}$$

... (15)

$F_z = \frac{1}{2 \times \pi \times R_3 \times C_1}$  ... (16)

$$F_{p} = \frac{1}{2 \times \pi \times R_{2} \times C_{2}} \qquad \dots (17)$$

Figure 16 - Type II compensator and its bode plot

For type II compensator,  $F_0$  has to satisfy  $F_{LC} < F_{ESR} < < F_0 < = 1/10 \sim 1/5F_s$ .

The following parameters are used as an example for type II compensator design, three 1500uF with 19mohm Sanyo electrolytic CAP 6MV1500WGL are used as output capacitors. Coilcraft DO5010P-152HC 1.5uH is used as output inductor. The other power stage information is that:

**V**IN=12V, Vout=1.2V, Iout =15A, Fs=200kHz.

1.Calculate the location of LC double pole  $\rm F_{LC}$  and ESR zero  $\rm F_{ESR}.$

$$F_{LC} = \frac{1}{2 \times \pi \times \sqrt{L_{OUT} \times C_{OUT}}}$$

$$= \frac{1}{2 \times \pi \times \sqrt{1.5 \text{uH} \times 4500 \text{uF}}}$$

$$= 1.94 \text{kHz}$$

$$F_{ESR} = \frac{1}{2 \times \pi \times ESR \times C_{OUT}}$$

$$= \frac{1}{2 \times \pi \times 6.33 \text{m}\Omega \times 4500 \text{uF}}$$

$$= 5.6 \text{kHz}$$

2.Set crossover frequency Fo=20kHz>>F<sub>ESR</sub>.

3. Set  $R_2$  equal to  $10k\Omega$ . Based on output voltage, using equation 18, the final selection of  $R_1$  is  $20k\Omega$ .

4. Calculate R<sub>3</sub> value by the following equation.

$$R_{3} = \frac{V_{OSC}}{V_{in}} \times \frac{2 \times \pi \times F_{O} \times L}{ESR} \times R_{2}$$

$$= \frac{1 V}{12 V} \times \frac{2 \times \pi \times 20 \text{kHz} \times 1.5 \text{uH}}{6.33 \text{m} \Omega} \times 10 \text{k}\Omega$$

$$= 24.8 \text{k}\Omega$$

Choose  $R_3 = 24.8 k\Omega$ .

5. Calculate  $C_1$  by setting compensator zero  $F_2$  at 75% of the LC double pole.

$$C_{1} = \frac{1}{2 \times \pi \times R_{3} \times F_{z}}$$

$$= \frac{1}{2 \times \pi \times 24.8 \text{k}\Omega \times 0.75 \times 1.94 \text{kHz}}$$

$$= 4.4 \text{nF}$$

Choose  $C_1=4.7nF$ .

6. Calculate  ${\rm C_2}$  by setting compensator pole  $F_{\rm p}$  at half the swithing frequency.

$$C_{2} = \frac{1}{\pi \times R_{3} \times F_{s}}$$

$$= \frac{1}{\pi \times 24.8 \, k \, \Omega \times 200 \, k \, H \, z}$$

$$= 64 \, p \, F$$

Choose C<sub>2</sub>=68pF

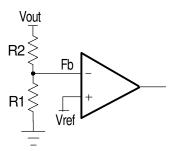

### **Output Voltage Calculation**

Output voltage is set by reference voltage and external voltage divider. The reference voltage is fixed at 0.8V. The divider consists of two ratioed resistors so that the output voltage applied at the Fb pin is 0.8V when the output voltage is at the desired value. The following equation and picture show the relationship between  $V_{\text{OUT}}$ ,  $V_{\text{RFF}}$  and voltage divider.

$$R_1 = \frac{R_2 \times V_{REF}}{V_{OUT} - V_{REF}} \qquad ...(18)$$

where R<sub>2</sub> is part of the compensator, and the value of R<sub>1</sub> value can be set by voltage divider.

Choose R<sub>2</sub>=10k $\Omega$ , to set the output voltage at 1.8V, the result of R<sub>1</sub> is 8k $\Omega$ .

Voltage divider

Figure 17 - Voltage divider

In general, the minimum output load impedance including the resistor divider should be less than  $5k\Omega$  to prevent overcharge the output voltage by leakage current (e.g. Error Amplifier feedback pin bias current). A minimum load for  $5k\Omega$  less (<1/16w for most of application) is recommended to put at the output. For example, in this application,

Vout=1.6V

The power loss is 1/16W less

$$R_{I,OAD} = 1.6V \times 1.6V / (1/16W) = 40\Omega$$

Select minimum load is  $1k\Omega$  should be good enough.

### **Input Capacitor Selection**

Input capacitors are usually a mix of high frequency ceramic capacitors and bulk capacitors. Ceramic capacitors bypass the high frequency noise, and bulk capacitors supply current to the MOSFETs. Usually 1uF ceramic capacitor is chosen to decouple the high frequency noise. The bulk input capacitors are decided by voltage rating and RMS current rating. The RMS current in the input capacitor can be calculated

$$\begin{split} I_{\text{RMS}} &= I_{\text{OUT}} \times \sqrt{D} \times \sqrt{1 - D} \\ D &= \frac{V_{\text{OUT}}}{V_{\text{IN}}} \\ &\dots (19) \end{split}$$

$V_{IN} = 12V$ ,  $V_{OUT} = 1.2V$ ,  $I_{OUT} = 15A$ , using equation (19), the result of input RMS current is 4.5A.

For higher efficiency, low ESR capacitors are recommended.

Two Sanyo OS-CON SVPA180M 16V 180uF **29m**O with 3.4A RMS rating are chosen as input bulk capacitors.

#### **Power MOSFETs Selection**

The NX2601 requires two N-Channel power MOSFETs. The selection of MOSFETs is based on maximum drain source voltage, gate source voltage, maximum current rating, MOSFET on resistance and power dissipation. The main consideration is the power loss contribution of MOSFETs to the overall converter efficiency. In this design example, two IRFR3706 are used. They have the following parameters:  $V_{DS}$ =30V,  $I_{DSON}$ =9m $\Omega$ ,  $Q_{GATE}$ =23nC.

There are three factors causing the MOSFET power loss:conduction loss, switching loss and gate driver loss.

Gate driver loss is the loss generated by discharging the gate capacitor and is dissipated in driver circuits. It is proportional to frequency and is defined as:

$$P_{\text{gate}} = (Q_{\text{HGATE}} \times V_{\text{HGS}} + Q_{\text{LGATE}} \times V_{\text{LGS}}) \times F_{\text{S}} \qquad ...(20)$$

where  $Q_{\text{HGATE}}$  is the high side MOSFETs gate charge,  $V_{\text{HGS}}$  is the high side gate source voltage, and  $V_{\text{LGS}}$  is the low side gate source voltage.

According to equation (3),  $P_{\text{GATE}} = 0.07W$ . This power dissipation should not exceed maximum power dissipation of the driver device.

Conduction loss is simply defined as:

$$\begin{split} &P_{\text{HCON}} \!=\! I_{\text{OUT}}^{2} \!\times\! D \!\times\! R_{\text{DS(ON)}} \!\times\! K \\ &P_{\text{LCON}} \!=\! I_{\text{OUT}}^{2} \!\times\! (1 \!-\! D) \!\times\! R_{\text{DS(ON)}} \!\times\! K \\ &P_{\text{TOTAL}} \!=\! P_{\text{HCON}} + P_{\text{LCON}} \end{split} \qquad ...(21)$$

where the R<sub>DS(ON)</sub> will increases as MOSFET junction temperature increases, K is R<sub>DS(ON)</sub> temperature dependency. As a result, R<sub>DS(ON)</sub> should be selected for the worst case, in which K equals to 1.4 at 125°C according to IRFR3706 datasheet. Using equation (4), the result of P<sub>TOTAL</sub> is 0.54W. Conduction loss should not exceed package rating or overall system thermal budget.

Switching loss is mainly caused by crossover conduction at the switching transition. The total switching loss can be approximated.

$$P_{SW} = \frac{1}{2} \times V_{IN} \times I_{OUT} \times T_{SW} \times F_{S} \qquad ...(22)$$

where  $I_{\text{OUT}}$  is output current,  $T_{\text{SW}}$  is the sum of  $T_{\text{R}}$  and  $T_{\text{F}}$  which can be found in mosfet datasheet, and  $F_{\text{S}}$  is switching frequency. The result of  $P_{\text{SW}}$  is 1.5W. Swithing loss  $P_{\text{SW}}$  is frequency dependent.

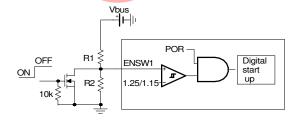

#### **Soft Start and Enable**

NX2601 has two switching controller and one LDO controller. Each of them has individual digital soft start. Each channel has one enable pin for start up. When the Power Ready (POR) signal is high and the voltage at enable pin is above 1.25V, the internal digital counter starts to operate and the voltage at positive input of Error amplifier starts to increase, the feedback network will force the output voltage follows the reference and starts the output slowly. After 2048 cycles, the soft start is complete and the output voltage is regulated to the desired voltage decided by the feedback resistor divider

Figure 18 - Enable and Shut down the NX2601 with Enable pin.

The start up of NX2601 can be programmed through resistor divider at Enable pin. For example, for channel 1, if the input bus voltage is 12V and we want NX2601 starts when Vbus is above 8V. We can select

$$R_1 = \frac{(8V - 1.25V) \times R_2}{1.25V} = 6.8k\Omega$$

The NX2601 can be turned off by pulling down the ENable pin by extra signal MOSFET as shown in the above Figure. When Enable pin (ENSW1) is below 1.15V, the digital soft start is reset to zero. In addition, all the high side is off and output voltage is turned off.

### Frequency Selection

The frequency can be set by external Rt resistor. The relationship between frequency and RT pin is shown as follows.

#### Frequency(kHz) vs. RT

Figure 19 - Frequency versus Rt resistor

For example, for 300kHz operation, Rt is about 62kohm.

#### **Over Current Limit Protection**

Over current limit for step down converter is achieved by sensing current through the low side

MOSFET. Inside NX2601, the current through Rt pin is mirrored and injecting to the pin OCP. Since the current through Rt pin is decided as

$$I_{RT} = \frac{1.25}{R_{+}}$$

This current is very accurate and does not change with silicon process and temperature, the over current limit tripping point can be set more accurate than traditional current source. This scheme is the property of Nexsem. When synchronous FET is on, the voltage at node SW is given as

$$V_{SW} = -I_1 \times R_{DSON}$$

The voltage at pin OCP is given as

$$I_{OCP} \times R_{OCP} + V_{SW}$$

When the voltage is below zero, the over current occurs. The over current limit can be set by the following equation

$$I_{\text{SET}} = I_{\text{RT}} \times R_{\text{OCP}} / R_{\text{DSON}}$$

For example, For 20A current limit and 9mohm Rdson for IRFR3706, the OCP set resistor is calculated as

$$I_{RT} = \frac{1.25V}{62k} = 20uA$$

$$R_{OCP} = \frac{I_{SET}}{I_{RT}} \times R_{DSON} = \frac{20A}{20uA} \times 9 \text{mohm} = 9 \text{kohm}$$

Select OCP set resistor R=10.5k.

For NX2601, if one channel goes to hiccup current limit, the other channels include LDO will go to hiccup too.

#### **LDO Selection Guide**

NX2601 offers a LDO controller. The selection of MOSFET to meet LDO is more straight forward. The selection is that the Rdson of MOSFET should meet the dropout requirement. For example.

$$V_{LDOIN} = 3.3V$$

$$V_{LDOOUT} = 2.5V$$

The maximum Rdson of MOSFET should be

$$R_{RDSON} = (V_{LDOIN} - V_{LDOOUT}) \times I_{LOAD}$$

$$= (3.3V - 2.5V)/2A = 0.4\Omega$$

Most of MOSFETs can meet the requirement. More

important is that MOSFET has to be selected right package to handle the thermal capability. For LDO, maximum power dissipation is given as

$$P_{LOSS} = (V_{LDOIN} - V_{LDOOUT}) \times I_{LOAD}$$

$$= (3.3V - 2.5V) \times 2A = 1.6W$$

Select IR MOSFET IRFR3706 with 9m $\Omega$  R  $_{\mbox{\tiny DSON}}$  is sufficient.

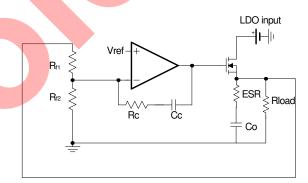

### **LDO Compensation**

The diagram of LDO controller including VCC regulator is shown in above figure 20. For low frequency capacitor such as electrolytic, POSCAP, OSCON, etc, The compensation parameter can be calculated as follows.

$$C_{c} = \frac{1}{2 \times \pi \times F_{o} \times R_{f1}} \times \frac{g_{m} \times ESR}{1 + g_{m} \times ESR}$$

where Fois the desired loop gain.

Figure 20 - NX2601 LDO controller.

Typically,  $\rm F_{\odot}$  has to be higher than zero caused by ESR.  $\rm F_{\odot}$  is typically around several tens kHz to a few hundred kHz. For this example, we select Fo=100kHz.  $\rm g_{m}$  is the forward trans-conductance of MOSFET.

For IRFR3706,  $g_m = 53$ .

Select R,=5kohm.

Output capacitor is Sanyo POSCAP 4TPE150MI with 150uF, ESR=18mohm.

$$C_{\text{C}} = \frac{1}{2 \times \pi \times 100 \text{kHz} \times 5 \text{k}\Omega} \times \frac{53 \times 18 \text{m}\Omega}{1 + 53 \times 18 \text{m}\Omega} = 155 \text{pF}$$

Choose  $C_c = 150 pF$ .

For electrolytic or POSCAP,  $R_{\rm C}$  is typically selected to be zero.

R<sub>fo</sub> is determined by the desired output voltage

$$\begin{aligned} R_{f2} &= R_{f1} \times V_{REF} / (V_{LDOOUT} - V_{REF}) \\ &= 5k\Omega \times 0.8V / (2.5V - 0.8) = 2.35k\Omega \end{aligned}$$

Choose  $R_p = 2.34 k\Omega$ .

#### **Current Limit for LDO**

Current limit of LDO is achieved by sensing the LDO feedback voltage. When LDO\_FB pin is below 0.4V, the IC goes into hiccup mode. The IC will turn off all the channel (Channel 1 and Channel 2) for 2096 cycles and start to restart system again.

### **Layout Considerations**

The layout is very important when designing high frequency switching converters. Layout will affect noise pickup and can cause a good design to perform with less than expected results.

There are two sets of components considered in the layout which are power components and small signal components. Power components usually consist of input capacitors, high-side MOSFET, low-side MOSFET, inductor and output capacitors. A noisy environment is generated by the power components due to the switching power. Small signal components are connected to sensitive pins or nodes. A multilayer layout which includes power plane, ground plane and signal plane is recommended.

Layout guidelines:

- 1. First put all the power components in the top layer connected by wide, copper filled areas. The input capacitor, inductor, output capacitor and the MOSFETs should be close to each other as possible. This helps to reduce the EMI radiated by the power loop due to the high switching currents through them.

- 2. Low ESR capacitor which can handle input RMS ripple current and a high frequency decoupling ceramic cap which usually is 1uF need to be practically touching the drain pin of the upper MOSFET, a plane connection is a must.

- 3. The output capacitors should be placed as close

as to the load as possible and plane connection is required.

- 4. Drain of the low-side MOSFET and source of the high-side MOSFET need to be connected thru a plane ans as close as possible. A snubber nedds to be placed as close to this junction as possible.

- 5. Source of the lower MOSFET needs to be connected to the GND plane with multiple vias. One is not enough. This is very important. The same applies to the output capacitors and input capacitors.

- 6. Hdrv and Ldrv pins should be as close to MOSFET gate as possible. The gate traces should be wide and short. A place for gate drv resistors is needed to fine tune noise if needed.

- 7. Vcc capacitor, BST capacitor or any other bypassing capacitor needs to be placed first around the IC and as close as possible. The capacitor on comp to GND or comp back to FB needs to be place as close to the pin as well as resistor divider.

- 8. The output sense line which is sensing output back to the resistor divider should not go through high frequency signals.

- 9. All GNDs need to go directly thru via to GND plane.

- 10. The feedback part of the system should be kept away from the inductor and other noise sources, and be placed close to the IC.

- 11. In multilayer PCB, separate power ground and analog ground. These two grounds must be connected together on the PC board layout at a single point. The goal is to localize the high current path to a separate loop that does not interfere with the more sensitive analog control function.

21

# **TYPICAL APPLICATIONS**

Figure 21 - NX2601 application with electrolytic capacitors as output capacitors

# **TYPICAL APPLICATIONS(cont')**

Figure 22 - NX2601 application with ceramic capacitors as output capacitors

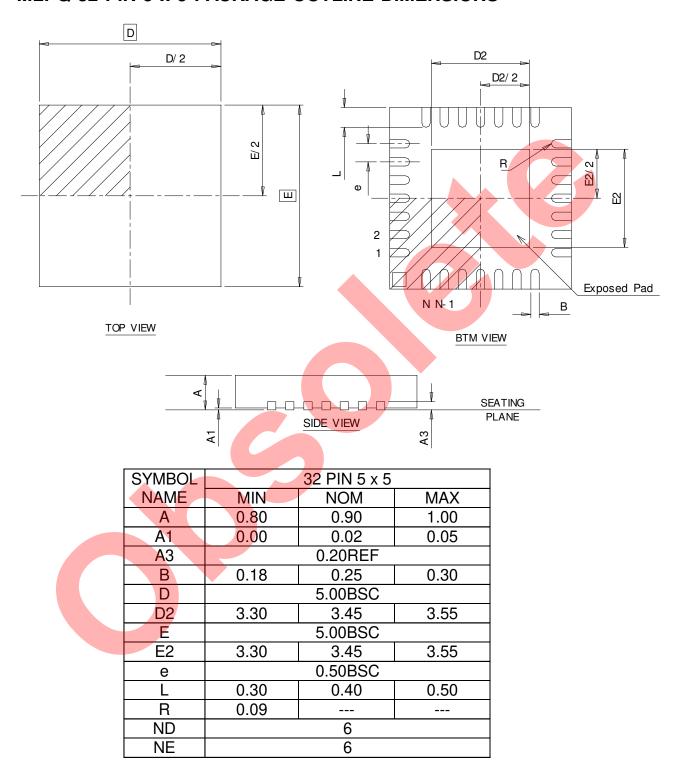

### MLPQ 32 PIN 5 x 5 PACKAGE OUTLINE DIMENSIONS

NOTE: ALL DIMENSIONS ARE DISPLAYED IN MILLIMETERS.

ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

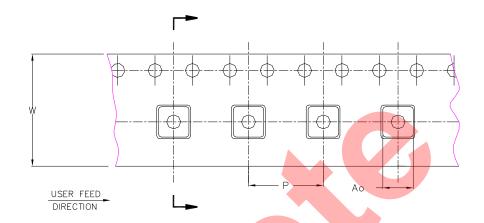

## MLPQ 32 PIN 5 x 5 TAPE AND REEL INFORMATION

| Dimension    | MLPQ 05X05   |

|--------------|--------------|

| Ао           | 5.30 +/- 0.1 |

| Во           | 6.30 +/- 0.1 |

| Ko           | 1.2 +/- 0.1  |

| P            | 8 +/- 0.1    |

| W            | 12 +/- 0.3   |

| 1            | 0.3 +/- 0.05 |

| R7/Quantity  | 1000         |

| R13/Quantity | 3000         |

#### NOTE:

- 1. R7 = 7 INCH LOCK REEL, R13 = 13 INCH LOCK REEL.

- 2. ALL DIMENSIONS ARE DISPLAYED IN MILLIMETERS.