# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Product data sheet COMPANY PUBLIC

### **1** General description

The NXP NXH5104 is a 4 Mbit serial electrically erasable and programmable read-only memory (EEPROM). It provides byte level and page level serial EEPROM functions, sector level protection and power-down functions. The device has been developed for low-power low-voltage applications and is provided with a Serial Peripheral Interface (SPI) compatible interface.

### 2 Features and benefits

- Compact Wafer Level Chip Scale Package (WLCSP) package

- – 7.8 mm<sup>2</sup>, 380 µm thick

- 13 bumps with 400 µm pitch

- Integrated Power Management Unit (PMU)

- V<sub>DD</sub> supply range 1.0 V to 2.0 V

- V<sub>DD(IO)</sub> supply range: V<sub>DD</sub> to 2.6 V

- Direct operation from ZnAir, NiMH, Silver-Zinc batteries

- Active peak current limiting

- Low current consumption

- Average power down current < 5 µA</li>

- Average read current 0.6 mA ( $V_{DD}$  =  $V_{DD(IO)}$  = 1.8 V,  $F_{SPI}$  =5 MHz)

- Average write current 0.7 mA ( $V_{DD} = V_{DD(IO)} = 1.8 \text{ V}, \text{ F}_{SPI} = 5 \text{ MHz}$ )

- Low-power CMOS technology

- · Auxiliary supply voltage enabling direct LED drive

- · Self-timed program cycle

- 256 byte page write buffer

- Partial page write allowed

- Write Protect

- Quarter, half or entire memory array

- Serial Peripheral Interface (SPI)

- - Speed up to 5 MHz for 1.2 V signaling level

- Speed up to 10 MHz for 1.8 V signaling level

- SPI Mode 0 (0,0) and 3 (1,1) support

- SPI 3-wire support for SPI mode 0

- Fixed High Supply mode for faster start-up

- Space-saving 2.80 mm × 2.74 mm Wafer Level Chip Scale Package (WLCSP)

- Highly integrated: 1 external cap

- High Reliability

- 10-year data retention

- 500 000 program cycles

- Wear-out management

- Operating temperature -20 °C to +85 °C

- Support for different supply configurations

- Device ID and Unique ID

- · Pb-free and RoHS compliant

### **3** Ordering information

| Table 1. Ordering information |         |                                                                          |           |  |  |  |

|-------------------------------|---------|--------------------------------------------------------------------------|-----------|--|--|--|

| Type number Package           |         |                                                                          |           |  |  |  |

|                               | Name    | Description                                                              | Version   |  |  |  |

| NXH5104UK/A1                  | WLCSP13 | wafer level chip-scale package; 13 bumps;<br>2.74 mm × 2.80 mm × 0.38 mm | SOT1461-1 |  |  |  |

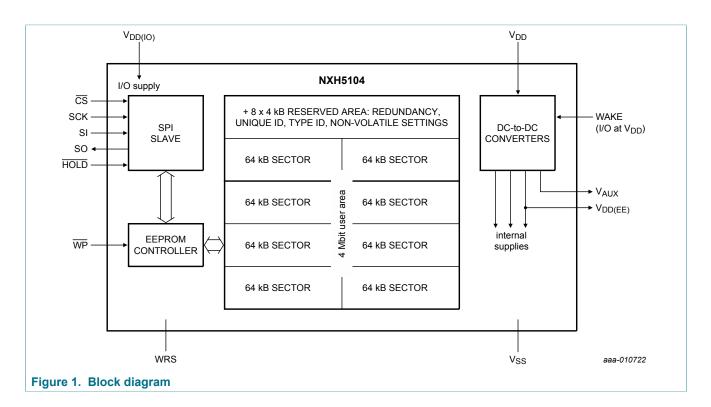

### 4 Block diagram

#### **Pinning information** 5

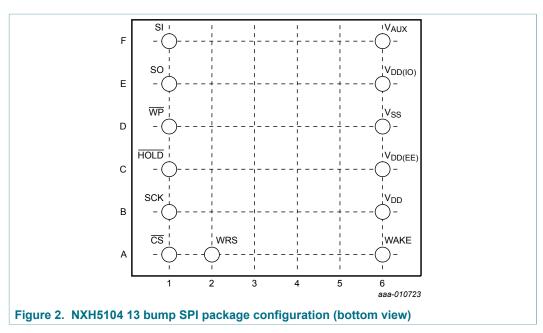

### 5.1 Pinning

### 5.2 Pin description

| Bump   | Symbol              | Туре | Description                                                                                                                                                                                                                                                       |

|--------|---------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dump   | Cymbol              | Type | Beschption                                                                                                                                                                                                                                                        |

| SUPPLY | /                   |      |                                                                                                                                                                                                                                                                   |

| B6     | V <sub>DD</sub>     | PWR  | primary supply input. The $V_{DD}$ pin is used to supply the source voltage to the device. Operations at invalid $V_{DD}$ voltages may produce spurious results and should not be attempted.                                                                      |

| E6     | V <sub>DD(IO)</sub> | PWR  | input/output supply input. The V <sub>DD(IO)</sub> pin is used to supply the IO voltage to the device and hence defines the signaling voltage of the SPI slave interface. The voltage level of V <sub>DD(IO)</sub> must be equal or higher than V <sub>DD</sub> . |

| C6     | V <sub>DD(EE)</sub> | PWR  | EEPROM array supply output. In Wide Range Supply mode, this pin requires a 470 nF decoupling capacitor. In Fixed High Supply (FHS) mode, this pin must be pulled HIGH with a 1 M $\Omega$ resistor to V <sub>DD</sub> .                                           |

| F6     | V <sub>AUX</sub>    | PWR  | auxiliary supply output. This pin provides a configurable voltage source for supplying other devices. <u>Section 6.3</u> describes this functionality. A separate Application Note ( <u>Ref. 2</u> ) provides more detailed usage information.                    |

| GROUN  | D                   |      |                                                                                                                                                                                                                                                                   |

| D6     | V <sub>SS</sub>     | GND  | analog/digital ground. Connect to the system GND.                                                                                                                                                                                                                 |

Table 2 D allocation table

© NXP B.V. 2017. All rights reserved.

| Bump   | Symbol  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONFIG | URATION |      | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| D1     | WP      | DI   | write-protect pin. This pin is used to prevent inadvertent writes to the EEPROM array. When connected to GND, the device is write protected. When connected to $V_{\text{DD}(IO)}$ , the device is not write protected.                                                                                                                                                                                                                                                                        |

| A2     | WRS     | DI   | wide-range supply pin. This pin configures the supply mode of the device. When connected to $V_{DD(IO)}$ , the chosen supply mode is the Wide Range Supply mode. When connected to GND, the chosen supply mode is the Fixed High Supply mode. In this latter mode, a higher minimum voltage is required on $V_{DD}$ , as described in <u>Section 6.4</u> .                                                                                                                                     |

| CONTR  | OL      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A6     | WAKE    | DI   | wake-up/power-down control input. To disable this functionality, the WAKE pin must be connected to GND. The SPI slave chip select input can then be used to wake up the device. To enable the WAKE functionality, the WAKE pin must be actively driven and may not be left unconnected nor floating. The input voltage level is referenced to $V_{DD}$ .                                                                                                                                       |

| SPI    |         |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A1     | CS      | DI   | SPI slave chip select. Asserting the $\overline{CS}$ pin selects the device. When the device is deselected, the SPI SO output pin is in a HIGH impedance state. Commands issued to the device are not accepted.A HIGH to LOW transition on the $\overline{CS}$ pin initiates an operation, a LOW to HIGH transition ends an operation.For communication, the signaling level is referenced to V <sub>DD(IO)</sub> For waking up the device, the input level is referenced to V <sub>DD</sub> . |

| E1     | SO      | DO   | SPI slave serial data output. The SO pin is used to shift data out from the device. Data on the SO pin is always clocked out on the falling edge of SCK. The SO pin is in a high impedance state whenever the device is not selected. The signaling level is referenced to $V_{DD(IO)}$ .For EMI, it is required to pull-up the SO line at some place in the system: either the SPI master has an internal weak pull-up, either an external pull-up resistor is required.                      |

| F1     | SI      | DI   | SPI slave serial data input. The SI pin is used the shift opcodes, addresses and data into the device and latched on the rising edge of SCK. The signaling level is referenced to $V_{DD(IO)}$ .                                                                                                                                                                                                                                                                                               |

| B1     | SCK     | DI   | SPI clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| C1     | HOLD    | DI   | SPI HOLD. The $\overline{HOLD}$ pin can be used to pause an on-<br>going SPI transaction. More information on usage can be<br>found in <u>Section 6.1.1</u> . The signaling level is referenced<br>to V <sub>DD(IO)</sub> . To disable this functionality, the $\overline{HOLD}$ pin must<br>be connected to V <sub>DD(IO)</sub> .                                                                                                                                                             |

### 6 Functional description

### 6.1 SPI interface

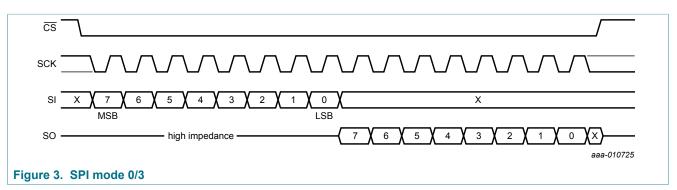

The NXP NXH5104 acts as a slave device on the Serial Peripheral Interface (SPI) bus. It supports mode 0 (0,0) and mode 3 (1,1) transfers at standard clock speeds up to 5 MHz. It also supports high-speed operation up to 10 MHz when  $V_{DD(IO)}$  exceeds 1.8 V. Incoming data on the SI pin is latched on the rising edge of SCK. Outgoing data output on the SO pin is output on the falling edge of SCK. A leading or trailing falling edge of SCK is discarded.

Transactions are byte-oriented, counting an integer multiple of 8-bit words, whereby the Most Significant Bit (MSB) is transmitted first, Least Significant Bit (LSB) last. The master initiates a transaction by asserting  $\overline{CS}$  low and terminates it by de-asserting  $\overline{CS}$  high, even if it is a single-byte command.

The command byte is the first byte transmitted by the master and received by the slave on the SI line after asserting low the  $\overline{CS}$  pin.

### 6.1.1 SPI transaction hold

A HOLD input is provided as an extension to the SPI interface. It enables the host to suspend an ongoing transaction such as performing a high priority transaction with another slave device.

While  $\overline{\text{HOLD}}$  is asserted low, the device releases the SO line to a high impedance state and discards any transitions on SCK and SI lines. The  $\overline{\text{CS}}$  line however, must remain asserted. The suspended transaction resumes when the  $\overline{\text{HOLD}}$  input is de-asserted high.

| cs                        |                                                          | ///////////////////               |                           |                                     |                                      |

|---------------------------|----------------------------------------------------------|-----------------------------------|---------------------------|-------------------------------------|--------------------------------------|

|                           |                                                          | <i></i>                           |                           |                                     |                                      |

| sск <sub>√∕</sub> ∕∕∕∕∕∕  |                                                          |                                   |                           |                                     |                                      |

| si <u>0 7 7 6 7</u>       | 5 <b>X</b> 4 <b>X</b> 3 <b>X</b> 2 <b>X</b> 1 <b>X</b> 0 | XX                                | <u> </u>                  | 5 4 3 2                             |                                      |

| so <u>0 7 6 </u>          | 5 <b>X</b> 4 <b>X</b> 3 <b>X</b> 2 <b>X</b> 1 <b>X</b> 0 | <b>(7)</b>                        | <u>    (  7  )(  6  )</u> | 5 4 3 2                             | <u>1</u> (0) (X)—                    |

| /                         | - ongoing transaction ————                               | —/— suspended –                   | -/                        | 2 <sup>nd</sup> part of transaction |                                      |

| Figure 4. SPI transaction | hold                                                     |                                   |                           |                                     | aaa-010726                           |

| NXH5104                   | All information provide                                  | ed in this document is subject to | legal disclaimers.        |                                     | © NXP B.V. 2017. All rights reserved |

The HOLD input must be asserted low when SCK is stable and must be de-asserted during the same clock phase as it was asserted.

The HOLD input must be asserted after the last bit of a byte has been asserted on SI (see Figure 4).

If this feature is not used, the  $\overline{HOLD}$  input must be tied to  $V_{DD(IO)}$ .

### 6.1.2 Overview commands

The NXP NXH5104 uses 8-bit commands. For some of these commands, the device needs time to execute the action during which no new commands can be serviced. These commands are referred to as Extended Operation Commands (EOC). For instance, the WRITE command is an EOC. The WRITE command triggers an erase-program cycle during which other commands are not serviced.

The host must poll readiness by issuing RDSR commands and must observe whether the  $\overline{\text{RDY}}$  bit is asserted low.

If an invalid command byte is received, the command is ignored and the SO line remains in a high impedance state.

There are two types of write accesses: volatile and persistent. When a setting is written volatile, the change takes effect, but this setting reinitializes with its default value after a device power cycle. When a setting is written persistent, the change takes effect and the updated value is automatically loaded after a device power cycle.

| Command | Value | Description                                                           | EOC | Reference |

|---------|-------|-----------------------------------------------------------------------|-----|-----------|

| WRSR    | 01h   | write status register                                                 | yes | Table 12  |

| WRITE   | 02h   | write data bytes to memory array                                      | yes | Table 7   |

| READ    | 03h   | read data bytes from memory array                                     | no  | Table 4   |

| WRDI    | 04h   | disable write operations                                              | no  | Table 9   |

| RDSR    | 05h   | read status register                                                  | no  | Table 17  |

| WREN    | 06h   | enable write operations                                               | no  | Table 8   |

| RDID    | 83h   | read device ID and unique ID                                          | no  | Table 18  |

| RDR     | F9h   | read response                                                         | no  | Table 20  |

| STBY    | E0h   | standby command                                                       | yes | Table 26  |

| SLEEP   | E1h   | sleep command                                                         | yes | Table 25  |

| PWDN    | E2h   | power-down command                                                    | yes | Table 24  |

| VWXSR   | E3h   | volatile write of extended status register                            | yes | Table 15  |

| PWXSR   | E4h   | persistent write of extended status register                          | yes | Table 16  |

| VAUXVW  | E5h   | volatile write of auxiliary supply configuration register (VAUXCFG)   | yes | Table 27  |

| VAUXPW  | E6h   | persistent write of auxiliary supply configuration register (VAUXCFG) | yes | Table 28  |

### Table 3. SPI command set overview

# NXH5104

### 4 Mbit Serial SPI EEPROM

| Command | Value | Description                                                                                                                                                                    | EOC | Reference       |

|---------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|

| VAUXR   | E7h   | prepares a read auxiliary supply<br>configuration register (VAUXCFG). To<br>read the auxiliary supply configuration<br>register value, use the RDR (Read<br>Response) command. | yes | <u>Table 29</u> |

| WOIR    | E8h   | prepares a read of wear out status<br>register. To read the wear-out status<br>register value, use the RDR (Read<br>Response) command.                                         | yes | Table 21        |

| RVDD    | E9h   | prepares a read of the V <sub>DD</sub> supply<br>voltage level. To read back the prepared<br>data, use the RDR (Read Response)<br>command.                                     | yes | Table 23        |

### 6.1.3 SPI read operation (READ)

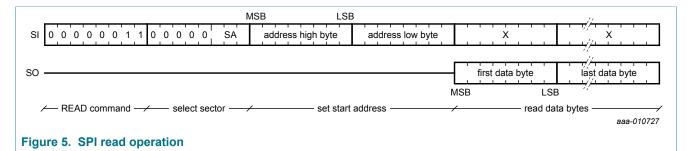

A read operation of the memory array is initiated when the SPI master issues a READ command, followed by the sector byte and the 16-bit address. The latter defines the offset within the chosen sector.

The NXP NXH5104 contains eight sectors; hence the SA field contains 3 bits. The remaining most-significant bits of the sector byte must be zero!

Immediately following the last address byte (READ command), the device starts driving the SO line. It transmits consecutive data bytes read from the memory array, starting at the selected memory location, until the  $\overline{CS}$  input is asserted HIGH.

During read operations, the internal address counter auto-increments. What happens at a sector boundary depends on the setting of the RAWMODE field of the Extended Status register (see Table 14). When RAWSEC is chosen, the address automatically wraps at the sector boundary. When RAWFULL is chosen, the address automatically increments beyond the sector boundary to the next sector.

If a previous program operation is in progress, the memory read/write operation is prohibited (treated as an invalid command).

A READ command is only allowed on sectors which are in Power-up mode.

| Table 4. | Table 4. SPI READ command |         |       |                             |  |  |

|----------|---------------------------|---------|-------|-----------------------------|--|--|

| Byte     | Access                    | Command | Value | Description                 |  |  |

| 0        | W                         | READ    | 03h   | read data bytes from memory |  |  |

| 1:3      | W                         | SPI_AR  | -     | address register            |  |  |

| Byte | Access | Command | Value | Description |

|------|--------|---------|-------|-------------|

| 4:   | R      | DATA    | -     | data bytes  |

### 6.1.4 SPI write protection

To prevent inadvertent writes to the memory array and Status register, software and hardware protection mechanisms are included in the device.

The following protection is available for writing to the EEPROM memory array:

- The write enable bit (WEN) must be first set by issuing a write enable (WREN) command. It is cleared by issuing a write disable (WRDI) command. The write enable bit is also automatically cleared at power-up, after each WRITE command, and when the status register is written (WRSR or PWXSR).

- The corresponding sector protection bit SP(n) must be disabled.

- If a program operation is still in progress ( $\overline{RDY} = 1$ ), writes are prohibited.

| RDY | WEN | WREN | WP | SP(n) | WRITE command <sup>[1]</sup> |

|-----|-----|------|----|-------|------------------------------|

| 1   | Х   | Х    | Х  | Х     | prohibited                   |

| Х   | 0   | Х    | Х  | Х     | prohibited                   |

| х   | Х   | Х    | Х  | 1     | prohibited                   |

| 0   | 1   | Х    | Х  | 0     | allowed                      |

### Table 5. SPI memory array write protection

[1] When prohibited, the WRITE command is treated as an invalid command.

The following protection is available for writing to the status register:

- The write enable bit (WEN) must be set by issuing a write enable (WREN) command. It is cleared by issuing a write disable (WRDI) command. It is also automatically cleared at power-up, after each WRITE instruction, and when the status register is written (WRSR or PWXSR).

- If the nonvolatile WPEN bit is set and the WP input is asserted low, hardware write protection is enabled.

- If a program operation is still in progress (RDY = 1), writes are discarded.

| RDY | WEN | WPEN | WP | SP(n) | WRSR or PWXSR commands <sup>[1]</sup> |

|-----|-----|------|----|-------|---------------------------------------|

| 1   | Х   | Х    | Х  | Х     | prohibited                            |

| х   | 0   | Х    | Х  | Х     | prohibited                            |

| 0   | 1   | 1    | 0  | Х     | prohibited                            |

| 0   | 1   | 0    | Х  | Х     | allowed                               |

| 0   | 1   | Х    | 1  | Х     | allowed                               |

#### Table 6. SPI Status register write protection

[1] When prohibited, the WRSR and PWXSR commands are treated as invalid commands.

Because the granularity of the write protection mechanisms is sector-based, it is recommended to store different types of data (e.g. firmware instructions versus data logging) in separate sectors.

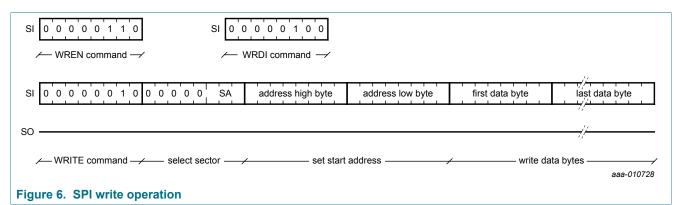

### 6.1.5 SPI write operation (WRITE)

Since the write enable bit (WEN) is cleared after each write operation, a write enable (WREN) command must precede each WRITE command. The write enable (WREN) command and write disable command (WRDI) are single-byte commands.

A write operation is initiated when the master issues a WRITE command followed by 3 bytes. The first byte selects the sector, and the remaining 2 bytes set the 16-bit address pointer (offset within the sector).

Following the address bytes, any number of data bytes between 1 and 256 transmitted by the master, are written to the page write buffer. The write transfer is completed by asserting  $\overline{CS}$  high, upon which an internal self-timed program cycle is started.

The eight lower bits of the address counter, corresponding to the offset within the page buffer, auto-increment after each byte is written via SPI. Hence, the current address wraps at page boundary. If more than 256 data bytes are transferred via SPI, all bytes from byte 256 are discarded.

A write operation must be preceded by setting the write enable bit (see previous section).

A write operation is initiated when the master issues a WRITE command byte followed by the sector byte and the 16 bit (2 byte) address. The latter defines the offset within the chosen sector.

The NXP NXH5104 contains eight sectors; hence the SA field contains 3 bit. The remaining most significant bits of the sector byte must be logic 0!

If more than 256 data bytes are transferred through the SPI slave interface, these additional bytes are discarded.

| Byte | Access | Command/Data | Value | Description                 |

|------|--------|--------------|-------|-----------------------------|

| 0    | W      | WRITE        | 02h   | write data bytes to memory. |

| 1:3  | W      | SPI_AR       | -     | address register.           |

| 4:   | R      | DATA         | -     | data bytes.                 |

| Table 7. SPI | WRITE command: | write data b | oytes to memory |

|--------------|----------------|--------------|-----------------|

|--------------|----------------|--------------|-----------------|

#### Table 8. SPI WREN command: enable write operations

| Byte | Access | Command/Data | Value | Description             |

|------|--------|--------------|-------|-------------------------|

| 0    | W      | WREN         | 06h   | enable write operations |

#### Table 9. SPI WRDI command: disable write operations

| Byte | Access | Command/Data | Value | Description              |

|------|--------|--------------|-------|--------------------------|

| 0    | W      | WRDI         | 04h   | disable write operations |

#### Table 10. SPI address register (SPI\_AR)

| Bits  | Access<br>[1] | Field | Value  | Description                                             |

|-------|---------------|-------|--------|---------------------------------------------------------|

| 23:19 | W             | -     | 00000b | fixed SPI prefix. These bits should be written as zeros |

| 18:16 | W             | SA_0  | 000b   | sector address bits. Sector 0                           |

|       |               | SA_1  | 001b   | sector address bits. Sector 1                           |

|       |               | SA_2  | 010b   | sector address bits. Sector 2                           |

|       |               | SA_3  | 011b   | sector address bits. Sector 3                           |

|       |               | SA_4  | 100b   | sector address bits. Sector 4                           |

|       |               | SA_5  | 101b   | sector address bits. Sector 5                           |

|       |               | SA_6  | 110b   | sector address bits. Sector 6                           |

|       |               | SA_7  | 111b   | sector address bits. Sector 7                           |

| 15:8  | W             | AH    | -      | high address bit                                        |

| 7:0   | W             | AL    | -      | low address bit                                         |

[1] W = volatile writable.

A write operation consists out of an erase cycle followed by a programming cycle. To guarantee the endurance, an adaptive trimming algorithm checks whether the erase cycle was successful. If not, another erase cycle is started at a higher (internal) supply level. This process leads to a longer programming time, which can be considerably higher than the typical programming time (see <u>Table 36</u>). It is highly recommended to poll completion through the RDSR command: as soon as the write operation is completed, the host can continue and issue new commands.

#### 6.1.6 SPI status register

The Status Register (SR) is accessible through the RDSR and WRSR instructions. It can be read at any time to poll the device RDY status bit. The other bits of the Status Register are not updated when the RDY is indicating busy state. They can be overwritten using the WRSR instruction. Under applicable write protection conditions (see Section 6.1.4), the WRSR command initiates a write of the Status Register

The status register can be accessed as part of the Extended Status Register (XSR).

| Table 11. SPI status register |                          |         |                      |                                         |  |  |

|-------------------------------|--------------------------|---------|----------------------|-----------------------------------------|--|--|

| Bits                          | Access<br><sup>[1]</sup> | Field   | Value <sup>[2]</sup> | Description                             |  |  |

| -                             | R/P                      | SR      | (00h)                | status register.                        |  |  |

| 7                             | R/P                      | WPEN    | (0b)                 | write protect enable bit.               |  |  |

| 6:4                           | R                        | -       | (000b)               | (reserved).                             |  |  |

| 3:2                           | R/P                      | SP      | (00b)                | sector protection.                      |  |  |

|                               |                          | SPNONE  | 00b                  | sector protection disabled.             |  |  |

|                               |                          | SPQUART | 01b                  | protect sector 6 and 7 (upper quarter). |  |  |

|                               |                          | SPHALF  | 10b                  | protect sectors 4 to 7 (upper half).    |  |  |

|                               |                          | SPALL   | 11b                  | protect all sectors.                    |  |  |

| 1                             | R <sup>[3]</sup>         | WEN     | (0b)                 | write enable bit.                       |  |  |

| 0                             | R                        | RDY     | (0b)                 | ready status bit.                       |  |  |

[1] R = readable, P = persistent writable.

[2] Default manufacturing values between brackets.

[3] The WREN/WRDI commands set/clear the WEN bit.

### Table 12. SPI write status register

| Byte | Access | Command/Data | Value | Description            |  |

|------|--------|--------------|-------|------------------------|--|

| 0    | W      | WRSR         | 01h   | write status register. |  |

| 1    | Р      | SR           | -     | status register.       |  |

### Table 13. SPI read status register

| Byte | Access | Command/Data | Value | Description           |

|------|--------|--------------|-------|-----------------------|

| 0    | W      | RDSR         | 05h   | read status register. |

| 1    | R      | SR           | -     | status register.      |

### 6.1.7 SPI extended status register

An extended, 32-bit status register (XSR) can be read using the same RDSR command. The upper (first) byte corresponds to the 8-bit status register (SR). Reading beyond this first byte provides access to extended features/settings of the device.

Two functions support writing to the Extended Status Register:

- VWXSR: Volatile Write of the XSR. Only the fields indicated with W are writing.

- PWXSR: Persistent Write of the XSR. Only the fields indicated with P are writing.

Manufacturing default R/W/P fields are indicated (between brackets). A persistent write can configure the device in a mode which is unrecoverable. It is recommended that the host programs the preferred settings once at initial start-up.

| Bits  | Access | extended status re | Value <sup>[2]</sup> | Description                       |

|-------|--------|--------------------|----------------------|-----------------------------------|

|       | [1]    |                    |                      |                                   |

| -     | R/W/P  | XSR                | (0010h)              | extended status register          |

| 31:24 | R/P    | SR                 | (00h)                | status register                   |

| 23:16 | R/W/P  | SPD                | (00h)                | sector power-down                 |

|       |        | bit 23             | 1b                   | power-down sector 7               |

|       |        | bit 22             | 1b                   | power-down sector 6               |

|       |        | bit 21             | 1b                   | power-down sector 5               |

|       |        | bit 20             | 1b                   | power-down sector 4               |

|       |        | bit 19             | 1b                   | power-down sector 3               |

|       |        | bit 18             | 1b                   | power-down sector 2               |

|       |        | bit 17             | 1b                   | power-down sector 1               |

|       |        | bit 16             | 1b                   | power-down sector 0               |

| 15:14 | W      | PMI                | (00b)                | power mode indicator              |

|       |        | PMSB               | 00b                  | standby.                          |

|       |        | PMS                | 01b                  | sleep                             |

| 13:12 | R/W/P  | IOMODE             | (00b)                | select V <sub>DD(IO)</sub> mode   |

|       |        |                    | 0xb                  | $V_{DD(IO)} = V_{DD}.$            |

|       |        |                    | 10b                  | $V_{DD(IO)}$ is fixed, > 1.5 V    |

|       |        |                    | 11b                  | $V_{DD(IO)}$ is fixed, < 1.5 V    |

| 11:8  | R      | -                  | (00b)                | (reserved).                       |

| 7     | R      | WOI                | (0b)                 | wear-out indication               |

|       |        | WOIOK              | 0b                   | no wear-out, indication OK        |

|       |        | WOINOK             | 1b                   | wear-out, indication not OK       |

| 6:5   | R      | PSTAT              | (00b)                | result of last program operation  |

|       |        | PNONE              | 00b                  | no program cycle has been started |

|       |        | PSUCCESS           | 01b                  | program cycle succeeded           |

|       |        | PABORT             | 10b                  | program cycle aborted             |

|       |        | PWORN              | 11b                  | page is worn out                  |

| 4     | R/W/P  | RAWMODE            | (1b)                 | read address wrapping mode        |

|       |        | RAWSEC             | 0b                   | wrap address at sector boundary   |

|       |        | RAWFULL            | 1b                   | read across sector boundary       |

| 3     | R/W/P  | WPPOL              | (0b)                 | write protect input polarity      |

|       |        | PLOW               | 0b                   | active low polarity               |

|       |        | PHIGH              | 1b                   | active high polarity              |

| 2:0   | R      | -                  | (000b)               | (reserved)                        |

|       |        |                    |                      |                                   |

### Table 14 CDI VCD: extended status register

R = readable, W = volatile writable, P = persistent writable.

Default manufacturing values between brackets.

NXH5104 **Product data sheet COMPANY PUBLIC**

Table 15. SPI VWXSR command: volatile write extended status register

| Byte | Access | Command/Data | Value | Description                              |

|------|--------|--------------|-------|------------------------------------------|

| 0    | W      | VWXSR        | E3h   | volatile write extended status register. |

| 1:4  | W      | XSR          | -     | extended status register.                |

Table 16. SPI PWXSR command: persistent write extended status register

| Byte | Access | Command/Data | Value | Description                                |

|------|--------|--------------|-------|--------------------------------------------|

| 0    | W      | PWXSR        | E4h   | persistent write extended status register. |

| 1:4  | W      | XSR          | -     | extended status register.                  |

### Table 17. SPI read status register

| Byte | Access | Command/Data | Value | Description               |  |

|------|--------|--------------|-------|---------------------------|--|

| 0    | W      | RDSR         | 05h   | read status register.     |  |

| 1:4  | R      | XSR          | -     | extended status register. |  |

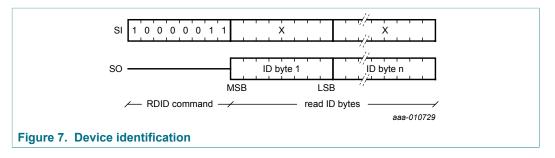

### 6.1.8 SPI device identification

Device identification data comprises a fixed device ID as well as a unique ID. The identifiers can be retrieved using the RDID command. This command can only be applied if sector 0 is powered-up.

| Table 18. | <b>SPI RDID</b> | command: re | ead device | ID and | unique ID |

|-----------|-----------------|-------------|------------|--------|-----------|

|-----------|-----------------|-------------|------------|--------|-----------|

| Byte | Access | Command/Data | Value     | Description                  |

|------|--------|--------------|-----------|------------------------------|

| 0    | W      | RDID         | 83h       | read device ID and unique ID |

| 1:3  | R      | DEVID        | (001010h) | device ID                    |

| 4:15 | R      | UID          | -         | unique ID.                   |

### Table 19. SPI device ID

| Bits  | Access | Field | Value     | Description                  |

|-------|--------|-------|-----------|------------------------------|

| -     | R      | DEVID | (001010h) | device ID                    |

| 23:12 | R      | MFG   | (001h)    | manufacturing identification |

| Bits | Access | Field | Value       | Description         |

|------|--------|-------|-------------|---------------------|

| 11:3 | R      | PART  | (00000010b) | part identification |

| 2:0  | R      | REV   | (000b)      | revision number     |

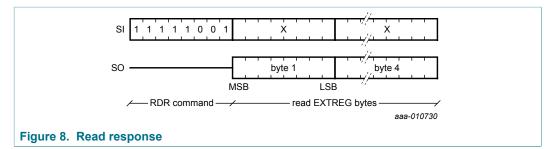

### 6.1.9 SPI read response (RDR)

Reads a 32-bit register after the extended commands: VAUXR or WOIR.

Table 20. SPI RDR command: read response

| Byte | Access | Command/Data | Value | Description             |

|------|--------|--------------|-------|-------------------------|

| 0    | W      | RDR          | F9h   | read extended register. |

| 1:4  | R      | EXTREG       | -     | extended register.      |

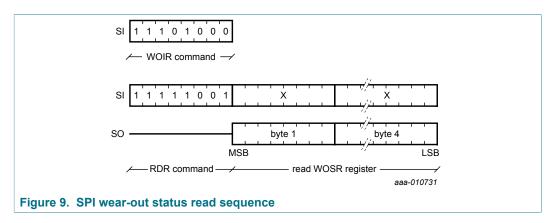

### 6.1.10 SPI wear-out status register (WOIR)

If the bit WOI in the XSR is set, a part of the EEPROM has reached its maximal endurance level. The host can request more details by consulting the Wear-Out Status Register (WOSR).

The register gives details informing which sector has reached the maximal endurance level.

The command WOIR prepares the wear-out status register.

The host must poll readiness by issuing RDSR commands and observing that the  $\overline{RDY}$  bit is asserted low. To read the wear-out status register value, use RDR.

| Bits  | Access | Field  | Value     | Description                         |

|-------|--------|--------|-----------|-------------------------------------|

| -     | R      | WOSR   | -         | wear-out status register.           |

| 31:24 | R      | SPD    | (00h)     | wear-out indicator.                 |

|       |        | bit 31 | 1b        | wear-out of sector 7 when set to 1. |

|       |        | bit 30 | 1b        | wear-out of sector 6 when set to 1. |

|       |        | bit 29 | 1b        | wear-out of sector 5 when set to 1. |

|       |        | bit 28 | 1b        | wear-out of sector 4 when set to 1. |

|       |        | bit 27 | 1b        | wear-out of sector 3 when set to 1. |

|       |        | bit 26 | 1b        | wear-out of sector 2 when set to 1. |

|       |        | bit 25 | 1b        | wear-out of sector 1 when set to 1. |

|       |        | bit 24 | 1b        | wear-out of sector 0 when set to 1. |

| 23:0  | R      | -      | undefined | (reserved).                         |

#### .....

### Table 22. SPI RDR command: read response

| Byte | Access | Command/Data | Value | Description                                                                                           |

|------|--------|--------------|-------|-------------------------------------------------------------------------------------------------------|

| 0    | W      | WOIR         | E8h   | Prepares a read of the wear-out status register. To read the wear-out status register value, use RDR. |

When writing a single byte, the full 32-bit data word containing this byte is cycled (erased and programmed) and eventually wears out. However, the internal adaptive algorithm for guaranteeing the endurance works on pages. So, when a user wears out a word by only repeatedly writing to only this location, it effectively wears out the full 128-byte page.

### 6.1.11 SPI read of the V<sub>DD</sub> supply (RVDD)

After the device receives the SPI read of the V<sub>DD</sub> supply command, a response can be eventually read in the response register.

The command RVDD prepares the read of the  $V_{DD}$  supply.

The host must poll readiness by issuing RDSR commands and observing whether the RDY bit is asserted low.

To read the value of the  $V_{DD}$  supply, use RDR.

| Bits | Access | Field      | Value | Description                          |

|------|--------|------------|-------|--------------------------------------|

| 7:4  | R      | RVDD       | (0h)  | V <sub>DD</sub> supply voltage level |

|      |        |            | 0h    | 0.850 V - 0.950 V                    |

|      |        |            | 1h    | 0.925 V - 1.025 V                    |

|      |        |            | 2h    | 1.000 V - 1.100 V                    |

|      |        |            | 3h    | 1.050 V - 1.150 V                    |

|      |        |            | 4h    | 1.150 V - 1.250 V                    |

|      |        |            | 5h    | 1.200 V - 1.300 V                    |

|      |        |            | 6h    | 1.250 V - 1.350 V                    |

|      |        |            | 7h    | 1.350 V - 1.450 V                    |

|      |        |            | 8h    | 1.400 V - 1.500 V                    |

|      |        |            | 9h    | 1.500 V - 1.600 V                    |

|      |        |            | Ah    | 1.550 V - 1.650 V                    |

|      |        |            | Bh    | 1.650 V - 1.750 V                    |

|      |        |            | Ch    | 1.700 V - 1.800 V                    |

|      |        |            | Dh    | 1.800 V - 1.900 V                    |

|      |        |            | Eh    | 1.850 V - 1.950 V                    |

|      |        |            | Fh    | 1.900 V - 2.000 V                    |

| 3:0  | -      | (reserved) | (0h)  | -                                    |

#### Table 22 SDI read of the V

### 6.2 Power modes

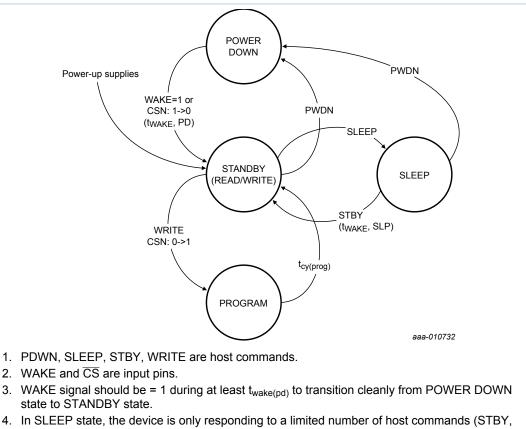

In order to conserve power, the NXH5104 features scalable power modes as illustrated below.

- PWDN, and RDSR). The V<sub>aux</sub> supply is not available in this mode.

5. Transition to PROGRAM state occurs after the host reverts CS to high and the device is

- presented with the complete page or word to be written.

Program cycle time t<sub>prog</sub> depends on whether a full 256 Byte sector or half sector is being written.

Figure 10. Power modes

### 6.2.1 Boot

When  $V_{DD}$  is supplied, the device by default boots into the STANDBY mode. To move the device into Sleep or Power-down mode, issue the Sleep or Power-down command over the SPI interface.

### 6.2.2 Power-down

The device features a Power-down mode with very low current consumption. All internal reference circuits are disabled in this mode, internally generated supplies are switched off, and output pins are in a high impedance state. The host controls the Power-down mode by using either a dedicated WAKE pin or the  $\overline{CS}$  pin. Both pins are plain inputs referenced to V<sub>DD</sub> and must not float.

### Wake up using the $\overline{CS}$ pin

When the  $\overline{CS}$  pin is asserted low at V<sub>DD</sub> start-up, the device starts ramping-up its supplies. After the wake-up time t<sub>wake</sub>, the supplies are stable and the device becomes active and ready to process requests. To test it, poll the RDY bit.

When a 1 to 0 transition is detected on the  $\overline{CS}$  pin, the device ramps-up its supplies. After wake-up time t<sub>wake</sub>, the supplies are stable and the device becomes active and ready to process requests. The RDY bit can be used to test that it is ready. This detection mechanism becomes active 1 ms after applying the V<sub>DD</sub>.

### Wake-up using the WAKE pin

If the WAKE pin is de-asserted (low) at start-up, the device remains in Power-down mode until the WAKE pin is asserted high.

When the WAKE pin is asserted high, the device ramps-up its supplies. After wakeup time  $t_{wake(pd)}$ , the supplies are stable and the device becomes active and ready to process requests. The RDY bit can be used to test that it is ready.

Note: The wake must be asserted low again before reverting to the Power-down mode.

When a PDWN command is issued, the device enters Power-down mode. If a program cycle is still in progress, the PDWN command is ignored. The  $\overline{\text{RDY}}$  bit can first be polled to check if the command is valid.

### Table 24. SPI PDWN: power-down command

| Byte | Access | Command | Value | Description         |

|------|--------|---------|-------|---------------------|

| 0    | W      | PWDN    | E2h   | power-down command. |

### 6.2.3 Sleep

Sleep mode is a power-saving mode in which the EEPROM array is powered down. However, internally generated supplies are maintained and the serial interfaces remainresponsive to a limited set of host commands. The Auxiliary supply voltage (V<sub>aux</sub>) cannotbe maintained. For more information, see the Application Note: V<sub>AUX</sub> - Auxiliary voltage supply (<u>Ref. 2</u>). This mode enables faster activation ( $t_{wake(sleep)}$ ) compared to Sleep and Power-down modes. When a SLEEP command is issued, the device enters Sleep mode. If a program cycle is still in progress, the SLEEP command is ignored. The RDY bit can first be polled to check if the command is valid.

When in Sleep mode, the device only responds to STBY, RDSR and PDWN commands. The  $V_{aux}$  supply is not available in Sleep mode.

| Table 25 | Table 25. SPI SLEEP: sleep command |         |       |                |  |  |  |

|----------|------------------------------------|---------|-------|----------------|--|--|--|

| Byte     | Access                             | Command | Value | Description    |  |  |  |

| 0        | W                                  | SLEEP   | E1h   | sleep command. |  |  |  |

### 6.2.4 Standby

In Standby mode, the EEPROM remains powered and ready to process read/write requests.

When an STBY command is issued in Sleep mode, the device ramps-up its internal supplies. After wake-up time  $t_{wake(sleep)}$ , the supplies are stable and the enabled EEPROM array sectors are switched to Power-on state. The enabled EEPROM array

sectors are configured in the XSR register (non-user area). The device becomes active and ready to process read/write requests. Polling the  $\overline{\text{RDY}}$  bit can be used to test it. Wake-up from Sleep mode is significantly faster ( $t_{wake(sleep)}$ ) as it does not involve rampup of the supplies. It does involve switching the enabled EEPROM sectors to the Poweron state.

In STANDBY mode, the EEPROM array can be read and written with READ and WRITE commands.

| Table 26 | SPI         | STRY. | standby | command  |

|----------|-------------|-------|---------|----------|

|          | <b>J</b> FI | 5151. | Stanuby | Commania |

| Table 20. Of FOTD1. Standby command |        |         |       |                  |  |  |

|-------------------------------------|--------|---------|-------|------------------|--|--|

| Byte                                | Access | Command | Value | Description      |  |  |

| 0                                   | W      | STBY    | E0h   | standby command. |  |  |

### 6.3 Auxiliary supply

The auxiliary supply voltage ( $V_{aux}$ ) is a configurable DC-to-DC supply, generated from the primary supply voltage ( $V_{DD}$ ) for supplying an external auxiliary component. It is configured using the VAUXVW, VAUXPW and VAUXR commands that configure the VAUXCFG register.

For performing a volatile write (VAUXVW) of the  $V_{AUX}$  configuration register, no preceding WREN command is required. If there is a persistent write (VAUXPW), a preceding WREN command is required.

| Byte |   | Command/Data | Value | Description                                    |

|------|---|--------------|-------|------------------------------------------------|

| 0    | W | VAUXVW       | E5h   | volatile write auxiliary supply configuration. |

| 1:4  | W | VAUXCFG      | -     | auxiliary supply configuration register.       |

### Table 27. SPI VAUXVW command: volatile write auxiliary supply configuration

#### Table 28. SPI VAUXPW command: persistent write auxiliary supply configuration

| Byte | Access | Command/Data | Value | Description                                                                                                                                                     |

|------|--------|--------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | W      | VAUXPW       | E6h   | persistent write auxiliary supply<br>configuration register. Persistent write of<br>the configuration register which is used<br>for initialization after reset. |

| 1:4  | Р      | VAUXCFG      | -     | auxiliary supply configuration register.                                                                                                                        |

#### Table 29. SPI VAUXR command: read auxiliary supply configuration

| Byte | Access | Command/Data | Value | Description                                                                                                          |

|------|--------|--------------|-------|----------------------------------------------------------------------------------------------------------------------|

| 0    | W      | VAUXR        | E7h   | prepares a read auxiliary supply<br>register. To read the auxiliary supply<br>configuration register value, use RDR. |

| Bits  | Access | Field      | Value  | Description                                |

|-------|--------|------------|--------|--------------------------------------------|

| 31:17 | -      | -          | -      | (reserved)                                 |

| 16    | R/W/P  | VAUXEN     | (0b)   | auxiliary supply enable                    |

|       |        | VAUXEN_DIS | 0b     | disabled                                   |

|       |        | VAUXEN_EN  | 1b     | enabled.                                   |

| 15    | R/W/P  | VAUXBY     | (0b)   | auxiliary supply bypass mode               |

|       |        | VAUXBY_DIS | 0b     | disabled                                   |

|       |        | VAUXBY_EN  | 1b     | enabled                                    |

| 14    | R/W/P  | VAUXRATIO  | (0b)   | auxiliary supply ratio setting             |

|       |        |            | 0b     | ratio 2                                    |

|       |        |            | 1b     | ratio 3                                    |

| 13    | -      | -          | -      | (reserved)                                 |

| 12:11 | R/W/P  | VAUXDS     | (00b)  | auxiliary supply drive strength            |

|       |        |            | 00b    | 1/4 of drive strength                      |

|       |        |            | 01b    | 2/4 of drive strength                      |

|       |        |            | 10b    | 3/4 of drive strength                      |

|       |        |            | 11b    | 4/4 of drive strength                      |

| 10:8  | R/W/P  | VAUXDF     | (000b) | auxiliary supply clock divider             |

|       |        |            | 000b   | maximum clock speed                        |

|       |        |            | 001b   | clock divided by 2                         |

|       |        |            | 010b   | clock divided by 4                         |

|       |        |            | 011b   | clock divided by 8                         |

|       |        |            | 100b   | clock divided by 16                        |

|       |        |            | 101b   | clock divided by 32                        |

|       |        |            | 110b   | clock divided by 64                        |

|       |        |            | 111b   | clock divided by 128                       |

| 7     | R/W/P  | VAUXREG    | (0b)   | auxiliary supply enable voltage regulation |

|       |        |            | 0b     | disabled (open loop).                      |

|       |        |            | 1b     | enabled (closed loop).                     |

| 6:0   | R/W/P  | VAUXV      | (0b)   | auxiliary supply comparator mode           |

|       |        |            | 00h    | minimum (1.5 V)                            |

|       |        |            | 7Fh    | maximum (3.3 V)                            |

#### Table 20 SPI auxilia

**Note:** Details of the  $V_{aux}$  principle and operation can be found in the separate application data note:  $V_{AUX}$  - Auxiliary voltage supply (Ref. 2).

### 6.4 Supply mode

There are two  $V_{\text{DD}}$  supply modes available. The Wide Range Supply pin (WRS) selects the supply mode.

If the supplied  $V_{DD}$  of the device is a regulated voltage always above 1.65 V, it is possible to use the Fixed High Supply (FHS) mode. In this mode, the DC-to-DC converter that is used to generate the EEPROM array voltage ( $V_{DD(EE)}$ ) is bypassed. The rise time of this supply is hence almost instantaneous, reducing the overall start-up time of the device by approximately 1.5 ms. For the actual values, refer to <u>Section 9</u>. To select the Fixed High Supply mode, the WRS pin must to be connected to GND.

If the minimum supplied V<sub>DD</sub> of the device cannot be guaranteed to be above 1.65 V, the Wide Range Supply mode can be used. To select the Wide Range Supply mode, the WRS pin must to be connected to  $V_{DD(IO)}$ .

### 6.5 Error-correcting code

The NXH5104 features an Error-Correcting Code (ECC) to improve reliability. It provides six parity bits for every 32 data bits so that a 38-bit word in memory represents four data bytes internally. Single bit read errors within a word are corrected.

Since the NXP NXH5104 supports byte level access, it is only allowed to write part of the four data bytes that make up a word. However, if a partial word is modified, the entire word is updated and endures a program cycle. To benefit from the qualified endurance optimally (500 000 program cycles), write entire words (multiples of 4 bytes at word boundaries) within a single transaction.

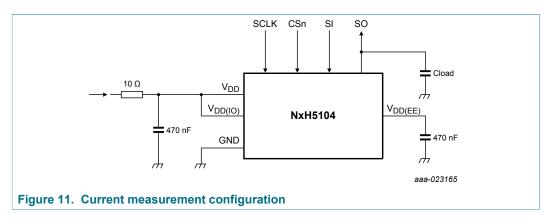

### 6.6 Current measurements

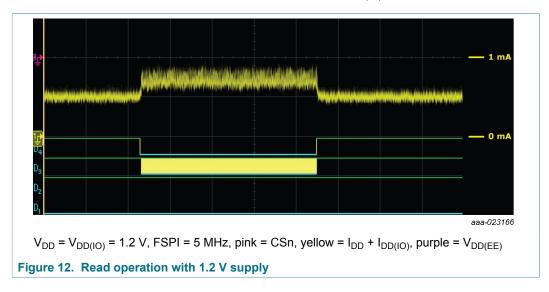

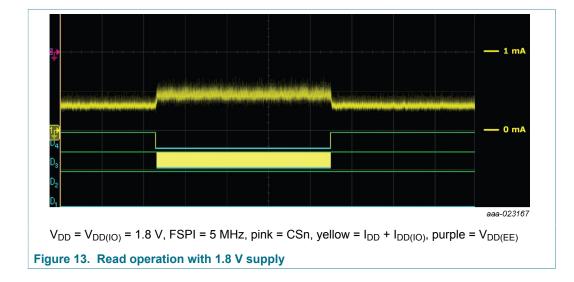

The most interesting modes impacting the current consumption of the NXP NXH5104 are the READ and the WRITE mode. Measurements performed for these modes are shown in this section. The current has been measured using a differential voltage amplifier across the 10  $\Omega$  resistor, as shown in the schematic. The scale for all following graphs is 1 mA/division.

### 6.6.1 Read

The following graphs depict a READ operation, with varying levels of supply. Take note that the capacitive load ( $C_{load}$ ) on the SO line dominates  $I_{DD(IO)}$ .

### 6.6.2 Write

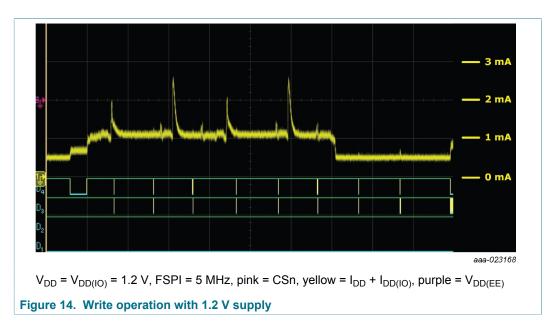

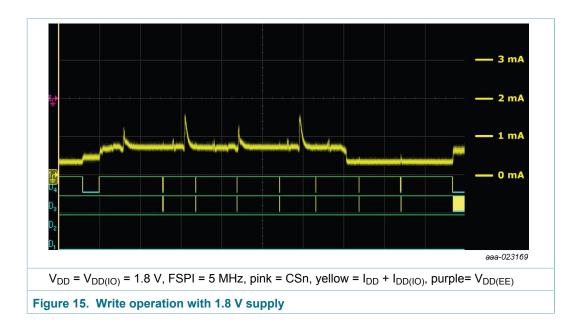

The following graphs depict a WRITE operation, with varying levels of supply.

#### **Limiting values** 7

### Table 31. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol              | Parameter                   | Conditions           |     | Min  | Max  | Unit |

|---------------------|-----------------------------|----------------------|-----|------|------|------|

| T <sub>stg</sub>    | storage temperature         |                      |     | -50  | +150 | °C   |

| V <sub>DD</sub>     | supply voltage              |                      | [1] | -0.5 | +2.4 | V    |

| V <sub>DD(IO)</sub> | input/output supply voltage |                      |     | -0.5 | +5.2 | V    |

| V <sub>aux</sub>    | auxiliary voltage           |                      |     | -0.5 | +5.2 | V    |

| V <sub>ESD</sub>    | electrostatic discharge     | human body model     | [2] | -    | 2    | kV   |

|                     | voltage                     | charged device model | [3] | -    | 500  | V    |

| l <sub>lu</sub>     | latch-up current            |                      | [4] | -    | ±100 | μA   |

Maximum voltage for a lifetime of 1 hour at 60 °C, with 0.01 % failure rate and 95 % confidence bound. In accordance with JESD22-A114. [1]

[2]

[3] [4] In accordance with JESD22-C101.

In accordance with JESD78.

### 7.1 Recommended operating conditions

#### Table 32. Operating conditions

| Symbol                   | Parameter                           | Conditions       |     | Min  | Тур      | Мах | Unit |

|--------------------------|-------------------------------------|------------------|-----|------|----------|-----|------|

| T <sub>oper</sub>        | operating temperature               |                  |     | -20  | +25      | +85 | °C   |

| V <sub>DD</sub>          | supply voltage                      |                  | [1] | 1.0  | 1.2      | 2.0 | V    |

| V <sub>DD(IO)</sub>      | input/output supply voltage         |                  |     | 1.0  | $V_{DD}$ | 2.6 | V    |

| V <sub>DD(IO)(1V2)</sub> | input/output supply voltage (1.2 V) | 1.2 V signalling |     | 1.08 | 1.2      | 1.9 | V    |

| V <sub>DD(IO)(1V8)</sub> | input/output supply voltage (1.8 V) | 1.8 V signalling |     | 1.62 | 1.8      | 2.6 | V    |

[1] During the READ and WRITE command execution the  $V_{DD}$  is allowed to dip to 0.9 V.

### 8 Static characteristics

| Symbol                | Parameter                  | Conditions          | Min | Тур  | Max | Unit |

|-----------------------|----------------------------|---------------------|-----|------|-----|------|

| Auxiliary             | r supply                   |                     |     |      |     |      |

| V <sub>aux</sub>      | auxiliary voltage          | regulation range    | 1.5 | 1.8  | 3.3 | V    |

|                       |                            | regulation step     | -   | 3.75 | -   | mV   |

| l <sub>aux(ext)</sub> | external auxiliary current | standby/active mode | -   | 0.75 | 2.0 | mA   |

|                       |                            | pass-through mode   | -   | -    | 2.0 | mA   |

### Table 34. Static characteristics-2

Current from V<sub>DD</sub>, excluding external current sourced through supply or I/O pads.

| Symbol                 | Parameter                         | Conditions                     |     | 1.2 V |     | 1.8 V |     | Unit |

|------------------------|-----------------------------------|--------------------------------|-----|-------|-----|-------|-----|------|

|                        |                                   |                                |     | Тур   | Мах | Тур   | Max |      |

| I <sub>DD(pd)</sub>    | average power-down supply current |                                |     | -     | 5   | -     | 5   | μA   |

| I <sub>DD(sleep)</sub> | average sleep supply current      |                                |     | 80    | -   | 70    | -   | μA   |

| I <sub>DD(stb)</sub>   | average standby supply current    | all sectors powered down       | [1] | 400   | -   | 350   | -   | μA   |

|                        |                                   | 4 sectors active               | [1] | 635   | -   | 475   | -   | μA   |

|                        |                                   | all sectors active             | [1] | 870   | -   | 600   | -   | μA   |

| I <sub>DD(RW)</sub>    | average read supply current       | 4 sectors active and 5 MHz SPI | [1] | 800   | -   | 600   | -   | μA   |

| I <sub>DD(prog)</sub>  | average write supply current      | 4 sectors active and 5 MHz SPI | [1] | 1.1   | -   | 0.7   | -   | mA   |

[1] Sectors powered down according to the SPD field in the External Status Register (XSR).

### Table 35. Static characteristics-3

| Symbol                  | Parameter                   | Conditions                                                            | Min                  | Тур | Мах          | Unit |

|-------------------------|-----------------------------|-----------------------------------------------------------------------|----------------------|-----|--------------|------|

| Supply volta            | ges and currents            |                                                                       |                      |     | 1            | _    |

| V <sub>DD(EEPROM)</sub> | EEPROM supply voltage       |                                                                       | 1.5                  | 1.6 | 2.0          | V    |

| Input charac            | teristics <sup>[1]</sup>    |                                                                       |                      |     | 1            |      |

| V <sub>IH</sub>         | HIGH-level input voltage    |                                                                       | 0.7 × V <sub>S</sub> | -   | 2.6          | V    |

| V <sub>IL</sub>         | LOW-level input voltage     |                                                                       | -0.5                 | -   | +0.3 × $V_S$ | V    |

| V <sub>hys</sub>        | hysteresis voltage          |                                                                       | 0.1 × V <sub>S</sub> | -   | -            | V    |

| Output chara            | acteristics 1.2 V signaling |                                                                       | I                    |     | 1            |      |

| I <sub>OH</sub>         | HIGH-level output current   | current sourcing capability;<br>$V_{OH} = 0.8 \times V_{DD(IO)(1V2)}$ | 2.0                  | -   | -            | mA   |

| I <sub>OL</sub>         | LOW-level output current    | current sinking capability;<br>$V_{OL} = 0.2 \times V_{DD(IO)(1V2)}$  | 2.0                  | -   | -            | mA   |