# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### Middle Power Class-D Speaker Amplifiers Class-D Speaker Amplifier for Digital Input

BD5451EFV

No.11075EAT17

#### Description

BD5451EFV is a Class D Speaker Amplifier designed for Flat-panel TVs in particular for space-saving and low-power consumption, delivers an output power of 15W+15W. This IC employs state-of-the-art Bipolar, CMOS, and DMOS (BCD) process technology that eliminates turn-on resistance in the output power stage and internal loss due to line resistances up to an ultimate level. With this technology, the IC can achieve high efficiency of 90% (15W+15W output with  $8\Omega$  load). In addition, the IC is packaged in a compact reverse heat radiation type power package to achieve low power consumption and low heat generation and eliminates necessity of external heat-sink up to s a total output power of 30W. This product satisfies both needs for drastic downsizing, low-profile structures and many function, high quality playback of sound system.

#### Features

- 1) This IC has one system of digital audio interface.

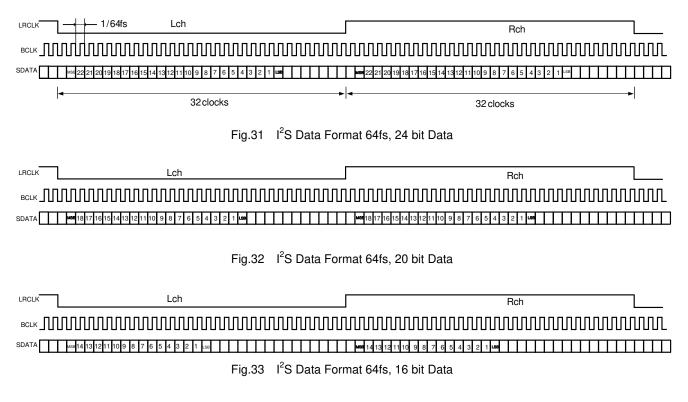

- (I<sup>2</sup>S format, SDATA: 16 / 20 / 24bit, LRCLK: 32kHz / 44.1kHz / 48kHz, BCLK: 64fs(fixed), MCLK: 256fs(fixed))

- 2) Low supply current at RESET mode.

- 3) The decrease in sound quality because of the change of the power supply voltage is prevented with the feedback circuitry of the output. In addition, a low noise and low distortion are achieved. Eliminate large electrolytic-capacitors for high performance of Power Supply Rejection.

- 4) S/N of the system can be optimized by adjusting the gain setting among 2 steps. (20dB / 26dB)

- 5) Available for Monaural mode.

- 6) Within the wide range of the power supply voltage, it is possible to operate in a single power supply.  $(10 \sim 18V)$

- 7) It contributes to miniaturizing, making to the thin type, and the power saving of the system by high efficiency and low heat.

- 8) Eliminates pop noise generated when the power supply goes on/off, or when the power supply is suddenly shut off. High quality muting performance is realized by using the soft-muting technology.

- This IC is a highly reliable design to which it has various protection functions. (High temperature protection, under voltage protection, Output short protection, Output DC voltage protection and Clock stop protection, (MCLK, BCLK, LRCLK))

- 10) Small package (HTSSOP-B28 package) contributes to reduction of PCB area.

#### Applications

Flat Panel TVs (LCD, Plasma), Home Audio, Desktop PC, Amusement equipments, Electronic Music equipments, etc.

#### ●Absolute maximum ratings (Ta=25°C)

| Parameter                    | Symbol            | Ratings    | Unit | Parameter                   |            |

|------------------------------|-------------------|------------|------|-----------------------------|------------|

| Supply voltage               | V <sub>CC</sub>   | 22         | V    | Pin 14, 15, 16, 27, 28 ※1   | ₩2         |

| Devues diseisentiere         | <b>D</b>          | 3.3        | w    | *3                          |            |

| Power dissipation            | P <sub>d</sub>    | 4.7        | w    | *4                          |            |

| Input voltage                | V <sub>IN</sub>   | -0.3 ~ 4.5 | V    | Pin 1 ~ 6, 13               | <b>%</b> 1 |

| Terminal voltage 1           | V <sub>PIN1</sub> | -0.3 ~ 7.0 | V    | Pin 8, 11, 12               | <b>%</b> 1 |

| Terminal voltage 2           | V <sub>PIN2</sub> | -0.3 ~ 4.5 | V    | Pin 9                       | <b>※</b> 1 |

| Terminal voltage 3           | V <sub>PIN3</sub> | 22         | V    | Pin 17, 18, 20 ~ 23, 25, 26 | <b>※</b> 1 |

| Open-drain terminal voltage  | V <sub>ERR</sub>  | -0.3 ~ 22  | V    | Pin 10                      | ₩1         |

| Operating temperature range  | T <sub>opr</sub>  | -25 ~ +85  | °C   |                             |            |

| Storage temperature range    | T <sub>stg</sub>  | -55 ~ +150 | °C   |                             |            |

| Maximum junction temperature | T <sub>jmax</sub> | +150       | °C   |                             |            |

%1 The voltage that can be applied reference to GND (Pin 7, 19, 24).

%2 Do not, however exceed Pd and Tjmax=150°C.

%3 70mm×70mm×1.6mm, FR4, 2-layer glass epoxy board (Copper on bottom layer : 70mm×70mm) Derating in done at 26.4mW/°C for operating above Ta=25°C. There are thermal via on the board.

%4 70mm×70mm×1.6mm, FR4, 4-layer glass epoxy board (Copper on bottom layer : 70mm×70mm) Derating in done at 37.6mW/°C for operating above Ta=25°C. There are thermal via on the board.

#### Operating conditions (Ta=25°C)

| Parameter              | Symbol          | Ratings | Unit | Parameter                    |  |

|------------------------|-----------------|---------|------|------------------------------|--|

| Supply voltage         | V <sub>CC</sub> | 10 ~ 18 | V    | Pin 14, 15, 16, 27, 28 ※1 ※2 |  |

| Minimum load impedance | RL              | 3.6     | Ω    | $VCC \leq 18V$ $\%5$         |  |

|                        |                 | 3.2     | 25   | VCC $\leq$ 16V $\%5$         |  |

%5 Do not, however exceed Pd.

※ No radiation-proof design.

#### Electrical characteristics

(Unless otherwise specified Ta=25°C, Vcc=12V, f=1kHz, RL=8Ω, RSTX=3.3V, MUTEX=3.3V, Gain=20dB, fs=48kHz \_Output LC filter: L=10µH, C=0.1µF)

| Parameter                                   | Symbol             |      | Limits |      | Unit      | Conditions                                            |            |

|---------------------------------------------|--------------------|------|--------|------|-----------|-------------------------------------------------------|------------|

| Falameter                                   | Symbol             | Min. | Тур.   | Max. | Onit      |                                                       |            |

| Total circuit                               |                    |      |        |      |           |                                                       |            |

| Circuit current<br>(Reset mode)             | I <sub>CC1</sub>   | -    | 0.1    | 0.2  | mA        | Pin 14, 15, 16, 27, 28, No I<br>RSTX=0V, MUTEX=0V     | oad        |

| Circuit current<br>(Mute mode)              | I <sub>CC 2</sub>  | -    | 15     | 25   | mA        | Pin 14, 15, 16, 27, 28, No I<br>RSTX=3.3V, MUTEX=0V   | oad        |

| Circuit current<br>(Sampling mode)          | I <sub>CC3</sub>   | -    | 50     | 80   | mA        | Pin 14, 15, 16, 27, 28, No I<br>RSTX=3.3V, MUTEX=3.3V |            |

| Open-drain terminal<br>Low level voltage    | V <sub>ERR</sub>   | -    | -      | 0.8  | V         | Pin 10, I <sub>0</sub> =0.5mA                         |            |

| Regulator output voltage 1                  | $V_{REG}_{G}$      | 4.7  | 5.0    | 5.3  | V         | Pin 11                                                |            |

| Regulator output voltage 2                  | $V_{\text{REG}_3}$ | 3.0  | 3.3    | 3.6  | V         | Pin 9                                                 |            |

| High level input voltage                    | V <sub>IH</sub>    | 2.0  | -      | 3.3  | V         | Pin 1 ~ 6, 13                                         |            |

| Low level input voltage                     | V <sub>IL</sub>    | 0    | -      | 0.9  | V         | Pin 1 ~ 6, 13                                         |            |

| Input current<br>(Input pull-down terminal) | Iн                 | 50   | 66     | 95   | μ Α       | Pin 1 ~ 6, 13, V <sub>IN</sub> = 3.3V                 |            |

| Speaker Output                              |                    |      |        |      |           |                                                       |            |

| Maximum output power 1                      | P <sub>O1</sub>    | -    | 10     | -    | W         | THD+n=10%<br>GAIN=20dB                                | <b>※</b> 6 |

| Maximum output power 2                      | Poz                | -    | 15     | -    | W         | VCC=15V, THD+n=10%<br>GAIN =26dB                      | <b>※</b> 6 |

| Voltage gain                                | G <sub>V20</sub>   | 19   | 20     | 21   | dB        | P <sub>O</sub> =1W, Gain=20dB                         | <b>※</b> 6 |

| Voltage gain                                | G <sub>V26</sub>   | 25   | 26     | 27   | dB        | P <sub>O</sub> =1W, Gain=26dB                         | <b>※</b> 6 |

| Total harmonic distortion                   | THD                | -    | 0.07   | -    | %         | P <sub>O</sub> =1W, BW=20∼20kHz                       | <b>※</b> 6 |

| Crosstalk                                   | СТ                 | 66   | 80     | -    | dB        | P <sub>O</sub> =1W, BW=IHF-A                          | <b>※</b> 6 |

| PSRR                                        | PSRR               | -    | 70     | -    | dB        | Vropple=1Vrms, f= 1kHz                                | <b>※</b> 6 |

| Output noise voltage<br>(Sampling mode)     | V <sub>NO</sub>    | -    | 100    | 200  | μ<br>Vrms | -∞dBFS, BW=IHF-A                                      | <b>※</b> 6 |

|                                             | f <sub>PWM1</sub>  | -    | 256    | -    | kHz       | fs=32kHz                                              | <b>※</b> 6 |

| PWM sampling frequency                      | f <sub>PWM2</sub>  | -    | 352.8  | -    | kHz       | fs=44.1kHz                                            | <b>※</b> 6 |

|                                             | f <sub>PWM3</sub>  | -    | 384    | -    | kHz       | fs=48kHz                                              | <b>※</b> 6 |

%6 These items show the typical performance of device and depend on board layout, parts, and power supply. The standard value is in mounting device and parts on surface of ROHM's board directly.

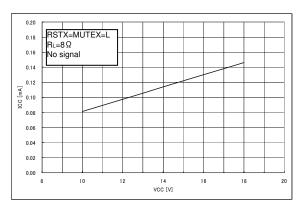

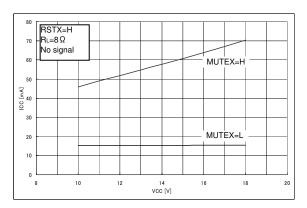

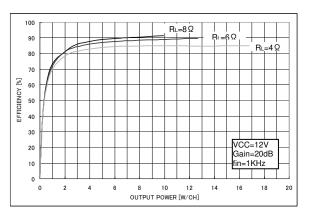

#### ●Electrical characteristic curves (VCC=12V, Ta=25°C, RL=8Ω, Gain=26dB, fin=1kHz, fs=48kHz) Measured by ROHM designed 4 layer board.

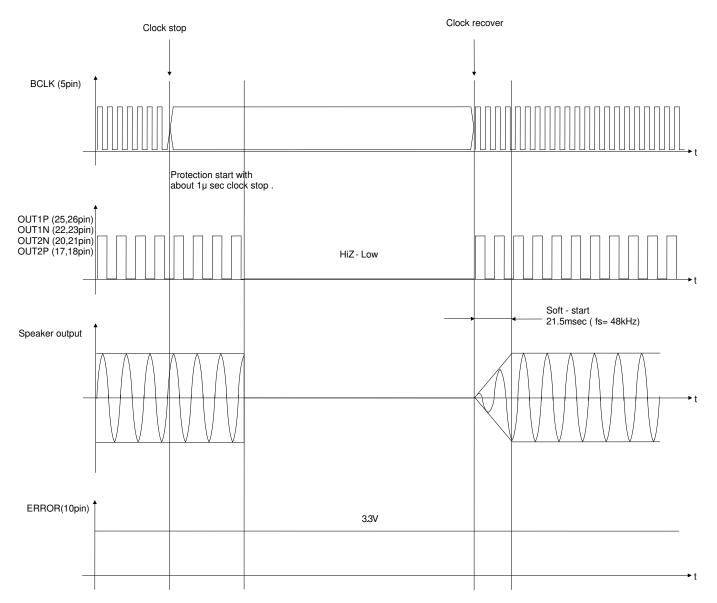

Fig.1 Current consumption - Power supply voltage

Fig.2 Current consumption - Power supply voltage

Fig.3 Efficiency - Output power

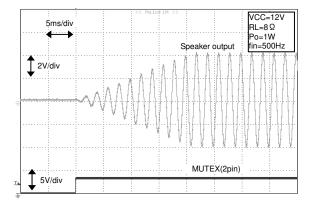

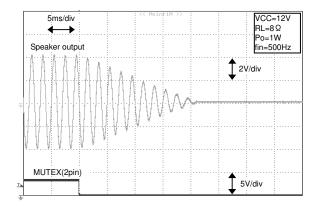

Fig.5 Wave form when releasing soft-mute

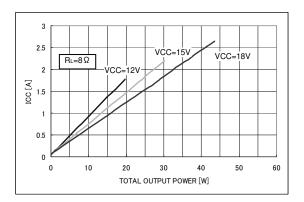

Fig.4 Current consumption - Output power

Fig.6 Wave form when activating soft-mute

VCC=18V

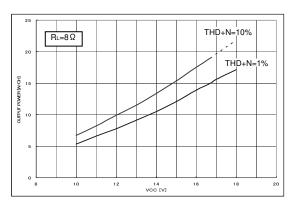

Electrical characteristics (VCC=12V, Gain=26dB, fin=1kHz, fs=48kHz) Measured by ROHM designed 4 layer board.

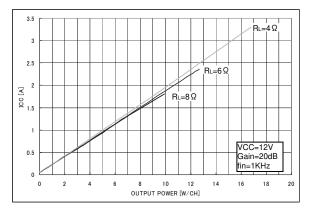

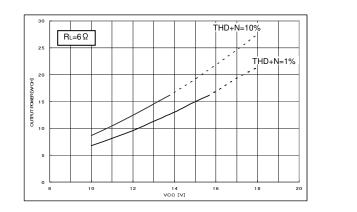

Fig.7 Output power – Power supply voltage

Fig.8 Current consumption - Output power

RL=6Ω

3.5

3

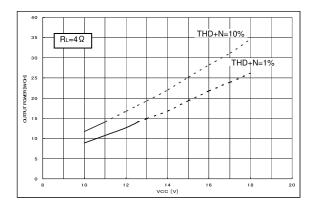

Fig.9 Output power – Power supply voltage

Fig.11 Output power – Power supply voltage

25 2 2 1.5 0.5 0 0 0 10 20 30 40 50 60 TOTAL OUTPUT POWER [W]

VCC=15V

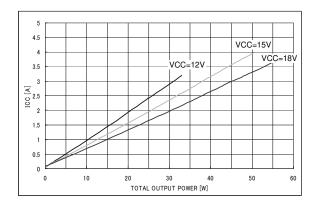

Fig.10 Current consumption - Output power

Fig.12 Current consumption - Output power

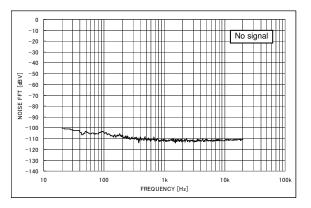

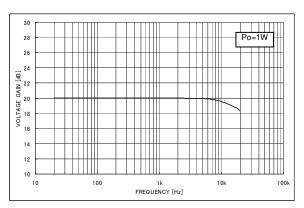

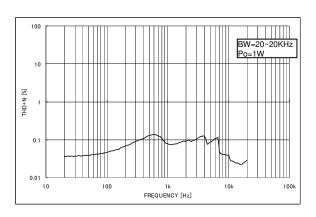

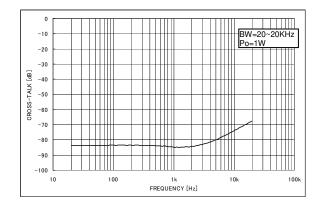

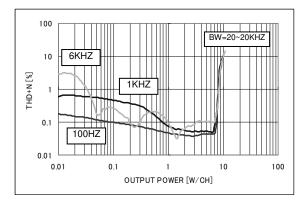

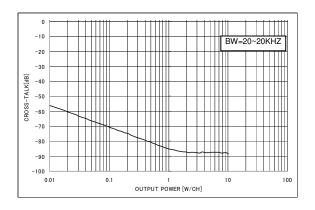

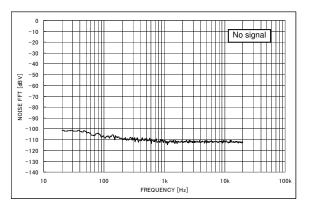

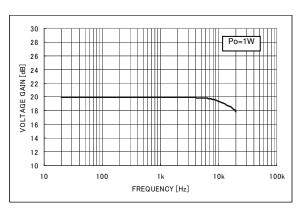

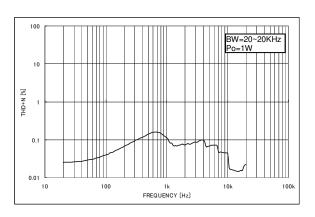

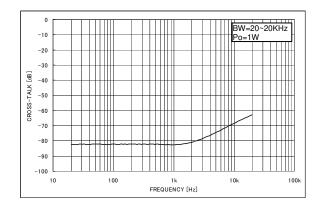

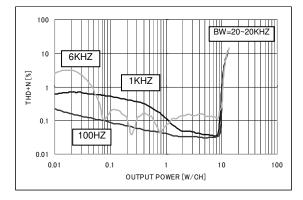

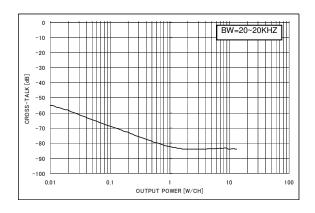

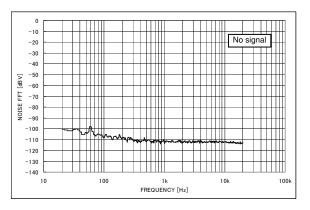

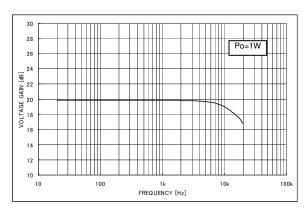

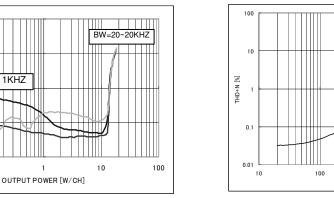

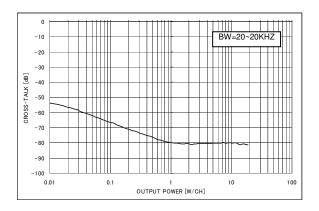

Electrical characteristic curves (VCC=12V, Ta=25°C, R<sub>L</sub>=8Ω, Gain=20dB, fin=1kHz, fs=48kHz) Measured by ROHM designed 4layer board.

Fig.13 FFT of output noise voltage

Fig.14 Voltage gain - Frequency

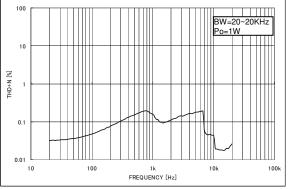

Fig.16 THD+N – Frequency

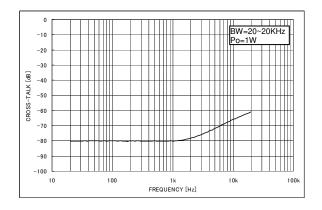

Fig.18 Crosstalk – Frequency

Fig.15 THD+N – Output power

Fig.17 Crosstalk – Output power

#### Electrical characteristic curves(VCC=12V, Ta=25°C, R<sub>L</sub>=6Ω, Gain=20dB, fin=1kHz, fs=48kHz) Measured by ROHM designed 4layer board

Fig.19 FFT of output noise voltage

Fig.20 Voltage gain - Frequency

Fig.22 THD+N – Frequency

Fig.24 Crosstalk – Frequency

Fig.21 THD+N – Output power

Fig.23 Crosstalk – Output power

100

10

0.1

0.01

0.01

THD+N [%]

6KHZ

100HZ

0.1

#### Electrical characteristic curves(VCC=12V, Ta=25°C, R<sub>L</sub>=4Ω, Gain=20dB, fin=1kHz, fs=48kHz) Measured by ROHM designed 4layer board

Fig.25 FFT of output noise voltage

Fig.26 Voltage gain - Frequency

Fig.27 THD+N – Output power

Fig.29 Crosstalk – Output power

Fig.28 THD+N – Frequency

Fig.30 Crosstalk – Frequency

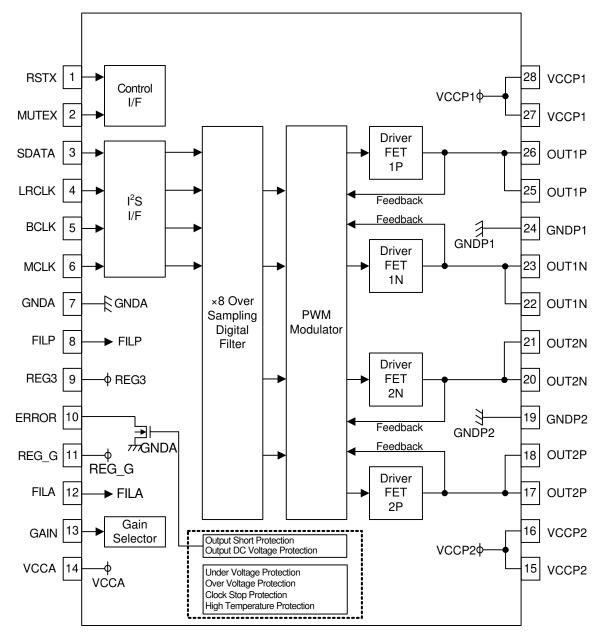

#### Pin configuration and Block diagram

#### ●Pin function explanation (Provided pin voltages are typ. Values)

| Pin No.          | Pin name                       | Pin voltage | ages are typ. Values)<br>Pin explanation                                                | Internal equivalence circuit                                        |

|------------------|--------------------------------|-------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| 1                | RSTX                           | ٥V          | Reset pin for Digital circuit<br>H: Reset OFF<br>L: Reset ON                            | (14)<br>17.3k<br>1 → ₩<br>17.3k<br>1 → ₩<br>32.7k                   |

| 2                | MUTEX                          |             | Speaker output mute control pin<br>H: Mute OFF<br>L: Mute ON                            | (14)                                                                |

| 3<br>4<br>5<br>6 | SDATA<br>LRCLK<br>BCLK<br>MCLK | ٥V          | Digital audio signal input pin                                                          | 2, 3, 4<br>5, 6, 13<br>50K                                          |

| 12               | GAIN                           |             | Gain setting terminal<br>L: 20dB<br>H: 26dB                                             | 7                                                                   |

| 7                | GNDA                           | ٥V          | GND pin for Analog signal                                                               | _                                                                   |

| 8                | FILP                           | 1.75V~2.55V | Bias pin for PWM signal<br>Please connect the capacitor.                                |                                                                     |

| 9                | REG3                           | 3.3V        | Internal power supply pin for Digital circuit<br>Please connect the capacitor.          | (14)<br>9<br>↓<br>500 K<br>7<br>↓                                   |

| 10               | ERROR                          | 3.3V        | Error flag pin<br>Please connect pull-up resister.<br>H: While Normal<br>L: While Error |                                                                     |

| 11               | REG_G                          | 5.2V        | Internal power supply pin for Gate driver<br>Please connect the capacitor.              | (14)<br>(14)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1 |

| Pin No. | Pin name | Pin voltage | Pin explanation                                                   | Internal equivalence circuit      |

|---------|----------|-------------|-------------------------------------------------------------------|-----------------------------------|

| 12      | FILA     | 2.5V        | Bias pin for PWM signal.<br>Please connect the capacitor.         | 14<br>12<br>50K<br>12<br>50K<br>7 |

| 14      | VCCA     | Vcc         | Power supply pin for Analog signal                                | _                                 |

| 15,16   | VCCP2    | Vcc         | Power supply pin for ch2 PWM signal Please connect the capacitor. | 15,16                             |

| 17,18   | OUT2P    | Vcc~0V      | Output pin of ch2 positive PWM<br>Please connect to Output LPF.   | (17,18)<br>↓ ← ←                  |

| 19      | GNDP2    | 0V          | GND pin for ch2 PWM signal                                        |                                   |

| 20,21   | OUT2N    | Vcc~0V      | Output pin of ch2 negative PWM<br>Please connect to Output LPF.   |                                   |

| 22,23   | OUT1N    | Vcc~0V      | Output pin of ch1 negative PWM<br>Please connect to Output LPF.   | 27,28                             |

| 24      | GNDP1    | 0V          | GND pin for ch1 PWM signal                                        |                                   |

| 25,26   | OUT1P    | Vcc~0V      | Output pin of ch1 posotive PWM<br>Please connect to Output LPF.   |                                   |

| 27,28   | VCCP1    | _           | Power supply pin for ch1 PWM signal Please connect the capacitor. | 24                                |

#### Terminal setting

(1) Gain pin function

| GAIN<br>(13pin) | Speaker output gain |

|-----------------|---------------------|

| L               | 20dB                |

| Н               | 26dB                |

#### (2) RSTX pin, MUTEX pin function

|                             |        | Normalcy                          |                 | Error detecting                   |                 |  |

|-----------------------------|--------|-----------------------------------|-----------------|-----------------------------------|-----------------|--|

| RSTX MUTEX<br>(1pin) (2pin) |        | PWM output<br>(OUT1P, 1N, 2P, 2N) | ERROR<br>Output | PWM output<br>(OUT1P, 1N, 2P, 2N) | ERROR<br>Output |  |

| L                           | L or H | HiZ_L<br>(Reset mode)             | н               | HiZ_L<br>(Reset mode)             | н               |  |

| Н                           | L      | HiZ_L<br>(MUTE_ON)                | н               | HiZ_L<br>(MUTE ON)                | L               |  |

| н                           | Н      | Normal operation<br>(MUTE OFF)    | Н               | HiZ_L<br>(MUTE_ON)                | L               |  |

$\label{eq:RSTX(1pin)terminal, MUTEX(2pin)terminal are internally pulled down by 50 k \Omega (Typ.)$

: With RSTX=L data of every register within IC (I<sup>2</sup>S / I/F part, × 8 over sampling digital filter part, latch circuit when detecting ERROR) becomes unnecessary.

#### Input digital audio signal sampling frequency (fs) explanation

PWM sampling frequency, Soft-start, Soft-mute time, and the detection time of the DC voltage protection in the speaker depends on sampling frequency (fs) of the digital audio input.

| Sampling frequency of the digital audio input (fs) | PWM sampling frequency (fpwm) | Soft-start / Soft-mute time | DC voltage protection in the speaker detection time |

|----------------------------------------------------|-------------------------------|-----------------------------|-----------------------------------------------------|

| 32kHz                                              | 256kHz                        | 32msec.                     | 64msec.                                             |

| 44.1kHz                                            | 352.8kHz                      | 23msec.                     | 46msec.                                             |

| 48kHz                                              | 384kHz                        | 21.5msec.                   | 43msec.                                             |

#### •For voltage gain (Gain setting)

BD5451EFV prescribe voltage gain at speaker output (BTL output) under the definition 0dBV (1Vrms) as full scale input of the digital audio input signal. For example, digital audio input signal = -20dBFS (0.1Vrms), Gain setting = 20dB, Load resistance  $R_L = 8\Omega$  will give speaker output (BTL output) amplitude as Vo=1Vrms. (Output power Po = Vo<sup>2</sup>/R = 0.125W)

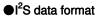

#### •Format of digital audio input

- MCLK: It is System Clock input signal.

It will input LRCLK, BCLK, SDATA that synchronizes with this clock that are 256 times of sampling frequency (256fs).

- LRCLK: It is L/R clock input signal. It corresponds to 32kHz / 44.1kHz / 48kHz with those clock (fs) that are same to the sampling frequency (fs). The data of a left channel and a right channel for one sample is input to this section.

- BCLK: It is Bit Clock input signal. It is used for the latch of data in every one bit by sampling frequency's 64 times sampling frequency (64fs).

- SDATA: It is Data input signal. It is amplitude data. The data length is different according to the resolution of the input digital audio data. It corresponds to 16/ 20/ 24 bit.

The Low section of LRCLK becomes Lch, the High section of LRCLK becomes Rch. After changing LRCLK, second bit becomes MSB.

#### Audio Interface format and timing

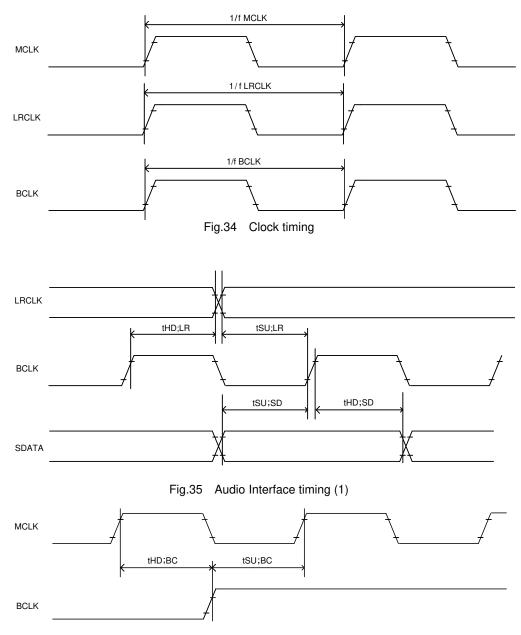

Recommended timing and operating conditions (MCLK, BCLK, LRCLK, SDATA)

| Parameter |                     | Symbol | Lir       | Unit   |     |

|-----------|---------------------|--------|-----------|--------|-----|

|           |                     | Symbol | Min. Max. |        |     |

| 1         | MCLK frequency      | fMCLK  | 8.192     | 12.288 | MHz |

| 2         | LRCLK frequency     | fLRCLK | 32        | 48     | kHz |

| 3         | BCLK frequency      | fBCLK  | 2.048     | 3.072  | MHz |

| 4         | Setup time, LRCLK%1 | tSU;LR | 20        | _      | ns  |

| 5         | Hold time, LRCLK%1  | tHD;LR | 20        | _      | ns  |

| 6         | Setup time, SDATA   | tSU;SD | 20        | _      | ns  |

| 7         | Hold time, SDATA    | tHD;SD | 20        | _      | ns  |

| 8         | Setup time, BCLK%2  | tSU;BC | 3         | _      | ns  |

| 9         | Hold time, BCLK%2   | tHD;BC | 7         | _      | ns  |

\*1 This regulation is to keep rising edge of LRCK and rising edge of BCLK from overlapping.

%2 This regulation is to keep rising edge of MCLK and rising edge of BCLK from overlapping.

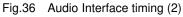

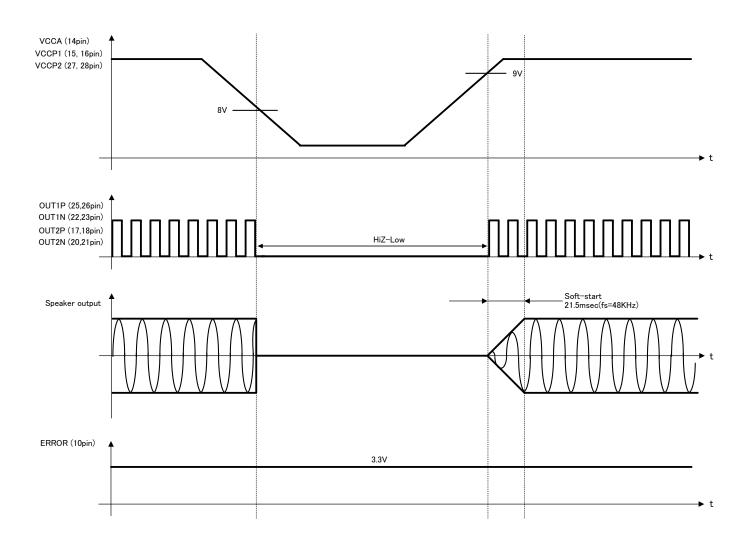

#### Power supply start-up sequence

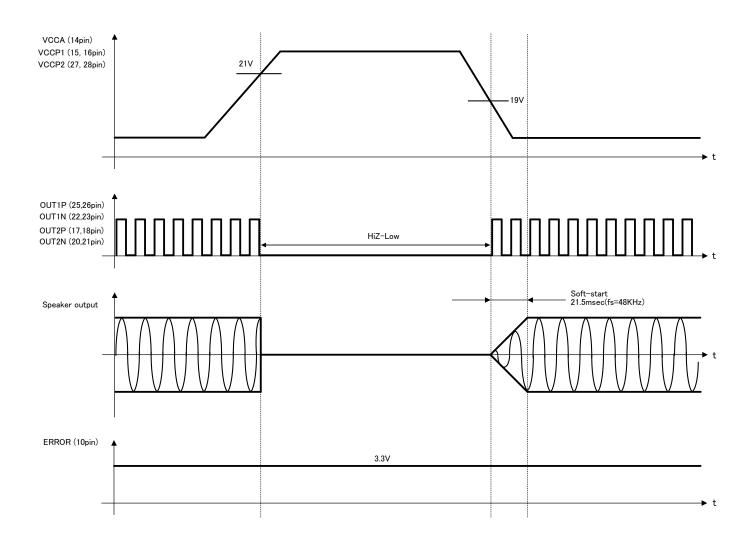

#### Power supply shut-down sequence

#### About the protection function

| Protection function                  |                     | Detecting & Releasing condition                                                                                                                   | PWM<br>Output      | ERROR<br>Output |

|--------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------|

| Output short protection              | Detecting condition |                                                                                                                                                   |                    | L<br>(Latch)    |

| DC voltage protection in the speaker | Detecting condition | PWM output Duty=0% or 100%<br>43msec(fs=48kHz) above fixed                                                                                        | HiZ_Low<br>(Latch) | L<br>(Latch)    |

| High temperature                     | Detecting condition | Chip temperature to be above 150°C (TYP.)                                                                                                         | HiZ_Low            |                 |

| protection                           | Releasing condition | Chip temperature to be below 120°C (TYP.)                                                                                                         | Normal operation   | Н               |

|                                      | Detecting condition | Power supply voltage to be below 8V (TYP.)                                                                                                        | HiZ_Low            |                 |

| Under voltage protection             | Releasing condition | Power supply voltage to be above 9V (TYP.)                                                                                                        | Normal operation   | Н               |

|                                      | Detecting condition | Power supply voltage to be above 21.5V(TYP.)                                                                                                      | HiZ_Low            |                 |

| Over voltage Protection              | Releasing condition | Power supply voltage to be below 20.5V(TYP.)                                                                                                      | Normal operation   | Н               |

| Clock stop protection                | Detecting condition | No change to MCLK more than 1µsec (TYP.) or<br>no change to BCLK more than 1µsec (TYP.) or<br>no change to LRCLK more than 21µsec (at fs=48kHz.). | HiZ_Low            |                 |

|                                      | Releasing condition | Normal input to MCLK, BCLK and LRCLK.                                                                                                             | Normal operation   | Н               |

The ERROR pin is Nch open-drain output.

Once an IC is latched, the circuit is not released automatically even after an abnormal status is removed.

The following procedures ① or ② is available for recovery. ①After turning MUTEX terminal to Low(holding time to Low = 10msec(Min.)) turn back to High again. ②Restore power supply after dropping to power supply voltage Vcc<3V(10msec (Min.) holding) which internal power on reset circuit activates.

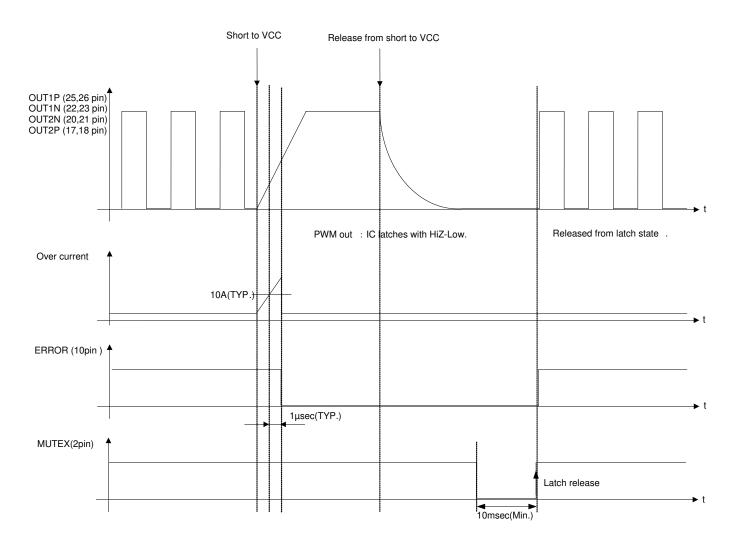

- 1) Output short protection(Short to the power supply)

- This IC has the PWM output short protection circuit that stops the PWM output when the PWM output is short-circuited to the power supply due to abnormality.

- Detecting condition It will detect when MUTEX pin is set High and the current that flows in the PWM output pin becomes 10A(TYP.) or more. The PWM output instantaneously enters the state of HiZ-Low if detected, and IC does the latch.

- Releasing method ①After turning MUTEX terminal to Low(holding time to Low = 10msec(Min.)) turn back to High again.

- ②Restore power supply after dropping to power supply voltage Vcc<3V(10msec (Min.) holding) which internal power on reset circuit activates.</p>

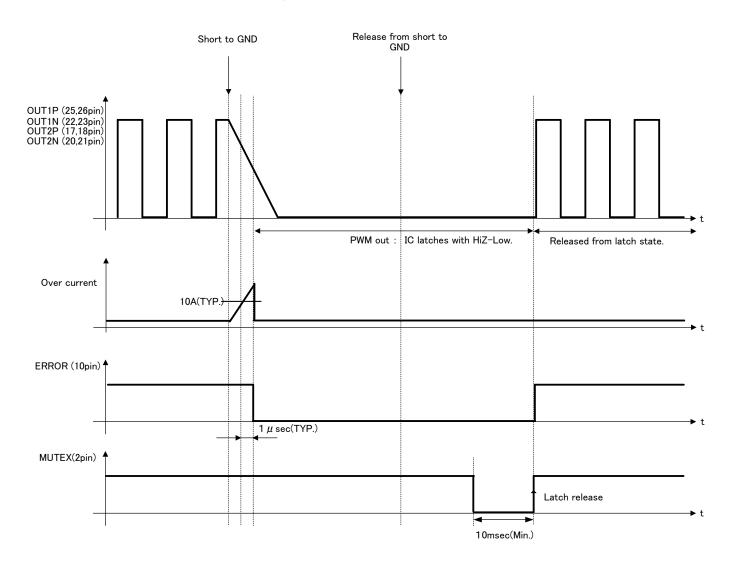

2) Output short protection(Short to GND)

This IC has the PWM output short protection circuit that stops the PWM output when the PWM output is short-circuited to GND due to abnormality.

Detecting condition - It will detect when MUTEX pin is set High and the current that flows in the PWM output terminal becomes 10A(TYP.) or more. The PWM output instantaneously enters the state of HiZ-Low if detected, and IC does the latch.

Releasing method – ①After turning MUTEX terminal to Low(holding time to Low = 10msec(Min.)) turn back to High again.

②Restore power supply after dropping to power supply voltage Vcc<3V(10msec (Min.) holding) which internal power on reset circuit activates.

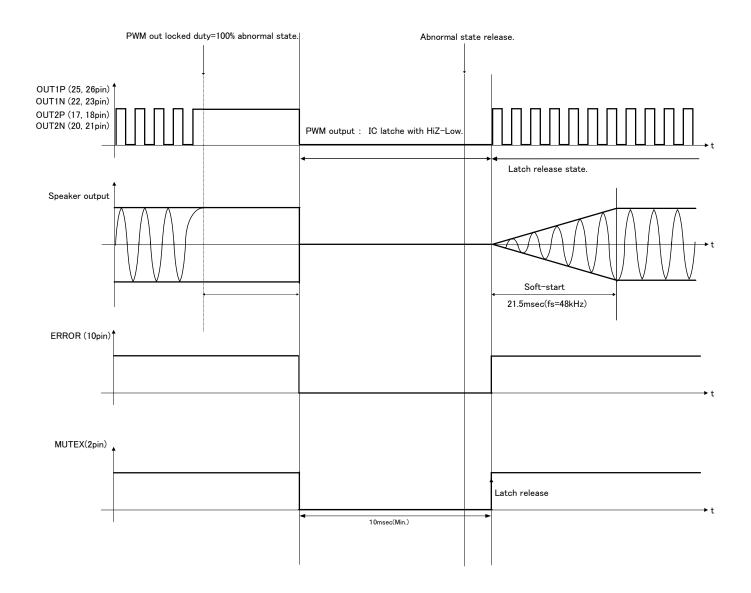

3) DC voltage protection in the speaker

- When the DC voltage in the speaker is impressed due to abnormality, this IC has the protection circuit where the speaker is defended from destruction.

- Detecting condition It will detect when MUTEX pin is set High or Low and PWM output Duty=0% or 100% , 43msec(fs=48kHz) or above. Once detected, The PWM output instantaneously enters the state of HiZ-Low, and IC does the latch.

- Releasing method ①After turning MUTEX terminal to Low(holding time to Low = 10msec(Min.)) turn back to High again.

- ②Restore power supply after dropping to power supply voltage Vcc<3V(10msec (Min.) holding) which internal power on reset circuit activates.

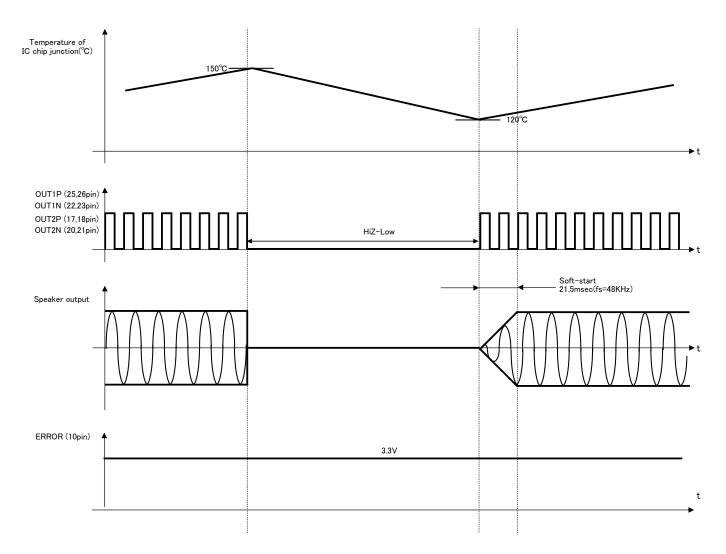

#### 4) High temperature protection

This IC has the high temperature protection circuit that prevents thermal reckless driving under an abnormal state for the temperature of the chip to exceed Tjmax=150°C.

Detecting condition - It will detect when MUTEX pin is set High and the temperature of the chip becomes 150°C(TYP.) or more. Speaker output turn MUTE immediately, when High temperature protection is detected. Releasing condition - It will release when MUTEX pin is set High and the temperature of the chip becomes 120°C (TYP.) or less. The speaker output is outputted through a soft-start when released.

#### 5) Under voltage protection

This IC has the under voltage protection circuit that make speaker output mute once detecting extreme drop of the power supply voltage.

Detecting condition – It will detect when MUTEX pin is set High and the power supply voltage becomes lower than 8V.Speaker output turn MUTE immediately, when Under voltage protection is detected.

Releasing condition – It will release when MUTEX pin is set High and the power supply voltage becomes more than 9V. The speaker output is outputted through a soft-start when released.

#### 6) Over voltage protection

This IC has the under voltage protection circuit that make speaker output mute once detecting extreme drop of the power supply voltage.

Detecting condition – It will detect when MUTEX pin is set High and the power supply voltage becomes more than 21.5V.Speaker output turn MUTE immediately, when over voltage protection is detected.

Releasing condition – It will release when MUTEX pin is set High and the power supply voltage becomes lower than 20.5V. The speaker output is outputted through a soft-start when released.

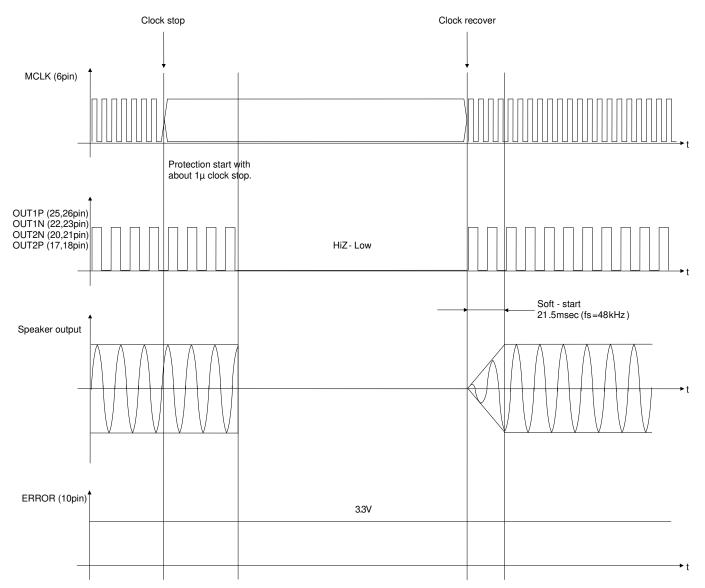

7-1) Clock stop protection(MCLK)

This IC has the clock stop protection circuit that make the speaker output mute when the MCLK signal of the digital audio input stops.

Detecting condition - It will detect when MUTEX pin is set High and the MCLK signal stops for about 1µsec or more. 21.5V. Speaker output turn MUTE immediately, clock stop protection is detected.

Releasing condition - It will release when MUTEX pin is set High and the MCLK signal returns to the normal clock operation. The speaker output is outputted through a soft-start when released.

7-2) Clock stop protection(BCLK)

This IC has the clock stop protection circuit that make the speaker output mute when the BCLK signal of the digital audio input stops.

Detecting condition - It will detect when MUTEX pin is set High and the BCLK signal stops for about 1µsec or more. 21.5V.Speaker output turn MUTE immediately, when clock stop protection is detected.

Releasing condition - It will release when MUTEX pin is set High and the BCLK signal returns to the normal clock operation. The speaker output is outputted through a soft-start when released.