# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## 1. General description

The P82B715 is a bipolar IC intended for application in I<sup>2</sup>C-bus and derivative bus systems. While retaining all the operating modes and features of the I<sup>2</sup>C-bus it permits extension of the practical separation distance between components on the I<sup>2</sup>C-bus by buffering both the data (SDA) and the clock (SCL) lines.

The I<sup>2</sup>C-bus capacitance limit of 400 pF restricts practical communication distances to a few meters. Using one P82B715 at each end of a long cable (connecting Lx/Ly to Lx/Ly) reduces that cable's loading on the linked I<sup>2</sup>C-buses by a factor of 10 and allows the total system capacitance load (all devices, cable, connectors, and traces or wires connected to the I<sup>2</sup>C-bus) to be around 3000 pF while the loading on each I<sup>2</sup>C-bus on the Sx/Sy sides remains below 400 pF. Longer cables or low-cost, general-purpose wiring may be used to link I<sup>2</sup>C-bus based modules without degrading noise margins. Multiple P82B715s can be connected together, linking their Lx/Ly ports, in a star or multi-point architecture as long as the total capacitance of the system is less than about 3000 pF and each bus at an Sx/Sy connection is well below 400 pF. This configuration, with the master and/or slave devices attached to the Sx/Sy port of each P82B715, has full multi-master communication capability. The P82B715 alone does not support voltage level translation, but it can be simply implemented using low cost transistors when required. There is no restriction on interconnecting the Sx/Sy I/Os, and, because the device output levels are always held within 100 mV of input drive levels, P82B715 is compatible with bus buffers that use voltage level offsets, e.g., PCA9511A, PCA9517, Sx/Sy side of P82B96.

The lower V<sub>OL</sub> level and ability to operate with any master, slave or bus buffer is the primary advantage of the using the P82B715 for long distance buses at the disadvantage of not isolating bus capacitance like the P82B96 or PCA9600 are able to do. The primary disadvantage of the P82B96 and PCA9600 is that the static level offset needed to isolate bus capacitance does not allow these devices to operate with other bus buffers with special offset levels or with master/slaves that require a V<sub>IL</sub> lower than 0.8 V with noise margin. A proven quick design-in point-to-point/multi-point circuit (Figure 9) is included in Section 8.2 to allow rapid use of the P82B715 along with comparison waveforms so that the designer can clearly see the trade-offs between the P82B715 and the P82B96/PCA9600 and choose the type of device that is best for their application.

## 2. Features

- Dual, bidirectional, unity voltage gain buffer with no external directional control required

- Compatible with I<sup>2</sup>C-bus and its derivatives SMBus, PMBus, DDC, etc.

- Logic signal levels may include (but not exceed) both supply and ground

- Logic signal input voltage levels are output without change and are independent of V<sub>CC</sub>

- ×10 impedance transformation, but does not change logic voltage levels

- Supply voltage range 3 V to 12 V

- Clock speeds to at least 100 kHz and 400 kHz when other system delays permit

- ESD protection exceeds 2500 V HBM per Mil. Std 883C-3015.7 and 400 V MM per JESD22-A115 (I/Os have diodes to V<sub>CC</sub> and GND)

- Latch-up testing is done to JEDEC Standard JESD78 which exceeds 100 mA

## 3. Applications

- Increase the total connected capacitance of an I<sup>2</sup>C-bus system to around 3000 pF

- Drive I<sup>2</sup>C-bus signals over long cables to approximately 50 meters or 3000 pF

- Drives ×10 lower impedance bus wiring for improved noise immunity

- Multi-drop distribution of I<sup>2</sup>C-bus signals using low cost twisted-pair cables

- AdvancedTCA radial IPMB architecture

- Driving 30 mA Fm+ devices from standard 3 mA parts

## 4. Ordering information

#### Table 1.Ordering information<sup>[1]</sup>

| Type number | Package | Package                                                   |         |  |  |

|-------------|---------|-----------------------------------------------------------|---------|--|--|

|             | Name    | Description                                               | Version |  |  |

| P82B715PN   | DIP8    | plastic dual in-line package; 8 leads (300 mil)           | SOT97-1 |  |  |

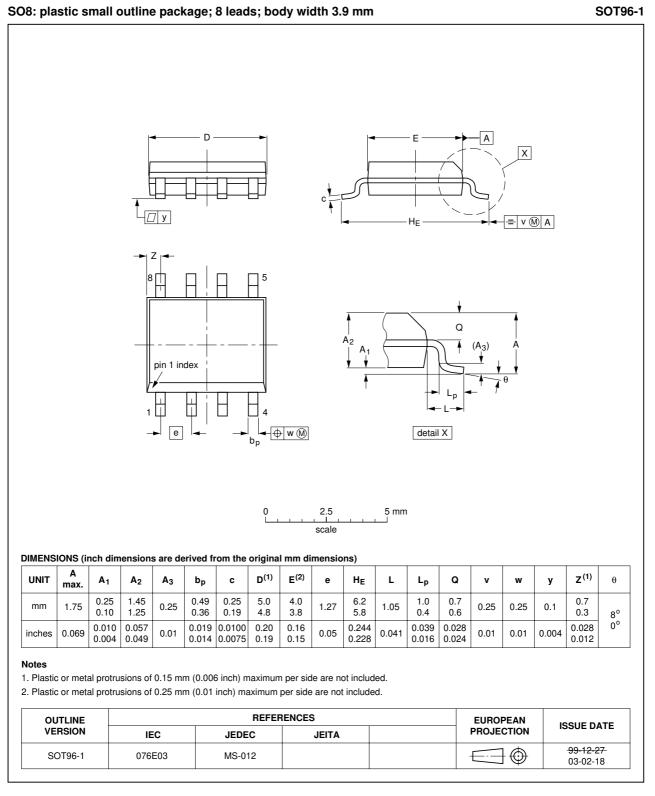

| P82B715TD   | SO8     | plastic small outline package; 8 leads; body width 3.9 mm | SOT96-1 |  |  |

For applications requiring lower voltage operation, or additional buffer performance, see application notes AN255, "I<sup>2</sup>C/SMBus repeaters, hubs and expanders" and AN10710, "Features and applications of the P82B715 I<sup>2</sup>C-bus extender".

#### 4.1 Ordering options

#### Table 2.Ordering options

|             | 0 1          |                   |

|-------------|--------------|-------------------|

| Type number | Topside mark | Temperature range |

| P82B715PN   | P82B715PN    | -40 °C to +85 °C  |

| P82B715TD   | P82B715      | –40 °C to +85 °C  |

P82B715 I<sup>2</sup>C-bus extender

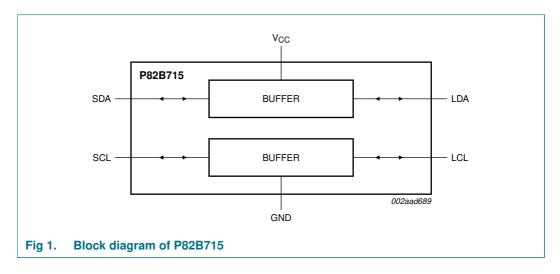

## 5. Block diagram

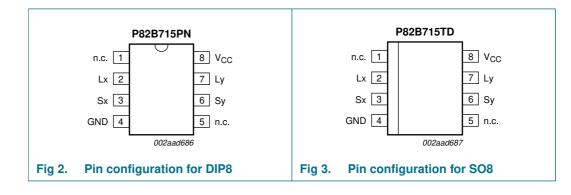

## 6. Pinning information

#### 6.1 Pinning

### 6.2 Pin description

#### Table 3.Pin description

| Symbol          | Pin | Description                      |

|-----------------|-----|----------------------------------|

| n.c.            | 1   | not connected                    |

| Lx              | 2   | buffered bus, LDA or LCL         |

| Sx              | 3   | I <sup>2</sup> C-bus, SDA or SCL |

| GND             | 4   | negative supply                  |

| n.c.            | 5   | not connected                    |

| Sy              | 6   | I <sup>2</sup> C-bus, SCL or SDA |

| Ly              | 7   | buffered bus, LCL or LDA         |

| V <sub>CC</sub> | 8   | positive supply                  |

|                 |     |                                  |

## 7. Functional description

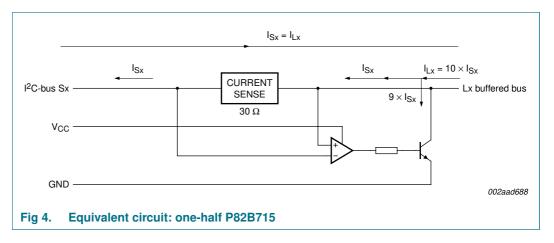

The P82B715 is a dual bidirectional logic signal device having unity voltage gain in both directions, but  $\times 10$  current amplification in one direction that allows increasing the allowable l<sup>2</sup>C-bus system capacitance. It contains identical circuits for each l<sup>2</sup>C-bus signal and requires no external directional control. It uses unidirectional analog current amplification to increase the current sink capability of l<sup>2</sup>C-bus chips by a factor of 10 and to change the l<sup>2</sup>C-bus specification limit of 400 pF to a 4 nF system limit. This allows l<sup>2</sup>C-bus, or similar bus systems, to be extended over long distances using conventional cables and without degradation of system performance.

P82B715 provides current amplification from its I<sup>2</sup>C-bus to its low-impedance or buffered bus. Whenever current is flowing out of Sx, into an I<sup>2</sup>C-bus chip driving the I<sup>2</sup>C-bus LOW, P82B715 will sink ten times that current into Lx to drive the buffered bus LOW (see Figure 4).

To minimize interference and ensure stability, the current rise and fall times of the Lx drive amplifier are internally controlled.

The P82B715 does not amplify signal currents flowing in the other direction, i.e., into Sx from the  $l^2$ C-bus. The Sx pin is driven LOW by current flowing out of Lx to the driver of that buffered side.

The buffered bus logic LOW voltage at Lx simply drives the I<sup>2</sup>C-bus at Sx LOW via the internal 30  $\Omega$  resistor. The buffer's offset voltage (the difference between Sx and Lx) depends on the current flowing in the sense resistor so it will be very small when the bus currents are small, but it is guaranteed not to exceed 100 mV in either direction with full static I<sup>2</sup>C-bus loading.

The unity voltage gain, with signal current amplification dependent on direction, preserves the multi-master, bidirectional, open-collector/open-drain, characteristic of any connected I<sup>2</sup>C-bus lines and provides these characteristics to the new low-impedance bus. Bus logic signal voltage levels will be clamped at (V<sub>CC</sub> + 0.7 V), but otherwise are independent of the supply voltage V<sub>CC</sub>.

### 7.1 Sx, Sy: I<sup>2</sup>C-bus SDA or SCL

On the normal side, because the two buffer circuits in the P82B715 are identical, either the Sx or Sy input pins can be used as the I<sup>2</sup>C-bus SDA data line, or the SCL clock line.

#### 7.2 Lx, Ly: buffered bus LDA or LCL

On the special low-impedance or buffered line side, the corresponding output at the Lx or Ly pins becomes the LDA data line or LCL clock line.

#### 7.3 V<sub>CC</sub>, GND: positive and negative supply pins

The power supply voltages at each P82B715 used in a system are normally nominally the same. If they differ by a significant amount, noise margin may be sacrificed as the bus HIGH level should not exceed the lowest of those supplies.

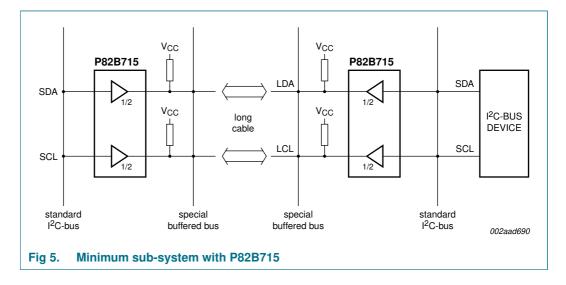

### 8. Application design-in information

By using two (or more) P82B715 ICs, a sub-system can be built that retains the interface characteristics of a normal I<sup>2</sup>C-bus device so that the sub-system may be included in, or added onto, any I<sup>2</sup>C-bus or related system.

The sub-system shown in <u>Figure 5</u> features a low-impedance or buffered bus, capable of driving large wiring capacitance.

The P82B715 will operate with a supply voltage from 3 V to 12.5 V but the logic signal levels at Sx/Lx are independent of the chip's supply. They remain at the levels presented to the chip by the attached ICs. The maximum static I<sup>2</sup>C-bus sink current, 3 mA, flowing in either direction in the internal current sense resistor, causes a difference, or offset voltage, less than 100 mV between the bus logic LOW levels at Sx and Lx. This makes P82B715 fully compatible with all logic signal drivers, including TTL. The P82B715 cannot modify the bus logic signal voltage levels but it contains internal diodes connected between Lx/Sx and V<sub>CC</sub> that will conduct and limit the logic signal swing if the applied logic levels would have exceeded the supply voltage by more than 0.7 V. In normal applications external pull-up resistors will pull the connected buses up to the desired voltage HIGH level. Usually this will be the chip supply, V<sub>CC</sub>, but for very low logic voltages it is necessary to use a V<sub>CC</sub> of at least 3.3 V and preferably even higher. Note that full performance over temperature is only guaranteed from 4.5 V. Specification de-ratings apply when its supply voltage is reduced below 4.5 V. The absolute minimum V<sub>CC</sub> is 3 V.

#### 8.1 I<sup>2</sup>C-bus systems

As in standard I<sup>2</sup>C-bus systems, pull-up resistors are required to provide the logic HIGH levels on the buffered bus. (The standard open-collector configuration is retained.) The value and number of pull-up resistors used is flexible and depends on the system requirements and designer preferences.

If P82B715 ICs are to be permanently connected into a system it could be configured with only one pull-up resistor on the buffered bus and none on the l<sup>2</sup>C-buses, but the system design will be simplified, and performance improved, by fitting separate pull-ups on each section of the bus. When a sub-system using P82B715 may be optionally connected to an existing l<sup>2</sup>C-bus system that already has a pull-up, then the effects of the sub-system pull-ups acting in parallel with the existing l<sup>2</sup>C-bus pull-up must be considered.

#### 8.1.1 Pull-up resistance calculation

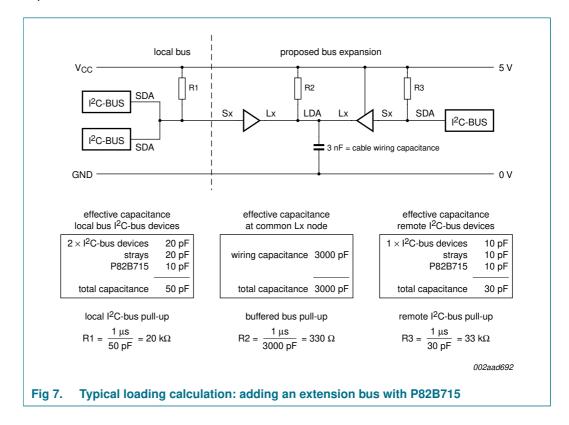

When calculating the pull-up resistance values, the gain of the buffer introduces scaling factors which must be applied to the system components. In practical systems the pull-up resistance value is usually calculated to achieve the rise time requirement of the system. As an approximation, this requirement will be satisfied for a standard 100 kHz system if the time constant of the total system (product of the net resistance and net capacitance) is set to 1 microsecond or less.

In systems using P82B715s, the most convenient way to achieve the total system rise time requirement is by considering each bus node separately. Each of the l<sup>2</sup>C-bus nodes, and the buffered bus node, is designed by selecting its pull-up resistor to provide the required rise time by setting its time constant (product of the pull-up resistance and load capacitance) equal to the l<sup>2</sup>C-bus rise time requirement. If each node complies, then the system requirement will also be met with a small safety margin.

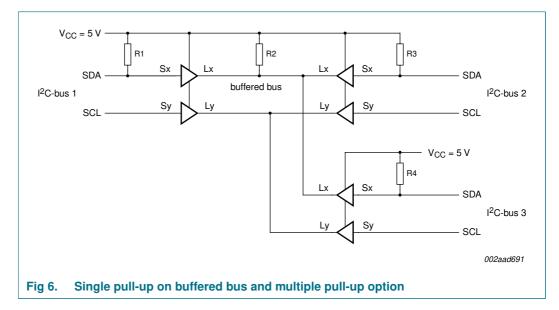

This arrangement, using multiple pull-ups as in <u>Figure 6</u>, provides the best system performance and allows stand-alone operation of individual l<sup>2</sup>C-buses if parts of the extended system are disconnected or re-connected. For each bus section the pull-up resistor for a Standard-mode system is calculated as shown in Equation 1:

$$R = \frac{l \ \mu s}{C \ device + C \ wiring} \tag{1}$$

Where: C device = sum of any connected device capacitances, and C wiring = total wiring and stray capacitance on the bus section.

**Remark:** The 1  $\mu$ s is an approximation, with a safety factor, to the theoretical time-constant necessary to meet the Standard-mode 1  $\mu$ s bus rise time specification in a system with variable logic thresholds where the CMOS limits of 30 % and 70 % of V<sub>CC</sub> apply. The actual RC requirement can be shown to be 1.18  $\mu$ s. For a Fast-mode system, and the same safety margin, replace the 1  $\mu$ s with its 300 ns requirement.

If these capacitances cannot be measured or calculated then an approximation can be made by assuming that each device presents 10 pF of load capacitance and 10 pF of trace capacitance and that cables range from 50 pF to 100 pF per meter.

If only a single pull-up must be used then it must be placed on the buffered bus (as R2 in Figure 6) and the associated total system capacitance calculated by combining the individual bus capacitances into an equivalent capacitive loading on the buffered bus.

This equivalent capacitance is the sum of the capacitance on the buffered bus plus 10 times the sum of the capacitances on all the connected  $l^2C$ -bus nodes. The calculated value should not exceed 4 nF. The single buffered bus pull-up resistor is then calculated to achieve the rise time requirement and it then provides the pull-up for the buffered bus and for all other connected  $l^2C$ -bus nodes included in the calculation.

#### 8.1.2 Calculating static bus drive currents

Figure 6 shows three P82B715s connected to a common buffered bus. The associated bus capacitances are omitted for clarity and we assume the pull-up resistors have been selected to give RC products equal to the bus rise time requirement. An I<sup>2</sup>C-bus chip connected at I<sup>2</sup>C-bus 1 and holding the SDA bus LOW must sink the current flowing in its local pull-up R1 plus, with assistance from the P82B715, the currents in R2, R3 and R4. When I<sup>2</sup>C-bus 1 is LOW, the resistors R3 and R4 act to pull the bus nodes I<sup>2</sup>C-bus 2 and I<sup>2</sup>C-bus 3, and their corresponding Sx pins, to a voltage higher than the voltage at their Lx pins (which are LOW) so their buffer amplifiers will be inactive. The SDA at Sx of I<sup>2</sup>C-bus 2 and I<sup>2</sup>C-bus 3 is pulled LOW by the LOW at Lx via the internal 30 Ω resistor that links Lx to Sx. So the effective current that must be sunk by the P82B715 buffer on I<sup>2</sup>C-bus 1, at its Lx pin, is the sum of the currents in R2, R3 and R4. The Sx current that must be sunk by an I<sup>2</sup>C-bus chip at I<sup>2</sup>C-bus 1, due to the buffer gain action, is 1/<sub>10</sub> of the Lx current. So the effective pull-up, determining the current to be sunk by an I<sup>2</sup>C-bus chip at I<sup>2</sup>C-bus 1, is R1 in parallel with resistors 10 times the values of R2, R3 and R4. If R1 = R3 = R4 = 10 kΩ, and R2 = 1 kΩ, the effective pull-up load at I<sup>2</sup>C-bus 1 is

10 k $\Omega \parallel$  10 k $\Omega \parallel$  100 k $\Omega \parallel$  100 k $\Omega = 4.55$  k $\Omega$ . (' $\parallel$ ' means 'in parallel with'.)

The same calculation applies for  $I^2$ C-bus 2 or  $I^2$ C-bus 3.

To calculate the current sunk by the Lx pin of the buffer at  $l^2$ C-bus 1, note that the current in R1 is sunk directly by the IC at  $l^2$ C-bus 1. The buffer therefore sinks only the currents flowing in R2, R3, and R4 so the effective pull-up is R2 in parallel with R3 and R4.

In this example that is 1 k $\Omega \parallel$  10 k $\Omega \parallel$  10 k $\Omega = 833 \Omega$ . For a 5.5 V supply and 0.4 V LOW, that means the buffer is sinking 16.3 mA.

I<sup>2</sup>C-bus extender

The P82B715 has a static sink rating of 30 mA at Lx. The requirement is that the pull-up on the buffered bus, in parallel with all other pull-ups that it is indirectly pulling LOW on Sx pins of other P82B715 ICs, will not cause this 30 mA limit to be exceeded.

The minimum pull-up resistance in a 5 V  $\pm$  10 % system is 170  $\Omega.$

The general requirement is given in Equation 2:

$$\frac{V_{CC(max)} - 0.4 V}{R_{PU}} < 30 mA$$

(2)

Where:  $R_{PU}$  = parallel combination of all pull-up resistors driven by the Lx pin of the P82B715.

Figure 7 shows calculations for an expanded Standard-mode I<sup>2</sup>C-bus with 3 nF of cable capacitance.

#### I<sup>2</sup>C-bus extender

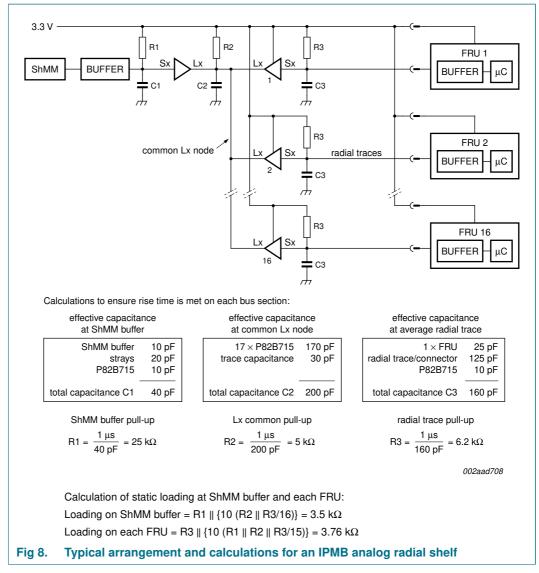

Figure 8 shows P82B715 in an analog radial IPMB shelf application.

In this example the total system capacitance is 2800 pF, but it is distributed over 18 different bus sections and no section has a capacitance greater than 200 pF.

If every individual bus section is designed to rise at least as fast as the IPMB requirement, then when any driver releases the bus, all bus sections will rise together and no amplifiers in the P82B715s will be activated or, if one is activated, it can only slow the system bus rise to its own rate and that has been designed to meet the requirement.

It is then only necessary to calculate the equivalent static bus pull-up loading and to ensure that it exceeds the specification requirement. The calculated loadings meet the requirements.

Note that in this example only one of the four IPMB lines is shown and the usual switching arrangements for isolating or cross-connecting bus lines are not shown. The typical offset (increase in the bus LOW level) measured between any two Sx points in this system is below 100 mV.

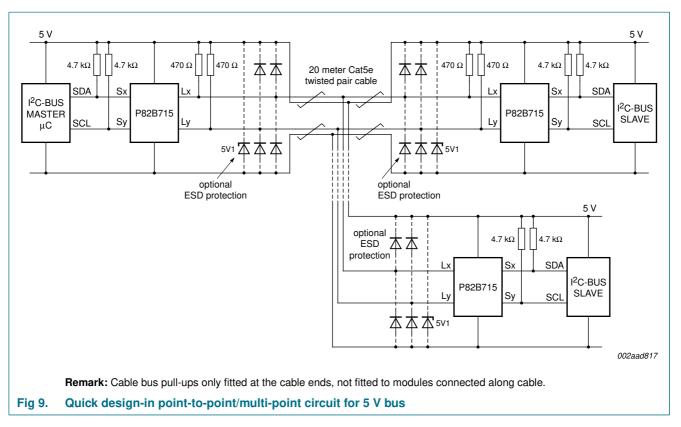

## 8.2 Quick design-in point-to-point/multi-point circuit information for 5 V bus

With many variables (cable length/capacitance, local capacitive loading on each I<sup>2</sup>C-bus, bus voltages, and bus speed), optimizing a design can be complex and requires significant study of the application note information. The following circuit and simplified approach has been checked to provide adequate performance in the typical 100 kHz application and can be easily implemented by just using the values and circuit shown for either point-to-point application, up to 30 meters long, or in multiple point applications if additional nodes need to be added along the way.

Specific information on this circuit implementation:

- The pull-up on each I²C-bus is (V\_{CC} 0.4 V) / 1 mA = 4.6 kΩ, using 4.7 kΩ as the nearest usual value.

- The net pull-up on the cable bus can be  $(V_{CC} 0.5 \text{ V}) / (21 n)$  mA where n = total number of P82B715 modules on the cable. When there are only two modules, one each end of the cable, the pull-up =  $(4.5 / 19) = 237 \Omega$ . Make the pull-ups at each end of the cable equal. Signalling is bidirectional so there is no advantage optimizing for any one direction. The pull-up at each end will be 474  $\Omega$ , using 470  $\Omega$  as the nearest usual value.

- The 100 kHz rise time requirement is 1  $\mu$ s. Meeting this requires the product of the bus capacitance and pull-up resistor on each bus section to be less than 1.18  $\mu$ s. That provides one capacitance limit. With 4.7 k $\Omega$  pull-ups the l<sup>2</sup>C-bus limit is 250 pF each, while the 235  $\Omega$  sets a cable bus limit at 5000 pF.

I<sup>2</sup>C-bus extender

- The 300 ns bus fall time, and the Standard-mode I<sup>2</sup>C-bus limit specification limit of 400 pF, must also be observed. If the 400 pF limit is observed the fall time limit will be met. Allocate about 1/3 of this 400 pF limit, or 133 pF, to each I<sup>2</sup>C-bus leaving 2/3, or 266 pF, for the cable bus loading as it will appear at the Sx/Sy pins. The ×10 gain of P82B715 allows the loading at Lx/Ly to be 10 times the load at Sx/Sy, so 2660 pF maximum. The loading at Lx/Ly due to the other standard buses is 133 pF each. For just one remote module the cable capacitance may then be up to (2660 133) = 2530 pF. For typical twisted pair or flat cables, as used for telephony or Ethernet (Cat5e) wiring, that capacitance is around 50 pF to 70 pF / meter so the cable could, in theory, be up to 50 m long. From practical experience, 30 m has proven a safe cable length to be driven in this simple way, up to 100 kHz, with the values shown. Longer distances and higher speeds are possible but require more careful design.

- If there are severe EMI/ESD tests to be passed then large clamp diodes can be fitted on the cable bus at each module to V<sub>CC</sub> and to ground. They may be diodes rated for this ESD application, or simply large rectifiers (1N4000). The low-impedance bus easily accommodates their relatively large capacitance. The P82B715 does not provide any isolation between Lx and Sx, so this clamping method provides the best protection for the lower voltage l<sup>2</sup>C-bus parts. The V<sub>CC</sub> supply should be bypassed using low-impedance capacitors. Zeners may be fitted to prevent the supply rising due to rectification during very large interference.

## 8.3 Comparison of P82B715 versus P82B96 in the quick design-in point-to-point/multi-point circuit

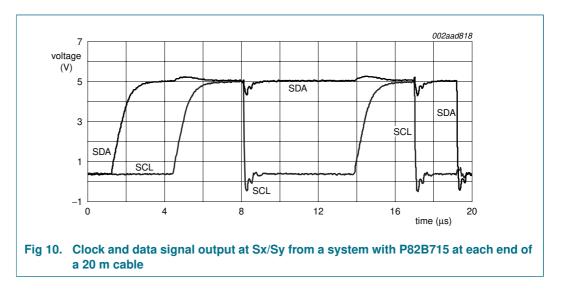

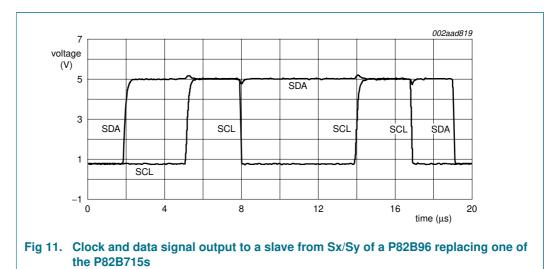

The lower V<sub>OL</sub> level and ability to operate with any master, slave or bus buffer is the primary advantage of the using the P82B715 for long distance buses at the disadvantage of not isolating bus capacitance like the P82B96 or PCA9600 are able to do. The primary disadvantage of the P82B96 and PCA9600 is that the static level offset needed to isolate bus capacitance does not allow these devices to operate with other bus buffers with special offset levels or with master/slaves that require a V<sub>IL</sub> lower than 0.8 V with noise margin. Waveforms using the circuit shown in Figure 9 are shown in Figure 10 using the P82B715 and Figure 11 using the P82B96 so that the designer can clearly see these trade-offs and choose the type of device that is best for their application.

Figure 10 shows the l<sup>2</sup>C-bus waveforms from the long distance line as seen by the slave on the P82B715 Sx/Sy I/O. Notice that the offset is small and the static levels remain under 0.4 V. Coupling of SDA to SCL is negligible when SCL is LOW but slight cross-coupling of SCL to SDA is visible when SDA is HIGH and therefore higher impedance. The waveforms are very clean and will easily support all available l<sup>2</sup>C-bus masters and slaves.

Figure 11 shows the waveforms on the Sx/Sy I/O as seen by the slave when a P82B96 is substituted. P82B96 uses a static level offset on the slave side to isolate noise and loadings on either side of this device. The nominal offset is 0.8 V and that  $V_{OL}$  may create worst-case design tolerance problems with slave devices that do not use I<sup>2</sup>C-bus switching levels, for example TTL levels. It also precludes operation with other bus buffers using special non-compliant I<sup>2</sup>C-bus levels.

The P82B96 does not actually interfere with the **operation** of compliant I<sup>2</sup>C-bus devices down to at least 2.7 V supply or even with TTL devices (that switch around 1.4 V). It only causes a theoretical worst case design tolerance problem because TTL devices have a worst case 0.8 V requirement. A TTL designer must center the actual switch point between the **two** specified limits, 0.8 V and 2.1 V, so in reality it cannot ever approach the problem 0.8 V theoretical limit.

The PCA9600 is an improved version of the P82B96 offering 1 MHz operation and lower, more closely controlled  $V_{OL}$  on the Sx and Sy pins.

## 9. Limiting values

| Table 4.<br>In accorda | Table 4.         Limiting values           In accordance with the Absolute Maximum Rating System (IEC 60134). |            |                 |                 |      |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------------|------------|-----------------|-----------------|------|--|--|

| Symbol                 | Parameter                                                                                                     | Conditions | Min             | Max             | Unit |  |  |

| V <sub>CC</sub>        | supply voltage                                                                                                |            | <u>[1]</u> –0.3 | +12             | V    |  |  |

| V <sub>bus</sub>       | voltage range I <sup>2</sup> C-bus, SCL or SDA                                                                |            | <u>[1]</u> 0    | V <sub>CC</sub> | V    |  |  |

| V <sub>buff</sub>      | voltage range buffered bus                                                                                    |            | <u>[1]</u> 0    | V <sub>CC</sub> | V    |  |  |

| I                      | DC current (any pin)                                                                                          |            | -               | 60              | mA   |  |  |

| P <sub>tot</sub>       | total power dissipation                                                                                       |            | -               | 300             | mW   |  |  |

| T <sub>stg</sub>       | storage temperature                                                                                           |            | -55             | +125            | °C   |  |  |

| T <sub>amb</sub>       | ambient temperature                                                                                           | operating  | -40             | +85             | °C   |  |  |

|                        |                                                                                                               |            |                 |                 |      |  |  |

[1] Voltages with respect to GND.

The bus voltages quoted are DC voltages and are allowed to be exceeded during any negative transient undershoot that may be generated by normal operation of P82B715, P82B96 or PCA9600 when any of those parts are driving long PCB traces, wiring or cables. The Lx/Sx pins have internal protective diodes to GND that will conduct when the applied bus voltage exceeds approximately -0.6 V and these diodes will limit the amplitude of the negative undershoot. If required, fitting additional Schottky diodes such as BAT54A at Sx/Sy may be used to further ensure any undershoot at these pins does not cause conduction of the diodes inside other ICs connected to Sx/Sy.

## **10. Characteristics**

#### Table 5. Characteristics

$T_{amb} = 25 \circ C$ ;  $V_{CC} = 5 V$ ; unless otherwise specified.

| Symbol                            | Parameter                                  | Conditions                                                                                                                                                                                               |     | Min | Тур | Мах | Unit |

|-----------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|------|

| Power su                          | pply                                       |                                                                                                                                                                                                          |     |     |     |     |      |

| V <sub>CC</sub>                   | supply voltage                             | operating                                                                                                                                                                                                | [1] | 4.5 | -   | 12  | V    |

| I <sub>CC</sub>                   | supply current                             |                                                                                                                                                                                                          |     | -   | 14  | -   | mA   |

|                                   |                                            | V <sub>CC</sub> = 12 V                                                                                                                                                                                   |     | -   | 15  | -   | mA   |

|                                   |                                            | both I <sup>2</sup> C-bus inputs LOW; both<br>buffered outputs sinking 30 mA                                                                                                                             |     | -   | 22  | -   | mA   |

| Drive cur                         | rents                                      |                                                                                                                                                                                                          |     |     |     |     |      |

| I <sub>Sx</sub> , I <sub>Sy</sub> | output sink on I <sup>2</sup> C-bus        | $\label{eq:V_CC} \begin{array}{l} V_{CC} > 3 \; V; \; V_{Sx}, \; V_{Sy} \; LOW = 0.4 \; V; \\ V_{Lx}, \; V_{Ly} \; LOW \; on \; buffered \; bus = 0.3 \; V; \\ I_{Lx}, \; I_{Ly} = -3 \; mA \end{array}$ | [2] | 3   | -   | -   | mA   |

| $I_{Lx}, I_{Ly}$                  | output sink on buffered bus                | $ \begin{array}{l} V_{Lx},  V_{Ly}  LOW = 0.4 \ V; \\ V_{Sx},  V_{Sy}  LOW \ on \ l^2C \hbox{-} bus = 0.3 \ V \end{array} $                                                                              |     | 30  | -   | -   | mA   |

| Derated d                         | lynamic drive currents for V <sub>CC</sub> | < 4.5 V[ <u>1]</u>                                                                                                                                                                                       |     |     |     |     |      |

| I <sub>Lx</sub> , I <sub>Ly</sub> | output sink on buffered bus                | $V_{CC} > 3 V;$<br>$V_{Lx}$ , $V_{Ly} LOW = 0.4 V$ to 1.5 V;<br>$I_{Sx}$ , $I_{Sy}$ sinking on I <sup>2</sup> C-bus < -4 mA                                                                              |     | 24  | -   | -   | mA   |

|                                   |                                            | $V_{CC} > 3 V;$<br>$V_{Lx}$ , $V_{Ly} LOW = 1.5 V$ to $V_{CC};$<br>$I_{Sx}$ , $I_{Sy}$ sinking on I <sup>2</sup> C-bus = -7 mA                                                                           |     | 24  | -   | -   | mA   |

I<sup>2</sup>C-bus extender

#### Table 5. Characteristics ...continued

$T_{amb} = 25 \circ C$ ;  $V_{CC} = 5 V$ ; unless otherwise specified.

| Symbol                                                                                                   | Parameter                                                                                         | Conditions                                                                                   | Min          | Тур | Max | Unit |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------|-----|-----|------|

| Input curre                                                                                              | ents                                                                                              |                                                                                              |              |     |     |      |

| I <sub>Sx</sub> , I <sub>Sy</sub>                                                                        | input current from I <sup>2</sup> C-bus                                                           | $I_{Lx}$ , $I_{Ly}$ sink on buffered bus = 30 mA                                             | -            | -   | -3  | mA   |

| $I_{Lx}, I_{Ly}$                                                                                         | input current from buffered bus                                                                   | $V_{CC}$ > 3 V; I <sub>Sx</sub> , I <sub>Sy</sub> sink on I <sup>2</sup> C-bus = 3 mA        | [2] _        | -   | -3  | mA   |

| I <sub>Lx</sub> , I <sub>Ly</sub>                                                                        | leakage current on buffered bus                                                                   | $V_{CC}$ = 3 V to 12 V; $V_{Lx},V_{Ly}$ = $V_{CC}$ and $V_{Sx},V_{Sy}$ = $V_{CC}$            | -            | -   | 200 | μA   |

| Impedance                                                                                                | e transformation                                                                                  |                                                                                              |              |     |     |      |

| Z <sub>in</sub> /Z <sub>out</sub>                                                                        | input/output impedance                                                                            | $V_{Sx} < V_{Lx}$ and the buffer is active;<br>I <sub>Lx</sub> sinking 30 mA on buffered bus | 8            | 10  | 13  |      |

| Buffer dela                                                                                              | ay times                                                                                          |                                                                                              |              |     |     |      |

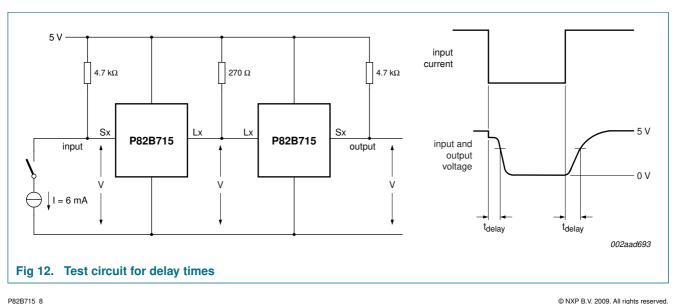

| $t_{rise/fall delay}$<br>$I_{Sx}$ to $V_{Lx}$<br>$I_{Sy}$ to $V_{Ly}$                                    | time delay to $V_{Lx}$ voltage crossing $0.5V_{CC}$ for input drive current step $I_{Sx}$ at $Sx$ | see Figure 12; $R_{Lx}$ pull-up = 270 $\Omega$ ;<br>no capacitive load; $V_{CC}$ = 5 V       | <u>[3]</u> _ | 250 | -   | ns   |

| t <sub>rise/fall delay</sub><br>V <sub>Lx</sub> to V <sub>Sx</sub><br>V <sub>Ly</sub> to V <sub>Sy</sub> | buffer time delay of switching edges between $V_{Lx}$ input and $V_{Sx}$ output                   | $R_{Sx}$ pull-up = 4700 $\Omega$ ;<br>no capacitive load; $V_{CC}$ = 5 V                     | <u>[4]</u> _ | 0   | -   | ns   |

[1] Operation with reduced performance is possible down to 3 V. Typical static sinking performance is not degraded at 3 V, but the dynamic sink currents while the output is being driven through 0.5V<sub>CC</sub> are reduced and can increase fall times. Timing-critical designs should accommodate the guaranteed minimums.

[2] Buffer is passive in this test. The Sx/Sy sink current flows via an internal resistor to the driver connected at the Lx/Ly I/O.

[3] A conventional input-output delay will not be observed in the Sx/Lx voltage waveforms because the input and output pins are internally tied with a 30 Ω resistor so they show equal logic voltage levels, to within 100 mV. When connected in an I<sup>2</sup>C-bus system, an Sx/Sy input pin cannot rise/fall until the buffered bus load at the output pin has been driven by the internal amplifier. This test measures the bus propagation delay caused to falling or rising voltages at the Lx/Ly output (as well as the Sx/Sy input) by the amplifier's response time. The figure given is measured with a drive current as shown in Figure 12. Because this is a dynamic bus test in which a corresponding bus driving IC has an output voltage well above 0.4 V, 6 mA is used instead of the static 3 mA.

[4] The signal path Lx to Sx and Ly to Sy is passive via the internal 30  $\Omega$  resistor. There is no amplifier involved and essentially no signal propagation delay.

## 11. Test information

P82B715 I<sup>2</sup>C-bus extender

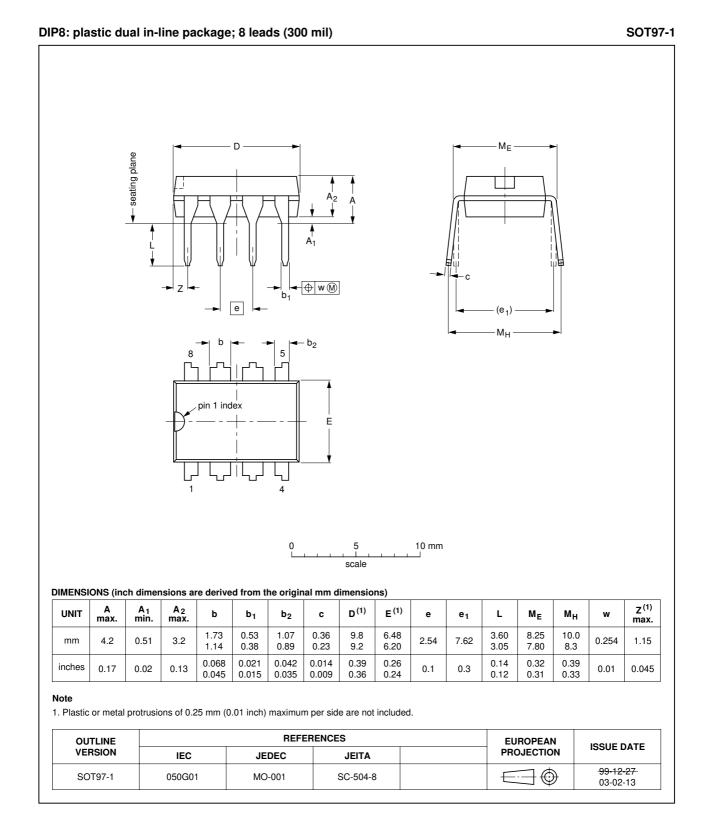

## 12. Package outline

#### Fig 13. Package outline SOT97-1 (DIP8)

#### Fig 14. Package outline SOT96-1 (SO8)

## 13. Soldering of SMD packages

This text provides a very brief insight into a complex technology. A more in-depth account of soldering ICs can be found in Application Note *AN10365 "Surface mount reflow soldering description"*.

#### 13.1 Introduction to soldering

Soldering is one of the most common methods through which packages are attached to Printed Circuit Boards (PCBs), to form electrical circuits. The soldered joint provides both the mechanical and the electrical connection. There is no single soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and Surface Mount Devices (SMDs) are mixed on one printed wiring board; however, it is not suitable for fine pitch SMDs. Reflow soldering is ideal for the small pitches and high densities that come with increased miniaturization.

#### 13.2 Wave and reflow soldering

Wave soldering is a joining technology in which the joints are made by solder coming from a standing wave of liquid solder. The wave soldering process is suitable for the following:

- Through-hole components

- · Leaded or leadless SMDs, which are glued to the surface of the printed circuit board

Not all SMDs can be wave soldered. Packages with solder balls, and some leadless packages which have solder lands underneath the body, cannot be wave soldered. Also, leaded SMDs with leads having a pitch smaller than ~0.6 mm cannot be wave soldered, due to an increased probability of bridging.

The reflow soldering process involves applying solder paste to a board, followed by component placement and exposure to a temperature profile. Leaded packages, packages with solder balls, and leadless packages are all reflow solderable.

Key characteristics in both wave and reflow soldering are:

- · Board specifications, including the board finish, solder masks and vias

- · Package footprints, including solder thieves and orientation

- · The moisture sensitivity level of the packages

- Package placement

- Inspection and repair

- Lead-free soldering versus SnPb soldering

#### 13.3 Wave soldering

Key characteristics in wave soldering are:

- Process issues, such as application of adhesive and flux, clinching of leads, board transport, the solder wave parameters, and the time during which components are exposed to the wave

- · Solder bath specifications, including temperature and impurities

#### 13.4 Reflow soldering

Key characteristics in reflow soldering are:

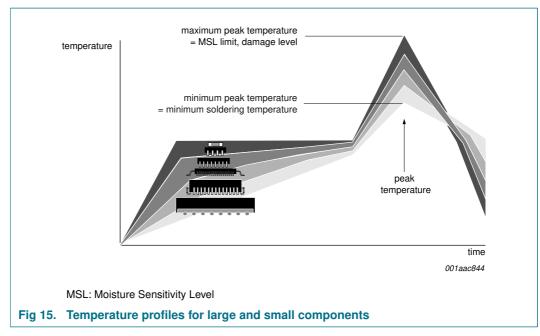

- Lead-free versus SnPb soldering; note that a lead-free reflow process usually leads to higher minimum peak temperatures (see <u>Figure 15</u>) than a SnPb process, thus reducing the process window

- Solder paste printing issues including smearing, release, and adjusting the process window for a mix of large and small components on one board

- Reflow temperature profile; this profile includes preheat, reflow (in which the board is heated to the peak temperature) and cooling down. It is imperative that the peak temperature is high enough for the solder to make reliable solder joints (a solder paste characteristic). In addition, the peak temperature must be low enough that the packages and/or boards are not damaged. The peak temperature of the package depends on package thickness and volume and is classified in accordance with Table 6 and 7

#### Table 6. SnPb eutectic process (from J-STD-020C)

| Package thickness (mm) | Package reflow temperature (°C) |       |  |

|------------------------|---------------------------------|-------|--|

|                        | Volume (mm <sup>3</sup> )       |       |  |

|                        | < 350                           | ≥ 350 |  |

| < 2.5                  | 235                             | 220   |  |

| ≥ 2.5                  | 220                             | 220   |  |

#### Table 7. Lead-free process (from J-STD-020C)

| Package thickness (mm) | Package reflow temperature (°C) |             |        |  |

|------------------------|---------------------------------|-------------|--------|--|

|                        | Volume (mm <sup>3</sup> )       |             |        |  |

|                        | < 350                           | 350 to 2000 | > 2000 |  |

| < 1.6                  | 260                             | 260         | 260    |  |

| 1.6 to 2.5             | 260                             | 250         | 245    |  |

| > 2.5                  | 250                             | 245         | 245    |  |

Moisture sensitivity precautions, as indicated on the packing, must be respected at all times.

Studies have shown that small packages reach higher temperatures during reflow soldering, see Figure 15.

## P82B715

I<sup>2</sup>C-bus extender

For further information on temperature profiles, refer to Application Note *AN10365 "Surface mount reflow soldering description"*.

## 14. Soldering of through-hole mount packages

#### 14.1 Introduction to soldering through-hole mount packages

This text gives a very brief insight into wave, dip and manual soldering.

Wave soldering is the preferred method for mounting of through-hole mount IC packages on a printed-circuit board.

#### 14.2 Soldering by dipping or by solder wave

Driven by legislation and environmental forces the worldwide use of lead-free solder pastes is increasing. Typical dwell time of the leads in the wave ranges from 3 seconds to 4 seconds at 250 °C or 265 °C, depending on solder material applied, SnPb or Pb-free respectively.

The total contact time of successive solder waves must not exceed 5 seconds.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified maximum storage temperature  $(T_{stg(max)})$ . If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

#### 14.3 Manual soldering

Apply the soldering iron (24 V or less) to the lead(s) of the package, either below the seating plane or not more than 2 mm above it. If the temperature of the soldering iron bit is less than 300 °C it may remain in contact for up to 10 seconds. If the bit temperature is between 300 °C and 400 °C, contact may be up to 5 seconds.

#### 14.4 Package related soldering information

#### Table 8. Suitability of through-hole mount IC packages for dipping and wave soldering

| Package                         | Soldering method |                         |  |

|---------------------------------|------------------|-------------------------|--|

|                                 | Dipping          | Wave                    |  |

| CPGA, HCPGA                     | -                | suitable                |  |

| DBS, DIP, HDIP, RDBS, SDIP, SIL | suitable         | suitable <sup>[1]</sup> |  |

| PMFP <sup>[2]</sup>             | -                | not suitable            |  |

[1] For SDIP packages, the longitudinal axis must be parallel to the transport direction of the printed-circuit board.

[2] For PMFP packages hot bar soldering or manual soldering is suitable.

### 15. Abbreviations

| Table 9. Abbreviations |                                         |  |  |

|------------------------|-----------------------------------------|--|--|

| Acronym                | Description                             |  |  |

| AdvancedTCA            | Advanced Telecom Computing Architecture |  |  |

| CMOS                   | Complementary Metal-Oxide Semiconductor |  |  |

| DDC                    | Data Display Channel                    |  |  |

| EMI                    | ElectroMagnetic Interference            |  |  |

| ESD                    | ElectroStatic Discharge                 |  |  |

| FRU                    | Field Replaceable Unit                  |  |  |

| HBM                    | Human Body Model                        |  |  |

| I <sup>2</sup> C-bus   | Inter-Integrated Circuit bus            |  |  |

| I/O                    | Input/Output                            |  |  |

| IC                     | Integrated Circuit                      |  |  |

| IPMB                   | Intelligent Platform Management Bus     |  |  |

| MM                     | Machine Model                           |  |  |

| PMBus                  | Power Management Bus                    |  |  |

| RC                     | Resistor-Capacitor network              |  |  |

| ShMM                   | Shelf Management Module                 |  |  |

| SMBus                  | System Management Bus                   |  |  |

| TTL                    | Transistor-Transistor Logic             |  |  |

## 16. Revision history

| Table 10. Revisio             | n history             |                                  |                                          |            |

|-------------------------------|-----------------------|----------------------------------|------------------------------------------|------------|

| Document ID                   | Release date          | Data sheet status                | Change notice                            | Supersedes |

| P82B715_8                     | 20091109              | Product data sheet               | -                                        | P82B715_7  |

| Modifications:                | <u>Table 4 "Limit</u> | ing values", Table note [1]: add | ed 2 <sup>nd</sup> paragraph.            |            |

| P82B715_7                     | 20080529              | Product data sheet               | -                                        | P82B715_6  |

| P82B715_6<br>(9397 750 12452) | 20031202              | Product data                     | ECN 853-2240 01-A14516<br>of 14 Nov 2003 | P82B715_5  |

| P82B715_5<br>(9397 750 11094) | 20030220              | Product data                     | ECN 853-2240 29410<br>of 22 Jan 2003     | P82B715_4  |

| P82B715_4<br>(9397 750 08163) | 20010306              | Product data                     | ECN 853-2240 25757<br>of 06 Mar 2001     | P82B715_3  |

|                               |                       |                                  |                                          |            |

## 17. Legal information

#### 17.1 Data sheet status

| Document status[1][2]          | Product status <sup>[3]</sup> | Definition                                                                            |

|--------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production                    | This document contains the product specification.                                     |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

#### 17.2 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

#### 17.3 Disclaimers

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

#### 17.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

## **18. Contact information**

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

## P82B715

I<sup>2</sup>C-bus extender

### **19. Contents**

| 1                                                                                                                                                                                                    | General description 1                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                                                                                                                                                                                                    | Features 1                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3                                                                                                                                                                                                    | Applications 2                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4                                                                                                                                                                                                    | Ordering information 2                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.1                                                                                                                                                                                                  | Ordering options 2                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5                                                                                                                                                                                                    | Block diagram 3                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6                                                                                                                                                                                                    | Pinning information 3                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6.1                                                                                                                                                                                                  | Pinning                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.2                                                                                                                                                                                                  | Pin description 3                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7                                                                                                                                                                                                    | Functional description 4                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7.1                                                                                                                                                                                                  | Sx, Sy: I <sup>2</sup> C-bus SDA or SCL                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7.2                                                                                                                                                                                                  | Lx, Ly: buffered bus LDA or LCL 5                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7.3                                                                                                                                                                                                  | $V_{CC}$ , GND: positive and negative supply pins 5                                                                                                                                                                                                                                                                                                                                                                                             |

| 8                                                                                                                                                                                                    | Application design-in information 5                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8.1                                                                                                                                                                                                  | I <sup>2</sup> C-bus systems 6                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8.1.1                                                                                                                                                                                                | Pull-up resistance calculation 6                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8.1.2                                                                                                                                                                                                | Calculating static bus drive currents                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8.2                                                                                                                                                                                                  | Quick design-in point-to-point/multi-point                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8.3                                                                                                                                                                                                  | circuit information for 5 V bus                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0.5                                                                                                                                                                                                  | in the quick design-in point-to-point/                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                      | multi-point circuit                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9                                                                                                                                                                                                    | Limiting values 13                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9<br>10                                                                                                                                                                                              | Limiting values                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10                                                                                                                                                                                                   | Characteristics 13                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10<br>11                                                                                                                                                                                             | Characteristics13Test information14                                                                                                                                                                                                                                                                                                                                                                                                             |

| 10<br>11<br>12                                                                                                                                                                                       | Characteristics13Test information14Package outline15                                                                                                                                                                                                                                                                                                                                                                                            |

| 10<br>11<br>12<br>13                                                                                                                                                                                 | Characteristics13Test information14Package outline15Soldering of SMD packages17                                                                                                                                                                                                                                                                                                                                                                 |

| 10<br>11<br>12<br>13<br>13.1                                                                                                                                                                         | Characteristics13Test information14Package outline15Soldering of SMD packages17Introduction to soldering17                                                                                                                                                                                                                                                                                                                                      |

| <b>10</b><br><b>11</b><br><b>12</b><br><b>13</b><br>13.1<br>13.2                                                                                                                                     | Characteristics13Test information14Package outline15Soldering of SMD packages17Introduction to soldering17Wave and reflow soldering17                                                                                                                                                                                                                                                                                                           |

| <b>10</b><br><b>11</b><br><b>12</b><br><b>13</b><br>13.1<br>13.2<br>13.3                                                                                                                             | Characteristics13Test information14Package outline15Soldering of SMD packages17Introduction to soldering17Wave and reflow soldering17Wave soldering17                                                                                                                                                                                                                                                                                           |

| <b>10</b><br><b>11</b><br><b>12</b><br><b>13</b><br>13.1<br>13.2<br>13.3<br>13.4                                                                                                                     | Characteristics13Test information14Package outline15Soldering of SMD packages17Introduction to soldering17Wave and reflow soldering17Wave soldering17Reflow soldering18                                                                                                                                                                                                                                                                         |

| <b>10</b><br><b>11</b><br><b>12</b><br><b>13</b><br>13.1<br>13.2<br>13.3                                                                                                                             | Characteristics13Test information14Package outline15Soldering of SMD packages17Introduction to soldering17Wave and reflow soldering17Wave soldering17Reflow soldering18Soldering of through-hole mount packages19                                                                                                                                                                                                                               |

| 10<br>11<br>12<br>13<br>13.1<br>13.2<br>13.3<br>13.4<br>14                                                                                                                                           | Characteristics13Test information14Package outline15Soldering of SMD packages17Introduction to soldering17Wave and reflow soldering17Wave soldering17Reflow soldering18                                                                                                                                                                                                                                                                         |

| 10<br>11<br>12<br>13<br>13.1<br>13.2<br>13.3<br>13.4<br>14                                                                                                                                           | Characteristics13Test information14Package outline15Soldering of SMD packages17Introduction to soldering17Wave and reflow soldering17Wave soldering17Reflow soldering18Soldering of through-hole mount packages19Introduction to soldering through-hole mount19                                                                                                                                                                                 |

| 10         11         12         13         13.1         13.2         13.3         13.4         14         14.1                                                                                      | Characteristics13Test information14Package outline15Soldering of SMD packages17Introduction to soldering17Wave and reflow soldering17Wave soldering17Reflow soldering18Soldering of through-hole mount packages19Introduction to soldering through-hole mount19Soldering by dipping or by solder wave19Manual soldering19                                                                                                                       |

| <b>10</b><br><b>11</b><br><b>12</b><br><b>13</b><br>13.1<br>13.2<br>13.3<br>13.4<br><b>14</b><br>14.1<br>14.2                                                                                        | Characteristics13Test information14Package outline15Soldering of SMD packages17Introduction to soldering17Wave and reflow soldering17Wave soldering17Reflow soldering18Soldering of through-hole mount packages19Introduction to soldering through-hole mount packages19Soldering by dipping or by solder wave19                                                                                                                                |