# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# INTEGRATED CIRCUITS

Preliminary Specification File under Integrated Circuits, IC28 2000 Jul 26

| CONTEN | TS                                               | 17           | , |

|--------|--------------------------------------------------|--------------|---|

| 1      | FEATURES                                         | 18           | I |

| 1.1    | 80C51 Related Features of the 8xC591             | 18.1         | l |

| 1.2    | CAN Related Features of the 8xC591               | 18.2         | l |

| 2      | GENERAL DESCRIPTION                              | 18.3         |   |

|        |                                                  | 19           |   |

| 3      |                                                  | 20           |   |

| 4      | BLOCK DIAGRAM                                    | 20.1         |   |

| 5      | FUNCTIONAL DIAGRAM                               | 20.2         | 1 |

| 6      | PINNING INFORMATION                              | 20.3         |   |

| 6.1    | Pinning diagram                                  | 20.4<br>20.5 |   |

| 6.2    | Pin description                                  |              |   |

| 7      | MEMORY ORGANIZATION                              | 21           | l |

| 7.1    | Program Memory                                   | 21.1         |   |

| 7.2    | Addressing                                       | 21.2         |   |

| 7.3    | Expanded Data RAM addressing                     | 21.3<br>21.4 |   |

| 7.4    | Dual DPTR                                        |              |   |

| 8      | I/O FACILITIES                                   | 22           |   |

| 9      | OSCILLATOR CHARACTERISTICS                       | 22.1         |   |

| 10     | RESET                                            | 23           |   |

| 11     | LOW POWER MODES                                  | 24           |   |

| 11.1   | Stop Clock Mode                                  | 25           | 4 |

| 11.2   | Idle Mode                                        | 25.1         | - |

| 11.3   | Power-down Mode                                  | 26           | l |

| 12     | CAN, CONTROLLER AREA NETWORK                     | 26.1         | I |

| 12.1   | Features of the PeliCAN controller               | 26.2         |   |

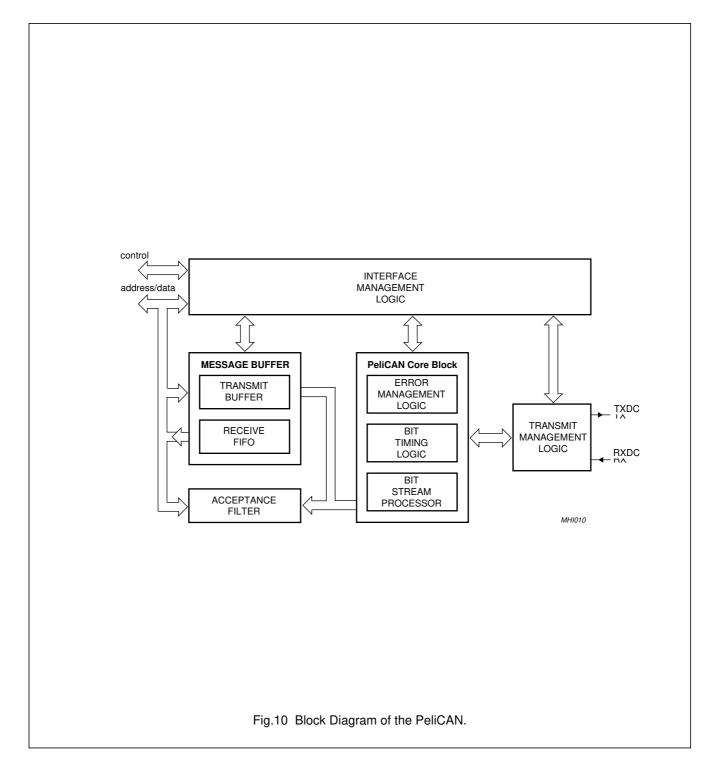

| 12.2   | PeliCAN structure                                | 27           |   |

| 12.3   | Communication between PeliCAN controller and CPU | 28           | : |

| 12.4   | Register and Message Buffer description          | 28.1         | l |

| 12.5   | CAN Registers                                    | 29           | l |

| 13     | SERIAL I/O                                       | 30           | l |

| 14     | SIO0 STANDARD SERIAL INTERFACE UART              |              |   |

| 14.1   | Multiprocessor Communications                    |              |   |

| 14.2   | Serial Port Control Register                     |              |   |

| 14.3   | Baud Rate Generation                             |              |   |

| 14.4   | More about UART Modes                            |              |   |

| 14.5   | Enhanced UART                                    |              |   |

- 15 SIO1, I<sup>2</sup>C SERIAL IO

- 15.1 Modes of Operation

- 15.2 SIO1 Implementation and Operation

- 15.3 Software Examples of SIO1 Service Routines

- 16 TIMER 2

- 16.1 Features of Timer 2

| 17                                   | WATCHDOG TIMER (T3)                                                                                                                                   |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18                                   | PULSE WIDTH MODULATED OUTPUTS                                                                                                                         |

| 18.1<br>18.2<br>18.3                 | Prescaler Frequency Control Register (PWMP)<br>Pulse Width Register 0 (PWM0)<br>Pulse Width Register 1 (PWM1)                                         |

| 19                                   | PORT 1 OPERATION                                                                                                                                      |

| 20                                   | ANALOG-TO-DIGITAL CONVERTER (ADC)                                                                                                                     |

| 20.1<br>20.2<br>20.3<br>20.4<br>20.5 | ADC features<br>ADC functional description<br>10-Bit Analog-to-Digital Conversion<br>10-Bit ADC Resolution and Analog Supply<br>Power Reduction Modes |

| 21                                   | INTERRUPTS                                                                                                                                            |

| 21.1<br>21.2<br>21.3<br>21.4         | Interrupt Enable Registers<br>Interrupt Enable and Priority Registers<br>Interrupt priority<br>Interrupt Vectors                                      |

| 22                                   | INSTRUCTION SET                                                                                                                                       |

| 22.1                                 | Addressing Modes                                                                                                                                      |

| 23                                   | LIMITING VALUES                                                                                                                                       |

| 24                                   | DC CHARACTERISTICS                                                                                                                                    |

| 25                                   | AC CHARACTERISTICS                                                                                                                                    |

| 25.1                                 | Timing symbol definitions                                                                                                                             |

| 26                                   | EPROM CHARACTERISTICS                                                                                                                                 |

| 26.1<br>26.2                         | Program verification<br>Security bits                                                                                                                 |

| 27                                   | PACKAGE OUTLINES                                                                                                                                      |

| 28                                   | SOLDERING                                                                                                                                             |

| 28.1                                 | Plastic leaded-chip carriers/quad flat-packs                                                                                                          |

|                                      |                                                                                                                                                       |

- 29 DEFINITIONS

- 30 LIFE SUPPORT APPLICATIONS

### P8xC591

#### **1 FEATURES**

#### 1.1 80C51 Related Features of the 8xC591

- Full static 80C51 Central Processing Unit available as OTP, ROM and ROMless

- 16 Kbytes internal Program Memory expandable externally to 64 Kbytes

- 512 bytes on-chip Data RAM expandable externally to 64 Kbytes

- Three 16-bit timers/counters T0, T1 (standard 80C51) and additional T2 (capture & compare)

- 10-bit ADC with 6 multiplexed analog inputs with fast 8-bit ADC option

- Two 8-bit resolution, Pulse Width Modulated outputs

- 32 I/O port pins in the standard 80C51 pinout

- I<sup>2</sup>C-bus serial I/O port with byte oriented master and slave functions

- On-chip Watchdog Timer T3

- Extended temperature range: -40 to +85°C

- Accelerated (prescaler 1:1) instruction cycle time 500 ns @ 12 MHz

- Operation voltage range: 5 V  $\pm$  5%

- Security bits:

- ROM version has 2 bits

- OTP/EPROM version has 3 bits

- 32 bytes Encryption array

- 4 level priority interrupt, 15 interrupt sources

- Full-duplex enhanced UART with programmable Baudrate Generator

- Power Control Modes:

- Clock can be stopped and resumed

- Idle Mode

- Power-down Mode

- ADC active in Idle Mode

- Second DPTR register

- ALE inhibit for EMI reduction

- Programmable I/O port pins (pseudo bi-directional, push-pull, high impedance, open drain)

- · Wake-up from Power-down by external interrupts

- Software reset bit (AUXR1.5)

- · Low active reset pin

- Power-on detect reset

- Once mode

### 1.2 CAN Related Features of the 8xC591

- CAN 2.0B active controller, supporting 11-bit Standard and 29-bit Extended indentifiers

- 1 Mbit/s CAN bus speed with 8 MHz clock achievable

- 64 byte receive FIFO (can capture sequential Data Frames from the *same* source as required by the Transport Layer of higher protocols such as DeviceNet, CANopen and OSEK)

- 13 byte transmit buffer

- Enhanced PeliCAN core (from the SJA1000 stand-alone CAN2.0B controller)

#### 1.2.1 PELICAN FEATURES

- Four independently configurable Screeners (Acceptance Filters)

- Each Screener has two 32-bit specifies:

- 32-bit Match and

- 32-bit Mask

- 32-bits of Mask *per Screener* allows *unique* Group addressing per *Screener*

- Higher layer protocols especially supported in Standard CAN format with:

- Up to four, 11-bit ID Screeners that also Screen the two (2) Data Bytes

- i.e., Data Frames are Screened by the CAN ID and by Data Byte content

- Up to eight, 11-bit ID Screeners half of which *also* Screen the *first* Data Byte

- · All Screeners are changeable "on the fly"

- Listen Only Mode, Self Test Mode

- Error Code Capture, Arbitration Lost Capture, readable Error Counters

### P8xC591

### 2 GENERAL DESCRIPTION

The P8xC591 is a single-chip 8-bit-high-performance microcontroller, with on-chip CAN-controller, derived from the 80C51 microcontroller family.

It uses the powerful 80C51 instruction set and includes the successful PeliCAN functionality of the SJA1000 CAN controller from Philips Semiconductors.

The fully static core provides extended power save provisions as the oscillator can be stopped and easily restarted without loss of data. The improved internal clock prescaler of 1:1 achieves a 500 ns instruction cycle time at 12 MHz external clock rate.

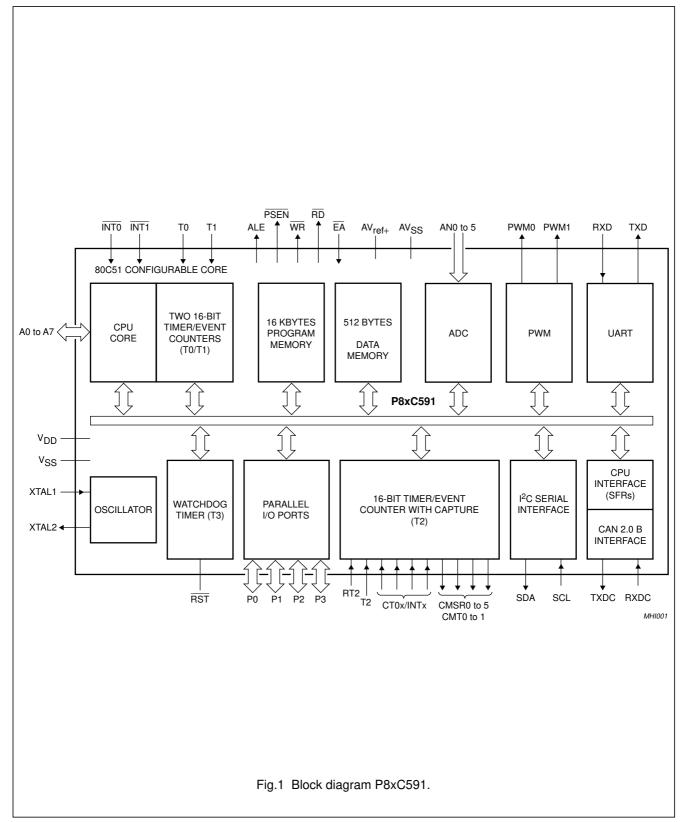

Figure 1 shows a Block Diagram of the P8xC591. The microcontroller is manufactured in an advanced CMOS process, and is designed for use in automotive and general industrial applications. In addition to the 80C51 standard features, the device provides a number of dedicated hardware functions for these applications.

Two versions of the P8xC591 will be offered:

- P83C591 (with ROM)

- P87C591 (with OTP)

Hereafter these versions will be referred to as P8xC591.

### **3 ORDERING INFORMATION**

- The temperature range includes (max.  $f_{CLK} = 12 \text{ MHz}$ ):

- -40 to +85 °C version, for general applications

The P8xC591 combines the functions of the P87C554 (microcontroller) and the SJA1000 (stand-alone CAN-controller) with the following enhanced features:

- Enhanced CAN receive interrupt (level sensitive)

- Extended acceptance filter

- Acceptance filter changeable "on the fly".

The main differences between P8xC591 and P87C554 are:

- CAN-controller on chip

- 6-input ADC

- · Low active Reset

- 44 leads.

| TYPE NUMBER  |        | TEMPERATURE                                               |          |            |  |

|--------------|--------|-----------------------------------------------------------|----------|------------|--|

| I TPE NUMBER | NAME   | RANGE (°C)                                                |          |            |  |

| P83C591VFA   | PLCC44 | plastic leaded chip carrier; 44 leads                     | SOT187-2 |            |  |

| P87C591VFA   | FL0044 | plastic leaded chip carrier, 44 leads                     | 301107-2 | -40 to +85 |  |

| P83C591VFB   | QFP44  | plastic quad flat package; 44 leads (lead length 1.3 mm); | SOT307-2 | -40 (0 +65 |  |

| P87C591VFB   |        | body $10 \times 10 \times 1.75 \text{ mm}$                | 301307-2 |            |  |

### P8xC591

### 4 BLOCK DIAGRAM

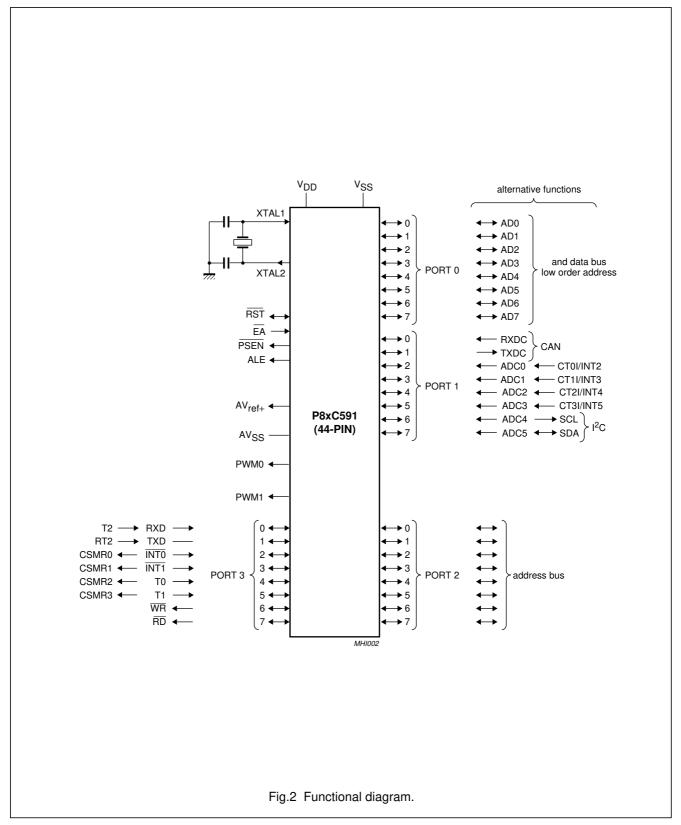

### 5 FUNCTIONAL DIAGRAM

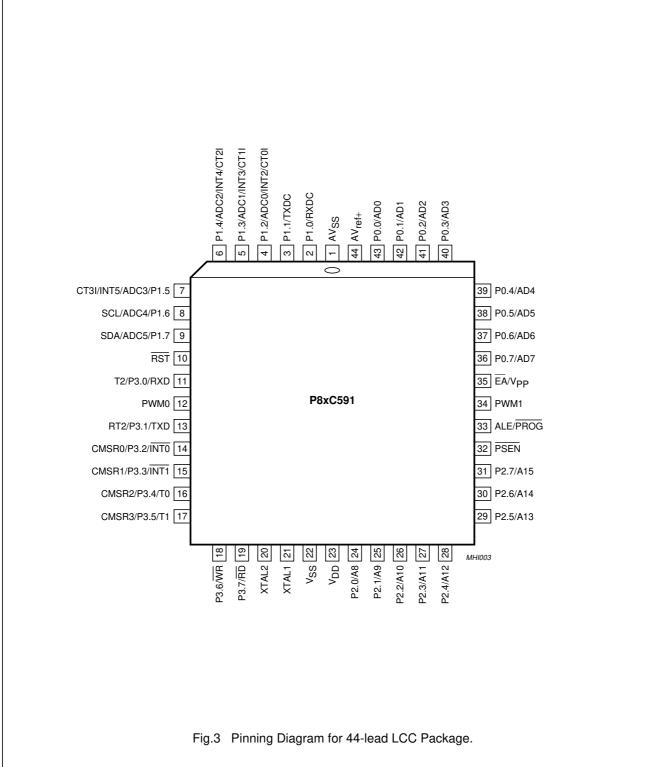

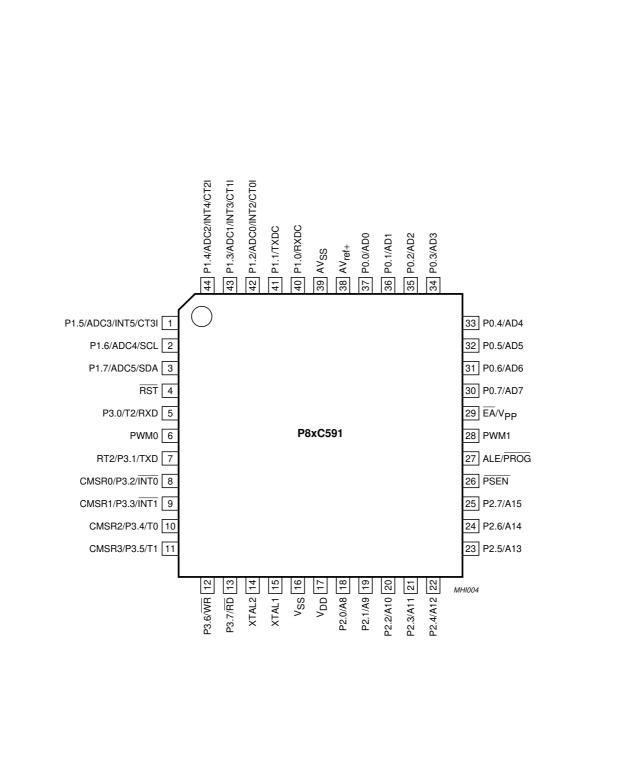

6 6.1

**PINNING INFORMATION**

**Pinning diagram**

Single-chip 8-bit microcontroller with CAN controller

Т

P8xC591

٦

### 6.2 Pin description

Г

|                     | Р     | IN     | DESCRIPTION                                                                                                                                                                                                     |  |  |  |  |  |  |

|---------------------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| SYMBOL              | QFP44 | PLCC44 | DESCRIPTION                                                                                                                                                                                                     |  |  |  |  |  |  |

| RST                 | 4     | 10     | <b>Reset:</b> A Input to reset the P8xC591. It also provides a reset pulse as output when Timer T3 overflows.                                                                                                   |  |  |  |  |  |  |

| P3.0to P3.7         |       |        | <b>Port 3 (P3.0 to P3.7)</b> : 8-bit programmable I/O port lines; Port 3 can sink/source 4 LSTTL inputs.                                                                                                        |  |  |  |  |  |  |

|                     |       |        | Port 3 pins serve alternate functions as follows:                                                                                                                                                               |  |  |  |  |  |  |

| P3.0/RXD            | 5     | 11     | <b>RXD</b> : Serial input port for UART;<br><b>T2:</b> T2 event input                                                                                                                                           |  |  |  |  |  |  |

| P3.1/TXD            | 7     | 13     | <b>TXD</b> : Serial output port for UART;<br><b>RT2:</b> T2 timer reset signal. Rising edge triggered.                                                                                                          |  |  |  |  |  |  |

| P3.2/INT0/CMSR0     | 8     | 14     | <b>INTO</b> : External interrupt input 0;<br><b>CMSR0:</b> Compare and Set/Reset output for Timer T2.                                                                                                           |  |  |  |  |  |  |

| P3.3/INT1/<br>CMSR1 | 9     | 15     | <b>INT1</b> : External interrupt input 1;<br><b>CMSR1:</b> Compare and Set/Reset output for Timer T2.                                                                                                           |  |  |  |  |  |  |

| P3.4/T0/CMSR2       | 10    | 16     | <b>T0</b> : Timer 0 external interrupt input;<br><b>CMSR2:</b> Compare and Set/Reset output for Timer T2.                                                                                                       |  |  |  |  |  |  |

| P3.5/T1/CMSR3       | 11    | 17     | <b>T1</b> : Timer 1 external interrupt input;<br><b>CMSR3:</b> Compare and Set/Reset output for Timer T2.                                                                                                       |  |  |  |  |  |  |

| P3.6/WR             | 12    | 18     | WR: External Data Memory Write strobe;                                                                                                                                                                          |  |  |  |  |  |  |

| P3.7/RD             | 13    | 19     | RD: External Data Memory Read strobe.                                                                                                                                                                           |  |  |  |  |  |  |

|                     |       |        | During reset, Port 3 will be asynchronously driven resistive HIGH.                                                                                                                                              |  |  |  |  |  |  |

|                     |       |        | Port 3 has four modes selected on a per bit basis by writing to the P3M1 and P3M2 registers as follows:                                                                                                         |  |  |  |  |  |  |

|                     |       |        | P3M1.x P3M2.x Mode Description                                                                                                                                                                                  |  |  |  |  |  |  |

|                     |       |        | 0 0 Pseudo-bidirectional (standard c51 configuration default)<br>0 1 Push-Pull                                                                                                                                  |  |  |  |  |  |  |

|                     |       |        | 1 0 High impedance<br>1 1 Open drain                                                                                                                                                                            |  |  |  |  |  |  |

| XTAL2               | 14    | 20     | <b>Crystal pin 2:</b> output of the inverting amplifier that forms the oscillator. Left open-circuit when an external oscillator clock is used.                                                                 |  |  |  |  |  |  |

| XTAL1               | 15    | 21     | <b>Crystal pin 1:</b> input to the inverting amplifier that forms the oscillator, and input to the internal clock generator. Receives the external oscillator clock signal when an external oscillator is used. |  |  |  |  |  |  |

| V <sub>SS</sub>     | 16    | 22     | Ground; circuit ground potential.                                                                                                                                                                               |  |  |  |  |  |  |

| V <sub>DD</sub>     | 17    | 23     | <b>Power supply;</b> power supply pin during normal operation and power reduction modes.                                                                                                                        |  |  |  |  |  |  |

Table 1

Pin description for QFP44/PLCC44, see Note 1.

|                           | <b>QFP44</b><br>18 to 25 | PLCC44   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------|--------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | 18 to 25                 |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                           | 10 10 20                 | 24 to 31 | Port 2 (P2.0 to P2.7): 8-bit programmable I/O port lines;<br>A08 to A15: High-order address byte for external memory.                                                                                                                                                                                                                                                                                                                                                                                                    |

|                           |                          |          | Alternate function: High-order address byte for external memory (A08-A15).<br>Port 2 is also used to input the upper order address during EPROM<br>programming and verification. A8 is on P2.0, A9 on P2.1, through A12 on<br>P2.4.                                                                                                                                                                                                                                                                                      |

|                           |                          |          | During reset, Port 2 will be asynchronously driven HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                           |                          |          | Port 2 has four output modes selected on a per bit basis by writing to the P2M1 and P2M2 registers as follows:                                                                                                                                                                                                                                                                                                                                                                                                           |

|                           |                          |          | P2M1.x P2M2.x Mode Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                           |                          |          | 0 0 Pseudo-bidirectional (standard c51 configuration default)<br>0 1 Push-Pull                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                           |                          |          | 1 0 High impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                           |                          |          | 1 1 Open drain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PSEN                      | 26                       | 32       | <b>Program Store Enable</b> output: read strobe to the external Program Memory via Ports 0 and 2. Is activated twice each machine cycle during fetches from external Program Memory. When executing out of external Program Memory two activations of PSEN are skipped during each access to external Data Memory. PSEN is not activated (remains HIGH) during no fetches from external Program Memory. PSEN can sink/source 8 LSTTL inputs. It can drive CMOS inputs without external pull-ups.                         |

| ALE/PROG :                | 27                       | 33       | Address Latch Enable output. Latches the low byte of the address during access of external memory in normal operation. It is activated every six oscillator periods except during an external Data Memory access. ALE can sink/source 8 LSTTL inputs. It can drive CMOS inputs without an external pull-up. To prohibit the toggling of ALE pin (RFI noise reduction) the bit A0 (SFR: AUXR.0) must be set by software; see Table 4.<br><b>PROG</b> : the programming pulse input; alternative function for the P87C591. |

| EA/V <sub>PP</sub> :      | 29                       | 35       | <b>External Access</b> input. If, during reset, $\overline{EA}$ is held at a TTL level HIGH the CPU executes out of the internal Program Memory. If, during reset, $\overline{EA}$ is held at a TTL level LOW the CPU executes out of external Program Memory via Port 0 and Port 2. $\overline{EA}$ is not allowed to float. $\overline{EA}$ is latched during reset and don't care after reset.<br><b>V</b> <sub>PP</sub> : the programming supply voltage; alternative function for the P87C591.                      |

| P0.0/AD0 to 5<br>P0.7/AD7 | 30 to 37                 | 36 to 43 | <b>Port 0</b> : 8-bit open-drain bidirectional I/O port.<br>During reset, Port 0 is HIGH-Impedance (Tri-State).                                                                                                                                                                                                                                                                                                                                                                                                          |

|                           |                          |          | <b>AD7 to AD0</b> : Multiplexed Low-order address and Data bus for external memory. During these accesses internal pull-ups are activated. Port 0 can sink/source up to 8 LSTTL inputs.                                                                                                                                                                                                                                                                                                                                  |

| AV <sub>ref+</sub> :      | 38                       | 44       | Analog to Digital Conversion Reference Resistor: High-end.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| AV <sub>SS</sub> :        | 39                       | 1        | Analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

P8xC591

| SYMDOL                       | PIN                |                  | DESCRIPTION                                                                                                                                                                                                   |  |  |  |  |  |

|------------------------------|--------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SYMBOL                       | QFP44              | PLCC44           | DESCRIPTION                                                                                                                                                                                                   |  |  |  |  |  |

| P1.0 to P1.4<br>P1.5 to P1.7 | 40 to 44<br>1 to 3 | 2 to 6<br>7 to 9 | <b>Port 1:</b> 8-bit I/O port with a user configurable output type. The operation of Port 1 pins as inputs or outputs depends upon the port configuration selected Each port pin is configured independently. |  |  |  |  |  |

|                              |                    |                  | Port 1 also provides various special functions as described below:                                                                                                                                            |  |  |  |  |  |

| P1.0                         | 40                 | 2                | RXDC: CAN Receiver input line.                                                                                                                                                                                |  |  |  |  |  |

| P1.1                         | 41                 | 3                | <b>TXDC:</b> CAN Transmit output line.<br>During reset, Port P1.0 and P1.1 will be asynchronously driven resistive HIGH, P1.2 to P1.7 is High-Impedance (Tri-state).                                          |  |  |  |  |  |

| P1.2 to P1.4                 | 42 to 44           | 4 to 6           | CT0I/INT2 / CT1I/INT3 / CT2I/INT4: T2 Capture timer inputs or External Interrupt inputs.                                                                                                                      |  |  |  |  |  |

|                              |                    |                  | ADC0 to ADC2: Alternate function: Input channels to ADC.                                                                                                                                                      |  |  |  |  |  |

| P1.5 to P1.7                 | 1 to 3             | 7 to 9           | ADC3 to ADC5: Input channels to ADC:                                                                                                                                                                          |  |  |  |  |  |

| P1.5                         | 1                  | 7                | CT3I/INT5: T2 Capture timer input or External Interrupt inputs.                                                                                                                                               |  |  |  |  |  |

| P1.6                         | 2                  | 8                | <b>SCL:</b> Serial port clock line I <sup>2</sup> C. Push-pull or pseudo bidrectional modes is not implemented at I <sup>2</sup> C.                                                                           |  |  |  |  |  |

| P1.7                         | 3                  | 9                | <b>SDA:</b> Serial data clock line I <sup>2</sup> C.Push-pull or pseudo bidrectional modes is not implemented at I <sup>2</sup> C.                                                                            |  |  |  |  |  |

|                              |                    |                  | Port 1 has four modes selected on a per bit basis by writing to the P1M1 and P1M2 registers as follows:                                                                                                       |  |  |  |  |  |

|                              |                    |                  | P1M1.x P1M2.x Mode Description                                                                                                                                                                                |  |  |  |  |  |

|                              |                    |                  | 0 0 Pseudo-bidirectional (standard c51 configuration default<br>0 1 <sup>(2)</sup> )                                                                                                                          |  |  |  |  |  |

|                              |                    |                  | 1 0 Push-Pull <sup>(2)</sup>                                                                                                                                                                                  |  |  |  |  |  |

|                              |                    |                  | 1 1 High impedance Open drain                                                                                                                                                                                 |  |  |  |  |  |

|                              |                    |                  | Port 1 is also used to input the lower order address byte during EPROM programming and verification. A0 is on P1.0, etc.                                                                                      |  |  |  |  |  |

| PWM0                         | 6                  | 12               | Pulse Width Modulation: Output 0.                                                                                                                                                                             |  |  |  |  |  |

| PWM1                         | 28                 | 34               | Pulse Width Modulation: Output 1.                                                                                                                                                                             |  |  |  |  |  |

#### Notes

1. To avoid "latch-up" effect as power-on, the voltage on any pin at any time must not be higher or lower than  $V_{DD}$  +0.5 V or  $V_{SS}$  –0.5 V.

2. Not implemented for P1.6 and P1.7.

### P8xC591

### 7 MEMORY ORGANIZATION

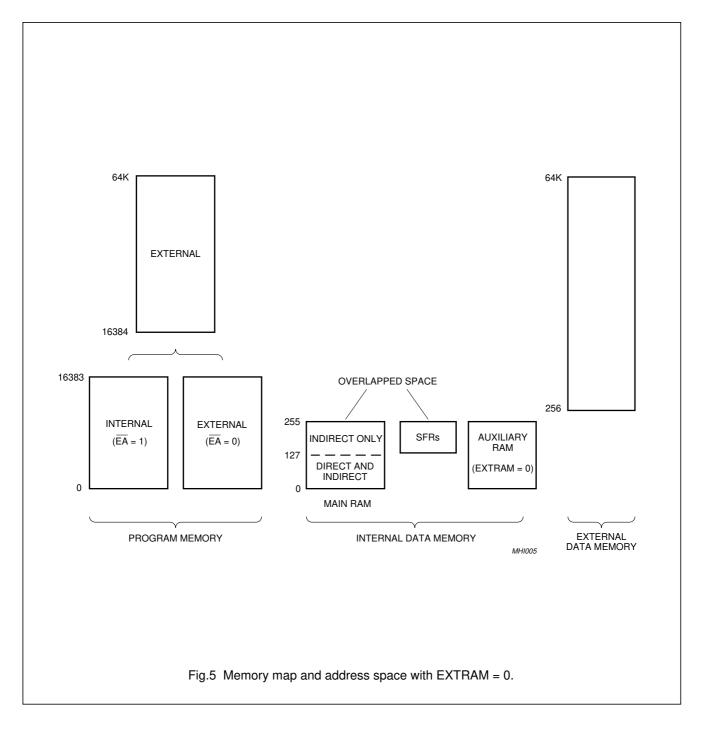

The Central Processing Unit (CPU) manipulates operands in three memory spaces as follows (see Fig.5):

- 16 Kbytes internal resp. 64 Kbytes external Program Memory

- 512 bytes internal Data Memory Main-and Auxiliary RAM

- up to 64 Kbytes external Data Memory (with 256 bytes residing in the internal Auxiliary RAM).

### P8xC591

#### 7.1 Program Memory

The P8xC591 contains 16 Kbytes of on-chip Program Memory which can be extended to 64 Kbytes with external memories. When  $\overline{\text{EA}}$  pin is held HIGH, the P8xC591 fetches instructions from internal ROM unless the address exceeds 3FFFh. Locations 4000h to FFFFh are fetched from external Program Memory. When the  $\overline{\text{EA}}$  pin is held LOW, all instruction fetches are from external memory. The  $\overline{\text{EA}}$  pin is latched during reset and is "don't care" after reset.

Both, for the ROM and EPROM version of the P8xC591, precautions are implemented to protect the device against illegal Program Memory code reading.

#### 7.2 Addressing

The P8xC591 has five methods for addressing the Program and Data memory:

- Register

- Direct

- Register-Indirect

- Immediate

- Base-Register plus Index-Register-Indirect.

For more details about Addressing modes please refer to Section 22.1 "Addressing Modes".

#### 7.3 Expanded Data RAM addressing

The P8xC591 has internal data memory that is mapped into four separate segments: the lower 128 bytes of RAM, upper 128 bytes of RAM, 128 bytes Special Function Register (SFR), and 256 bytes Auxiliary RAM (AUX-RAM) as shown in Figure 5.

The four segments are:

- 1. The Lower 128 bytes of RAM (addresses 00H to 7FH) are directly and indirectly addressable (see Fig.6).

- 2. The Upper 128 bytes of RAM (addresses 80H to FFH) are indirectly addressable.

- 3. The Special Function Registers, SFRs, (addresses 80H to FFH) are directly addressable only. All these SFRs are described in Table 4.

- 4. The 256-bytes AUX-RAM (00H FFH) are indirectly accessed by move external instruction, MOVX, and within the EXTRAM bit cleared, see Table 3.

The Lower 128 bytes can be accessed by either direct or indirect addressing. The Upper 128 bytes can be accessed by indirect addressing only. The Upper 128 bytes occupy the same address space as the SFR. That

means they have the same address, but are physically separate from SFR space.

When an instruction accesses an internal location above address 7FH, the CPU knows whether the access is to the upper 128 bytes of data RAM or to SFR space by the addressing mode used in the instruction. Instructions that use direct addressing access SFR space.

For example:

MOV 0A0H,#data

accesses the SFR at location 0A0H (which is P2). Instructions that use indirect addressing access the Upper 128 bytes of data RAM.

For example: MOV @ R0,#data

where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H).

The AUX-RAM can be accessed by indirect addressing, with EXTRAM bit cleared and MOVX instructions. This part of memory is physically located on-chip, logically occupies the first 256-bytes of external data memory.

With EXTRAM = 0, the AUX-RAM is indirectly addressed, using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. An access to AUX-RAM will not affect ports P0, P3.6 (WR#) and P3.7 (RD#). P2 SFR is output during external addressing. For example, with EXTRAM = 0,

MOV @ R0,#data

where R0 contains 0A0h, access the AUX-RAM at address 0A0H rather than external memory. An access to external data memory locations higher than FFH (i.e., 0100H to FFFFH) will be performed with the MOVX DPTR instructions in the same way as in the standard 80C51, so with P0 and P2 as data/address bus, and P3.6 and P3.7 as write and read timing signals. Refer to Table 4.

With EXTRAM = 1, MOVX @ Ri and MOVX @ DPTR will be similar to the standard 80C51. MOVX @ Ri will provide an 8-bit address multiplexed with data on Port 0 and any output port pins can be used to output higher order address bits. This is to provide the external paging capability. MOVX @ DPTR will generate a 16-bit address. Port 2 outputs the high-order eight address bits (the contents of DPH) while Port 0 multiplexes the low-order eight address bits (DPL) with data. MOVX @ Ri and MOVX @ DPTR will generate either read or write signals on P3.6 (#WR) and P3.7 (#RD).

The stack pointer (SP) may be located anywhere in the 256 bytes RAM (lower and upper RAM) internal data memory. The stack cannot be located in the AUX-RAM.

### P8xC591

| Table 2         AUX-RAM Page Register (address 8EH) |  |  |  |  |  |  |

|-----------------------------------------------------|--|--|--|--|--|--|

|                                                     |  |  |  |  |  |  |

| 7 | 6 | 5 | 4 | 3 | 2     | 1      | 0  |

|---|---|---|---|---|-------|--------|----|

| - | - | - | - | - | LVADC | EXTRAM | AO |

### Table 3Description of AUX-RAM bits

| BIT    | SYMBOL |                | FUNCTION                                                             |  |  |  |  |  |  |  |

|--------|--------|----------------|----------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7 to 3 | _      | Reserved for   | leserved for future use; see Note 1.                                 |  |  |  |  |  |  |  |

| 2      | LVADC  | Enable A/D lo  | nable A/D low voltage operation.                                     |  |  |  |  |  |  |  |

|        |        | LVADC          | LVADC Operating Mode                                                 |  |  |  |  |  |  |  |

|        |        | 0              | Turns off A/D charge pump.                                           |  |  |  |  |  |  |  |

|        |        | 1              | Turns on A/D charge pump. Required for operation below 4 V.          |  |  |  |  |  |  |  |

| 1      | EXTRAM | Internal/Exter | Internal/External RAM (00H - FFH) access using MOVX @ RI / @ DPTR    |  |  |  |  |  |  |  |

|        |        | EXTRAM         | Operating Mode                                                       |  |  |  |  |  |  |  |

|        |        | 0              | Internal AUX-RAM (00H - FH) access using MOVX @ RI / @ DPTR.         |  |  |  |  |  |  |  |

|        |        | 1              | External data memory access.                                         |  |  |  |  |  |  |  |

| 0      | AO     | Disable/Enab   | le ALE.                                                              |  |  |  |  |  |  |  |

|        |        | AO             | Operating Mode                                                       |  |  |  |  |  |  |  |

|        |        | 0              | ALE is permitted at a constant rate of 1/6 the oscillator frequency. |  |  |  |  |  |  |  |

|        |        | 1              | ALE is active only during a MOVX or MOVC instruction.                |  |  |  |  |  |  |  |

### Notes

- 1. User software should not write '1's to reserved bits. These bits may be used in future 80C51 family products to invoke new features. In that case, the reset or inactive of the new bit will be 0, and its active value will be '1'. The value read from a reserved bit is indeterminate.

- 2. Reset value is 'xxxxx10B'.

# P8xC591

| 7Fh        | (MS      | B)       |          |          |          |          | (]       | .SB)     | 127      |

|------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

|            |          | -,       |          |          |          |          | (-       | ,        |          |

|            | Ť        |          |          |          |          |          |          | ŝ        | 5        |

|            |          |          |          |          |          |          |          |          |          |

| 2Fh        | 7F       | 7E       | 7D       | 7C       | 7B       | 7A       | 79       | 78       | 47       |

| 2Eh        | 77       | 76       | 75       | 74       | 73       | 72       | 71       | 70       | 46       |

| 2Dh<br>2Ch | 6F<br>67 | 6E<br>66 | 6D<br>65 | 6C<br>64 | 6B<br>63 | 6A<br>62 | 69<br>61 | 68<br>60 | 45<br>44 |

| 2Bh        | 5F       | 5E       | 5D       | 5C       | 5B       | 5A       | 59       | 58       | 43       |

| 2Ah        | 57       | 56       | 55       | 54       | 53       | 52       | 51       | 50       | 42       |

| 29h        | 4F       | 4E       | 4D       | 4C       | 4B       | 4A       | 49       | 48       | 41       |

| 28h<br>27h | 47<br>3F | 46<br>3E | 45<br>3D | 44<br>3C | 43<br>3B | 42<br>3A | 41<br>39 | 40<br>38 | 40<br>39 |

| 26h        | 37       | 36       | 35       | 34       | 33       | 32       | 31       | 30       | 38       |

| 25h        | 2F       | 2E       | 2D       | 2C       | 2B       | 2A       | 29       | 28       | 37       |

| 24h        | 27       | 26       | 25       | 24       | 23       | 22       | 21       | 20       | 36       |

| 23h<br>22h | 1F<br>17 | 1E<br>16 | 1D<br>15 | 1C<br>14 | 1B<br>13 | 1A<br>12 | 19<br>11 | 18<br>10 | 35<br>34 |

| 21h        | 0F       | 0E       | 0D       | 0C       | 0B       | 0A       | 09       | 08       | 33       |

| 20h        | 07       | 06       | 05       | 04       | 03       | 02       | 01       | 00       | 32       |

| 1Fh        |          |          | REG      | ISTE     | R BA     | NK 3     |          |          | 31       |

| 18h        |          |          |          |          |          |          |          |          | 24       |

| 17h<br>10h |          |          | REG      | ISTE     | R BA     | NK 2     |          |          | 23<br>16 |

| 0Fh        | <u> </u> |          |          |          |          |          |          |          | 15       |

| 08h        |          |          | REG      | ISTE     | R BA     | NK 1     |          |          | 8        |

| 07h        |          |          | BEG      | ISTE     | R RA     | NK 0     |          |          | 7        |

| 00h        |          |          |          |          |          |          |          |          | 0        |

|            |          |          |          |          |          |          | Λ        | лніоо6   |          |

|            |          |          |          |          |          |          |          |          |          |

|            |          |          |          |          |          |          |          |          |          |

|            |          |          |          |          |          |          |          |          |          |

|            |          |          |          |          |          |          |          |          |          |

|            |          |          |          |          |          |          |          |          |          |

|            |          |          |          |          |          |          |          |          |          |

|            |          |          |          |          |          |          |          |          |          |

Fig.6 Internal Main RAM bit addresses.

P8xC591

### 7.3.1 SPECIAL FUNCTION REGISTERS

| Table 4  | Special Function Register Bit Address, Symbol or Alternate Port Function    |

|----------|-----------------------------------------------------------------------------|

| * = SFRs | are bit addressable; # = SFRs are modified from or added to the 80C51 SFRs. |

| NAME    | DESCRIPTION                                | SFR<br>ADDR | BIT FUNCTIONS AND ADDRESSES |       |       |       |       |       |        |       | RESET<br>VALUE |

|---------|--------------------------------------------|-------------|-----------------------------|-------|-------|-------|-------|-------|--------|-------|----------------|

|         |                                            | ADDR        | MSB                         |       |       |       |       |       |        | LSB   | VALUE          |

| ACC*    | Accumulator                                | E0H         | E7                          | E6    | E5    | E4    | E3    | E2    | E1     | E0    | 00H            |

| ADCH#   | A/D converter high                         | C6H         |                             |       |       |       |       |       | •      |       | xxxxxxxb       |

| ADCON#  | A/D control                                | C5H         | ADC.1                       | ADC.0 | -     | ADCI  | ADCS  | AADR2 | AADR1  | AADR0 | xx000000b      |

| AUXR    | Auxiliary                                  | 8EH         | -                           | -     | -     | -     | -     | LVADC | EXTRAM | A0    | xxxxx110B      |

| AUXR1   | Auxiliary                                  | A2H         | ADC8                        | AIDL  | SRST  | WDE   | WUPD  | 0     | -      | DPS   | 000000x0B      |

| B*      | B register                                 | F0H         | F7                          | F6    | F5    | F4    | F3    | F2    | F1     | F0    | 00H            |

| CTCON#  | Capture control                            | EBH         | CTN3                        | CTP3  | CTN2  | CTP2  | CTN1  | CTP1  | CTN0   | CTP0  | 00H            |

| CTH3#   | Capture high 3                             | CFH         |                             |       |       |       |       |       |        |       | xxxxxxxB       |

| CTH2#   | Capture high 2                             | CEH         |                             |       |       |       |       |       |        |       | xxxxxxxB       |

| CTH1#   | Capture high 1                             | CDH         |                             |       |       |       |       |       |        |       | xxxxxxxB       |

| CTH0#   | Capture high 0                             | ССН         |                             |       |       |       |       |       |        |       | xxxxxxxB       |

| CMH2#   | Compare high 2                             | СВН         |                             |       |       |       |       |       |        |       | 00H            |

| CMH1#   | Compare high 1                             | CAH         |                             |       |       |       |       |       |        |       | 00H            |

| CMH0#   | Compare high 0                             | С9Н         |                             |       |       |       |       |       |        |       | 00H            |

| CTL3#   | Capture low 3                              | AFH         |                             |       |       |       |       |       |        |       | xxxxxxxB       |

| CTL2#   | Capture low 2                              | AEH         |                             |       |       |       |       |       |        |       | xxxxxxxB       |

| CTL1#   | Capture low 1                              | ADh         |                             |       |       |       |       |       |        |       | xxxxxxxB       |

| CTL0#   | Capture low 0                              | ACH         |                             |       |       |       |       |       |        |       | xxxxxxxB       |

| CML2#   | Compare low 2                              | ABH         |                             |       |       |       |       |       |        |       | 00H            |

| CML1#   | Compare low 1                              | ААН         |                             |       |       |       |       |       |        |       | 00H            |

| CML0#   | Compare low 0                              | A9H         |                             |       |       |       |       |       |        |       | 00H            |

| DPTR:   | Data Pointer (2 bytes):                    |             |                             |       |       |       |       |       |        |       |                |

| DPH     | Data Pointer High                          | 83h         |                             |       |       |       |       |       |        |       | 00H            |

| DPL     | Data Pointer Low                           | 82h         |                             |       |       |       |       |       |        |       | 00H            |

|         |                                            |             | AF                          | AE    | AD    | AC    | AB    | AA    | A9     | A8    |                |

| IENO*#  | Interrupt Enable 0                         | A8H         | EA                          | EAD   | ES1   | ES0   | ET1   | EX1   | ET0    | EX0   | оон            |

|         |                                            |             | EF                          | EE    | ED    | EC    | EB    | EA    | E9     | E8    |                |

| IEN1*#  | Interrupt Enable 1                         | E8H         | ET2                         | ECAN  | ECM1  | ECM0  | ECT3  | ECT2  | ECT1   | ECT0  | оон            |

|         |                                            |             | BF                          | BE    | BD    | BC    | BB    | BA    | B9     | B8    |                |

| IP0*#   | Interrupt Priority 0                       | B8H         | -                           | PAD   | PS1   | PS0   | PT1   | PX1   | PT0    | PX0   | x0000000B      |

|         |                                            | -           | FF                          | FE    | FD    | FC    | FB    | FA    | F9     | F8    |                |

| IP0H    | Interrupt Priority 0 high                  | B7H         | -                           | PADH  | PS1H  | PS0H  | PT1H  | PX1H  | PT0H   | PX0H  | x0000000B      |

| IP1*#   | Interrupt Priority 1                       | F8h         | PT2                         | PCAN  | PCM1  | PCM0  | РСТ3  | PCT2  | PCT1   | PCT0  | 00H            |

| IP1H    | Interrupt Priority 1 high                  | F7H         | PT2H                        | PCANH | PCM1H | PCM0H | РСТЗН | PCT2H | PCT1H  | РСТОН | 00H            |

| CANMOD  | CAN Mode Register                          | C4H         |                             |       |       |       |       |       |        |       | 00H            |

| CANCON  | CAN Command (w) and<br>Interrupt (r)       | СЗН         |                             |       |       |       |       |       |        |       | 00H            |

| CANDAT  | CAN Data                                   | C2H         |                             |       |       |       |       |       |        |       | 00H            |

| CANADR  | CAN Address                                | C1H         |                             |       |       |       |       |       |        |       | 00H            |

|         |                                            |             | C7                          | C6    | C5    | C4    | C3    | C2    | C1     | C0    |                |

| CANSTA* | CAN Status (r)                             | СОН         | BS                          | ES    | TS    | RS    | TCS   | TBS   | DOS    | RBS   | 00Н            |

|         | CAN Status (I)<br>CAN Interrupt Enable (w) |             | BEIE                        | ALIE  | EPIE  | WUIE  | DOIE  | EIE   | TIE    | RIE   |                |

|         |                                            |             | DEIE                        | ALIE  | EFIE  | WUIE  |       | EIE   |        |       |                |

| NAME    | DESCRIPTION            | SFR<br>ADDR | MSB    |       | BIT FUN | CTIONS | AND ADE | RESSES      |               | LSB    | RESET<br>VALUE |

|---------|------------------------|-------------|--------|-------|---------|--------|---------|-------------|---------------|--------|----------------|

| P1M1    | Port 1 output mode 1   | 92H         |        |       |         |        |         |             |               |        | FCH            |

| P1M2    | Port 1 output mode 2   | 93H         |        |       |         |        |         |             |               |        | 00H            |

| P2M1    | Port 2 output mode 1   | 94H         |        |       |         |        |         |             |               |        | 00H            |

| P2M2    | Port 2 output mode 2   | 95H         |        |       |         |        |         |             |               |        | 00H            |

| P3M1    | Port 3 output mode 1   | 9AH         |        |       |         |        |         |             |               |        | 00H            |

| P3M2    | Port 3 output mode 2   | 9BH         |        |       |         |        |         |             |               |        | 00H            |

| 1 OWL   |                        | 5511        | B7     | B6    | B5      | B4     | B3      | B2          | B1            | B0     |                |

|         |                        |             | -      |       | CSMR3   | CSMR2  | CSMR1   | CSMR0       | RT2           | T2     | 1              |

| P3*     | Port 3                 | B0H         | RD     | WR    | T1      | ТО     | INT1    | INTO        | TXD           | RXD    | FFH            |

|         |                        |             | A7     | A6    | A5      | A4     | A3      | A2          | A1            | A0     | 1              |

| P2*     | Port 2                 | A0H         | A15    | A14   | A13     | A12    | A11     | A10         | A9            | A8     | FFH            |

|         |                        |             | 97     | 96    | 95      | 94     | 93      | 92          | 91            | 90     | 1              |

|         |                        |             | ADC5   | ADC4  | ADC3    | ADC2   | ADC1    | ADC0        | -             | _      | 1              |

| P1*     | Port 1                 | 90H         | SDA    | SCL   | CT3I    | CT2I   | CT1I    | CTOI        | TXDC          | RXDC   | -<br>FFH       |

|         |                        | 0011        | 87     | 86    | 85      | 84     | 83      | 82          | 81            | 80     | 1              |

| P0*     | Port 0                 | 80H         | AD7    | AD6   | AD5     | AD4    | AD3     | AD2         | AD1           | AD0    | FFH            |

| PCON    | Power Control          | 87H         | SMOD1  | SMOD0 | POF     | WLE    | GF1     | GF0         | PD            | IDL    | 00x00000B      |

| PSW     | Program Status Word    | D0H         | CY     | AC    | F0      | RS1    | RS0     | OV          | F1            | P      | 00H            |

| PWMP#   | PWM Prescaler          | FEH         |        | ////  | 10      | 1101   | 1100    | 0.          |               | •      | оон            |

| PWMP1#  | PWM Register 1         | FDH         |        |       |         |        |         |             |               |        | 00H            |

| PWMP0#  | PWM Register 0         | FCH         |        |       |         |        |         |             |               |        | 00H            |

| RTE#    | Reset Enable           | EFH         |        |       |         |        | RP35    | RP34        | RP33          | RP32   | xxxx0000B      |

| SOADDR  | Serial 0 Slave Address | F9H         |        |       |         |        | 1       |             |               | 111 02 | 00H            |

| SOADEN  | Slave Address Mask     | B9H         |        |       |         |        |         |             |               |        | 00H            |

| SP      | Stack Pointer          | 81H         |        |       |         |        |         |             |               |        | 07H            |

| S0BUF   | Serial 0 Data Buffer   | 99H         |        |       |         |        |         |             |               |        | xxxxxxxB       |

| SOPSL   | Prescaler Value UART   | FAH         |        |       |         |        |         |             |               |        | 00H            |

| SOPSH   | Prescaler/Value UART   | FBH         | SPS    |       |         |        |         | Prescaler h | nigher nibble | 9      | 0xxx0000B      |

|         |                        |             | 9F     | 9E    | 9D      | 9C     | 9B      | 9A          | 99            | 98     | 1              |

| S0CON*  | Serial 0 Control       | 98H         | SM0/FE | SM1   | SM2     | REN    | TB8     | RB8         | TI            | RI     | оон            |

| S1CON#* | Serial 1Control        | D8H         | CR2    | ENS1  | STA     | ST0    | SI      | AA          | CR1           | CR0    | 00H            |

| S1ADR#  | Serial 1 Address       | DBH         |        |       |         |        | ESS     |             |               | GC     | 00H            |

| S1DAT#  | Serial 1 Data          | DAH         |        |       |         |        |         |             |               |        | 00Н            |

| S1STA#  | Serial 1 Status        | D9H         | SC4    | SC3   | SC2     | SC1    | SC0     | 0           | 0             | 0      | F8H            |

|         |                        |             | DF     | DE    | DD      | DC     | DB      | DA          | D9            | D8     | -              |

| STE#    | Set Enable             | EEH         |        |       |         |        | SP35    | SP34        | SP33          | SP32   | xxxx0000B      |

| TH1     | Timer High 1           | 8DH         |        | 1     | L       | 1      | 1       | 1           | 1             | 1      | 00Н            |

| TH0     | Timer High 0           | 8CH         |        |       |         |        |         |             |               |        | 00H            |

| TL1     | Timer Low 1            | 8BH         |        |       |         |        |         |             |               |        | 00H            |

| TL0     | Timer Low 0            | 8AH         |        |       |         |        |         |             |               |        | 00H            |

| TMH2#   | Timer High 2           | EDH         |        |       |         |        |         |             |               |        | 00H            |

| TML2#   | Timer Low 2            | ECH         |        |       |         |        |         |             |               |        | 00H            |

| NAME    | DESCRIPTION              | SFR<br>ADDR | MOD   | BIT FUNCTIONS AND ADDRESSES |      |      |      |      |       | 1.00  | RESET<br>VALUE |

|---------|--------------------------|-------------|-------|-----------------------------|------|------|------|------|-------|-------|----------------|

|         |                          |             | MSB   |                             |      | -    |      |      |       | LSB   |                |

| TMOD    | Timer Mode               | 89H         | GATE  | C/T                         | M1   | M0   | GATE | C/T  | M1    | M0    | 00H            |

|         |                          |             | 8F    | 8E                          | 8D   | 8C   | 8B   | 8A   | 89    | 88    |                |

| TCON*   | Timer Control            | 88H         | TF1   | TR1                         | TF0  | TR0  | IE1  | IT1  | IE0   | IT0   | 00H            |

| TM2CON# | Timer 2 Control          | EAH         | T2IS1 | T2IS0                       | T2ER | T2B0 | T2P1 | T2P0 | T2MS1 | T2MS0 | 00H            |

|         |                          |             | CF    | CE                          | CD   | CC   | СВ   | CA   | C9    | C8    |                |

| TM2IR#* | Timer 2/CAN Int Flag Reg | C8H         | T2OV  | CMI2/<br>CAN                | CMI1 | CMI0 | СТІЗ | CTI2 | CTI1  | CTI0  | 00H            |

| T3#     | Timer 3                  | FFH         |       |                             |      |      |      |      |       |       | 00H            |

### P8xC591

### 7.4 Dual DPTR

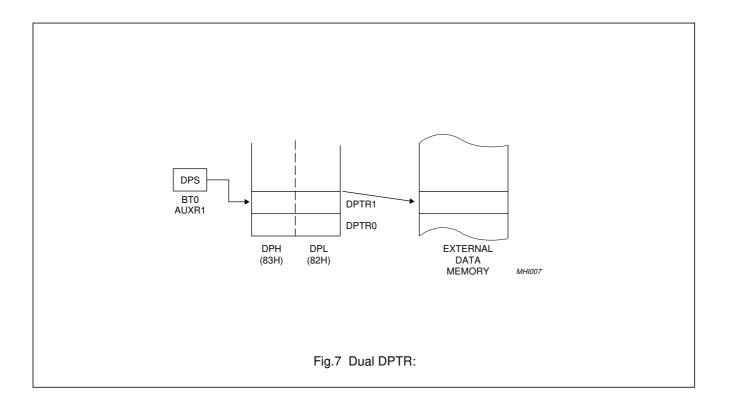

The dual DPTR structure (see Figure 7) is a way by which the chip will specify the address of an external data memory location. There are two 16-bit DPTR registers that address the external memory, and a single bit called DPS = AUXR1/bit0 that allows the program code to switch between them.

The DPS bit status should be saved by software when switching between DPTR0 and DPTR1.

Note that bit 2 is not writable and is always read as a zero. This allows the DPS bit to be quickly toggled simply by executing an INC AUXR1 instruction without affecting the other bits.

### **DPTR Instructions**

The instructions that refer to DPTR refer to the data pointer that is currently selected using the AUXR1/bit 0 register. The six instructions that use the DPTR are as follows:

| INC DPTRIncrements the      | e data pointer by 1                       |

|-----------------------------|-------------------------------------------|

| MCV DPTR, #data 16 constant | Loads the DPTR with a 16-bit              |

| MOV A, @ A+DPTR             | Move code byte relative to<br>DPTR to ACC |

| MOVX A, @ DPTR              | Move external RAM (16-bit address) to ACC |

| MOVX @ DPTR, A              | Move ACC to external RAM (16-bit address) |

| JMP @ A + DPTR              | Jump indirect relative to<br>DPTR         |

|                             |                                           |

The data pointer can be accessed on a byte-by-byte basis by specifying the low or high byte in an instruction which accesses the SFRs. See application note AN458 for more details.

### P8xC591

### 7.4.1 AUXR1 PAGE REGISTER

#### Table 5 AUXR1 Page Register (address A2H)

| 7    | 6    | 5    | 4   | 3    | 2 | 1 | 0   |

|------|------|------|-----|------|---|---|-----|

| ADC8 | AIDL | SRST | WDE | WUPD | 0 | — | DSP |

#### Table 6 Description of AUXR1 of bits

User software should not write 1s to reserved bits. Theses bits may be used in future 8051 family products to invoke new features. In that case, the reset or inactive value of the new bit will be logic 0, and its active value will be logic 1. The value read from a reserved bit is indeterminate. The reset value of AUXR1 is (00000xB).

| BIT | SYMBOL | DESCRIPTION                                                              |  |  |  |  |  |

|-----|--------|--------------------------------------------------------------------------|--|--|--|--|--|

| 7   | ADC8   | ADC Mode Switch. Switches between 10-bit conversion and 8-bit conversion |  |  |  |  |  |

|     |        | ADC8 Operating Mode                                                      |  |  |  |  |  |

|     |        | 0 10-bit conversion (50 machine cycles)                                  |  |  |  |  |  |

|     |        | 1 8-bit conversion (24 machine cycles)                                   |  |  |  |  |  |

| 6   | AIDL   | Enables the ADC during Idle mode.                                        |  |  |  |  |  |

| 5   | SRST   | Software Reset.                                                          |  |  |  |  |  |

| 4   | WDE    | Watchdog Timer Enable Flag.                                              |  |  |  |  |  |

| 3   | WUPD   | Enable Wake-up from Power-down.                                          |  |  |  |  |  |

| 2   | 0      | Reserved.                                                                |  |  |  |  |  |

| 1   | _      | Reserved.                                                                |  |  |  |  |  |

| 0   | DSP    | Data Pointer Switch. Switches between DPRT0 and DPTR1.                   |  |  |  |  |  |

|     |        | ADC8 Operating Mode                                                      |  |  |  |  |  |

|     |        | 0 DPTR0                                                                  |  |  |  |  |  |

|     |        | 1 DPTR1                                                                  |  |  |  |  |  |

P8xC591

### 8 I/O FACILITIES

The P8xC591 consists of 32 I/O Port lines with partly multiple functions. The I/O's are held HIGH during reset (asynchronous, before oscillator is running).

Ports 0, 1, 2 and 3 perform the following alternative functions:

- Port 0 is the same as in the 80C51. After reset the Port Special Function Register is set to 'FFh' as known from other 80C51 derivatives. Port 0 also provides the multiplexed low-order address and data bus used for expanding the P8xC591 with standard memories and peripherals.

- Port 1 supports several alternative functionalities. For this reason it has different I/O stages. Note, port P1.0 and P1.1 are Driven-High and P1.2 to P1.7 are High-Impedance (Tri-state) after reset.

- Port 2 is the same as in the 80C51. After reset the Port Special Function Register is set to 'FFh' as known from other 80C51 derivatives. Port 2 also provides the high-order address bus when the P8xC591 is expanded with external Program Memory and/or external Data Memory.

- Port 3 is the same as in the 80C51. During reset the Port 3 Special Function Register is set to 'FFh' as known from other 80C51 derivatives.

### 9 OSCILLATOR CHARACTERISTICS

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier. The pins can be configured for use as an on-chip oscillator, as shown in the logic symbol.

To drive the device from an external clock source, XTAL1 should be driven while XTAL2 is left unconnected. There are no requirements on the duty cycle of the external clock signal. However, minimum and maximum high and low times specified in the data sheet must be observed.

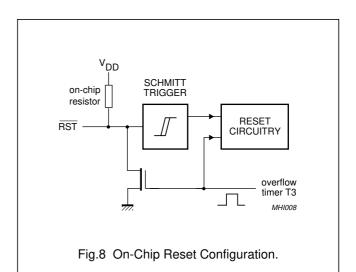

#### 10 RESET

A reset is accomplished by holding the  $\overrightarrow{\text{RST}}$  pin LOW for at least two machine cycles (12 oscillator periods), while the oscillator is running. To insure a good power-on reset, the  $\overrightarrow{\text{RST}}$  pin must be low long enough to allow the oscillator time to start up (normally a few milliseconds) plus two machine cycles.

The RST line can also be pulled LOW internally by a pull-down transistor activated by the watchdog timer T3. The length of the output pulse from T3 is 3 machine cycles.

A pulse of such short duration is necessary in order to recover from a processor or system fault as fast as possible.

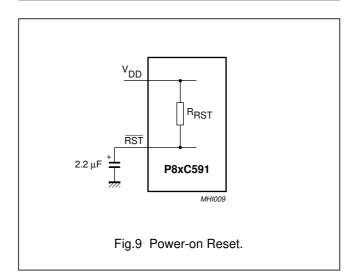

Note that the short reset pulse from Timer T3 cannot discharge the power-on reset capacitor (see Figure 8). Consequently, when the watchdog timer is also used to set external devices, this capacitor arrangement should not be connected to the  $\overline{\text{RST}}$  pin, and a different circuit should be used to perform the power-on reset operation. A timer T3 overflow, if enabled, will force a reset condition to the P8xC591 by an internal connection, whether the output  $\overline{\text{RST}}$  is pulled-up HIGH or not.

A reset may be performed in software by setting the software reset bit, SRST (AUXR1.5).

This device also has a Power-on Detect Reset circuit as  $V_{CC}$  transitions from  $V_{CC}$  past  $V_{\overline{RST}}.$

P8xC591

#### **11 LOW POWER MODES**

#### 11.1 Stop Clock Mode

The static design enables the clock speed to be reduced down to 0 MHz (stopped). When the oscillator is stopped, the RAM and Special Function Registers retain their values. This mode allows step-by-step utilization and permits reduced system power consumption by lowering the clock frequency down to any value. For lowest power consumption the Power-down mode is suggested.

#### 11.2 Idle Mode

In the Idle mode (see Table 7), the CPU puts itself to sleep while all of the on-chip peripherals stay active. The instruction to invoke the idle mode is the last instruction executed in the normal operating mode before the Idle mode is activated. The CPU contents, the on-chip RAM, and all of the special function registers remain intact during this mode. The Idle mode can be terminated either by any enabled interrupt (at which time the process is picked up at the interrupt service routine and continued), or by a hardware reset which starts the processor in the same manner as a Power-on reset.

#### 11.3 Power-down Mode

To save even more power, a Power-down mode (see Table 7) can be invoked by software. In this mode, the oscillator is stopped and the instruction that invoked Power Down is the last instruction executed. The on-chip RAM and Special Function Registers retain their values down to 2.0 V and care must be taken to return  $V_{CC}$  to the minimum specified operating voltages before the Power-down Mode is terminated.

A hardware reset or external interrupt can be used to exit from Power-down. The Wake-up from Power-down bit, WUPD (AUXR1.3) must be set in order for an interrupt to cause a Wake-up from Power-down. Reset redefines all the SFRs but does not change the on-chip RAM. A Wake-up allows both the SFRs and the on-chip RAM to retain their values.

To properly terminate Power-down the reset or external interrupt should not be executed before  $V_{CC}$  is restored to its normal operating level and must be held active long enough for the oscillator to restart and stabilize (normally less than 10 ms).

| MODE       | MEMORY   | ALE | PSEN | PORT 0    | PORT 1    | PORT 2    | PORT 3    | PWM0/<br>PWM1 |

|------------|----------|-----|------|-----------|-----------|-----------|-----------|---------------|

| Idle       | internal | 1   | 1    | port data | port data | port data | port data | high          |

|            | external | 1   | 1    | float     | port data | address   | port data | high          |

| Power-down | internal | 0   | 0    | port data | port data | port data | port data | high          |

|            | external | 0   | 0    | float     | port data | port data | port data | high          |

**Table 7** Status of external pins during Idle and Power-down modes

With an external interrupt, INT0 and INT1 must be enabled and configured as level-sensitive. Holding the pin low restarts the oscillator but bringing the pin back high completes the exit. Once the interrupt is serviced, the next instruction to be executed after RETI will be the one following the instruction that put the device into Power-down.

### P8xC591

### 11.3.1 POWER OFF FLAG

The Power Off Flag (POF) is set by on-chip circuitry when the V<sub>CC</sub> level on the P8xC591 rises from 0 to 5 V. The POF bit can be set or cleared by software allowing a user to determine if the reset is the result of a power-on or warm after Power-down. The V<sub>CC</sub> level must remain above 3 V for the POF to remain unaffected by the V<sub>CC</sub> level.

### 11.3.2 DESIGN CONSIDERATION

• When the Idle mode is terminated by a hardware reset, the device normally resumes program execution, from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write when Idle is terminated by reset, the instruction following the one that invokes Idle should not be one that writes to a port pin or to external memory.

### 11.3.3 ONCE<sup>TM</sup> MODE

The  $ONCE^{TM}$  ("On-Circuit Emulation") Mode facilities testing and debugging of systems without the device having to be removed from the circuit. The ONCE Mode is invoked by:

- 1. Pull ALE low while the device is in reset an PSEN is high,

- 2. Hold ALE low as  $\overline{RST}$  is deactivated.

While the device is in ONCE Mode, the Port 0 pins go into a float state, and the other port pins and ALE and  $\overrightarrow{\text{PSEN}}$  are weakly pulled high. The oscillator circuit remains active. While the device is in this mode, an emulator or test CPU can be used to drive the circuit. Normal operation is restored when a normal reset is applied.

### 11.3.4 REDUCED EMI MODE

The ALE-Off bit, AO (AUXR.0) can be set to 0 disable the ALE output. It will automatically become active when required for external memory accesses and resume to the OFF state after completing the external memory access.

### 11.3.5 POWER CONTROL REGISTER (PCON)

Table 8

Power Control Register (address 87H)

| 7     | 6     | 5   | 4   | 3   | 2   | 1  | 0   |

|-------|-------|-----|-----|-----|-----|----|-----|

| SMOD1 | SMOD0 | POF | WLE | GF1 | GF0 | PD | IDL |

### Table 9 Description of PCON bits

If logic 1s are written to PD and IDL at the same time, PD takes precedence. The reset value of PCON is (0XX00000).