# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### INTEGRATED CIRCUITS

Product data Replaces P89C660/P89C662/P89C664 of 2001 Jul 19 and P89C668 of 2001 Jul 27

2002 Oct 28

Philips Semiconductors

### P89C660/P89C662/P89C664/ P89C668

#### DESCRIPTION

The P89C660/662/664/668 device contains a non-volatile 16KB/32KB/64KB Flash program memory that is both parallel programmable and serial In-System and In-Application Programmable. In-System Programming (ISP) allows the user to download new code while the microcontroller sits in the application. In-Application Programming (IAP) means that the microcontroller fetches new program code and reprograms itself while in the system. This allows for remote programming over a modem link. A default serial loader (boot loader) program in ROM allows serial In-System Programming of the Flash memory via the UART without the need for a loader in the Flash code. For In-Application Programming, the user program erases and reprograms the Flash memory by use of standard routines contained in ROM.

This device executes one instruction in 6 clock cycles, hence providing twice the speed of a conventional 80C51. An OTP configuration bit gives the user the option to select conventional 12-clock timing.

This device is a Single-Chip 8-Bit Microcontroller manufactured in advanced CMOS process and is a derivative of the 80C51 microcontroller family. The instruction set is 100% executing and timing compatible with the 80C51 instruction set.

The device also has four 8-bit I/O ports, three 16-bit timer/event counters, a multi-source, four-priority-level, nested interrupt structure, an enhanced UART and on-chip oscillator and timing circuits.

The added features of the P89C660/662/664/668 makes it a powerful microcontroller for applications that require pulse width modulation, high-speed I/O and up/down counting capabilities such as motor control.

#### FEATURES

- 80C51 Central Processing Unit

- On-chip Flash program memory with In-System Programming (ISP) and In-Application Programming (IAP) capability

- Boot ROM contains low level Flash programming routines for downloading via the UART

- Can be programmed by the end-user application (IAP)

- Parallel programming with 87C51 compatible hardware interface to programmer

- Six clocks per machine cycle operation (standard)

- 12 clocks per machine cycle operation (optional)

- Speed up to 20 MHz with 6 clock cycles per machine cycle (40 MHz equivalent performance); up to 33 MHz with 12 clocks per machine cycle

- Fully static operation

- RAM externally expandable to 64 kbytes

- Four interrupt priority levels

- Eight interrupt sources

- Four 8-bit I/O ports

- Full-duplex enhanced UART

- Framing error detection

- Automatic address recognition

- Power control modes

- Clock can be stopped and resumed

- Idle mode

- Power-Down mode

- Programmable clock out

- Second DPTR register

- Asynchronous port reset

- Low EMI (inhibit ALE)

- I<sup>2</sup>C serial interface

- Programmable Counter Array (PCA)

- PWMCapture/compare

- Well-suited for IPMI applications

P89C660/P89C662/P89C664/

### 80C51 8-bit Flash microcontroller family 16KB/32KB/64KB ISP/IAP Flash with 512B/1KB/2KB/8KB RAM

#### SELECTION TABLE

| Туре    |      | Mem | ory |       |             | Tim          | ers          |              | S            | erial<br>fac |     | r-  |              |          |                          |                     |                       |                        |                           |                                                |                                  |                                  |

|---------|------|-----|-----|-------|-------------|--------------|--------------|--------------|--------------|--------------|-----|-----|--------------|----------|--------------------------|---------------------|-----------------------|------------------------|---------------------------|------------------------------------------------|----------------------------------|----------------------------------|

|         | RAM  | ROM | OTP | Flash | # of Timers | PWM          | PCA          | WD           | UART         | 12C          | CAN | SPI | ADC bits/ch. | I/O Pins | Interrupts<br>(External) | Program<br>Security | Default Clock<br>Rate | Optional<br>Clock Rate | Reset active<br>low/high? | Max.<br>Freq.<br>at 6-clk<br>/ 12-clk<br>(MHz) | Freq.<br>Range<br>at 3V<br>(MHz) | Freq.<br>Range<br>at 5V<br>(MHz) |

| P89C668 | 8K   | -   | -   | 64K   | 4           | $\checkmark$ | $\checkmark$ | $\checkmark$ | V            | $\checkmark$ | -   | -   | -            | 32       | 8(2)/4                   | $\checkmark$        | 6-clk                 | 12-clk                 | н                         | 20/33                                          | -                                | 0-20/33                          |

| P89C664 | 2K   | -   | -   | 64K   | 4           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -   | -   | -            | 32       | 8(2)/4                   | $\checkmark$        | 6-clk                 | 12-clk                 | Н                         | 20/33                                          | -                                | 0-20/33                          |

| P89C662 | 1K   | -   | -   | 32K   | 4           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -   | -   | -            | 32       | 8(2)/4                   | $\checkmark$        | 6-clk                 | 12-clk                 | Н                         | 20/33                                          | -                                | 0-20/33                          |

| P89C660 | 512B | -   | -   | 16K   | 4           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -   | -   | -            | 32       | 8(2)/4                   | $\checkmark$        | 6-clk                 | 12-clk                 | Н                         | 20/33                                          | -                                | 0-20/33                          |

#### **ORDERING INFORMATION**

|             | MEM   | ORY   |                                       | VOLTAGE          | FREQUEN      | ICY (MHz)        |          |

|-------------|-------|-------|---------------------------------------|------------------|--------------|------------------|----------|

| DEVICE      | FLASH | RAM   | TEMPERATURE RANGE (°C)<br>AND PACKAGE | VOLTAGE<br>RANGE | 6 CLOCK MODE | 12 CLOCK<br>MODE | DWG #    |

| P89C660HBA  | 16 KB | 512 B | 0 to +70, PLCC                        | 4.5–5.5 V        | 0 to 20 MHz  | 0 to 33 MHz      | SOT187-2 |

| P89C660HFA  | 16 KB | 512 B | -40 to +85, PLCC                      | 4.75–5.25 V      | 0 to 20 MHz  | 0 to 33 MHz      | SOT187-2 |

| P89C660HBBD | 16 KB | 512 B | 0 to +70, LQFP                        | 4.5–5.5 V        | 0 to 20 MHz  | 0 to 33 MHz      | SOT389-1 |

| P89C662HBA  | 32 KB | 1 KB  | 0 to +70, PLCC                        | 4.5–5.5 V        | 0 to 20 MHz  | 0 to 33 MHz      | SOT187-2 |

| P89C662HFA  | 32 KB | 1 KB  | -40 to +85, PLCC                      | 4.75–5.25 V      | 0 to 20 MHz  | 0 to 33 MHz      | SOT187-2 |

| P89C662HBBD | 32 KB | 1 KB  | 0 to +70, LQFP                        | 4.5–5.5 V        | 0 to 20 MHz  | 0 to 33 MHz      | SOT389-1 |

| P89C662HFBD | 32 KB | 1 KB  | -40 to +85, LQFP                      | 4.75–5.25 V      | 0 to 20 MHz  | 0 to 33 MHz      | SOT389-1 |

| P89C664HBA  | 64 KB | 2 KB  | 0 to +70, PLCC                        | 4.5–5.5 V        | 0 to 20 MHz  | 0 to 33 MHz      | SOT187-2 |

| P89C664HFA  | 64 KB | 2 KB  | -40 to +85, PLCC                      | 4.75–5.25 V      | 0 to 20 MHz  | 0 to 33 MHz      | SOT187-2 |

| P89C664HBBD | 64 KB | 2 KB  | 0 to +70, LQFP                        | 4.5–5.5 V        | 0 to 20 MHz  | 0 to 33 MHz      | SOT389-1 |

| P89C664HFBD | 64 KB | 2 KB  | -40 to +85, LQFP                      | 4.75–5.25 V      | 0 to 20 MHz  | 0 to 33 MHz      | SOT389-1 |

| P89C668HBA  | 64 KB | 8 KB  | 0 to +70, PLCC                        | 4.5–5.5 V        | 0 to 20 MHz  | 0 to 33 MHz      | SOT187-2 |

| P89C668HFA  | 64 KB | 8 KB  | -40 to +85, PLCC                      | 4.5–5.5 V        | 0 to 20 MHz  | 0 to 33 MHz      | SOT187-2 |

| P89C668HBBD | 64 KB | 8 KB  | 0 to +70, LQFP                        | 4.5–5.5 V        | 0 to 20 MHz  | 0 to 33 MHz      | SOT389-1 |

P89C660/P89C662/P89C664/

## 80C51 8-bit Flash microcontroller family

16KB/32KB/64KB ISP/IAP Flash with 512B/1KB/2KB/8KB RAM

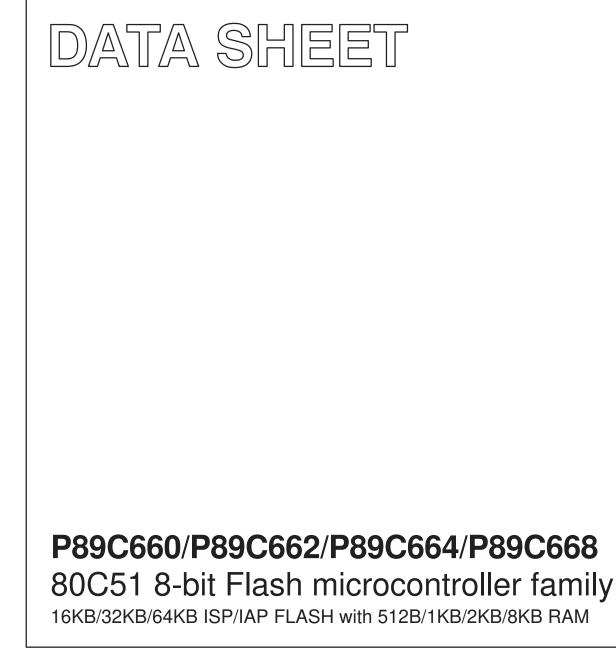

#### **BLOCK DIAGRAM 1**

P89C660/P89C662/P89C664/

### 80C51 8-bit Flash microcontroller family 16KB/32KB/64KB ISP/IAP Flash with 512B/1KB/2KB/8KB RAM

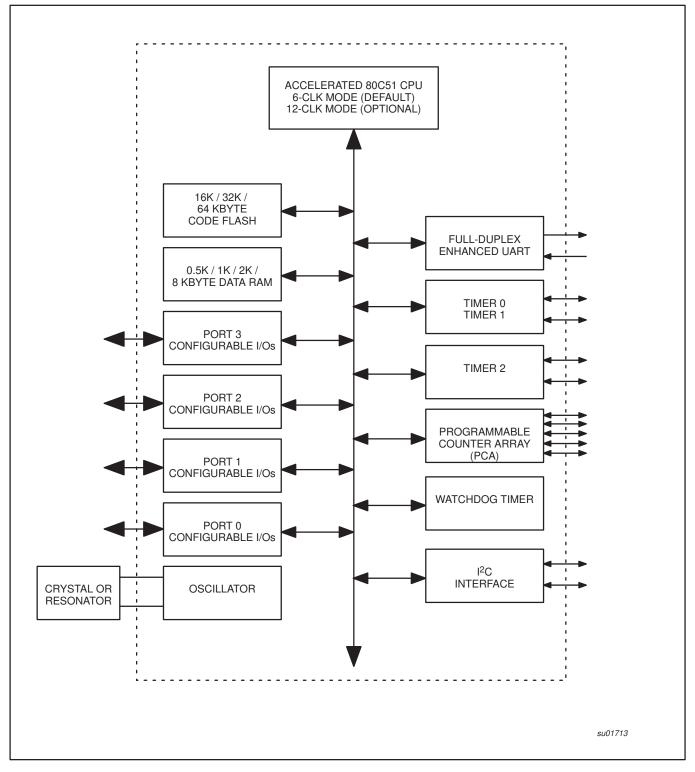

#### **BLOCK DIAGRAM (CPU-ORIENTED)**

P89C660/P89C662/P89C664/

### 80C51 8-bit Flash microcontroller family 16KB/32KB/64KB ISP/IAP Flash with 512B/1KB/2KB/8KB RAM

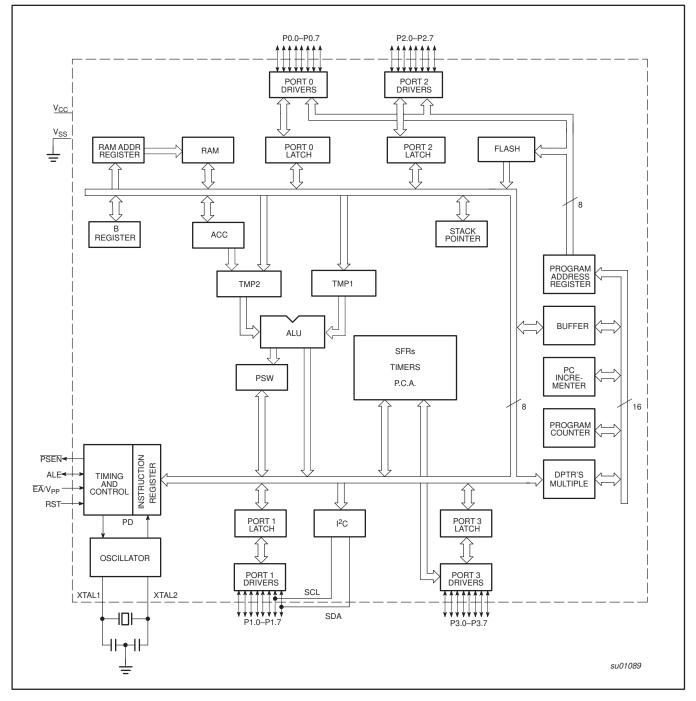

#### LOGIC SYMBOL

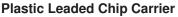

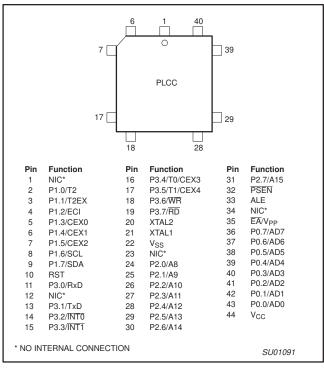

### PINNING

#### Low Quad Flat Pack

### P89C660/P89C662/P89C664/ P89C668

#### **PIN DESCRIPTIONS**

|                 | PIN NU       | JMBER         | ТҮРЕ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|--------------|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC        | PLCC         | LQFP          | ITPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>SS</sub> | 22           | 16            | I    | Ground: 0 V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>CC</sub> | 44           | 38            | 1    | Power Supply: This is the power supply voltage for normal, idle, and power-down operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| P0.0–0.7        | 43–36        | 37–30         | I/O  | <b>Port 0:</b> Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory. In this application, it uses strong internal pull-ups when emitting 1s.                                                                                                                                                                                                                                                                                                                                                                                                         |

| P1.0-P1.7       | 2–9          | 40–44,<br>1–3 | I/O  | <b>Port 1:</b> Port 1 is an 8-bit bidirectional I/O port with internal pull-ups on all pins except P1.6 and P1.7 which are open drain. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 1 pins that are externally pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: $I_{IL}$ ).                                                                                                                                                                                                                                                                                                                                             |

|                 |              |               |      | Alternate functions for P89C660/662/664/668 Port 1 include:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | 2            | 40            | I/O  | T2 (P1.0): Timer/Counter 2 external count input/Clockout (see Programmable Clock-Out)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | 3            | 41            | I.   | T2EX (P1.1): Timer/Counter 2 Reload/Capture/Direction Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 | 4            | 42            | 1    | ECI (P1.2): External Clock Input to the PCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | 5            | 43            | I/O  | CEX0 (P1.3): Capture/Compare External I/O for PCA module 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | 6            | 44            | I/O  | CEX1 (P1.4): Capture/Compare External I/O for PCA module 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | 7            | 1             | I/O  | CEX2 (P1.5): Capture/Compare External I/O for PCA module 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | 8            | 2             | I/O  | SCL (P1.6): I <sup>2</sup> C bus clock line (open drain)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 | 9            | 3             | I/O  | SDA (P1.7): I <sup>2</sup> C bus data line (open drain)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P2.0–P2.7       | 24–31        | 18–25         | I/O  | <b>Port 2:</b> Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 2 pins that are externally being pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: $I_{IL}$ ). Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOV @Ri), port 2 emits the contents of the P2 special function register. |

| P3.0–P3.7       | 11,<br>13–19 | 5, 7–13       | I/O  | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 3 pins that are externally being pulled low will source current because of the pull-ups. (See DC Electrical Characteristics: $I_{IL}$ ). Port 3 also serves the special features of the P89C660/662/664/668, as listed below:                                                                                                                                                                                                                                                                                                                 |

|                 | 11           | 5             | 1    | RxD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 | 13           | 7             | 0    | TxD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                 | 14           | 8             | 1    | INTO (P3.2): External interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | 15           | 9             | 1    | INT1 (P3.3): External interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | 16           | 10            | 1    | CEX3/T0 (P3.4): Timer 0 external input; Capture/Compare External I/O for PCA module 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | 17           | 11            | 1    | CEX4/T1 (P3.5): Timer 1 external input; Capture/Compare External I/O for PCA module 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | 18           | 12            | 0    | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 | 19           | 13            | 0    | RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RST             | 10           | 4             | I    | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal resistor to $V_{SS}$ permits a power-on reset using only an external capacitor to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ALE             | 33           | 27            | 0    | Address Latch Enable: Output pulse for latching the low byte of the address during an access to external memory. In normal operation, ALE is emitted twice every machine cycle, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory. ALE can be disabled by setting SFR auxiliary.0. With this bit set, ALE will be active only during a MOVX instruction.                                                                                                                                                                                                                                                                                                                       |

| PSEN            | 32           | 26            | 0    | <b>Program Store Enable:</b> The read strobe to external program memory. When executing code from the external program memory, <u>PSEN</u> is activated twice each machine cycle, except that two <u>PSEN</u> activations are skipped during each access to external data memory. <u>PSEN</u> is not activated during fetches from internal program memory.                                                                                                                                                                                                                                                                                                                                                                                                 |

### P89C660/P89C662/P89C664/ P89C668

| MNEMONIC           | PIN NU | MBER | ТҮРЕ | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------|--------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | PLCC   | LQFP | TIFE | NAME AND FONCTION                                                                                                                                                                                                                                                                                                                                                                                                                         |

| EA/V <sub>PP</sub> | 35     | 29   | Ι    | <b>External Access Enable/Programming Supply Voltage:</b> EA must be externally held low to enable the device to fetch code from external program memory locations. If EA is held high, the device executes from internal program memory. The value on the EA pin is latched when RST is released and any subsequent changes have no effect. This pin also receives the programming supply voltage ( $V_{PP}$ ) during Flash programming. |

| XTAL1              | 21     | 15   | I    | <b>Crystal 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                         |

| XTAL2              | 20     | 14   | 0    | Crystal 2: Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                |

#### NOTE:

To avoid "latch-up" effect at power-on, the voltage on any pin (other than  $V_{PP}$ ) must not be higher than  $V_{CC}$  + 0.5 V or less than  $V_{SS}$  – 0.5 V.

### P89C660/P89C662/P89C664/ P89C668

#### Table 1. Special Function Registers

| SYMBOL              | DESCRIPTION                                                     | DIRECT<br>ADDRESS | BIT A<br>MSB | DDRESS | , SYMBO     | L, OR AL    | TERNATI | E PORT | FUNCTIO | N<br>LSB | RESET<br>VALUE         |

|---------------------|-----------------------------------------------------------------|-------------------|--------------|--------|-------------|-------------|---------|--------|---------|----------|------------------------|

| ACC*                | Accumulator                                                     | E0H               | E7           | E6     | E5          | E4          | E3      | E2     | E1      | E0       | 00H                    |

| AUXR#               | Auxiliary                                                       | 8EH               | -            | -      | -           | -           | -       | -      | EXTRAM  | AO       | xxxxxx10B              |

| AUXR1#              | Auxiliary 1                                                     | A2H               | -            | -      | ENBOOT      | -           | GF2     | 0      | _       | DPS      | xxxxx0x0B              |

| B*                  | B register                                                      | F0H               | F7           | F6     | F5          | F4          | F3      | F2     | F1      | F0       | 00H                    |

| CCAP0H#             | Module 0 Capture High                                           | FAH               |              |        |             |             |         |        |         |          | xxxxxxxB               |

| CCAP1H#             | Module 1 Capture High                                           | FBH               |              |        |             |             |         |        |         |          | xxxxxxxB               |

| CCAP2H#             | Module 2 Capture High                                           | FCH               |              |        |             |             |         |        |         |          | xxxxxxxB               |

| CCAP3H#             | Module 3 Capture High                                           | FDH               |              |        |             |             |         |        |         |          | xxxxxxxB               |

| CCAP4H#             | Module 4 Capture High                                           | FEH               |              |        |             |             |         |        |         |          | xxxxxxxxB              |

| CCAP0L#<br>CCAP1L#  | Module 0 Capture Low<br>Module 1 Capture Low                    | EAH<br>EBH        |              |        |             |             |         |        |         |          | xxxxxxxxB<br>xxxxxxxxB |

| CCAP1L#             | Module 2 Capture Low                                            | ECH               |              |        |             |             |         |        |         |          | xxxxxxxB               |

| CCAP3L#             | Module 3 Capture Low                                            | EDH               |              |        |             |             |         |        |         |          | xxxxxxxB               |

| CCAP4L#             | Module 4 Capture Low                                            | EEH               |              |        |             |             |         |        |         |          | xxxxxxxB               |

| CCAPM0#             | Module 0 Mode                                                   | C2H               | _            | ECOM   | CAPP        | CAPN        | MAT     | TOG    | PWM     | ECCF     | x0000000B              |

| CCAPM1#             | Module 1 Mode                                                   | СЗН               | _            | ECOM   | CAPP        | CAPN        | MAT     | TOG    | PWM     | ECCF     | x0000000B              |

| CCAPM2#             | Module 2 Mode                                                   | C4H               | _            | ECOM   | CAPP        | CAPN        | MAT     | TOG    | PWM     | ECCF     | x0000000B              |

| CCAPM3#             | Module 3 Mode                                                   | C5H               | _            | ECOM   | CAPP        | CAPN        | MAT     | TOG    | PWM     | ECCF     | x0000000B              |

| CCAPM4#             | Module 4 Mode                                                   | C6H               | _            | ECOM   | CAPP        | CAPN        | MAT     | TOG    | PWM     | ECCF     | x0000000B              |

|                     |                                                                 | 0011              | C7           | C6     | C5          | C4          | C3      | C2     | C1      | C0       |                        |

| CCON*#              | PCA Counter Control                                             | C0H               | CF           | CR     | _           | CCF4        | CCF3    | CCF2   | CCF1    | CCF0     | 00x00000B              |

| CH#                 | PCA Counter High                                                | F9H               | 0.           | on     |             | 0011        | 0010    | 0012   | 0011    | 0010     | 00H                    |

| CL#                 | PCA Counter Low                                                 | E9H               |              | WOTE   |             |             |         | 0.004  | 0.000   | 505      | 00H                    |

| CMOD#               | PCA Counter Mode                                                | C1H               | CIDL         | WDTE   | -           | -           | -       | CPS1   | CPS0    | ECF      | 00xxx000B              |

| DPTR:<br>DPH<br>DPL | Data Pointer (2 bytes)<br>Data Pointer High<br>Data Pointer Low | 83H<br>82H        |              |        |             |             |         |        |         |          | 00H<br>00H             |

|                     |                                                                 |                   | AF           | AE     | AD          | AC          | AB      | AA     | A9      | A8       |                        |

| IEN0*               | Interrupt Enable 0                                              | A8H               | EA           | EC     | ES1         | ES0         | ET1     | EX1    | ET0     | EX0      | 00H                    |

| IEN1*               | Interrupt Enable 1                                              | E8                | _            | -      | -           | -           | -       | -      | -       | ET2      | xxxxxxx0B              |

|                     |                                                                 |                   | BF           | BE     | BD          | BC          | BB      | BA     | B9      | B8       | 1                      |

| IP*                 | Interrupt Priority                                              | B8H               | PT2          | PPC    | PS1         | PS0         | PT1     | PX1    | PT0     | PX0      | x0000000B              |

| IPH#                | Interrupt Priority High                                         | B7H               | PT2H         | PPCH   | PS1H        | PS0H        | PT1H    | PX1H   | PT0H    | PX0H     | x0000000B              |

|                     |                                                                 |                   | 87           | 86     | 85          | 84          | 83      | 82     | 81      | 80       |                        |

| P0*                 | Port 0                                                          | 80H               | AD7          | AD6    | AD5         | AD4         | AD3     | AD2    | AD1     | AD0      | FFH                    |

|                     |                                                                 |                   | 97           | 96     | 95          | 94          | 93      | 92     | 91      | 90       |                        |

| P1*                 | Port 1                                                          | 90H               | SDA          | SCL    | CEX2        | CEX1        | CEX0    | ECI    | T2EX    | T2       | FFH                    |

|                     |                                                                 |                   | A7           | A6     | A5          | A4          | A3      | A2     | A1      | A0       | 1                      |

| P2*                 | Port 2                                                          | A0H               | AD15         | AD14   | AD13        | AD12        | AD11    | AD10   | AD9     | AD8      | FFH                    |

|                     |                                                                 |                   | B7           | B6     | B5          | B4          | B3      | B2     | B1      | B0       | 1                      |

| P3*                 | Port 3                                                          | B0H               | RD           | WR     | T1/<br>CEX4 | T0/<br>CEX3 | INT1    | ĪNT0   | TxD     | RxD      | FFH                    |

| PCON# <sup>1</sup>  | Power Control                                                   | 87H               | SMOD1        | SMOD0  | _           | POF         | GF1     | GF0    | PD      | IDL      | 00xxx000B              |

\* SFRs are bit addressable.

# SFRs are modified from or added to the 80C51 SFRs.

Reserved bits.

1. Reset value depends on reset source.

### P89C660/P89C662/P89C664/ P89C668

#### Table 1 Special Function Registers (Continued)

| SYMBOL                                   | DESCRIPTION                                                                               | DIRECT<br>ADDRESS                      | BIT A<br>MSB | ADDRESS | 6, SYMBO | L, OR AL | TERNATIV | E PORT | FUNCTIO | ON<br>LSB | RESET<br>VALUE                         |

|------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------|--------------|---------|----------|----------|----------|--------|---------|-----------|----------------------------------------|

|                                          |                                                                                           |                                        | D7           | D6      | D5       | D4       | D3       | D2     | D1      | D0        |                                        |

| PSW*                                     | Program Status Word                                                                       | D0H                                    | CY           | AC      | F0       | RS1      | RS0      | OV     | F1      | Р         | 0000000B                               |

| RCAP2H#<br>RCAP2L#                       | Timer 2 Capture High<br>Timer 2 Capture Low                                               | CBH<br>CAH                             |              |         |          |          |          |        |         |           | 00H<br>00H                             |

| SADDR#<br>SADEN#                         | Slave Address<br>Slave Address Mask                                                       | A9H<br>B9H                             |              |         |          |          |          |        |         |           | 00H<br>00H                             |

| SOBUF                                    | Serial Data Buffer                                                                        | 99H                                    | 9F           | 9E      | 9D       | 9C       | 9B       | 9A     | 99      | 98        | xxxxxxxB                               |

| S0CON*                                   | Serial Control                                                                            | 98H                                    | SM0/FE       | SM1     | SM2      | REN      | TB8      | RB8    | TI      | RI        | 00H                                    |

| SP                                       | Stack Pointer                                                                             | 81H                                    |              |         |          |          |          |        |         |           | 07H                                    |

| S1DAT#                                   | Serial 1 Data                                                                             | DAH                                    |              |         |          |          |          |        |         |           | 00H                                    |

| S1ADR#                                   | Serial 1 Address                                                                          | DBH                                    |              |         | SLA      | VE ADDR  | ESS      |        |         | GC        | 00H                                    |

| S1STA#                                   | Serial 1 Status                                                                           | D9H                                    | SC4          | SC3     | SC2      | SC1      | SC0      | 0      | 0       | 0         | F8H                                    |

|                                          |                                                                                           |                                        | DF           | DE      | DD       | DC       | DB       | DA     | D9      | D8        |                                        |

| S1CON*#                                  | Serial 1 Control                                                                          | D8H                                    | CR2          | ENS1    | STA      | STO      | SI       | AA     | CR1     | CR0       | 00000000B                              |

|                                          |                                                                                           |                                        | 8F           | 8E      | 8D       | 8C       | 8B       | 8A     | 89      | 88        |                                        |

| TCON*                                    | Timer Control                                                                             | 88H                                    | TF1          | TR1     | TF0      | TR0      | IE1      | IT1    | IE0     | IT0       | 00H                                    |

|                                          |                                                                                           |                                        | CF           | CE      | CD       | CC       | СВ       | CA     | C9      | C8        |                                        |

| T2CON*                                   | Timer 2 Control                                                                           | C8H                                    | TF2          | EXF2    | RCLK     | TCLK     | EXEN2    | TR2    | C/T2    | CP/RL2    | 00H                                    |

| T2MOD#                                   | Timer 2 Mode Control                                                                      | C9H                                    | -            | -       | -        | -        | -        | -      | T2OE    | DCEN      | xxxxxx00B                              |

| TH0<br>TH1<br>TH2#<br>TL0<br>TL1<br>TL2# | Timer High 0<br>Timer High 1<br>Timer High 2<br>Timer Low 0<br>Timer Low 1<br>Timer Low 2 | 8CH<br>8DH<br>CDH<br>8AH<br>8BH<br>CCH |              |         |          |          |          |        |         |           | 00H<br>00H<br>00H<br>00H<br>00H<br>00H |

| TMOD                                     | Timer Mode                                                                                | 89H                                    | GATE         | C/T     | M1       | M0       | GATE     | C/T    | M1      | M0        | 00H                                    |

| WDTRST                                   | Watchdog Timer Reset                                                                      | A6H                                    |              |         |          |          |          |        |         |           |                                        |

SFRs are bit addressable.

# SFRs are modified from or added to the 80C51 SFRs.

Reserved bits.

#### **OSCILLATOR CHARACTERISTICS**

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier. The pins can be configured for use as an on-chip oscillator.

To drive the device from an external clock source, XTAL1 should be driven while XTAL2 is left unconnected. Minimum and maximum high and low times specified in the data sheet must be observed.

This device is configured at the factory to operate using 6 clock periods per machine cycle, referred to in this datasheet as "6 clock mode". (This yields performance equivalent to twice that of standard 80C51 family devices). It may be optionally configured on commercially-available EPROM programming equipment to operate at 12 clock periods per machine cycle, referred to in this datasheet as "12 clock mode". Once 12 clock mode has been configured, it cannot be changed back to 6 clock mode.

#### RESET

A reset is accomplished by holding the RST pin high for at least two machine cycles (12 oscillator periods in 6 clock mode, or 24 oscillator periods in 12 clock mode), while the oscillator is running. To insure a good power-on reset, the RST pin must be high long enough to allow the oscillator time to start up (normally a few milliseconds) plus two machine cycles. At power-on, the voltage on  $V_{CC}$  and RST must come up at the same time for a proper start-up. Ports 1, 2, and 3 will asynchronously be driven to their reset condition when a voltage above  $V_{IH1}$  (min.) is applied to RST.

The value on the  $\overline{\text{EA}}$  pin is latched when RST is deasserted and has no further effect.

### P89C660/P89C662/P89C664/ P89C668

#### LOW POWER MODES

#### Stop Clock Mode

The static design enables the clock speed to be reduced down to 0 MHz (stopped). When the oscillator is stopped, the RAM and Special Function Registers retain their values. This mode allows step-by-step utilization and reduces system power consumption by lowering the clock frequency down to any value. For lowest power consumption the Power-Down mode is suggested.

#### Idle Mode

In the idle mode (see Table 2), the CPU puts itself to sleep while all of the on-chip peripherals stay active. The instruction to invoke the idle mode is the last instruction executed in the normal operating mode before the idle mode is activated. The CPU contents, the on-chip RAM, and all of the special function registers remain intact during this mode. The idle mode can be terminated either by any enabled interrupt (at which time the process is picked up at the interrupt service routine and continued), or by a hardware reset which starts the processor in the same manner as a power-on reset.

#### **Power-Down Mode**

To save even more power, a Power-Down mode (see Table 2) can be invoked by software. In this mode, the oscillator is stopped and the instruction that invoked Power-Down is the last instruction executed. The on-chip RAM and Special Function Registers retain their values down to 2.0 V and care must be taken to return  $V_{CC}$  to the minimum specified operating voltages before the Power-Down mode is terminated.

Either a hardware reset or external interrupt can be used to exit from Power-Down. Reset redefines all the SFRs but does not change the on-chip RAM. An external interrupt allows both the SFRs and the on-chip RAM to retain their values.

To properly terminate Power-Down the reset or external interrupt should not be executed before  $V_{CC}$  is restored to its normal operating level and must be held active long enough for the oscillator to restart and stabilize (normally less than 10ms).

With an external interrupt, INT0 and INT1 must be enabled and configured as level-sensitive. Holding the pin low restarts the oscillator, but bringing the pin back high completes the exit. Once the interrupt is serviced, the next instruction to be executed after RETI will be the one following the instruction that put the device into Power-Down.

#### **POWER-ON FLAG**

The Power-On Flag (POF) is set by on-chip circuitry when the V<sub>CC</sub> level on the P89C660/662/664/668 rises from 0 to 5 V. The POF bit can be set or cleared by software allowing a user to determine if the reset is the result of a power-on or a warm start after Power-Down. The V<sub>CC</sub> level must remain above 3 V for the POF to remain unaffected by the V<sub>CC</sub> level.

#### **Design Consideration**

When the idle mode is terminated by a hardware reset, the device normally resumes program execution, from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, however, access to the port pins is not inhibited. To eliminate the possibility of an unexpected write when the idle mode is terminated by reset, the instruction following the one that invokes the idle mode should not be one that writes to a port pin or to external memory.

#### **ONCE™ Mode**

The ONCE ("On-Circuit Emulation") mode facilitates testing and debugging of systems without the device having to be removed from the circuit. The ONCE mode is invoked by:

- 1. Pulling ALE low while the device is in reset and PSEN is high;

- 2. Holding ALE low as RST is deactivated.

While the device is in ONCE mode, the Port 0 pins go into a float state, and the other port pins and ALE and PSEN are weakly pulled high. The oscillator circuit remains active. While the device is in this mode, an emulator or test CPU can be used to drive the circuit. Normal operation is restored when a normal reset is applied.

#### **Programmable Clock-Out**

A 50% duty cycle clock can be programmed to come out on P1.0. This pin, besides being a regular I/O pin, has two alternate functions. It can be programmed:

- 1. to input the external clock for Timer/Counter 2, or

- to output a 50% duty cycle clock ranging from 122 Hz to 8 MHz at a 16 MHz operating frequency (61 Hz to 4 MHz in 12 clock mode).

To configure the Timer/Counter 2 as a clock generator, bit C/T2 (in T2CON) must be cleared and bit T20E in T2MOD must be set. Bit TR2 (T2CON.2) also must be set to start the timer.

The Clock-Out frequency depends on the oscillator frequency and the reload value of Timer 2 capture registers (RCAP2H, RCAP2L) as shown in this equation:

$\frac{\text{Oscillator Frequency}}{n \times (65536 ( \text{ RCAP2H, RCAP2L}))}$  n = 2 in 6 clock mode 4 in 12 clock mode

Where (RCAP2H,RCAP2L) = the content of RCAP2H and RCAP2L taken as a 16-bit unsigned integer.

In the Clock-Out mode Timer 2 roll-overs will not generate an interrupt. This is similar to when it is used as a baud-rate generator. It is possible to use Timer 2 as a baud-rate generator and a clock generator simultaneously. Note, however, that the baud-rate and the Clock-Out frequency will be the same.

| Table 2. E | External Pin | Status | During | Idle and | Power-Down mode |

|------------|--------------|--------|--------|----------|-----------------|

|------------|--------------|--------|--------|----------|-----------------|

| MODE       | PROGRAM MEMORY | ALE | PSEN | PORT 0 | PORT 1 | PORT 2  | PORT 3 |

|------------|----------------|-----|------|--------|--------|---------|--------|

| Idle       | Internal       | 1   | 1    | Data   | Data   | Data    | Data   |

| Idle       | External       | 1   | 1    | Float  | Data   | Address | Data   |

| Power-Down | Internal       | 0   | 0    | Data   | Data   | Data    | Data   |

| Power-Down | External       | 0   | 0    | Float  | Data   | Data    | Data   |

### P89C660/P89C662/P89C664/ P89C668

#### I<sup>2</sup>C SERIAL COMMUNICATION — SIO1

The I<sup>2</sup>C serial port is identical to the I<sup>2</sup>C serial port on the 8XC554, 8XC654, and 8XC652 devices.

Note that the P89C660/662/664/668 I<sup>2</sup>C pins are alternate functions to port pins P1.6 and P1.7. Because of this, P1.6 and P1.7 on these parts do not have a pull-up structure as found on the 80C51. Therefore P1.6 and P1.7 have open drain outputs on the P89C660/662/664/668.

The I<sup>2</sup>C bus uses two wires (SDA and SCL) to transfer information between devices connected to the bus. The main features of the bus are:

- Bidirectional data transfer between masters and slaves

- Multimaster bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer

- The I<sup>2</sup>C bus may be used for test and diagnostic purposes

The output latches of P1.6 and P1.7 must be set to logic 1 in order to enable SIO1.

The P89C66x on-chip  $I^2C$  logic provides a serial interface that meets the  $I^2C$  bus specification and supports all transfer modes (other than the low-speed mode) from and to the  $I^2C$  bus. The SIO1 logic handles bytes transfer autonomously. It also keeps track of serial transfers, and a status register (S1STA) reflects the status of SIO1 and the  $I^2C$  bus.

The CPU interfaces to the I<sup>2</sup>C logic via the following four special function registers: S1CON (SIO1 control register), S1STA (SIO1 status register), S1DAT (SIO1 data register), and S1ADR (SIO1 slave address register). The SIO1 logic interfaces to the external I<sup>2</sup>C bus via two port 1 pins: P1.6/SCL (serial clock line) and P1.7/SDA (serial data line).

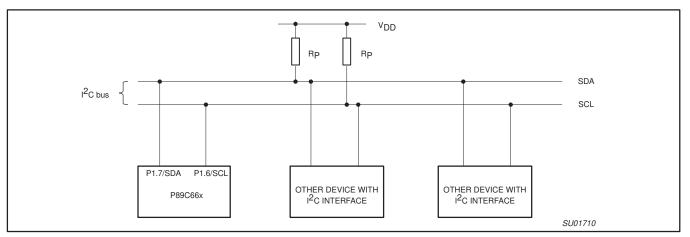

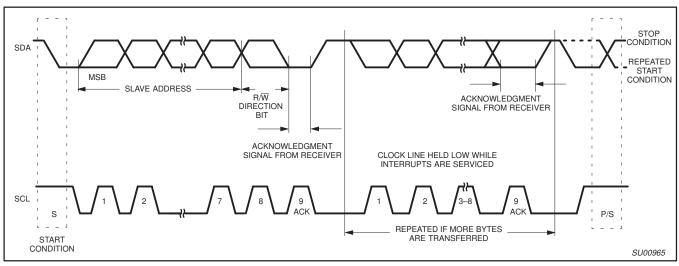

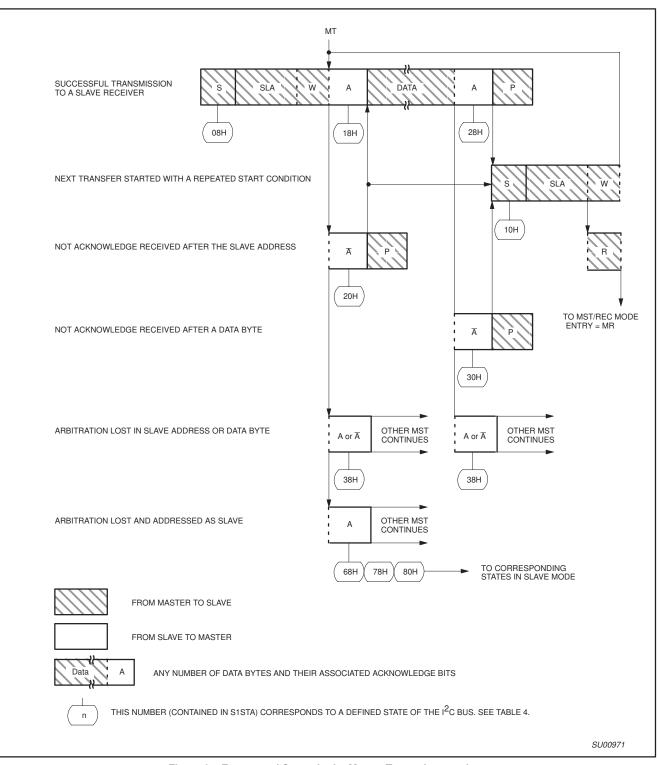

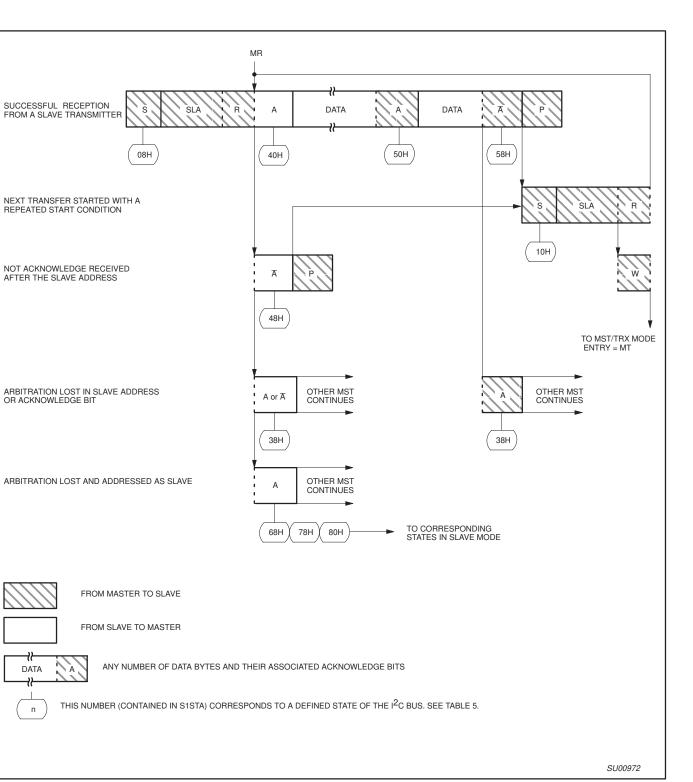

A typical I<sup>2</sup>C bus configuration is shown in Figure 1. Figure 2 shows how a data transfer is accomplished on the bus. Depending on the state of the direction bit (R/W), two types of data transfers are possible on the I<sup>2</sup>C bus:

- Data transfer from a master transmitter to a slave receiver. The first byte transmitted by the master is the slave address. Next follows a number of data bytes. The slave returns an acknowledge bit after each received byte.

- 2. Data transfer from a slave transmitter to a master receiver. The first byte (the slave address) is transmitted by the master. The slave then returns an acknowledge bit. Next follows the data bytes transmitted by the slave to the master. The master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received byte, a "not acknowledge" is returned.

The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP

condition or with a repeated START condition. Since a repeated START condition is also the beginning of the next serial transfer, the  $I^2C$  bus will not be released.

#### **Modes of Operation**

The on-chip SIO1 logic may operate in the following four modes:

1. Master Transmitter mode:

Serial data output through P1.7/SDA while P1.6/SCL outputs the serial clock. The first transmitted byte contains the slave address of the receiving device (7 bits) and the data direction bit. In this mode the data direction bit (R/W) will be logic 0, and we say that a "W" is transmitted. Thus the first byte transmitted is SLA+W. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an acknowledge bit is received. START and STOP conditions are output to indicate the beginning and the end of a serial transfer.

2. Master Receiver Mode:

The first transmitted byte contains the slave address of the transmitting device (7 bits) and the data direction bit. In this mode the data direction bit (R/W) will be logic 1, and we say that an "R" is transmitted. Thus the first byte transmitted is SLA+R. Serial data is received via P1.7/SDA while P1.6/SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an acknowledge bit is transmitted. START and STOP conditions are output to indicate the beginning and end of a serial transfer.

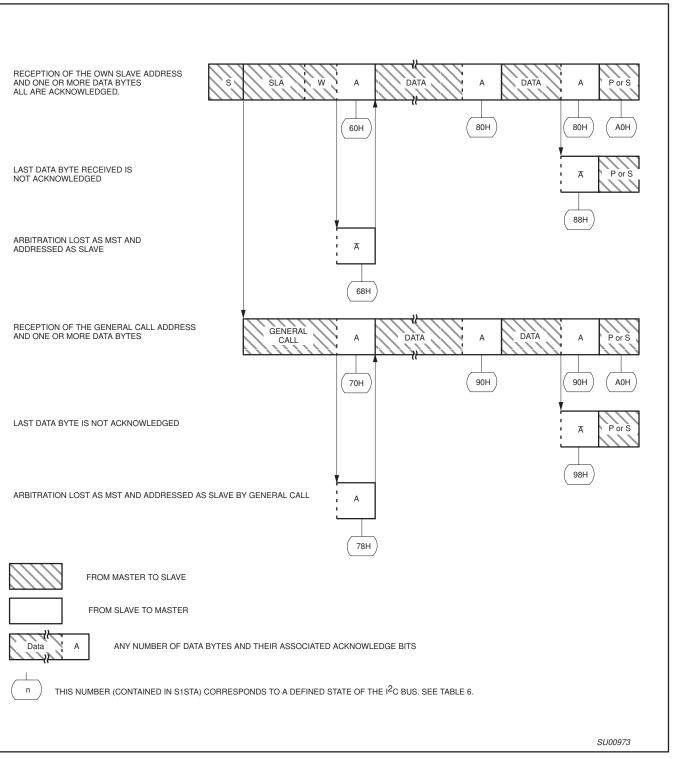

3. Slave Receiver mode:

Serial data and the serial clock are received through P1.7/SDA and P1.6/SCL. After each byte is received, an acknowledge bit is transmitted. START and STOP conditions are recognized as the beginning and end of a serial transfer. Address recognition is performed by hardware after reception of the slave address and direction bit.

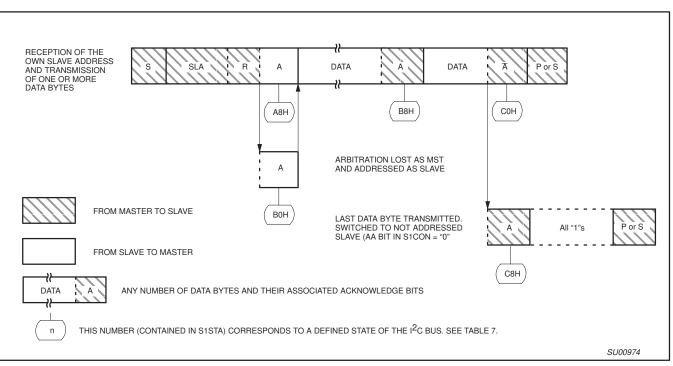

4. Slave Transmitter mode:

The first byte is received and handled as in the Slave Receiver mode. However, in this mode, the direction bit will indicate that the transfer direction is reversed. Serial data is transmitted via P1.7/SDA while the serial clock is input through P1.6/SCL. START and STOP conditions are recognized as the beginning and end of a serial transfer.

In a given application, SIO1 may operate as a master and as a slave. In the Slave mode, the SIO1 hardware looks for its own slave address and the general call address. If one of these addresses is detected, an interrupt is requested. When the microcontroller wishes to become the bus master, the hardware waits until the bus is free before the Master mode is entered so that a possible slave action is not interrupted. If bus arbitration is lost in the Master mode, SIO1 switches to the Slave mode immediately and can detect its own slave address in the same serial transfer.

Figure 1. Typical I<sup>2</sup>C Bus Configuration

Figure 2. Data Transfer on the I<sup>2</sup>C Bus

#### SIO1 Implementation and Operation

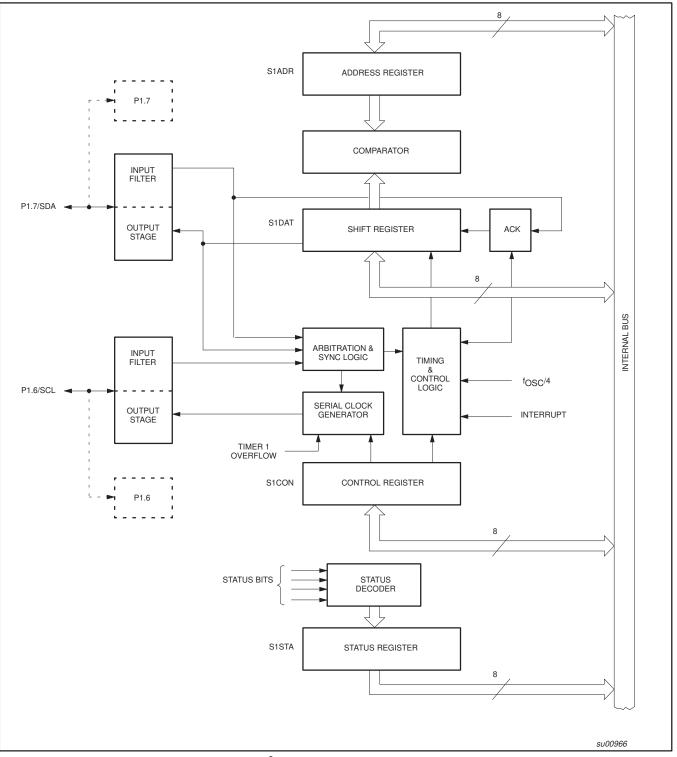

Figure 3 shows how the on-chip  $I^2C$  bus interface is implemented, and the following text describes the individual blocks.

#### Input Filters and Output Stages

The input filters have I<sup>2</sup>C compatible input levels. If the input voltage is less than 1.5 V, the input logic level is interpreted as 0; if the input voltage is greater than 3.0 V, the input logic level is interpreted as 1. Input signals are synchronized with the internal clock ( $f_{OSC}/4$ ), and spikes shorter than three oscillator periods are filtered out.

The output stages consist of open drain transistors that can sink 3mA at  $V_{OUT}$  < 0.4 V. These open drain outputs do not have clamping diodes to  $V_{DD}$ . Thus, if the device is connected to the  $l^2C$  bus and  $V_{DD}$  is switched off, the  $l^2C$  bus is not affected.

#### Address Register, S1ADR

This 8-bit special function register may be loaded with the 7-bit slave address (7 most significant bits) to which SIO1 will respond when programmed as a slave transmitter or receiver. The LSB (GC) is used to enable general call address (00H) recognition.

#### Comparator

The comparator compares the received 7-bit slave address with its own slave address (7 most significant bits in S1ADR). It also compares the first received 8-bit byte with the general call address (00H). If an equality is found, the appropriate status bits are set and an interrupt is requested.

#### Shift Register, S1DAT

This 8-bit special function register contains a byte of serial data to be transmitted or a byte which has just been received. Data in S1DAT is always shifted from right to left; the first bit to be transmitted is the MSB (bit 7) and, after a byte has been received, the first bit of received data is located at the MSB of S1DAT. While data is being shifted out, data on the bus is simultaneously being shifted in; S1DAT always contains the last byte present on the bus. Thus, in the event of lost arbitration, the transition from master transmitter to slave receiver is made with the correct data in S1DAT.

Figure 3. I<sup>2</sup>C Bus Serial Interface Block Diagram

### 80C51 8-bit Flash microcontroller family 16KB/32KB/64KB ISP/IAP Flash with 512B/1KB/2KB/8KB RAM

#### Arbitration and Synchronization Logic

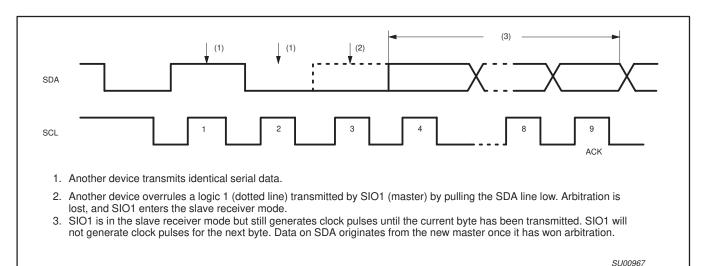

In the Master Transmitter mode, the arbitration logic checks that every transmitted logic 1 actually appears as a logic 1 on the  $I^2C$ bus. If another device on the bus overrules a logic 1 and pulls the SDA line low, arbitration is lost, and SIO1 immediately changes from master transmitter to slave receiver. SIO1 will continue to output clock pulses (on SCL) until transmission of the current serial byte is complete.

Arbitration may also be lost in the Master Receiver mode. Loss of arbitration in this mode can only occur while SIO1 is returning a "not acknowledge: (logic 1) to the bus. Arbitration is lost when another device on the bus pulls this signal LOW. Since this can occur only at the end of a serial byte, SIO1 generates no further clock pulses. Figure 4 shows the arbitration procedure.

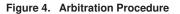

The synchronization logic will synchronize the serial clock generator with the clock pulses on the SCL line from another device. If two or more master devices generate clock pulses, the "mark" duration is determined by the device that generates the shortest "marks," and the "space" duration is determined by the device that generates the longest "spaces." Figure 5 shows the synchronization procedure.

P89C660/P89C662/P89C664/

A slave may stretch the space duration to slow down the bus master. The space duration may also be stretched for handshaking purposes. This can be done after each bit or after a complete byte transfer. SIO1 will stretch the SCL space duration after a byte has been transmitted or received and the acknowledge bit has been transferred. The serial interrupt flag (SI) is set, and the stretching continues until the serial interrupt flag is cleared.

Figure 5. Serial Clock Synchronization

### 80C51 8-bit Flash microcontroller family 16KB/32KB/64KB ISP/IAP Flash with 512B/1KB/2KB/8KB RAM

#### Serial Clock Generator

This programmable clock pulse generator provides the SCL clock pulses when SIO1 is in the Master Transmitter or Master Receiver mode. It is switched off when SIO1 is in a Slave mode. The programmable output clock frequencies are:  $f_{OSC}/120$ ,  $f_{OSC}/9600$  (12-clock mode) or  $f_{OSC}/60$ ,  $f_{OSC}/4800$  (6-clock mode) and the Timer 1 overflow rate divided by eight. The output clock pulses have a 50% duty cycle unless the clock generator is synchronized with other SCL clock sources as described above.

#### **Timing and Control**

The timing and control logic generates the timing and control signals for serial byte handling. This logic block provides the shift pulses for S1DAT, enables the comparator, generates and detects start and stop conditions, receives and transmits acknowledge bits, controls the master and Slave modes, contains interrupt request logic, and monitors the  $I^2C$  bus status.

#### **Control Register, S1CON**

This 7-bit special function register is used by the microcontroller to control the following SIO1 functions: start and restart of a serial transfer, termination of a serial transfer, bit rate, address recognition, and acknowledgment.

#### Status Decoder and Status Register

The status decoder takes all of the internal status bits and compresses them into a 5-bit code. This code is unique for each I<sup>2</sup>C bus status. The 5-bit code may be used to generate vector addresses for fast processing of the various service routines. Each service routine processes a particular bus status. There are 26 possible bus states if all four modes of SIO1 are used. The 5-bit status code is latched into the five most significant bits of the status register when the serial interrupt flag is set (by hardware) and remains stable until the interrupt flag is cleared by software. The three least significant bits of the status register are always zero. If the status code is used as a vector to service routines, then the routines are displaced by eight address locations. Eight bytes of code is sufficient for most of the service routines.

#### The Four SIO1 Special Function Registers

The microcontroller interfaces to SIO1 via four special function registers. These four SFRs (S1ADR, S1DAT, S1CON, and S1STA) are described individually in the following sections.

#### The Address Register, S1ADR

The CPU can read from and write to this 8-bit, directly addressable SFR. S1ADR is not affected by the SIO1 hardware. The contents of this register are irrelevant when SIO1 is in a Master mode. In the Slave modes, the seven most significant bits must be loaded with the microcontroller's own slave address, and, if the least significant bit is set, the general call address (00H) is recognized; otherwise it is ignored.

|             | 7                 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |  |  |

|-------------|-------------------|---|---|---|---|---|---|----|--|--|

| S1ADR (DBH) | Х                 | Х | Х | Х | Х | Х | х | GC |  |  |

|             | own slave address |   |   |   |   |   |   |    |  |  |

The most significant bit corresponds to the first bit received from the  $I^2C$  bus after a start condition. A logic 1 in S1ADR corresponds to a high level on the  $I^2C$  bus, and a logic 0 corresponds to a low level on the bus.

#### The Data Register, S1DAT

S1DAT contains a byte of serial data to be transmitted or a byte which has just been received. The CPU can read from and write to

this 8-bit, directly addressable SFR while it is not in the process of shifting a byte. This occurs when SIO1 is in a defined state and the serial interrupt flag is set. Data in S1DAT remains stable as long as SI is set. Data in S1DAT is always shifted from right to left: the first bit to be transmitted is the MSB (bit 7), and, after a byte has been received, the first bit of received data is located at the MSB of S1DAT. While data is being shifted out, data on the bus is simultaneously being shifted in; S1DAT always contains the last data byte present on the bus. Thus, in the event of lost arbitration, the transition from master transmitter to slave receiver is made with the correct data in S1DAT.

P89C660/P89C662/P89C664/

|             | 7   | 6   | 5   | 4           | 3      | 2   | 1   | 0   |

|-------------|-----|-----|-----|-------------|--------|-----|-----|-----|

| S1DAT (DAH) | SD7 | SD6 | SD5 | SD4         | SD3    | SD2 | SD1 | SD0 |

|             | -   |     |     | shift direc | tion — |     |     |     |

#### SD7 - SD0:

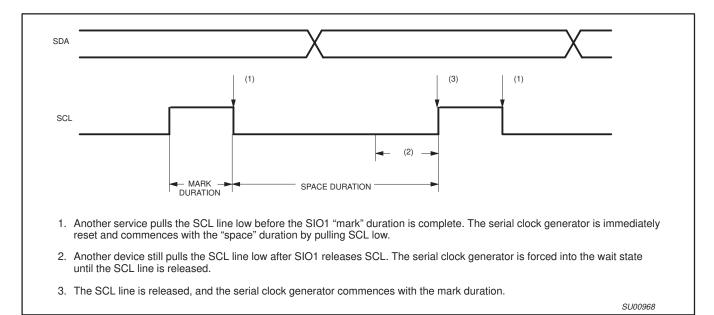

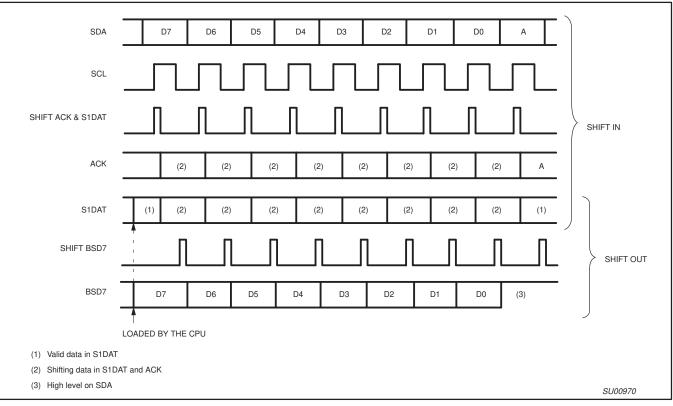

Eight bits to be transmitted or just received. A logic 1 in S1DAT corresponds to a high level on the  $l^2C$  bus, and a logic 0 corresponds to a low level on the bus. Serial data shifts through S1DAT from right to left. Figure 6 shows how data in S1DAT is serially transferred to and from the SDA line.

S1DAT and the ACK flag form a 9-bit shift register which shifts in or shifts out an 8-bit byte, followed by an acknowledge bit. The ACK flag is controlled by the SIO1 hardware and cannot be accessed by the CPU. Serial data is shifted through the ACK flag into S1DAT on the rising edges of serial clock pulses on the SCL line. When a byte has been shifted into S1DAT, the serial data is available in S1DAT, and the acknowledge bit is returned by the control logic during the ninth clock pulse. Serial data is shifted out from S1DAT via a buffer (BSD7) on the falling edges of clock pulses on the SCL line.

When the CPU writes to S1DAT, BSD7 is loaded with the content of S1DAT.7, which is the first bit to be transmitted to the SDA line (see Figure 7). After nine serial clock pulses, the eight bits in S1DAT will have been transmitted to the SDA line, and the acknowledge bit will be present in ACK. Note that the eight transmitted bits are shifted back into S1DAT.

#### The Control Register, S1CON

The CPU can read from and write to this 8-bit, directly addressable SFR. Two bits are affected by the SIO1 hardware: the SI bit is set when a serial interrupt is requested, and the STO bit is cleared when a STOP condition is present on the  $I^2C$  bus. The STO bit is also cleared when ENS1 = "0".

|             | 7   | 6    | 5   | 4   | 3  | 2  | 1   | 0   |

|-------------|-----|------|-----|-----|----|----|-----|-----|

| S1CON (D8H) | CR2 | ENS1 | STA | STO | SI | AA | CR1 | CR0 |

**ENS1, the SIO1 Enable Bit:** ENS1 = "0": When ENS1 is "0", the SDA and SCL outputs are in a high impedance state. SDA and SCL input signals are ignored, SIO1 is in the "not addressed" slave state, and the STO bit in S1CON is forced to "0". No other bits are affected. P1.6 and P1.7 may be used as open drain I/O ports.

ENS1 ="1": When ENS1 is "1", SIO1 is enabled. The P1.6 and P1.7 port latches must be set to logic 1.

ENS1 should not be used to temporarily release SIO1 from the I2C bus since, when ENS1 is reset, the I2C bus status is lost. The AA flag should be used instead (see description of the AA flag in the following text).

### P89C660/P89C662/P89C664/ P89C668

Figure 6. Serial Input/Output Configuration

Figure 7. Shift-in and Shift-out Timing

In the following text, it is assumed that ENS1 = "1".

The "START" Flag, STA: STA = "1": When the STA bit is set to enter a Master mode, the SIO1 hardware checks the status of the I2C bus and generates a START condition if the bus is free. If the bus is not free, then SIO1 waits for a STOP condition (which will free the bus) and generates a START condition after a delay of half a clock period of the internal serial clock generator.

If STA is set while SIO1 is already in a Master mode and one or more bytes are transmitted or received, SIO1 transmits a repeated START condition. STA may be set at any time. STA may also be set when SIO1 is an addressed slave. STA = "0": When the STA bit is reset, no START condition or repeated START condition will be generated.