Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Audio, LED Backlight, Power Management, and Control

**Product Datasheet**

## **IDTP95020**

#### **Features**

- Quick Turn Customization

- Embedded Microcontroller

- Master controller during power-up and power-down

- Power up/down sequence field programmable with external EEPROM

- Dynamic power management via I<sup>2</sup>C bus interface

- Up to 10 general purpose I/Os

- Housekeeping for IDTP95020 and other devices

- Audio 4 Channel CODEC with 24-bit resolution

- Integrated 2.5W mono Class D amplifier with filterless operation

- Stereo cap-less headphone driver

- Differential analog audio line inputs

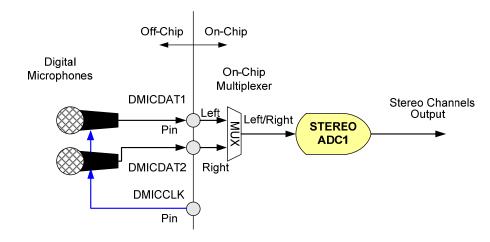

- Dual mode microphone inputs (analog or DMIC)

- Battery Charger for Li-Ion / Li-Polymer up to 1.5A

- High efficiency switch-mode EnergyPath™ controller with advanced safety features

- USB or AC adaptor power input (5V)

- Programmable current limit

- Internal  $180m\Omega$  ideal diode with external ideal diode controller

- Buck DC-DC PWM converters with PFM mode

- 2x at 500mA, 0.75V to 3.7V output

- 1x at 1000mA, 0.75V to 3.7V output

- Boost DC-DC PWM converter

- 1x at 1.5A peak current, 4.05V to 5.0V output

- 2-ch white LED driver with 2W total output power

- Two programmable current sinks, 25mA each

- Voltage limited to rating of external FET and diode

- Linear regulators

- 3x at 150mA, 0.75V to 3.7V output

- 4x at 50mA, 0.75V to 3.7V output

- 1x at 10mA, 3.3V or 3.0V output, always-on

- ADC and Touch Screen Controller

- 12 bit resolution, Sample rate 62.5kSPS, DNL -1~+2LSB, INL +/-2LSB, on chip 2.5V reference

- On-chip temperature, charging current, SYS voltage and battery voltage measurement

- Touch pressure measurement

- 4-wire Touch Screen interface (shared with GPIO pins and ADC input channels)

- 0°C to 70°C operating temperature range

- 132-ld 10x10x0.85mm dual-row QFN package

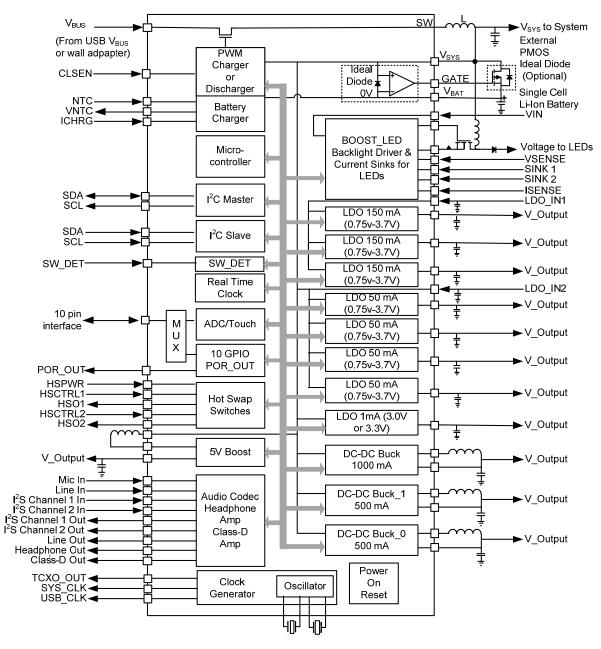

#### **Description**

The IDTP95020 is designed to provide maximum flexibility to system designers by providing full customization and programmability. It is a highly integrated single chip device that incorporates an embedded general purpose microcontroller, a high fidelity audio CODEC, full power management functionality, backlight driver, battery charger, touch screen controller, and real time clock, all of which make it an ideal solution for portable consumer devices, such as cellular phone handsets, portable gaming devices, digital media players, and portable navigational devices. The device compact footprint optimizes board area and reduces component count.

The IDTP95020 embedded Microcontroller features 4kB factory-programmable ROM, or the I²C master can load a custom program from an external EEPROM module. The system power-on/power-off sequencing and general system housekeeping can be programmed in internal ROM or external EEPROM. The I²C slave can be used during operation to communicate with the host to accept commands and report status.

The IDTP95020 operates from an adapter or USB power source to deliver power to the system load while charging the battery; up to 1.5A charging current. The input current is limited to the value set by the host for adapter source (up to 2A) or for USB source (100mA or 500mA). The switch-mode EnergyPath™ Battery Charger operates with a high efficiency buck regulator to transmit the power to the load with minimal loss.

The IDTP95020 power management features along with the switching regulators and LDOs can provide power for most extremely complex hand-held devices.

The device is offered in a small 132-ld 10x10x0.85mm QFN package and guaranteed to operate over the commercial temperature range 0°C to 70°C.

## **Applications**

- Smart Phones

- Portable Gaming Device

- Digital Media Players

- Handheld Computers

- Portable Navigational Devices

## Audio, LED Backlight, Power Management, and Control

**Product Datasheet**

**IDTP95020**

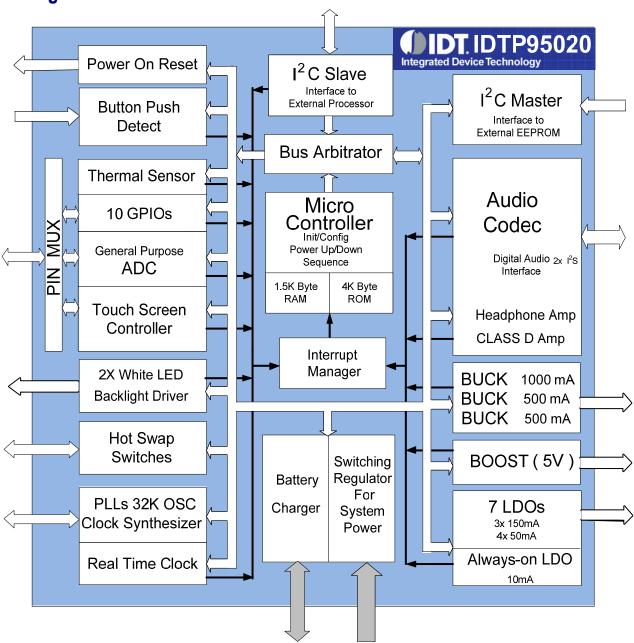

## **Block Diagram**

Figure 1. Simplified Block Diagram

## **Table of Contents**

| Absolute Maximum Ratings                           | 5      | Charger – Register Addresses                                    | 62       |

|----------------------------------------------------|--------|-----------------------------------------------------------------|----------|

| ESD Warning                                        | 6      | Charger – Pre-Regulator                                         | 67       |

| Recommended Operating Conditions                   | 6      | Charger – Ideal Diode from V <sub>BAT</sub> to V <sub>SYS</sub> | 68       |

| Power Consumption                                  |        | Charger – Charger / Discharger                                  | 68       |

| Overall Power Consumption                          | 6      | Charger – Thermal Monitoring                                    | 69       |

| Audio Power Consumption                            | 7      | Charger – Power On Reset                                        | 69       |

| Digital Interfaces Electrical Characteristics      | 8      | Clock Generator Module                                          | 71       |

| I <sup>2</sup> C Master Electrical Characteristics | 8      | Clock Generator – Pin Definitions                               | 72       |

| I <sup>2</sup> C Slave Electrical Characteristics  | 8      | Clock Generator - Oscillator Electrical Characte                | eristics |

| I <sup>2</sup> S Electrical Characteristics        | 8      |                                                                 | 72       |

| GPIO Electrical Characteristics                    | 8      | Clock Generator – PLL Control                                   | 74       |

| Pin Configuration and Description                  | 9      | Clock Generator – Oscillator Circuit                            | 74       |

| I/O Type Description                               | 14     | Clock Generator – Power Source                                  | 74       |

| Product Overview                                   | 15     | Clock Generator – On Chip Clock                                 | 75       |

| Functional Modes                                   | 16     | Clock Generator – Clock Accuracy                                | 76       |

| Register Map                                       | 16     | Clock Generator - Registers                                     | 76       |

| Byte Ordering and Offset                           | 17     | RTC Module                                                      | 78       |

| Reserved Bit Fields                                |        | RTC – General Description                                       | 78       |

| Register Access Types                              | 17     | RTC – Timekeeper Registers                                      | 79       |

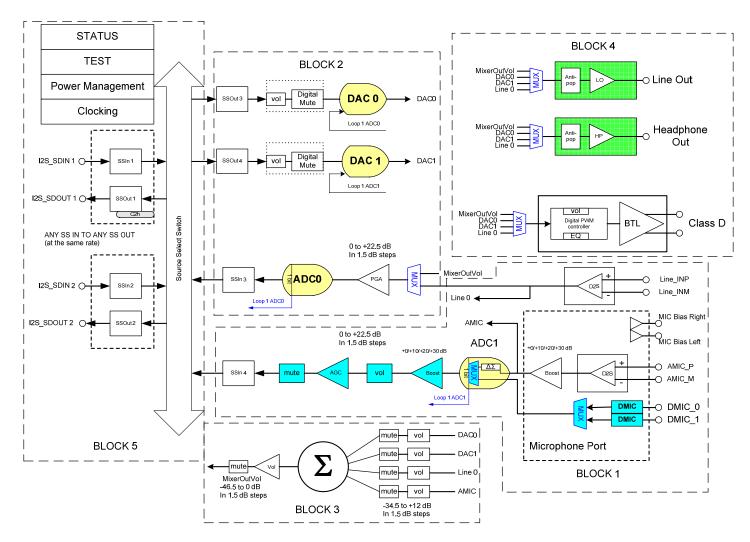

| Audio Module                                       |        | RTC – Date Registers                                            | 80       |

| Audio – Pin Definitions                            | 19     | RTC – Alarm Registers                                           | 81       |

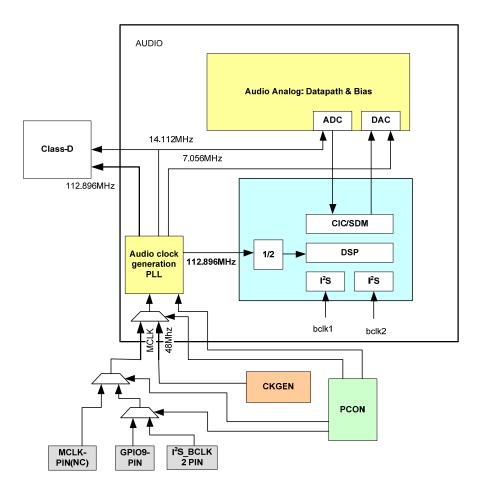

| Audio – Section Overview                           | 19     | RTC – Interrupt Registers                                       | 84       |

| Audio – Power Up Audio Module                      | 19     | RTC – Reserved Registers                                        | 84       |

| Audio – Analog Performance Characteristics         |        | General Purpose Timers                                          | 85       |

| Audio – Microphone Input Port                      |        | GP Timers – General Description                                 |          |

| Audio – Analog Line Input                          |        | GP Timers – Registers                                           |          |

| Audio – DAC, ADC                                   |        | DC-DC Module                                                    |          |

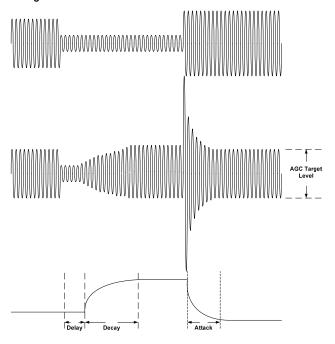

| Audio – Automatic Gain Control                     |        | Buck Regulators                                                 | 89       |

| Audio – Analog Mixer Block                         | 25     | Buck Regulators – Pin Definitions                               |          |

| Audio – Digital Audio Input / Output Interface     |        | Buck Regulators – Electrical Characteristics                    |          |

| Audio – Subsystem Clocking                         |        | Buck Regulators – Typical Performance Characte                  | eristics |

| Audio - Reference Voltage Generator, Buffer        |        |                                                                 | 91       |

| Filtering Caps                                     |        | Buck Regulators – Register Addresses                            | 92       |

| Audio - Analog and Class D Output Block            | 28     | Buck Regulators – Enable / Disable                              |          |

| Audio – Class D BTL Amplifier                      | 28     | Buck Regulators – Application                                   | 96       |

| Audio – Class D Registers                          | 29     | LED Boost Converter and Sinks                                   | 98       |

| Audio - Class D Equalizer Coefficient and Pre      | scaler | LED Boost – Operating Requirements                              | 99       |

| Ram (EQRAM)                                        |        | LED Boost – Electrical Characteristics                          | 99       |

| Audio - Control Registers                          |        | LED Boost – Typical Performance Characteristics                 | 3 100    |

| Charger Module                                     |        | LED Boost – Register Settings                                   | 100      |

| Charger – Overview                                 | 58     | LED Boost – Enable / Disable                                    |          |

| Charger – Sub-blocks                               |        | LED Boost – Over-Voltage Protection                             | 102      |

| Charger – DC Electrical Characteristics            | 59     | LED Boost – Over-Current Limiter                                | 102      |

| Charger – Typical Performance Characteristics      |        | LED Boost - Application                                         | 103      |

## **IDTP95020**

#### **Product Datasheet**

| Boost5 Regulator105                                      | I <sup>2</sup> C Slave                                 | 143 |

|----------------------------------------------------------|--------------------------------------------------------|-----|

| Boost5 – Electrical Specifications106                    | Interrupt Dispatcher                                   | 144 |

| Boost5 – Typical Performance Characteristics106          | Access Arbiter                                         | 144 |

| Boost5 – Register Settings107                            | Digital Audio Data Serial Interface                    | 144 |

| Boost5 – Enable / Disable108                             | I <sup>2</sup> C / I <sup>2</sup> S – Interface Timing |     |

| Boost5 – Output Diode109                                 | Global Register Settings (I <sup>2</sup> C-page 0)     | 146 |

| Boost5 - Application109                                  | ACCM Registers                                         |     |

| Class D BTL Output Module111                             | LDO Module                                             |     |

| Class D – Electrical Characteristics112                  | LDO – Pin Definitions                                  |     |

| Class D – Typical Performance Characteristics112         | LDO - LDO_150 and LDO_050                              |     |

| Class D – Register Settings113                           | Specifications                                         |     |

| Class D – Audio Interface and Decode114                  | LDO – Typical Performance Characteristics              | 155 |

| Class D – Short Circuit Protection114                    | LDO - LDO_LP Electrical Specifications                 | 156 |

| Class D - Application114                                 | LDO – List of All LDOs                                 | 156 |

| ADC and TSC Module115                                    | LDO - Register Settings                                | 157 |

| ADC and TSC Module – Electrical Characteristics116       | EMBUP – Embedded Microcontroller Subsyste              |     |

| ADC and TSC Module – Pin Definitions116                  |                                                        |     |

| ADC and TSC Module – Operation117                        | EMBUP – Overview                                       | 162 |

| ADC and TSC Module – Registers119                        | EMBUP – Functional Description                         | 163 |

| PCON Module – Power Controller and General Purpose       | EMBUP - On-chip RAM and ROM                            | 163 |

| I/O131                                                   | EMBUP – I <sup>2</sup> C Slave Interface               | 163 |

| GPIO Pin Definitions131                                  | EMBUP – Peripherals                                    | 163 |

| Power States131                                          | EMBUP – Interrupt Controller                           | 164 |

| Power Sequencing by Embedded Microcontroller132          | Applications Information                               | 165 |

| Power On Reset Output (POR_OUT)132                       | External Components                                    | 165 |

| Power Switch Detector (SW_DET)132                        | Digital Logic Decoupling Capacitors                    | 165 |

| GPIO General Description132                              | Class D Considerations                                 | 165 |

| PCON Registers133                                        | Series Termination Resistors                           | 165 |

| Hotswap Module139                                        | I <sup>2</sup> C External Resistor Connection          | 165 |

| Hotswap – Electrical Characteristics140                  | Crystal Load Capacitors                                | 165 |

| Hotswap – Typical Performance Characteristics140         | PCB Layout Considerations                              | 165 |

| Hotswap – Pin Definitions141                             | Power Dissipation and Thermal Requiremen               |     |

| PCON Register – Hotswap Configuration141                 | Special Notes                                          | 166 |

| I <sup>2</sup> C / I <sup>2</sup> S Module142            | Package Outline Drawing                                |     |

| I <sup>2</sup> C / I <sup>2</sup> S – Pin Definitions142 | Ordering Guide                                         | 169 |

## **Revision History**

V1.0 February 2011 – Unreleased Final.

V1.1 June 2011 – Added ESD specifications.

V1.2 June 2011 - Updated ordering part numbers, released Final

V1.3 September 2011 - Improved Buck0,1,2 Regulators VIN Input Operating Voltage Range Maximum specification from 4.5V to 5.25V. Changed Trickle Current Accuracy from +/-10% to +/-15%. Bit 6 (labeled MSS) in Table 84 and 86 changed to Slave only. Added assembly notes for the NQG QFN-132 package.

## **ABSOLUTE MAXIMUM RATINGS**

Stresses above the ratings listed below can cause permanent damage to the IDTP95020. These ratings are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of

the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

**Table 1. Absolute Maximum Ratings**

| SYMBOL                                                                                                                                         | PARAMETER                                                               | MIN  | MAX                  | UNIT |

|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------|----------------------|------|

| CHRG_INPUT to CHRG_GND                                                                                                                         | USB or AC adaptor Charger Input<br>(Transient t < 1ms, Duty Cycle < 1%) | -0.3 | 7                    | ٧    |

| CHRG_BAT to DGND                                                                                                                               | Battery Input Source                                                    | -0.3 | 5.5                  | V    |

| CHRG_SYSVCC to DGND                                                                                                                            | System VCC Output (Vsys)                                                | -0.3 | 5.5                  | V    |

| PVDD to PGND                                                                                                                                   | CLASS_D BTL Input Power                                                 | -0.3 | 6                    | V    |

| LDO_IN1, IN2, IN3 to DGND                                                                                                                      | Input voltage for LDO                                                   | -0.3 | 6                    | V    |

| BUCK500_0_IN to BUCK500_0_GND                                                                                                                  | BUCK0 Input voltage                                                     | -0.3 | 6                    | V    |

| BUCK500 1 IN to BUCK500 1 GND                                                                                                                  | BUCK1 Input voltage                                                     | -0.3 | 6                    | V    |

| BUCK1000_IN to BUCK1000_GND                                                                                                                    | BUCK2 Input voltage                                                     | -0.3 | 6                    | V    |

| FDBK to DGND                                                                                                                                   | BUCK0, 1, 2 feedback voltage                                            | -0.3 | 6                    | V    |

| LED_BOOST_VIN to LED_BOOST_GND                                                                                                                 | LED_BOOST Converter gate bias supply                                    | -0.3 | 6                    | V    |

| LED_BOOST_GATE to LED_BOOST_GND                                                                                                                | LED BOOST Gate Drive to Power FET                                       | -0.3 | LED BOOST VIN + 0.3  | V    |

| LED_BOOST_VSENSE to LED_BOOST_GND                                                                                                              | Voltage Sense Input                                                     | -0.3 | LED BOOST VIN + 0.3  | V    |

| LED_BOOST_ISENSE to LED_BOOST_GND                                                                                                              | Current Sense Input                                                     | -0.3 | LED BOOST VIN + 0.3  | V    |

| LED_BOOST_SINK to LED_BOOST_GND                                                                                                                | Current Sink for LED String #1 or String #2                             | -0.3 | 6                    | V    |

| BOOST5_OUT to BOOST5_GND                                                                                                                       | BOOST5 Converter Output                                                 | -0.3 | 6                    | V    |

| BOOST5_SW to BOOST5_GND                                                                                                                        | BOOST5 Converter Power Switch1 and<br>Switch2                           | -0.3 | 6                    | V    |

| HSPWR to DGND                                                                                                                                  | Hot Swap Switches Power                                                 | -0.3 | 6                    | V    |

| HSCTRL1, HSCTRL2 to DGND                                                                                                                       | Input voltage for Hot Swap Control                                      | -0.3 | HSPWR + 0.3          | V    |

| VDDIO_CK to CKGEN_GND                                                                                                                          | Power Supply for TCXO_OUT1, TCXO_OUT2                                   | -0.3 | 2.5                  | V    |

| TCXO_IN to CKGEN_GND                                                                                                                           | Input voltage for TCXO_IN                                               | -0.3 | VDD CKGEN18 + 0.3    | V    |

| 32KHZ_CLKIN to CKGEN_GND                                                                                                                       | Input voltage for 32KHZ_CLK                                             | -0.3 | LDO LP + 0.3         | V    |

| GPIO to DGND                                                                                                                                   | Input voltage for GPIO                                                  | -0.3 | CHRG_SYSVCC + 0.3    | V    |

| SDA, SCL to DGND                                                                                                                               | Input voltage for I2C Master or Slave                                   | -0.3 | 6                    | V    |

| BCLK, WS, SDOUT, SDIN to DGND                                                                                                                  | Input voltage for I2S channel 1 or 2                                    | -0.3 | LDO 050 0 + 0.3      | V    |

| EX ROM to DGND                                                                                                                                 | External ROM enable                                                     | -0.3 | CHRG SYSVCC + 0.3    | V    |

| AGND, LDO_GND, CKGEN_GND, GND, PGND, BOOST5_GND, BCUCK500_0_GND, BCUCK500_1_GND, BUCK1000_GND, LED_BOOST_GND, CHRG_GND, GND_BAT/ADCGND to DGND |                                                                         | -0.3 | 0.3                  | V    |

| TJ                                                                                                                                             | Operating Junction Temperature                                          |      | -40 to +125          | °C   |

| Ts                                                                                                                                             | Storage Temperature                                                     |      | -40 to +150          | °C   |

| Tsolder                                                                                                                                        | Soldering Temperature                                                   |      | 260°C for 10 seconds | °C   |

|                                                                                                                                                | (HBM) Human Body Model<br>(all pins except A62, A63, B52, B53)          |      | ±1500                |      |

| ESD Rating                                                                                                                                     | (HBM) Human Body Model<br>(only pins A62, A63, B52, B53)                |      | ±450                 | V    |

|                                                                                                                                                | (CDM) Charged Device Model (all pins)                                   |      | ± 500                | 1    |

|                                                                                                                                                | (MM) Machine Model (all pins)                                           |      | $\pm200$             |      |

#### **ESD Warning**

The IDTP95020 is an ESD (electrostatic discharge) sensitive device. The human body and test equipment can accumulate and discharge electrostatic charges up to 4000 Volts without detection. Even though the

IDTP95020 implements internal ESD protection circuitry, proper ESD precautions should be followed to avoid damaging the functionality or performance.

## RECOMMENDED OPERATING CONDITIONS

Table 2. Recommended Operating Conditions<sup>1</sup>

| SYMBOL                                        | PARAMETER                                                                         | CONDITIONS                            | MIN  | TYP  | MAX  | UNIT |

|-----------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------|------|------|------|------|

| CHRG_INPUT                                    | USB or AC Adaptor Charger Input                                                   |                                       | 4.35 |      | 5.5  | V    |

| CHRG_BAT                                      | Battery Input Source                                                              | When V <sub>BAT</sub> providing power | 3.0  |      | 4.5  | V    |

| PVDD                                          | CLASS_D BTL Input Power Supply                                                    |                                       | 3.0  |      | 5.0  | V    |

| LDO_IN1, IN2, IN3                             | Input voltage for LDO                                                             |                                       | 3.0  |      | 5.5  | V    |

| BUCK500_0_IN,<br>BUCK500_1_IN,<br>BUCK1000_IN | BUCK0, 1, 2 Input voltage                                                         |                                       | 3.0  |      | 5.25 | V    |

| LED_BOOST_VIN                                 | LED Boost Converter gate bias supply                                              |                                       | 3.0  |      | 5.5  | V    |

| VDDIO_CK voltage                              | Power Supply for TCXO_OUT1, TCXO_OUT2                                             |                                       | 1.1  |      | 1.9  | V    |

| HSPWR                                         | Hot Swap Switches Power Supply                                                    | Do not tie to ground or floating      | 3.0  |      | 5.5  | V    |

| LDO_050_0                                     | Power Supply for I <sup>2</sup> C Slave Channel, I <sup>2</sup> S Channel 1 and 2 |                                       | 1.7  |      | 3.6  | V    |

| T <sub>A</sub>                                | Ambient Operating Temperature                                                     |                                       | 0    |      | 70   | °C   |

| TJ                                            | Operating Junction Temperature                                                    |                                       | -40  |      | 125  | °C   |

| $_{	extsf{JA}}$                               | Maximum Thermal Resistance                                                        | Junction to Ambient                   |      | 23.5 |      | °C/W |

| $\theta_{\sf JC}$                             | Maximum Thermal Resistance                                                        | Junction to Case                      |      | 7.6  |      | °C/W |

| $\theta_{JB}$                                 | Maximum Thermal Resistance                                                        | Junction to Board                     |      | 0.15 |      | °C/W |

| P <sub>D</sub>                                | Maximum Package Power Dissipation                                                 |                                       |      | 2.3  |      | W    |

Note 1 - Per JEDEC spec, the NQG QFN-132 package is rated at MSL3.

## POWER CONSUMPTION

## **Overall Power Consumption**

**Table 3. Overall Power Consumption**

| MODE                        | DESCRIPTION                                                                                                                                                                                                 | CHARGE_BAT              | TYPICAL CONSUMPTION  |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------|

| Sleep                       | USB or AC Adaptor is not present, a main battery is present and well-charged. Always on LDO_LP is on, RTC is on and RTC registers are maintained. Wake-up capabilities (Switch Detect Input) are available. | V <sub>BAT</sub> = 3.8V | 85 * 3.8 = 323 μW    |

| Standby                     | USB or AC Adaptor is not present, a main battery is present and well-charged. Always on LDO_LP is on, all DC-DC Bucks in PFM mode. All LDOs are on, no load.                                                | V <sub>BAT</sub> = 3.8V | 385 * 3.8 = 1463 μW  |

| Touch Controller<br>Standby | USB or AC Adaptor is not present, a main battery is present and well-charged. Always on LDO_LP is on, touch screen controller is on, LDO_050_0 is on.                                                       | V <sub>BAT</sub> = 3.8V | 7.4 * 3.8 = 28.12 mW |

## **Audio Power Consumption**

**Table 4. Audio Power Consumption**

|                                            | CHRG_BAT | LDO_050_0 | VDD_AUDIO18 | VDD_AUDIO33 | PVDD | CHRG_BAT | PVDD | TOTAL<br>POWER |

|--------------------------------------------|----------|-----------|-------------|-------------|------|----------|------|----------------|

| MODE                                       | (V)      | (V)       | (V)         | (V)         | (V)  | (mA)     | (mA) | (mW)           |

| Playback to 4Ω                             | 3.3      | 2.3       | 1.5         | 3.0         | 3.0  | 52       | 7    | 192            |

| speaker, sampling at 96                    | 3.8      | 3.3       | 1.8         | 3.3         | 3.3  | 60       | 7    | 252            |

| kHz, no signal                             | 4.2      | 3.6       | 1.8         | 3.6         | 5.0  | 60       | 10   | 302            |

| Playback to 4Ω                             | 3.3      | 2.3       | 1.5         | 3.0         | 3.0  | 53       | 155  | 640            |

| speaker, sampling at 96                    | 3.8      | 3.3       | 1.8         | 3.3         | 3.3  | 61       | 170  | 793            |

| kHz, 0dB FS 1 kHz<br>signal                | 4.2      | 3.6       | 1.8         | 3.6         | 5.0  | 61       | 258  | 1546           |

| Playback to 8Ω                             | 3.3      | 2.3       | 1.5         | 3.0         | 3.0  | 52       | 6    | 190            |

| speaker, sampling at 48                    | 3.8      | 3.3       | 1.8         | 3.3         | 3.3  | 59       | 6    | 244            |

| kHz, no signal                             | 4.2      | 3.6       | 1.8         | 3.6         | 5.0  | 59       | 10   | 298            |

| Playback to 8Ω                             | 3.3      | 2.3       | 1.5         | 3.0         | 3.0  | 52       | 96   | 460            |

| speaker, sampling at 48                    | 3.8      | 3.3       | 1.8         | 3.3         | 3.3  | 60       | 105  | 575            |

| kHz, 0dB FS 1 kHz<br>signal                | 4.2      | 3.6       | 1.8         | 3.6         | 5.0  | 60       | 163  | 1067           |

| Playback to 16Ω                            | 3.3      | 2.3       | 1.5         | 3.0         | 3.0  | 54       | 0    | 178            |

| headphone, sampling at                     | 3.8      | 3.3       | 1.8         | 3.3         | 3.3  | 58       | 0    | 220            |

| 96 kHz, no signal                          | 4.2      | 3.6       | 1.8         | 3.6         | 5.0  | 60       | 0    | 252            |

| Playback to 16Ω                            | 3.3      | 1.7       | 1.5         | 3.0         | 3.0  | 120      | 0    | 396            |

| headphone, sampling at                     | 3.8      | 3.3       | 1.8         | 3.3         | 3.3  | 133      | 0    | 506            |

| 96 kHz, 0dB FS 1 kHz<br>signal             | 4.2      | 3.6       | 1.8         | 3.6         | 5.0  | 135      | 0    | 567            |

| Playback to 16Ω cap-                       | 3.3      | 2.3       | 1.5         | 3.0         | 3.0  | 55       | 0    | 182            |

| less headphone,                            | 3.8      | 3.3       | 1.8         | 3.3         | 3.3  | 60       | 0    | 228            |

| sampling at 96 kHz, no signal              | 4.2      | 3.6       | 1.8         | 3.6         | 5.0  | 62       | 0    | 260            |

| Playback to 16Ω cap-                       | 3.3      | 2.3       | 1.5         | 3.0         | 3.0  | 122      | 0    | 403            |

| less headphone,                            | 3.8      | 3.3       | 1.8         | 3.3         | 3.3  | 135      | 0    | 513            |

| sampling at 96 kHz,<br>0dB FS 1 kHz signal | 4.2      | 3.6       | 1.8         | 3.6         | 5.0  | 137      | 0    | 576            |

| Stereo playback                            | 3.3      | 2.3       | 1.5         | 3.0         | 3.0  | 41       | 7    | 156            |

| bypassing ADC and                          | 3.8      | 3.3       | 1.8         | 3.3         | 3.3  | 48       | 7    | 206            |

| DAC to Class-D 4Ω speaker, no signal       | 4.2      | 3.6       | 1.8         | 3.6         | 5.0  | 48       | 10   | 252            |

| Record mode – Stereo                       | 3.3      | 2.3       | 1.5         | 3.0         | 3.0  | 45       | 0    | 149            |

| Line-In to ADC0                            | 3.8      | 3.3       | 1.8         | 3.3         | 3.3  | 49       | 0    | 186            |

| sampling at 96 kHz, no signal              | 4.2      | 3.6       | 1.8         | 3.6         | 5.0  | 50       | 0    | 210            |

| Record mode – Analog                       | 3.3      | 2.3       | 1.5         | 3.0         | 3.0  | 43       | 0    | 142            |

| microphone I/P to                          | 3.8      | 3.3       | 1.8         | 3.3         | 3.3  | 47       | 0    | 179            |

| ADC1 sampling at 16 kHz, no signal         | 4.2      | 3.6       | 1.8         | 3.6         | 5.0  | 47       | 0    | 198            |

| Record mode – Analog                       | 3.3      | 2.3       | 1.5         | 3.0         | 3.0  | 45       | 0    | 149            |

| microphone I/P to                          | 3.8      | 3.3       | 1.8         | 3.3         | 3.3  | 49       | 0    | 186            |

| ADC1 sampling at 96 kHz, no signal         | 4.2      | 3.6       | 1.8         | 3.6         | 5.0  | 50       | 0    | 210            |

## DIGITAL INTERFACES ELECTRICAL CHARACTERISTICS

Unless otherwise specified, typical values at T<sub>A</sub> = 25°C, V<sub>SYS</sub> = 3.8V, V<sub>LD0 LP</sub>=3.3V, T<sub>A</sub> = 0°C to +70°C

#### I<sup>2</sup>C Master Electrical Characteristics

Table 5. I<sup>2</sup>C Master Electrical Specifications

| SYMBOL          | PARAMETER                       | CONDITIONS | MIN                      | TYP | MAX                      | UNIT |

|-----------------|---------------------------------|------------|--------------------------|-----|--------------------------|------|

| V <sub>IH</sub> | Input High Voltage              |            | 0.7x V <sub>LD0_LP</sub> |     |                          | V    |

| V <sub>IL</sub> | Input Low Voltage               |            | -0.3                     |     | 0.3x V <sub>LD0_LP</sub> | V    |

| V <sub>OL</sub> | Output Low Voltage (Open Drain) | IOL = 3 mA |                          |     | 0.4                      | V    |

#### I<sup>2</sup>C Slave Electrical Characteristics

Table 6. I<sup>2</sup>C Slave Electrical Specifications

| SYMBOL                 | PARAMETER          | CONDITIONS  | MIN                         | TYP | MAX                         | UNIT |

|------------------------|--------------------|-------------|-----------------------------|-----|-----------------------------|------|

| V <sub>LDO_050_0</sub> | Input Power Supply |             | 1.7                         |     | 3.6                         | V    |

| VIH                    | Input High Voltage |             | 0.7x V <sub>LDO_050_0</sub> |     |                             | V    |

| VIL                    | Input Low Voltage  |             | -0.3                        |     | 0.3x V <sub>LDO_050_0</sub> | V    |

| V <sub>OL</sub>        | Output Low Voltage | IOL = +3 mA |                             |     | 0.4                         | V    |

#### I<sup>2</sup>S Electrical Characteristics

Table 7. I2S Electrical Specifications

| SYMBOL                 | PARAMETER           | CONDITIONS                                                | MIN                          | TYP | MAX                         | UNIT |

|------------------------|---------------------|-----------------------------------------------------------|------------------------------|-----|-----------------------------|------|

| V <sub>LDO_050_0</sub> | Input Power Supply  |                                                           | 1.7                          |     | 3.6                         | V    |

| VIH                    | Input High Voltage  |                                                           | 0.7x V <sub>LDO_050_0</sub>  |     | V <sub>SYS</sub> + 0.3      | V    |

| V <sub>IL</sub>        | Input Low Voltage   |                                                           | -0.3                         |     | 0.3x V <sub>LDO_050_0</sub> | V    |

| V <sub>OH</sub>        | Output High Voltage | $I_{OH} = -1 \text{mA}, \ V_{LDO\_050\_0} = 3.3 \text{V}$ | 0.9x V <sub>LDO_050_0</sub>  |     |                             | V    |

|                        |                     | $I_{OH} = -1 \text{mA}, \ V_{LDO\_050\_0} = 2.5 \text{V}$ | 0.9x V <sub>LDO_050_0</sub>  |     |                             | V    |

|                        |                     | I <sub>OH</sub> = -100uA, V <sub>LDO_050_0</sub> = 1.8V   | V <sub>LDO_050_0</sub> - 0.2 |     |                             | V    |

| VoL                    | Output Low Voltage  | I <sub>OL</sub> = 1mA                                     |                              |     | 0.1x V <sub>LDO_050_0</sub> | V    |

#### **GPIO Electrical Characteristics**

**Table 8. GPIO Electrical Specifications**

| SYMBOL          | PARAMETER           | CONDITIONS             | MIN                      | TYP | MAX                      | UNIT |

|-----------------|---------------------|------------------------|--------------------------|-----|--------------------------|------|

| VIH             | Input High Voltage  |                        | 0.7x V <sub>LD0_LP</sub> |     | V <sub>SYS</sub> + 0.3   | V    |

| V <sub>IL</sub> | Input Low Voltage   |                        | -0.3                     |     | 0.3x V <sub>LD0_LP</sub> | V    |

| Vон             | Output High Voltage | I <sub>OH</sub> = -2mA | 0.9x V <sub>SYS</sub>    |     |                          | V    |

| Vol             | Output Low Voltage  | I <sub>OL</sub> = 2mA  |                          |     | 0.1x V <sub>SYS</sub>    | V    |

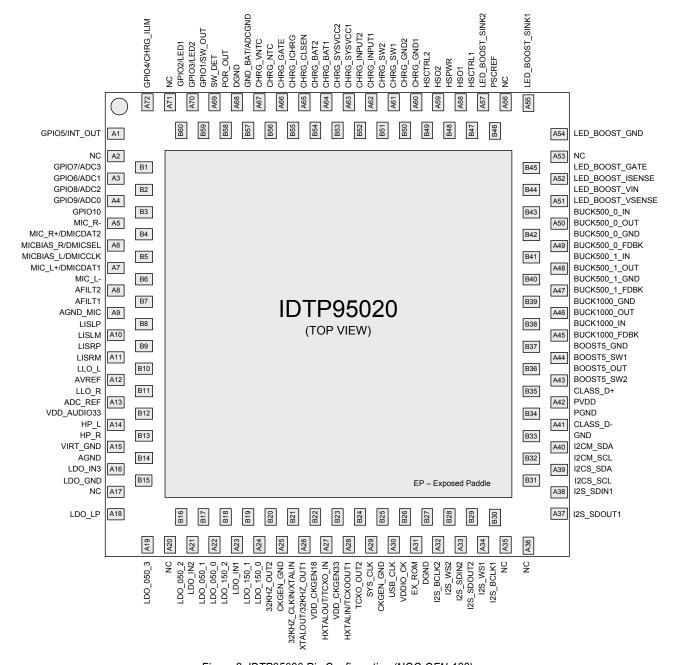

## PIN CONFIGURATION AND DESCRIPTION

Figure 2. IDTP95020 Pin Configuration (NGQ QFN-132)

NOTE: All the Buck Converter inputs (BUCK500\_0\_IN, BUCK500\_1\_IN, BUCK1000\_IN) must be connected to CHRG\_SYSVCC1 and CHRG\_SYSVCC2.

**IDTP95020**

Table 9 - NQG132 Pin Functions by Pin Number (see Figure 2)

| MODULE     | PIN# | PIN NAME           | DESCRIPTION                                                                | I/O TYPE |

|------------|------|--------------------|----------------------------------------------------------------------------|----------|

| GPIO_TSC   | A1   | GPIO5/INT_OUT      | GPIO 5: General Purpose I/O # 5                                            | GPIO     |

| (Also, see |      |                    | INT_OUT : Interrupt Output                                                 | 1        |

| pins       | A2   | NC                 | No Connect                                                                 | NC       |

| B57 – A71) | B1   | GPIO7/ADC3         | GPIO 7: General Purpose I/O # 7                                            | GPIO     |

|            |      |                    | ADC3: Auxiliary Input Channel 4 / Y- pin to 4 wire resistive touch screen  | 1        |

|            | А3   | GPIO6/ADC1         | GPIO 6: General Purpose I/O # 6                                            | GPIO     |

|            |      |                    | ADC1 : Auxiliary Input Channel 2 / X- pin to 4-wire resistive touch screen | 1        |

|            | B2   | GPIO8/ADC2         | GPIO 8: General Purpose I/O # 8                                            | GPIO     |

|            |      |                    | ADC2 : Auxiliary Input Channel 3 / Y+ pin to 4-wire resistive touch        | 1        |

|            |      |                    | screen                                                                     |          |

|            | A4   | GPIO9/ADC0/MCLK_IN | GPIO 9: General Purpose I/O # 9                                            | GPIO     |

|            |      |                    | ADC0 : Auxiliary Input Channel 1 / X+ pin to 4-wire resistive touch        | 1        |

|            |      |                    | screen                                                                     |          |

|            |      |                    | MCLK_IN : Master Clock Input                                               |          |

|            | В3   | GPIO10             | GPIO 10: General Purpose I/O # 10                                          | GPIO     |

| AUDIO      | A5   | MIC_R-             | MIC_R-: Analog Microphone Differential Stereo Right Inverting Input        | A-I      |

|            | B4   | MIC_R+/DMICDAT2    | MIC_R+: Analog Microphone Differential Stereo Right Non-Inverting          | A-I      |

|            |      |                    | Input                                                                      |          |

|            |      |                    | DMICDAT2: Digital Microphone 2 Data Input                                  | D-I      |

|            | A6   | MICBIAS_R/DMICSEL  | MICBIAS : Microphone Right Bias                                            | A-O      |

|            |      |                    | DMICSEL : Digital Microphone Select (Common to both inputs)                | D-O      |

|            | B5   | MICBIAS_L/DMICCLK  | MICBIAS : Microphone Left Bias                                             | A-O      |

|            |      |                    | DMICCLK : Digital Microphone Clock (Common to both inputs)                 | D-O      |

|            | A7   | MIC_L+/DMICDAT1    | MIC_L+ : Analog Microphone Differential Stereo Left Non-Inverting Input    | A-I      |

|            |      |                    | DMICDAT1 : Digital Microphone 1 Data Input                                 | D-I      |

|            | B6   | MIC_L-             | MIC_L- : Analog Microphone Differential Stereo Left Inverting Input        | A-I      |

|            | A8   | AFILT2             | Microphone ADC Anti-Aliasing Filter Capacitor #2                           | A-I      |

|            | B7   | AFILT1             | Microphone ADC Anti-Aliasing Filter Capacitor #1                           | A-I      |

|            | A9   | AGND MIC           | Microphone Ground (Analog Ground)                                          | GND      |

|            | B8   | LISLP              | Line Input Stereo Left Non-Inverting                                       | A-I      |

|            | A10  | LISLM              | Line Input Stereo Left Inverting                                           | A-I      |

|            | В9   | LISRP              | Line Input Stereo Right Non-Inverting                                      | A-I      |

|            | A11  | LISRM              | Line Input Stereo Right Inverting                                          | A-I      |

|            | B10  | LLO_L              | Line Level Output, Left                                                    | A-O      |

|            | A12  | AVREF              | Analog Reference                                                           | A-O      |

|            | B11  | LLO_R              | Line Level Output, Right                                                   | A-O      |

|            | A13  | ADC_REF            | ADC Reference Bypass Capacitor                                             | A-I      |

|            | B12  | VDD AUDIO33        | Filter Capacitor for Internal 3.3V AUDIO LDO                               | A-O      |

|            | A14  | HP L               | Left Headphone Output                                                      | A-O      |

|            | B13  | HP R               | Right Headphone Output                                                     | A-O      |

|            | A15  | VIRT_GND           | Virtual Ground for Cap-Less Output                                         | A-O      |

|            | B14  | AGND               | Analog Ground                                                              | GND      |

| MODULE | PIN# | PIN NAME           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                            | I/O TYPE |

|--------|------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| LDO    | A16  | LDO_IN3            | Input Voltage to LDOs for AUDIO Power (VDD_AUDIO33 and VDD_AUDIO18)                                                                                                                                                                                                                                                                                                    | AP-I     |

|        | B15  | LDO_GND            | LDO Ground                                                                                                                                                                                                                                                                                                                                                             | GND      |

|        | A17  | NC                 | No Connect                                                                                                                                                                                                                                                                                                                                                             | NC       |

|        | A18  | LDO_LP             | Always on Low Power LDO Output (Voltage Programmable to 3.0 V or 3.3 V)                                                                                                                                                                                                                                                                                                | AP-O     |

|        | A19  | LDO_050_3          | 50mA LDO Output #3 (Voltage Range: 0.75-3.7 V)                                                                                                                                                                                                                                                                                                                         | AP-O     |

|        | A20  | NC                 | No Connect                                                                                                                                                                                                                                                                                                                                                             | NC       |

|        | B16  | LDO 050 2          | 50mA LDO Output #2 (Voltage Range: 0.75-3.7 V)                                                                                                                                                                                                                                                                                                                         | AP-O     |

|        | A21  | LDO_IN2            | Input Voltage to LDO_050_0, LDO_050_1, LDO_050_2 and LDO_050_3                                                                                                                                                                                                                                                                                                         | AP-I     |

|        | B17  | LDO 050 1          | 50mA LDO Output #1 (Voltage Range: 0.75-3.7 V)                                                                                                                                                                                                                                                                                                                         | AP-O     |

|        | A22  | LDO_050_0          | 50mA LDO Output #0 (Voltage Range: 0.75-3.7 V)  Note: This LDO also serves as the internal power source for I <sup>2</sup> S1, I <sup>2</sup> S2 and I <sup>2</sup> CS. The external function of this pin is not affected but the voltage register setting for this LDO will also govern the I/O level for I <sup>2</sup> S1, I <sup>2</sup> S2 and I <sup>2</sup> CS. | AP-O     |

|        | B18  | LDO 150 2          | 150mA LDO Output #2 (Voltage Range: 0.75-3.7 V)                                                                                                                                                                                                                                                                                                                        | AP-O     |

|        | A23  | LDO IN1            | Input Voltage to LDO_150_0, LDO_150_1 and LDO_150_2                                                                                                                                                                                                                                                                                                                    | AP-I     |

|        | B19  | LDO 150 1          | 150mA LDO Output #1 (Voltage Range: 0.75-3.7 V)                                                                                                                                                                                                                                                                                                                        | AP-O     |

|        | A24  | LDO_150_0          | 150mA LDO Output #0 (Voltage Range: 0.75-3.7 V)                                                                                                                                                                                                                                                                                                                        | AP-O     |

|        | B20  | 32KHZ OUT2         | Buffered 32.768kHz Output #2                                                                                                                                                                                                                                                                                                                                           | D-O      |

|        | A25  | CKGEN GND          | PLL Analog Ground                                                                                                                                                                                                                                                                                                                                                      | GND      |

|        | B21  | 32KHZ_CLKIN/XTALIN | 32KHZ_CLKIN: External 32.768kHz Clock Input;  XTALIN: Input Pin when used with an external crystal                                                                                                                                                                                                                                                                     | A-I      |

|        | A26  | XTALOUT/32KHZ_OUT1 | XTALOUT: Output Pin when used with an external crystal  32KHZ_OUT1: when XTALIN is connected to a 32kHz input this pin can be a 32kHz Output when CKGEN_PLL_STATUS register, 32KOUT1_EN (bit 4) is set to 1.                                                                                                                                                           | A-O      |

|        | B22  | VDD_CKGEN18        | Filter Capacitor for Internal 1.8V CKGEN LDO                                                                                                                                                                                                                                                                                                                           | A-IO     |

|        | A27  | HXTALOUT/TCXO_IN   | HXTALOUT: 12 MHz, 13 MHz, 19.2 MHz or 26 MHz output TCXO_IN: External 12 MHz, 13 MHz, 19.2 MHz or 26 MHz clock input                                                                                                                                                                                                                                                   | TCXO-D-I |

|        | B23  | VDD CKGEN33        | Filter Capacitor for Internal 3.3V CKGEN LDO                                                                                                                                                                                                                                                                                                                           | A-IO     |

|        | A28  | HXTALIN/TCXO_OUT1  | HXTALIN: 12 MHz, 13 MHz, 19.2 MHz, or 26 MHz crystal oscillator input TCXO_OUT1: Buffered HXTALOUT/TCXO_IN Clock Output #1, 32.7638 KHz Output or 24 MHz PLL Output                                                                                                                                                                                                    | TCXO-D-O |

|        | B24  | TCXO_OUT2          | Buffered HXTALOUT/TXCO_IN Clock Output #2, 12 MHz PLL Output or 48 MHz PLL Output                                                                                                                                                                                                                                                                                      | TCXO-D-O |

|        | A29  | SYS_CLK            | 12MHz Output or Buffered Output of TCXO_IN                                                                                                                                                                                                                                                                                                                             | D-O      |

|        | B25  | CKGEN_GND          | PLL Analog Ground                                                                                                                                                                                                                                                                                                                                                      | GND      |

|        | A30  | USB_CLK            | 24 MHz or 48 MHz Output                                                                                                                                                                                                                                                                                                                                                | D-O      |

|        | B26  | VDDIO CK           | Power Supply Input for TCXO_OUT1 and TCXO_OUT2 (1.1V – 1.9V)                                                                                                                                                                                                                                                                                                           | AP-I     |

## **IDTP95020**

| MODULE PIN# PIN NAME DESCRIPTION |            |                                 | DESCRIPTION                                                                                                                   | I/O TYPE              |  |

|----------------------------------|------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|

| 2C_I2S                           | A31        | EX_ROM                          | ROM Select. EX_ROM = 1, read contents of external ROM. EX_ROM = 0, read contents of internal ROM into internal shadow memory. | D-I                   |  |

|                                  | B27        | DGND                            | Digital Ground (1)                                                                                                            | GND                   |  |

|                                  | A32        | I2S_BCLK2                       | I <sup>2</sup> S Bit Clock Channel 2                                                                                          | D-I                   |  |

|                                  | B28        | I2S WS2                         | I2S Word Select (Left/Right) Channel 2                                                                                        | D-I                   |  |

|                                  | A33        | I2S SDIN2                       | I <sup>2</sup> S Serial Data IN Channel 2                                                                                     | D-I                   |  |

|                                  | B29        | I2S_SDOUT2                      | I <sup>2</sup> S Serial Data OUT Channel 2                                                                                    | D-O                   |  |

|                                  | A34        | I2S_WS1                         | I2S Word Select (Left/Right) Channel 1                                                                                        | D-I                   |  |

|                                  | B30        | I2S BCLK1                       | I2S Bit Clock Channel 1                                                                                                       | D-I                   |  |

|                                  | A35        | NC NC                           | No Connect                                                                                                                    | NC                    |  |

|                                  | A36        | NC                              | No Connect                                                                                                                    | NC                    |  |

|                                  | A37        | I2S_SDOUT1                      | I <sup>2</sup> S Serial Data OUT Channel 1                                                                                    | D-O                   |  |

|                                  | A38        | I2S SDIN1                       | I <sup>2</sup> S Serial Data IN Channel 1                                                                                     | D-I                   |  |

|                                  | B31        | I2CS_SCL                        | I <sup>2</sup> C Slave clock                                                                                                  | I <sup>2</sup> C -I/O |  |

|                                  | A39        | I2CS SDA                        | I <sup>2</sup> C Slave data                                                                                                   | I <sup>2</sup> C -O   |  |

|                                  | B32        | I2CM SCL                        | I <sup>2</sup> C Master clock                                                                                                 | I <sup>2</sup> C -O   |  |

|                                  | A40        | I2CM_SDA                        | I <sup>2</sup> C Master data                                                                                                  | I <sup>2</sup> C -I/O |  |

|                                  | B33        | GND                             | GND : Ground                                                                                                                  | GND                   |  |

| LASS_D                           | A41        | CLASS D-                        | Class-D Inverting Output                                                                                                      | A-O                   |  |

| _A00_D                           | B34        | PGND                            | Ground for Class D BTL Power Stage                                                                                            | GND                   |  |

|                                  | A42        | PVDD                            | Input Power for CLASS_D BTL Power Stage                                                                                       | A-I                   |  |

|                                  | B35        | CLASS D+                        | Class-D Non-Inverting Output                                                                                                  | A-O                   |  |

| C_DC                             | A43        | BOOST5_SW2                      | BOOST5 Converter Power Switch                                                                                                 | AP-O                  |  |

| טע_טע                            | 740        | D00013_0W2                      | Internally connected to pin A44 (BOOST_SW1)                                                                                   | AI -0                 |  |

|                                  | B36        | BOOST5_OUT                      | BOOST5 Converter Output                                                                                                       | AP-O                  |  |

|                                  | A44        | BOOST5 SW1                      | BOOST5 Converter Power Switch                                                                                                 | AP-O                  |  |

|                                  | /\++       | B00013_0W1                      | Internally connected to pin A43 (BOOST_SW2)                                                                                   | AI -0                 |  |

|                                  | B37        | BOOST5_GND                      | Ground for BOOST5 Power Supply                                                                                                | AP-I                  |  |

|                                  | A45        | BUCK1000 FDBK                   | BUCK2 Converter #2 - Feedback                                                                                                 | AP-I                  |  |

|                                  | B38        | BUCK1000_I DBK                  | BUCK2 Converter #2 - Input                                                                                                    | AP-I                  |  |

|                                  | A46        | BUCK1000_IN                     | BUCK2 Converter Output #2 – 1000mA                                                                                            | AP-0                  |  |

|                                  | B39        | BUCK1000_GND                    | Ground for BUCK2 Converter #2                                                                                                 | GND                   |  |

|                                  | A47        |                                 | BUCK1 Converter #1 – Feedback                                                                                                 | AP-I                  |  |

|                                  | B40        | BUCK500_1_FDBK<br>BUCK500 1 GND | Ground for BUCK1 Converter #1                                                                                                 | GND                   |  |

|                                  |            | BUCK500_1_GND                   |                                                                                                                               |                       |  |

|                                  | A48<br>B41 |                                 | BUCK1 Converter #1 Input                                                                                                      | AP-O                  |  |

|                                  |            | BUCK500_1_IN<br>BUCK500 0 FDBK  | BUCK1 Converter #1 Input BUCK0 Converter #0 feedback                                                                          | AP-I                  |  |

|                                  | A49        |                                 |                                                                                                                               | AP-I                  |  |

|                                  | B42        | BUCK500_0_GND<br>BUCK500 0 OUT  | Ground for BUCK0 Converter #0                                                                                                 | GND<br>AP-O           |  |

|                                  | A50<br>B43 |                                 | BUCK0 Converter #0 Input                                                                                                      |                       |  |

|                                  |            | BUCK500_0_IN                    | BUCK0 Converter #0 Input                                                                                                      | AP-I                  |  |

|                                  | A51        | LED_BOOST_VSENSE                | LED_BOOST Converter Output Voltage Sense Input to PWM Controller                                                              | AP-I                  |  |

|                                  | B44        | LED_BOOST_VIN                   | LED_BOOST Converter GATE BIAS Supply                                                                                          | AP-I                  |  |

|                                  | A52        | LED_BOOST_ISENSE                | LED_BOOST Converter Output Current Sense Input to PWM Controller                                                              | AP-I                  |  |

|                                  | B45        | LED_BOOST_GATE                  | LED_BOOST Converter GATE Drive to Power FET                                                                                   | AP-I                  |  |

|                                  | A53        | NC                              | No Connect                                                                                                                    | NC                    |  |

|                                  | A54        | LED_BOOST_GND                   | Ground for LED_BOOST                                                                                                          | AP-I                  |  |

|                                  | A55        | LED_BOOST_SINK1                 | LED_BOOST Converter Current Sink for LED String #1                                                                            | AP-I                  |  |

|                                  | A56        | NC                              | No Connect                                                                                                                    | NC<br>AB C            |  |

|                                  | B46        | PSCREF                          | Power Supply Current Reference                                                                                                | AP-O                  |  |

| MODULE   | PIN#  | PIN NAME                 | DESCRIPTION                                                                                                                                                                                                                  | I/O TYPE |

|----------|-------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| HOTSWAP  | B47   | HSCTRL1                  | Hot Swap Control Input 1                                                                                                                                                                                                     | D-I      |

|          | A58   | HSO1                     | Hot Swap Output 1                                                                                                                                                                                                            | A-O      |

|          | B48   | HSPWR                    | Hot Swap Switches Power Input                                                                                                                                                                                                | AP-I     |

|          | A59   | HSO2                     | Hot Swap Output 2                                                                                                                                                                                                            | A-O      |

|          | B49   | HSCTRL2                  | Hot Swap Control Input 2                                                                                                                                                                                                     | D-I      |

| CHARGER  | A60   | CHRG_GND1                | Pins A60 and B50 are the Power GND Pins for the Switching Regulator                                                                                                                                                          | A-I      |

|          | B50   | CHRG_GND2                | in the Charger. Due to their higher current requirement they are internally tied together and must be connected externally at the PC board also.                                                                             | A-I      |

|          | A61   | CHRG_SW1                 | Pins A61 and B51connect to the inductor of the switch-mode step-down                                                                                                                                                         | A-O      |

|          | B51   | CHRG_SW2                 | regulator for the Battery Charger. Due to their higher current requirement they are internally tied together and must be connected externally at the PC board also.                                                          | A-O      |

|          | A62   | CHRG_INPUT1              | Pins A62 and B52 provide 5V V <sub>BUS</sub> Input Power from the USB or from an                                                                                                                                             | AP-I     |

|          | B52   | CHRG_INPUT2              | external AC adaptor supply. Due to the pins higher current requirement, they are internally tied together and must be connected externally at the PC board also.                                                             | AP-I     |

|          | A63   | CHRG_SYSVCC1             | Pins A63 and B53 are System VCC Output (V <sub>SYS</sub> ). Due to their higher                                                                                                                                              | A-O      |

|          | B53   | CHRG_SYSVCC2             | current requirement they are internally tied together and must be connected externally at the PC board also.                                                                                                                 | A-O      |

|          | A64   | CHRG_BAT1                | Pins A64 and B64 form the positive battery lead connection to a single cell                                                                                                                                                  | AP-I/O   |

|          | B54   | CHRG_BAT2                | Li-lon/Li-Poly battery. Due to their higher current requirement they are internally tied together and must be connected externally at the PC board also.                                                                     | AP-I/O   |

|          | A65   | CHRG_CLSEN               | Input Current Limit Sense/filtering pin for current limit detection                                                                                                                                                          | A-I      |

|          | B55   | CHRG_ICHRG               | Current setting. Connect to a current sense resistor                                                                                                                                                                         | AP-I/O   |

|          | A66   | CHRG_GATE                | Gate Drive for (Optional) External Ideal Diode                                                                                                                                                                               | A-O      |