Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **PCA2002**

# 32 kHz watch circuit with programmable output period and pulse width

Rev. 8 — 25 November 2011

**Product data sheet**

### 1. General description

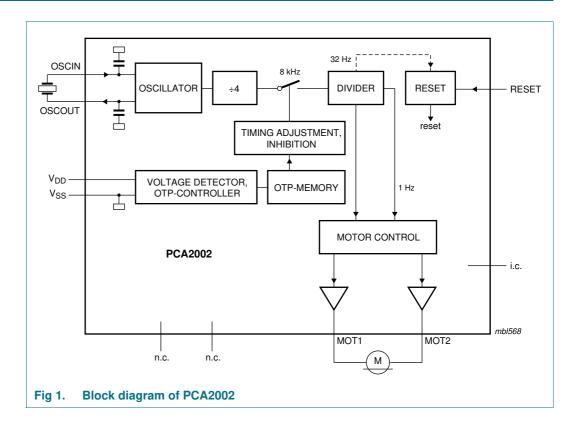

The PCA2002 is a CMOS¹ integrated circuit for battery operated wrist watches with a 32 kHz quartz crystal as the timing element and a bipolar stepping motor. The quartz crystal oscillator and the frequency divider are optimized for minimum current consumption. A timing accuracy of 1 ppm is achieved with a programmable, digital frequency adjustment.

The output period and the output pulse width can be programmed. It can be selected between a full output pulse or a chopped output pulse with a duty cycle of 75 %. In addition, a stretching pulse can be added to the primary driving pulse.

A pad RESET is provided (used for stopping the motor) for accurate time setting and for accelerated testing of the watch.

### 2. Features and benefits

- Amplitude-regulated 32 kHz quartz crystal oscillator, with excellent frequency stability and high immunity to leakage currents

- Electrically programmable time calibration with 1 ppm resolution stored in One Time Programmable (OTP) memory

- The quartz crystal is the only external component required

- Very low current consumption: typically 90 nA

- Output pulses for bipolar stepping motors

- Five different programmable output periods (1 s to 30 s)

- Output pulse width programmable between 1 ms and 8 ms

- Full or chopped motor pulse and pulse stretching, selectable

- Stop function for accurate time setting and current saving during shelf life

- Test mode for accelerated testing of the mechanical parts of the watch

- Test bits for type recognition

# 3. Applications

- Driver circuits for bipolar stepping motors

- High immunity motor drive circuits

- High production volumes

<sup>1.</sup> The definition of the abbreviations and acronyms used in this data sheet can be found in Section 15.

### 32 kHz watch circuit with programmable output period and pulse width

# 4. Ordering information

Table 1. Ordering information

| Type number     | Package          |                                                     |                                                                                                    |           |  |  |  |  |

|-----------------|------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------|--|--|--|--|

|                 | Name             | Description                                         | Delivery form                                                                                      | Version   |  |  |  |  |

| PCA2002U/AB/1   | wire bond<br>die | 8 bonding pads;<br>1.16 × 0.86 × 0.22 mm            | bare die; chip in tray                                                                             | PCA200xU  |  |  |  |  |

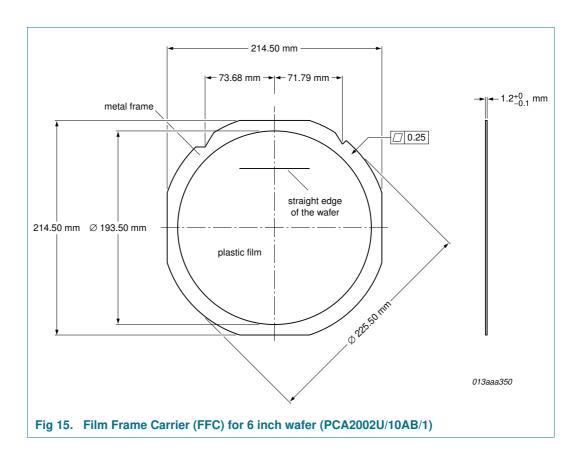

| PCA2002U/10AB/1 | wire bond<br>die | 8 bonding pads; 1.16 $\times$ 0.86 $\times$ 0.22 mm | sawn wafer on Film Frame<br>Carrier (FFC), see Figure 15 on<br>page 22                             | PCA200xU  |  |  |  |  |

| PCA2002CX8/5/1  | WLCSP8           | wafer level chip-size package;<br>8 bumps           | unsawn wafer with lead free solder bumps                                                           | PCA200xCX |  |  |  |  |

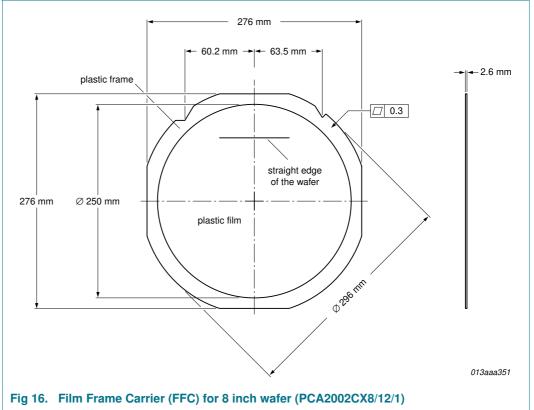

| PCA2002CX8/12/1 | WLCSP8           | wafer level chip-size package;<br>8 bumps           | sawn wafer with lead free solder<br>bumps on Film Frame Carrier (FFC),<br>see Figure 16 on page 22 | PCA200xCX |  |  |  |  |

# 5. Marking

Table 2. Marking codes

| Table 2. Marking codes |              |

|------------------------|--------------|

| Type number            | Marking code |

| PCA2002U/AB/1          | PC<br>2002-1 |

| PCA2002U/10AB/1        | PC<br>2002-1 |

| PCA2002CX8/5/1         | PC<br>2002-1 |

| PCA2002CX8/12/1        | PC<br>2002-1 |

### 32 kHz watch circuit with programmable output period and pulse width

# 6. Block diagram

### 32 kHz watch circuit with programmable output period and pulse width

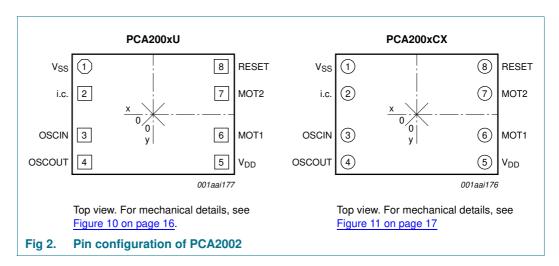

# 7. Pinning information

### 7.1 Pinning

### 7.2 Pin description

Table 3. Pin description

| Symbol   | Pin | Description          |

|----------|-----|----------------------|

| $V_{SS}$ | 1   | ground               |

| i.c.     | 2   | internally connected |

| OSCIN    | 3   | oscillator input     |

| OSCOUT   | 4   | oscillator output    |

| $V_{DD}$ | 5   | supply voltage       |

| MOT1     | 6   | motor 1 output       |

| MOT2     | 7   | motor 2 output       |

| RESET    | 8   | reset input          |

32 kHz watch circuit with programmable output period and pulse width

# 8. Functional description

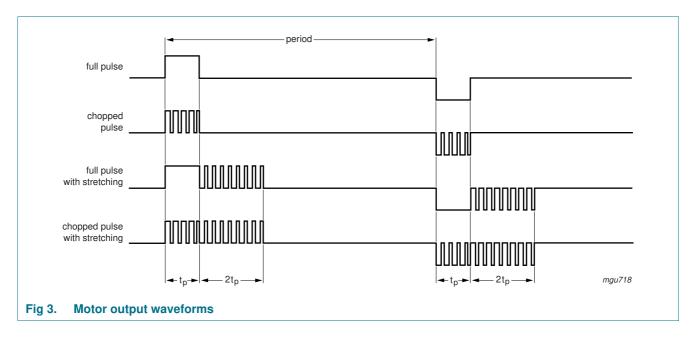

#### 8.1 Motor pulse

The motor driver delivers pulses with an alternating polarity. The output waveform across the motor terminals is illustrated in <u>Figure 3</u>. Between the motor pulses, both terminals are connected to  $V_{DD}$ , which means that the motor is short-circuit.

The following parameters can be selected and are stored in a One Time Programmable (OTP) memory:

- Output periods of 1 s, 5 s, 10 s, 20 s and 30 s

- Pulse width (t<sub>p</sub>) between 0.98 ms and 7.8 ms in steps of 0.98 ms

- Full or chopped (75 %) output pulse

- Pulse stretching: an enlargement pulse is added to the primary motor pulse. This

enlargement pulse has a duty cycle of 25 % and a width, which is twice the

programmed motor pulse width.

#### 8.2 Time calibration

The quartz crystal oscillator has an integrated capacitance of 5.2 pF, which is lower than the specified capacitance ( $C_L$ ) of 8.2 pF for the quartz crystal (see <u>Table 10</u>). Therefore, the oscillator frequency is typically 60 ppm higher than 32.768 kHz. This positive frequency offset is compensated by removing the appropriate number of 8192 Hz pulses in the divider chain (maximum 127 pulses), every 1 or 2 minutes. The time correction is given in <u>Table 4</u>.

#### 32 kHz watch circuit with programmable output period and pulse width

Table 4. Time calibration

| Calibration period | Correction per ste | ep (n = 1)      | Correction per step (n = 127) |                 |  |

|--------------------|--------------------|-----------------|-------------------------------|-----------------|--|

|                    | ppm                | seconds per day | ppm                           | seconds per day |  |

| 1 minute           | 2.03               | 0.176           | 258                           | 22.3            |  |

| 2 minutes          | 1.017              | 0.088           | 129                           | 11.15           |  |

After measuring the effective oscillator frequency, the number of correction pulses must be calculated and stored together with the calibration period in the OTP memory (see Section 8.6).

The oscillator frequency can be measured at pad RESET, where a square wave signal with the frequency of  $\frac{I}{1024} \times f_{osc}$  is provided.

This frequency shows a jitter every minute or every two minutes, depending on the programmed calibration period, which originates from the time calibration.

Details on how to measure the oscillator frequency and the programmed inhibition time are given in Section 8.10.

#### 8.3 Reset

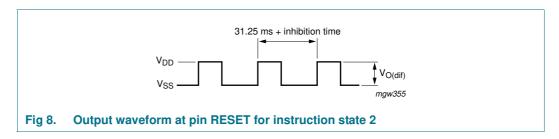

At pin RESET an output signal with a frequency of  $\frac{1}{1024} \times f_{osc} = 32Hz$  is provided.

Connecting pin RESET to V<sub>DD</sub> stops the motor drive and opens the motor switches.

After releasing pin RESET, the first motor pulse is generated exactly one period later with the opposite polarity to the last pulse before stopping. The debounce time for the reset function is between 31 ms and 62 ms.

Connecting pin RESET to  $V_{SS}$  activates the test mode. In this mode the motor output frequency is 32 Hz, which can be used to test the mechanical function of the watch.

### 8.4 Programming possibilities

The programming data is organized in an array of 8-bit words (see <u>Table 5</u>): Word A contains the time calibration, word B the setting for the monitor pulses, word C is not used and word D contains the type recognition.

Table 5. Words and bits

| Word | Bit                                                      |   |   |               |   |   |               |                     |  |

|------|----------------------------------------------------------|---|---|---------------|---|---|---------------|---------------------|--|

|      | 1                                                        | 2 | 3 | 4             | 5 | 6 | 7             | 8                   |  |

| Α    | number of 8192 Hz pulses to be removed calibrated period |   |   |               |   |   |               |                     |  |

| В    | pulse width                                              |   |   | output period |   |   | duty<br>cycle | pulse<br>stretching |  |

| С    |                                                          |   |   |               |   |   |               |                     |  |

| D    | type factory test bit                                    |   |   |               |   |   |               |                     |  |

#### 32 kHz watch circuit with programmable output period and pulse width

Table 6. Description of word A bits

| Bit                | Value | Description                                                                                  |

|--------------------|-------|----------------------------------------------------------------------------------------------|

| Inhibit time       |       |                                                                                              |

| 1 to 7             | -     | adjust the number of the 8192 Hz pulses to be removed; bit 1 is the MSB and bit 7 is the LSB |

| Calibration period | ı     |                                                                                              |

| 8                  | 0     | 1 minute                                                                                     |

|                    | 1     | 2 minutes                                                                                    |

Table 7. Description of word B bits

|                               | ption of word b bit |                                                                                |

|-------------------------------|---------------------|--------------------------------------------------------------------------------|

| Bit                           | Value               | Description                                                                    |

| Pulse width t <sub>p</sub> (m | s)                  |                                                                                |

| 1 to 3                        | 000                 | 0.98                                                                           |

|                               | 001                 | 1.95                                                                           |

|                               | 010                 | 2.9                                                                            |

|                               | 011                 | 3.9                                                                            |

|                               | 100                 | 4.9                                                                            |

|                               | 101                 | 5.9                                                                            |

|                               | 110                 | 6.8                                                                            |

|                               | 111                 | 7.8                                                                            |

| Output period (s)             |                     |                                                                                |

| 4 to 6                        | 000                 | 1                                                                              |

|                               | 001                 | 5                                                                              |

|                               | 010                 | 10                                                                             |

|                               | 011                 | 20                                                                             |

|                               | 100                 | 30                                                                             |

| Duty cycle of mo              | tor pulse           |                                                                                |

| 7                             | 0                   | 75 %                                                                           |

|                               | 1                   | 100 %                                                                          |

| Pulse stretching              |                     |                                                                                |

| 8                             | 0                   | no pulse stretching                                                            |

|                               | 1                   | a pulse width of 2 $\times$ $t_{\text{p}}$ and a duty factor of 25 % are added |

|                               |                     |                                                                                |

# 8.5 Type recognition

Byte D is read to determine, which type of the PCA200x family is used in a particular application.

Table 8. Description of word D bits

| Value | Description          |

|-------|----------------------|

|       |                      |

| 0000  | PCA2002              |

| 1000  | PCA2000              |

| 0100  | PCA2001              |

| 1100  | PCA2003              |

|       | 0000<br>1000<br>0100 |

#### 32 kHz watch circuit with programmable output period and pulse width

#### 8.6 Programming procedure

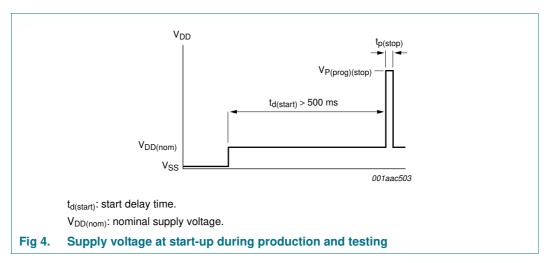

To ensure that the oscillator starts up correctly you must execute a reset sequence (see Figure 4).

For a watch it is essential that the timing calibration can be made after the watch is fully assembled. In this situation, the supply pins are often the only terminals which are still accessible.

Writing to the OTP cells and performing the related functional checks is achieved in the PCA2002 by modulating the supply voltage. The necessary control circuit consists basically of a voltage level detector, an instruction counter, which determines the function to be performed, and an 8-bit shift register, which allows writing the OTP cells of an 8-bit word in one step and which acts as data pointer for checking the OTP content.

- State 1; measurement of the crystal oscillator frequency (divided by 1024)

- · State 2; measurement of the inhibition time

- · State 3; write/check word A

- · State 4; write/check word B

- State 5; check word C (don't care since no meaning)

- State 6; check word D (type recognition)

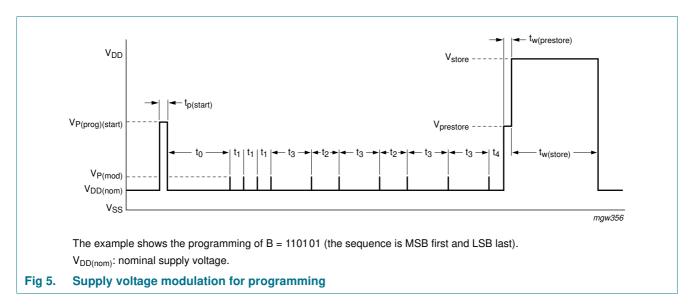

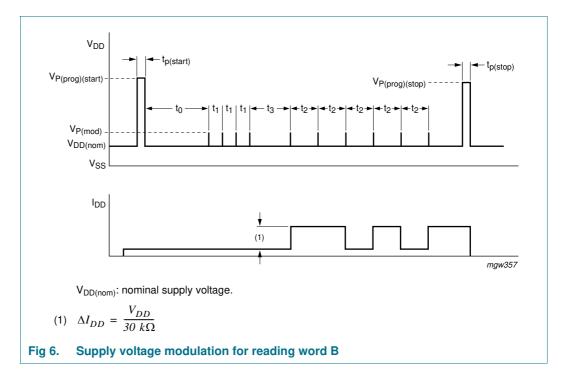

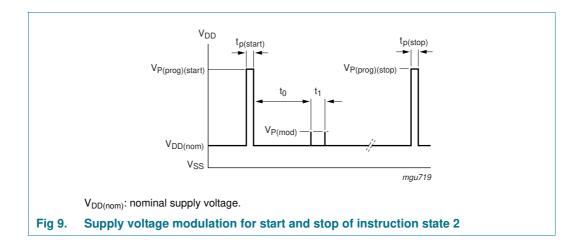

Each instruction state is switched on with a pulse to  $V_{P(prog)(start)}$ . After this large pulse, an initial waiting time of  $t_0$  is required. The programming instructions are then entered by modulating the supply voltage with small pulses (amplitude  $V_{P(mod)}$  and pulse width  $t_{mod}$ ). The first small pulse defines the start time, the following pulses perform three different functions, depending on the time delay ( $t_d$ ) from the preceding pulse (see <u>Figure 5</u>, <u>Figure 6</u>, <u>Figure 7</u>, <u>Figure 8</u> and <u>Figure 9</u>):

- $t_d = t_1$  (0.7 ms); increments the instruction counter

- $t_d = t_2$  (1.7 ms); clocks the shift register with data = logic 0

- t<sub>d</sub> = t<sub>3</sub> (2.7 ms); clocks the shift register with data = logic 1

The programming procedure requires a stable oscillator, which means that a waiting time, determined by the start-up time of the oscillator, is necessary after power-up of the circuit.

#### 32 kHz watch circuit with programmable output period and pulse width

After the  $V_{P(prog)(start)}$  pulse, the instruction counter is in state 1 and the data shift register is cleared.

The instruction state ends with a second pulse to  $V_{P(prog)(stop)}$  or with the pulse to  $V_{store}$ .

In any case, the instruction states are terminated automatically 2 seconds after the last supply modulation pulse.

#### 8.7 Programming the memory cells

Applying the two-stage programming pulse (see <u>Figure 5</u>) transfers the stored data in the shift register to the OTP cells.

Perform the following to program a memory word:

- 1. Starting with a  $V_{P(prog)(start)}$  pulse, wait for the time period  $t_0$  then set the instruction counter to the word to be written  $(t_d = t_1)$ .

- 2. Enter the data to be stored into the shift register ( $t_d = t_2$  or  $t_3$ ), LSB first (bit 8) and MSB last (bit 1).

- 3. Applying the two-stage programming pulse  $V_{prestore}$  followed by  $V_{store}$  stores the word. The delay between the last data bit and the pre-store pulse  $V_{prestore}$  is  $t_d = t_4$ . Store the word by raising the supply voltage to  $V_{store}$ ; the delay between the last data bit and the store pulse is  $t_d$ .

The example shown in Figure 5 performs the following functions:

- Start

- Setting the instruction counter to state 4 (word B)

- Entering data word 110101 into the shift register (sequence: LSB first and MSB last)

- · Writing the OTP cells for word B

#### 32 kHz watch circuit with programmable output period and pulse width

#### 8.8 Checking the memory content

The stored data of the OTP array can be checked bit wise by measuring the supply current (see Figure 6). The array word is selected by the instruction state and the bit is addressed by the shift register.

To read a word, the word is first selected ( $t_d = t_1$ ) and a logic 1 is written into the first cell of the shift register ( $t_d = t_3$ ). This logic 1 is then shifted through the entire shift register ( $t_d = t_2$ ), so that it points with each clock pulse to the next bit.

If the addressed OTP cell contains a logic 1, a 30 k $\Omega$  resistor is connected between  $V_{DD}$  and  $V_{SS}$ ; this increases the supply current accordingly.

<u>Figure 6</u> shows the supply voltage modulation for reading word B, with the corresponding supply current variation for word B = 110101 (sequence: first MSB and last LSB).

#### 32 kHz watch circuit with programmable output period and pulse width

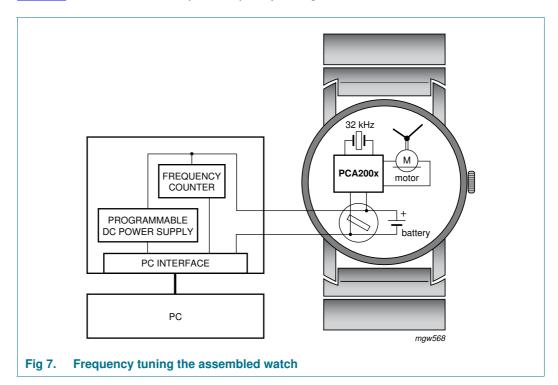

#### 8.9 Frequency tuning at assembled watch

Figure 7 shows the test set-up for frequency tuning the assembled watch.

# 8.10 Measurement of the oscillator frequency and the inhibition time

The output of the two measuring states can either be monitored directly at pin RESET or as a modulation of the supply current (a modulating resistor of 30 k $\Omega$  is connected between  $V_{DD}$  and  $V_{SS}$  when the signal at pin RESET is at HIGH-level).

The supply voltage modulation must be followed as shown in <u>Figure 4</u> in order to guarantee the correct start-up of the circuit during production and testing.

#### Measuring states:

- State 1; quartz crystal oscillator frequency divided by 1024; state 1 starts with a pulse to V<sub>P</sub> and ends with a second pulse to V<sub>P</sub>

- State 2; inhibition time has a value of  $n \times 0.122$  ms. A signal with the periodicity of 31.25 ms +  $n \times 0.122$  ms appears at pin RESET and as current modulation at pin  $V_{DD}$  (see Figure 8 and Figure 9)

### 32 kHz watch circuit with programmable output period and pulse width

#### 32 kHz watch circuit with programmable output period and pulse width

# 9. Limiting values

Table 9. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol           | Parameter                       | Conditions     |            | Min  | Max        | Unit |

|------------------|---------------------------------|----------------|------------|------|------------|------|

| $V_{DD}$         | supply voltage                  | $V_{SS} = 0 V$ | [1][2]     | -1.8 | +7.0       | V    |

| VI               | input voltage                   |                |            | -0.5 | +7.5       | V    |

| t <sub>sc</sub>  | short circuit duration time     | output         |            | -    | indefinite | S    |

| $V_{ESD}$        | electrostatic discharge voltage | НВМ            | [3]        | -    | ±2000      | V    |

|                  |                                 | MM             | [4]        | -    | ±200       | V    |

| I <sub>lu</sub>  | latch-up current                |                | <u>[5]</u> | -    | 100        | mA   |

| T <sub>stg</sub> | storage temperature             |                | [6]        | -30  | +100       | °C   |

| T <sub>amb</sub> | ambient temperature             |                |            | -10  | +60        | °C   |

<sup>[1]</sup> When writing to the OTP cells, the supply voltage (V<sub>DD</sub>) can be raised to a maximum of 12 V for a time period of 1 s.

<sup>[2]</sup> Connecting the battery with reversed polarity does not destroy the circuit, but in this condition a large current flows which rapidly discharges the battery.

<sup>[3]</sup> Pass level; Human Body Model (HBM), according to Ref. 5 "JESD22-A114".

<sup>[4]</sup> Pass level; Machine Model (MM), according to Ref. 6 "JESD22-A115".

<sup>[5]</sup> Pass level; latch-up testing according to Ref. 7 "JESD78" at maximum ambient temperature (T<sub>amb(max)</sub>).

<sup>[6]</sup> According to the NXP store and transport requirements (see Ref. 9 "NX3-00092") the devices have to be stored at a temperature of +8 °C to +45 °C and a humidity of 25 % to 75 %. For long term storage products deviant conditions are described in that document.

#### 32 kHz watch circuit with programmable output period and pulse width

# 10. Characteristics

Table 10. Characteristics

$V_{DD}$  = 1.55 V;  $V_{SS}$  = 0 V;  $f_{osc}$  = 32.768 kHz;  $T_{amb}$  = 25 °C; quartz crystal:  $R_s$  = 40 k $\Omega$ ,  $C_1$  = 2 fF to 3 fF,  $C_L$  = 8.2 pF; unless otherwise specified.

| Symbol               | Parameter                        | Conditions                                                                        | Min           | Тур  | Max  | Unit |

|----------------------|----------------------------------|-----------------------------------------------------------------------------------|---------------|------|------|------|

| Supplies             |                                  |                                                                                   |               |      |      |      |

| $V_{DD}$             | supply voltage                   | normal operating mode;<br>$T_{amb} = -10 \text{ °C to } +60 \text{ °C}$           | 1.1           | 1.55 | 3.6  | V    |

| $\Delta V_{DD}$      | supply voltage variation         | $\Delta V/\Delta t = 1 V/\mu s$                                                   | -             | -    | 0.25 | V    |

| I <sub>DD</sub>      | supply current                   | between motor pulses                                                              | -             | 90   | 120  | nA   |

|                      |                                  | between motor pulses at $V_{DD} = 3.5 \text{ V}$                                  | -             | 120  | 180  | nA   |

|                      |                                  | $T_{amb} = -10  ^{\circ}\text{C} \text{ to } +60  ^{\circ}\text{C}$               | -             | -    | 200  | nA   |

|                      |                                  | stop mode; pin RESET connected to $V_{DD}$                                        | -             | 100  | 135  | nA   |

| Motor out            | put                              |                                                                                   |               |      |      |      |

| V <sub>sat</sub>     | saturation voltage               | $R_{motor} = 2 \text{ k}\Omega;$<br>$T_{amb} = -10 \text{ °C to } +60 \text{ °C}$ | -             | 150  | 200  | mV   |

| $Z_{o(sc)} \\$       | output impedance (short circuit) | between motor pulses;<br>I <sub>motor</sub> < 1 mA                                | -             | 200  | 300  | Ω    |

| Oscillator           |                                  |                                                                                   |               |      |      |      |

| V <sub>start</sub>   | start voltage                    |                                                                                   | 1.1           | -    | -    | V    |

| g <sub>m</sub>       | transconductance                 | $V_{i(osc)} \leq 50 \ mV(p\hbox{-}p)$                                             | 5             | 10   | -    | μS   |

| t <sub>startup</sub> | start-up time                    |                                                                                   | -             | 0.3  | 0.9  | s    |

| Δf/f                 | frequency stability              | $\Delta V_{DD} = 100 \text{ mV}$                                                  | -             | 0.05 | 0.2  | ppm  |

| $C_{L(itg)}$         | integrated load capacitance      |                                                                                   | 4.3           | 5.2  | 6.3  | pF   |

| R <sub>par</sub>     | parasitic resistance             | allowed resistance between adjacent pins                                          | 20            | -    | -    | MΩ   |

| Pad RESE             | Т                                |                                                                                   |               |      |      |      |

| fo                   | output frequency                 |                                                                                   | -             | 32   | -    | Hz   |

| $V_{O(dif)}$         | differential output voltage      | $R_L = 1 \text{ M}\Omega$ ; $C_L = 10 \text{ pF}$                                 | <u>11</u> 1.4 | -    | -    | V    |

| t <sub>r</sub>       | rise time                        | $R_L = 1 \text{ M}\Omega$ ; $C_L = 10 \text{ pF}$                                 | <u>[1]</u> -  | 1    | -    | μS   |

| t <sub>f</sub>       | fall time                        | $R_L = 1 \text{ M}\Omega; C_L = 10 \text{ pF}$                                    | <u>[1]</u> -  | 1    | -    | μS   |

| $I_{i(AV)} \\$       | average input current            | pin RESET connected to $V_{DD}$ or $V_{SS}$                                       | -             | 10   | 20   | nA   |

<sup>[1]</sup>  $R_L$  and  $C_L$  are a load resistor and load capacitor, externally connected to pad RESET.

### 32 kHz watch circuit with programmable output period and pulse width

# 11. OTP programming characteristics

Table 11. Specifications for OTP programming

| Symbol                      | Parameter <sup>[1]</sup>           | Conditions                                                        | Min  | Тур  | Max  | Unit |

|-----------------------------|------------------------------------|-------------------------------------------------------------------|------|------|------|------|

| $V_{DD}$                    | supply voltage                     | during programming procedure                                      | 1.5  | -    | 3.0  | V    |

| V <sub>P(prog)(start)</sub> | programming supply voltage (start) |                                                                   | 6.6  | -    | 6.8  | V    |

| $V_{P(prog)(stop)}$         | programming supply voltage (stop)  |                                                                   | 6.2  | -    | 6.4  | V    |

| $V_{P(mod)}$                | supply voltage modulation          | for entering instructions, referred to $V_{\text{DD}}$            | 320  | 350  | 380  | mV   |

| V <sub>prestore</sub>       | prestore voltage                   | for prestore pulse                                                | 6.2  | -    | 6.4  | V    |

| V <sub>store</sub>          | supply voltage                     | for writing to the OTP cells                                      | 9.9  | 10.0 | 10.1 | V    |

| I <sub>store</sub>          | store current                      | for writing to the OTP cells                                      | -    | -    | 10   | mA   |

| t <sub>p(start)</sub>       | start pulse width                  |                                                                   | 8    | 10   | 12   | ms   |

| t <sub>p(stop)</sub>        | pulse width of stop pulse          |                                                                   | 0.05 | -    | 0.5  | ms   |

| t <sub>mod</sub>            | modulation pulse width             |                                                                   | 25   | 30   | 40   | μS   |

| $t_{w(prestore)}$           | prestore pulse width               |                                                                   | 0.05 | -    | 0.5  | ms   |

| $t_{w(store)} \\$           | store pulse width                  | for writing to the OTP cells                                      | 95   | 100  | 110  | ms   |

| $t_0$                       | time 0                             | waiting time after start pulse                                    | 20   | -    | 30   | ms   |

| t <sub>1</sub>              | time 1                             | pulse distance for incrementing the state counter                 | 0.6  | 0.7  | 0.8  | ms   |

| t <sub>2</sub>              | time 2                             | pulse distance for clocking the data register with data = logic 0 | 1.6  | 1.7  | 1.8  | ms   |

| t <sub>3</sub>              | time 3                             | pulse distance for clocking the data register with data = logic 1 | 2.6  | 2.7  | 2.8  | ms   |

| t <sub>4</sub>              | time 4                             | waiting time for writing to OTP cells                             | 0.1  | 0.2  | 0.3  | ms   |

| SR                          | slew rate                          | for modulation of the supply voltage                              | 0.5  | -    | 5.0  | V/μs |

| $R_{mod}$                   | modulation resistance              | supply current modulation read-out resistor                       | 18   | 30   | 45   | kΩ   |

<sup>[1]</sup> Program each word once only.

#### 32 kHz watch circuit with programmable output period and pulse width

# 12. Bare die outline

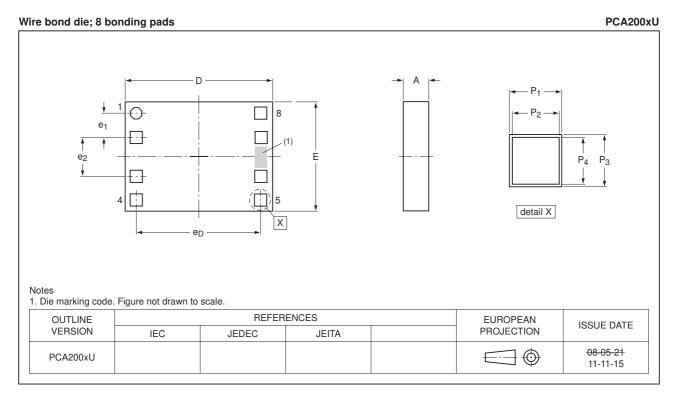

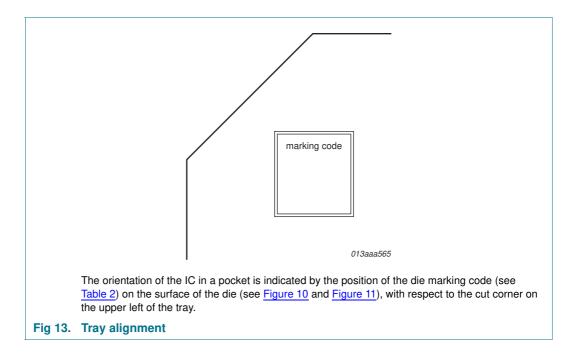

Fig 10. Bare die outline of PCA2002U (for dimensions see Table 12, for pin location see Table 14)

Table 12. Dimensions of PCA2002U

Original dimensions are in mm.

| Unit (mm) | Α    | D    | E    | e <sub>1</sub> | $\mathbf{e_2}$ | $\mathbf{e}_{D}$ | $P_1$ | $P_2$ | $P_3$ | $P_4$ |

|-----------|------|------|------|----------------|----------------|------------------|-------|-------|-------|-------|

| max       | 0.22 | -    | -    | -              | -              | -                | 0.099 | 0.089 | 0.099 | 0.089 |

| nom       | 0.20 | 1.16 | 0.86 | 0.17           | 0.32           | 0.96             | 0.096 | 0.086 | 0.096 | 0.086 |

| min       | 0.18 | -    | -    | -              | -              | -                | 0.093 | 0.083 | 0.093 | 0.083 |

#### 32 kHz watch circuit with programmable output period and pulse width

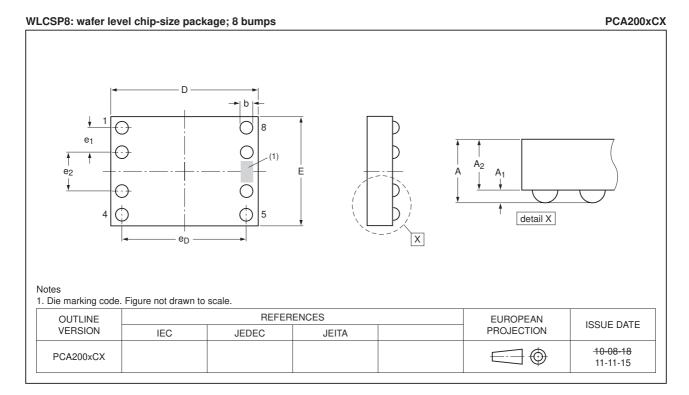

Fig 11. Bare die outline PCA2002CX (WLCSP8) (for dimensions see Table 13, for pin location see Table 14)

**Table 13. Dimensions of PCA200xCX** *Original dimensions are in mm.*

| Unit (mm)       | Α     | A <sub>1</sub> | A <sub>2</sub> | b    | D    | E    | e <sub>1</sub> | e <sub>2</sub> | e <sub>D</sub> |

|-----------------|-------|----------------|----------------|------|------|------|----------------|----------------|----------------|

| PCA2002CX8/5/1  |       |                |                |      |      |      |                |                |                |

| max             | -     | 0.090          | -              | 0.12 | -    | -    | -              | -              | -              |

| nom             | 0.762 | 0.075          | 0.69           | 0.10 | 1.16 | 0.86 | 0.17           | 0.32           | 0.96           |

| min             | -     | 0.060          | -              | 0.08 | -    | -    | -              | -              | -              |

| PCA2002CX8/12/1 |       |                |                |      |      |      |                |                |                |

| max             | 0.310 | 0.090          | 0.22           | 0.12 | -    | -    | -              | -              | -              |

| nom             | 0.275 | 0.075          | 0.20           | 0.10 | 1.16 | 0.86 | 0.17           | 0.32           | 0.96           |

| min             | 0.240 | 0.060          | 0.18           | 0.08 | -    | -    | -              | -              | -              |

#### 32 kHz watch circuit with programmable output period and pulse width

Table 14. Bonding pad and solder bump description

| Symbol              | Pin | X[1] | Υ[1] | Type   | Description          |

|---------------------|-----|------|------|--------|----------------------|

| V <sub>SS</sub> [2] | 1   | -480 | +330 | supply | ground               |

| i.c.[3]             | 2   | -480 | +160 | -      | internally connected |

| OSCIN               | 3   | -480 | -160 | input  | oscillator input     |

| OSCOUT              | 4   | -480 | -330 | output | oscillator output    |

| $V_{DD}$            | 5   | +480 | -330 | supply | supply voltage       |

| MOT1                | 6   | +480 | -160 | output | motor 1 output       |

| MOT2                | 7   | +480 | +160 | output | motor 2 output       |

| RESET               | 8   | +480 | +330 | input  | reset input          |

<sup>[1]</sup> All coordinates are referenced, in  $\mu m$ , to the center of the die (see Figure 10 and Figure 11).

<sup>[2]</sup> The substrate (rear side of the chip) is connected to  $V_{SS}$ . Therefore, the die pad must be either floating or connected to  $V_{SS}$ .

<sup>[3]</sup> Pad i.c. is used for factory test; in normal operation it must be left open-circuit, and it has an internal pull-down resistor connected to  $V_{\rm SS}$ .

32 kHz watch circuit with programmable output period and pulse width

# 13. Packing information

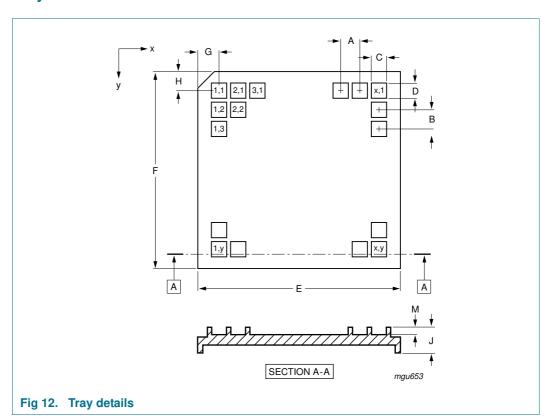

# 13.1 Tray information

Table 15. Tray dimensions

| Dimension | Description                                         | Value    |

|-----------|-----------------------------------------------------|----------|

| A         | pocket pitch; x direction                           | 2.15 mm  |

| В         | pocket pitch; y direction                           | 2.43 mm  |

| С         | pocket width; x direction                           | 1.01 mm  |

| D         | pocket width; y direction                           | 1.39 mm  |

| E         | tray width; x direction                             | 50.67 mm |

| F         | tray width; y direction                             | 50.67 mm |

| G         | distance from cut corner to pocket (1 and 1) center | 4.86 mm  |

| Н         | distance from cut corner to pocket (1 and 1) center | 4.66 mm  |

| J         | tray thickness                                      | 3.94 mm  |

| M         | pocket depth                                        | 0.61 mm  |

| Х         | number of pockets in x direction                    | 20       |

| у         | number of pockets in y direction                    | 18       |

### 32 kHz watch circuit with programmable output period and pulse width

#### 32 kHz watch circuit with programmable output period and pulse width

# 13.2 Wafer and Film Frame Carrier (FFC) information

PCA2002

#### 32 kHz watch circuit with programmable output period and pulse width

#### 32 kHz watch circuit with programmable output period and pulse width

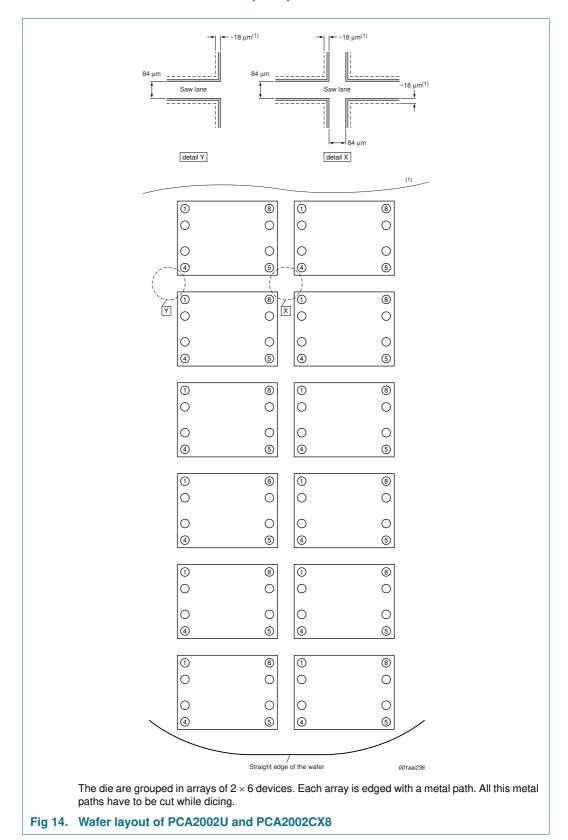

Table 16. PCA2002 wafer information

| Type number     | Wafer thickness | Wafer diameter | FFC for wafer size | Marking of bad die |

|-----------------|-----------------|----------------|--------------------|--------------------|

| PCA2002U/10AB/1 | 0.20 mm         | 6 inch         | 6 inch             | inking             |

| PCA2002CX8/5/1  | 0.69 mm         | 6 inch         | 6 inch             | wafer mapping      |

| PCA2002CX8/12/1 | 0.20 mm         | 6 inch         | 8 inch             | wafer mapping      |

# 14. Soldering of WLCSP packages

#### 14.1 Introduction to soldering WLCSP packages

This text provides a very brief insight into a complex technology. A more in-depth account of soldering WLCSP (Wafer Level Chip-Size Packages) can be found in application note AN10439 "Wafer Level Chip Scale Package" and in application note AN10365 "Surface mount reflow soldering description".

Wave soldering is not suitable for this package.

All NXP WLCSP packages are lead-free.

#### 14.2 Board mounting

Board mounting of a WLCSP requires several steps:

- 1. Solder paste printing on the PCB

- 2. Component placement with a pick and place machine

- 3. The reflow soldering itself

### 14.3 Reflow soldering

Key characteristics in reflow soldering are:

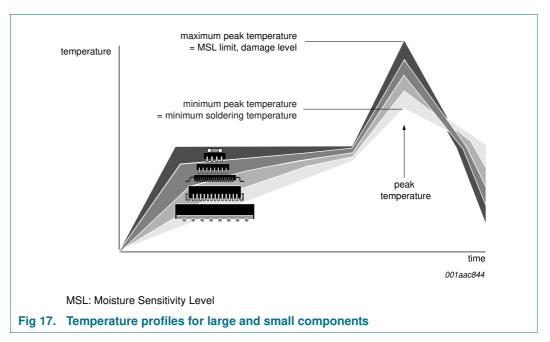

- Lead-free versus SnPb soldering; note that a lead-free reflow process usually leads to higher minimum peak temperatures (see <u>Figure 17</u>) than a PbSn process, thus reducing the process window

- Solder paste printing issues, such as smearing, release, and adjusting the process window for a mix of large and small components on one board

- Reflow temperature profile; this profile includes preheat, reflow (in which the board is heated to the peak temperature), and cooling down. It is imperative that the peak temperature is high enough for the solder to make reliable solder joints (a solder paste characteristic) while being low enough that the packages and/or boards are not damaged. The peak temperature of the package depends on package thickness and volume and is classified in accordance with <u>Table 17</u>.

#### 32 kHz watch circuit with programmable output period and pulse width

Table 17. Lead-free process (from J-STD-020C)

| Package thickness (mm) | Package reflow temperature (°C) |             |        |  |  |  |

|------------------------|---------------------------------|-------------|--------|--|--|--|

|                        | Volume (mm³)                    |             |        |  |  |  |

|                        | < 350                           | 350 to 2000 | > 2000 |  |  |  |

| < 1.6                  | 260                             | 260         | 260    |  |  |  |

| 1.6 to 2.5             | 260                             | 250         | 245    |  |  |  |

| > 2.5                  | 250                             | 245         | 245    |  |  |  |

Moisture sensitivity precautions, as indicated on the packing, must be respected at all times.

Studies have shown that small packages reach higher temperatures during reflow soldering, see Figure 17.

For further information on temperature profiles, refer to application note *AN10365* "Surface mount reflow soldering description".

#### 14.3.1 Stand off

The stand off between the substrate and the chip is determined by:

- · The amount of printed solder on the substrate

- · The size of the solder land on the substrate

- The bump height on the chip

The higher the stand off, the better the stresses are released due to TEC (Thermal Expansion Coefficient) differences between substrate and chip.

#### 32 kHz watch circuit with programmable output period and pulse width

#### 14.3.2 Quality of solder joint

A flip-chip joint is considered to be a good joint when the entire solder land has been wetted by the solder from the bump. The surface of the joint should be smooth and the shape symmetrical. The soldered joints on a chip should be uniform. Voids in the bumps after reflow can occur during the reflow process in bumps with high ratio of bump diameter to bump height, i.e. low bumps with large diameter. No failures have been found to be related to these voids. Solder joint inspection after reflow can be done with X-ray to monitor defects such as bridging, open circuits and voids.

#### 14.3.3 Rework

In general, rework is not recommended. By rework we mean the process of removing the chip from the substrate and replacing it with a new chip. If a chip is removed from the substrate, most solder balls of the chip will be damaged. In that case it is recommended not to re-use the chip again.

Device removal can be done when the substrate is heated until it is certain that all solder joints are molten. The chip can then be carefully removed from the substrate without damaging the tracks and solder lands on the substrate. Removing the device must be done using plastic tweezers, because metal tweezers can damage the silicon. The surface of the substrate should be carefully cleaned and all solder and flux residues and/or underfill removed. When a new chip is placed on the substrate, use the flux process instead of solder on the solder lands. Apply flux on the bumps at the chip side as well as on the solder pads on the substrate. Place and align the new chip while viewing with a microscope. To reflow the solder, use the solder profile shown in application note *AN10365 "Surface mount reflow soldering description"*.

#### 14.3.4 Cleaning

Cleaning can be done after reflow soldering.