# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Rev. 04 — 19 August 2009

**Product data sheet**

### 1. General description

The PCA9511A is a hot swappable I<sup>2</sup>C-bus and SMBus buffer that allows I/O card insertion into a live backplane without corrupting the data and clock buses. Control circuitry prevents the backplane from being connected to the card until a stop command or bus idle occurs on the backplane without bus contention on the card. When the connection is made, the PCA9511A provides bidirectional buffering, keeping the backplane and card capacitances isolated.

The PCA9511A rise time accelerator circuitry allows the use of weaker DC pull-up currents while still meeting rise time requirements. The PCA9511A incorporates a digital ENABLE input pin, which enables the device when asserted HIGH and forces the device into a low current mode when asserted LOW, and an open-drain READY output pin, which indicates that the backplane and card sides are connected together (HIGH) or not (LOW).

During insertion, the PCA9511A SDA and SCL lines are precharged to 1 V to minimize the current required to charge the parasitic capacitance of the chip.

### 2. Features

- Bidirectional buffer for SDA and SCL lines increases fan out and prevents SDA and SCL corruption during live board insertion and removal from multipoint backplane systems

- Compatible with I<sup>2</sup>C-bus Standard-mode, I<sup>2</sup>C-bus Fast-mode, and SMBus standards

- Built-in  $\Delta V/\Delta t$  rise time accelerators on all SDA and SCL lines (0.6 V threshold) requires the bus pull-up voltage and supply voltage (V<sub>CC</sub>) to be the same

- Active HIGH ENABLE input

- Active HIGH READY open-drain output

- High-impedance SDA and SCL pins for V<sub>CC</sub> = 0 V

- 1 V precharge on all SDA and SCL lines

- Supporting clock stretching and multiple master arbitration/synchronization

- Operating power supply voltage range: 2.7 V to 5.5 V

- 0 Hz to 400 kHz clock frequency

- ESD protection exceeds 2000 V HBM per JESD22-A114, 200 V MM per JESD22-A115, and 1000 V CDM per JESD22-C101

- Latch-up testing is done to JEDEC Standard JESD78 which exceeds 100 mA

- Packages offered: SO8, TSSOP8 (MSOP8)

### 3. Applications

cPCI, VME, AdvancedTCA cards and other multipoint backplane cards that are required to be inserted or removed from an operating system

### 4. Feature selection

#### Table 1. Feature selection chart

| Feature                                                                                 | PCA9510A | PCA9511A | PCA9512A | PCA9513A | PCA9514A |

|-----------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|

| idle detect                                                                             | yes      | yes      | yes      | yes      | yes      |

| high-impedance SDA, SCL pins for $V_{CC} = 0 V$                                         | yes      | yes      | yes      | yes      | yes      |

| rise time accelerator circuitry on SDAn and SCLn lines                                  | -        | yes      | yes      | yes      | yes      |

| rise time accelerator circuitry hardware disable pin for lightly loaded systems         | -        | -        | yes      | -        | -        |

| rise time accelerator threshold 0.8 V versus 0.6 V improves noise margin                | -        | -        | -        | yes      | yes      |

| ready open-drain output                                                                 | yes      | yes      | -        | yes      | yes      |

| two $V_{CC}$ pins to support 5 V to 3.3 V level translation with improved noise margins | -        | -        | yes      | -        | -        |

| 1 V precharge on all SDA and SCL lines                                                  | in only  | yes      | yes      | -        | -        |

| 92 $\mu$ A current source on SCLIN and SDAIN for PICMG applications                     | -        | -        | -        | yes      | -        |

### 5. Ordering information

#### Table 2.Ordering information

$T_{amb} = -40 \circ C$  to  $+85 \circ C$

| Type number | Topside | Package               | Package                                                                |          |  |  |  |

|-------------|---------|-----------------------|------------------------------------------------------------------------|----------|--|--|--|

|             | mark    | Name                  | Description                                                            | Version  |  |  |  |

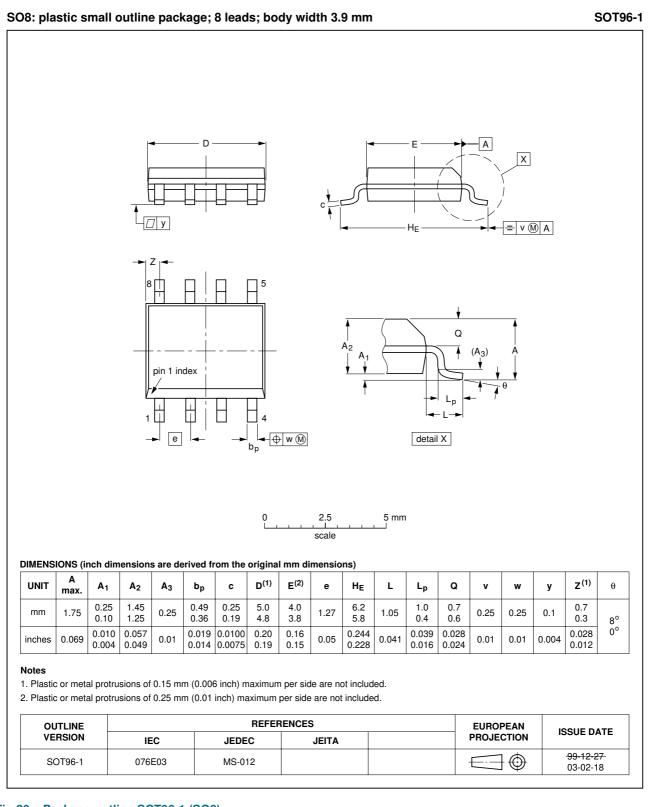

| PCA9511AD   | PA9511A | SO8                   | plastic small outline package; 8 leads; body width 3.9 mm              | SOT96-1  |  |  |  |

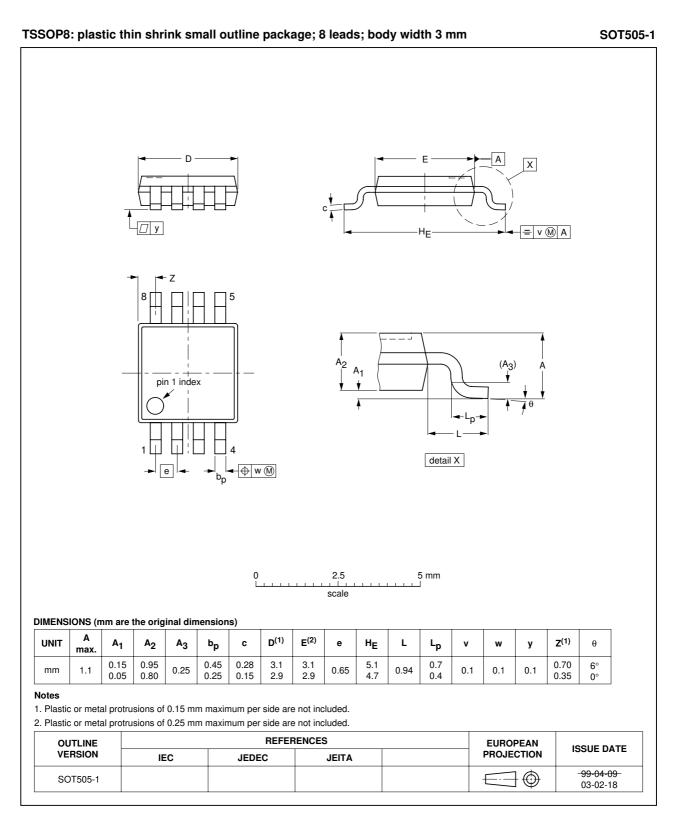

| PCA9511ADP  | 9511A   | TSSOP8 <sup>[1]</sup> | plastic thin shrink small outline package; 8 leads;<br>body width 3 mm | SOT505-1 |  |  |  |

[1] Also known as 'MSOP8'.

#### Hot swappable I<sup>2</sup>C-bus and SMBus bus buffer

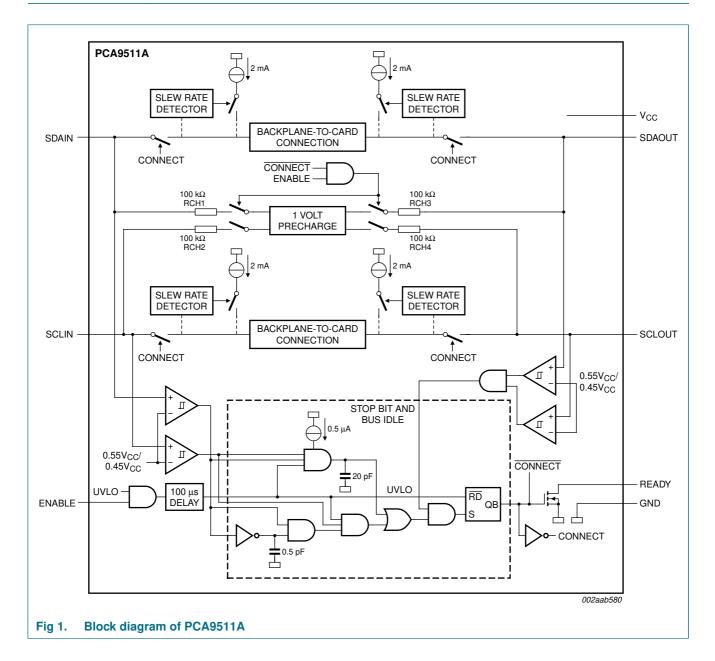

### 6. Block diagram

Hot swappable I<sup>2</sup>C-bus and SMBus bus buffer

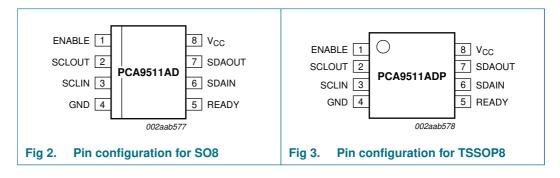

### 7. Pinning information

#### 7.1 Pinning

#### 7.2 Pin description

#### Table 3. Pin description

|                 |     | and the second                                                                             |

|-----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol          | Pin | Description                                                                                                                                                                                  |

| ENABLE          | 1   | Chip enable. Grounding this input puts the part in a low current (< 1 $\mu$ A) mode. It also disables the rise time accelerators, isolates SDAIN from SDAOUT and isolates SCLIN from SCLOUT. |

| SCLOUT          | 2   | serial clock output to and from the SCL bus on the card                                                                                                                                      |

| SCLIN           | 3   | serial clock input to and from the SCL bus on the backplane                                                                                                                                  |

| GND             | 4   | Ground. Connect this pin to a ground plane for best results.                                                                                                                                 |

| READY           | 5   | open-drain output which pulls LOW when SDAIN and SCLIN are disconnected from SDAOUT and SCLOUT, and goes HIGH when the two sides are connected                                               |

| SDAIN           | 6   | serial data input to and from the SDA bus on the backplane                                                                                                                                   |

| SDAOUT          | 7   | serial data output to and from the SDA bus on the card                                                                                                                                       |

| V <sub>CC</sub> | 8   | power supply                                                                                                                                                                                 |

|                 |     |                                                                                                                                                                                              |

### 8. Functional description

Refer to Figure 1 "Block diagram of PCA9511A".

#### 8.1 Start-up

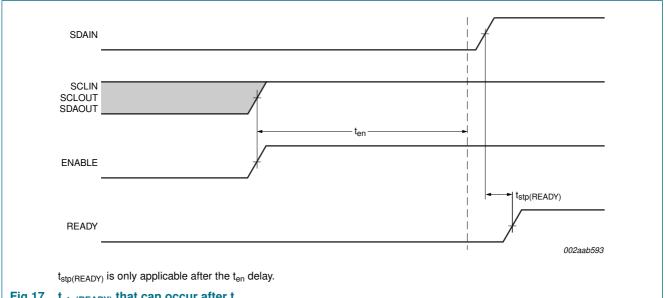

An undervoltage/initialization circuit holds the parts in a disconnected state which presents high-impedance to all SDA and SCL pins during power-up. A LOW on the ENABLE pin also forces the parts into the low current disconnected state when the  $I_{CC}$  is essentially zero. As the power supply is brought up and the ENABLE is HIGH or the part is powered and the ENABLE is taken from LOW to HIGH it enters an initialization state where the internal references are stabilized and the precharge circuit is enabled. At the end of the initialization state the 'Stop Bit And Bus Idle' detect circuit is enabled. With the ENABLE pin HIGH long enough to complete the initialization state ( $t_{en}$ ) and remaining HIGH when all the SDA and SCL pins have been HIGH for the bus idle time or when all pins are HIGH and a STOP condition is seen on the SDAIN and SCLIN pins, SDAIN is connected to SDAOUT and SCLIN is connected to SCLOUT. The 1 V precharge circuitry

is activated during the initialization and is deactivated when the connection is made. The precharge circuitry pulls up the SDA and SCL pins to 1 V through individual 100 k $\Omega$  nominal resistors. This precharges the pins to 1 V to minimize the worst case disturbances that result from inserting a card into the backplane where the backplane and the card are at opposite logic levels.

#### 8.2 Connect circuitry

Once the connection circuitry is activated, the behavior of SDAIN and SDAOUT as well as SCLIN and SCLOUT become identical with each acting as a bidirectional buffer that isolates the input capacitance from the output bus capacitance while communicating the logic levels. A LOW forced on either SDAIN or SDAOUT will cause the other pin to be driven to a LOW by the part. The same is also true for the SCL pins. Noise between  $0.7V_{CC}$  and  $V_{CC}$  is generally ignored because a falling edge is only recognized when it falls below  $0.7V_{CC}$  with a slew rate of at least  $1.25 \text{ V/}\mu\text{s}$ . When a falling edge is seen on one pin, the other pin in the pair turns on a pull-down driver that is referenced to a small voltage above the falling pin. The driver will pull the pin down at a slew rate determined by the driver and the load initially, because it does not start until the first falling pin is below  $0.7V_{CC}$ . The first falling pin may have a fast or slow slew rate, if it is faster than the pull down slew rate then the initial pull-down rate will continue. If the first falling pin has a slow slew rate then the second pin will be pulled down at its initial slew rate only until it is just above the first pin voltage then they will both continue down at the slew rate of the first.

Once both sides are LOW they will remain LOW until all the external drivers have stopped driving LOWs. If both sides are being driven LOW to the same value for instance, 10 mV by external drivers, which is the case for clock stretching and is typically the case for acknowledge, and one side external driver stops driving that pin will rise until the internal driver pulls it down to the offset voltage. When the last external driver stops driving a LOW, that pin will rise up and settle out just above the other pin as both rise together with a slew rate determined by the internal slew rate control and the RC time constant. As long as the slew rate is at least 1.25 V/ $\mu$ s, when the pin voltage exceeds 0.6 V for the PCA9511A, the rise time accelerator's circuits are turned on and the pull-down driver is turned off.

#### 8.3 Maximum number of devices in series

Each buffer adds about 0.1 V dynamic level offset at 25 °C with the offset larger at higher temperatures. Maximum offset (V<sub>offset</sub>) is 0.150 V with a 10 kΩ pull-up resistor. The LOW level at the signal origination end (master) is dependent upon the load and the only specification point is that the I<sup>2</sup>C-bus specification of 3 mA will produce V<sub>OL</sub> < 0.4 V, although if lightly loaded the V<sub>OL</sub> may be ~0.1 V. Assuming V<sub>OL</sub> = 0.1 V and V<sub>offset</sub> = 0.1 V, the level after four buffers would be 0.5 V, which is only about 0.1 V below the threshold of the rising edge accelerator (about 0.6 V). With great care a system with four buffers may work, but as the V<sub>OL</sub> moves up from 0.1 V, noise or bounces on the line will result in firing the rising edge accelerator thus introducing false clock edges. Generally it is recommended to limit the number of buffers in series to two, and to keep the load light to minimize the offset.

The PCA9510A (rise time accelerator is permanently disabled) and the PCA9512A (rise time accelerator can be turned off) are a little different with the rise time accelerator turned off because the rise time accelerator will not pull the node up, but the same logic that turns

on the accelerator turns the pull-down off. If the V<sub>IL</sub> is above ~0.6 V and a rising edge is detected, the pull-down will turn off and will not turn back on until a falling edge is detected.

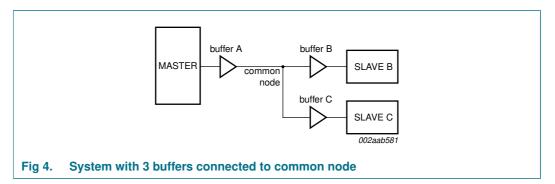

Consider a system with three buffers connected to a common node and communication between the Master and Slave B that are connected at either end of buffer A and buffer B in series as shown in Figure 4. Consider if the V<sub>OL</sub> at the input of buffer A is 0.3 V and the V<sub>OL</sub> of Slave B (when acknowledging) is 0.4 V with the direction changing from Master to Slave B and then from Slave B to Master. Before the direction change you would observe V<sub>II</sub> at the input of buffer A of 0.3 V and its output, the common node, is ~0.4 V. The output of buffer B and buffer C would be ~0.5 V, but Slave B is driving 0.4 V, so the voltage at Slave B is 0.4 V. The output of buffer C is ~0.5 V. When the Master pull-down turns off, the input of buffer A rises and so does its output, the common node, because it is the only part driving the node. The common node will rise to 0.5 V before buffer B's output turns on, if the pull-up is strong the node may bounce. If the bounce goes above the threshold for the rising edge accelerator ~0.6 V the accelerators on both buffer A and buffer C will fire contending with the output of buffer B. The node on the input of buffer A will go HIGH as will the input node of buffer C. After the common node voltage is stable for a while the rising edge accelerators will turn off and the common node will return to ~0.5 V because the buffer B is still on. The voltage at both the Master and Slave C nodes would then fall to ~0.6 V until Slave B turned off. This would not cause a failure on the data line as long as the return to 0.5 V on the common node (~0.6 V at the Master and Slave C) occurred before the data setup time. If this were the SCL line, the parts on buffer A and buffer C would see a false clock rather than a stretched clock, which would cause a system error.

#### 8.4 Propagation delays

The delay for a rising edge is determined by the combined pull-up current from the bus resistors and the rise time accelerator current source and the effective capacitance on the lines. If the pull-up currents are the same, any difference in rise time is directly proportional to the difference in capacitance between the two sides. The  $t_{PLH}$  may be negative if the output capacitance is less than the input capacitance and would be positive if the output capacitance is larger than the input capacitance, when the currents are the same.

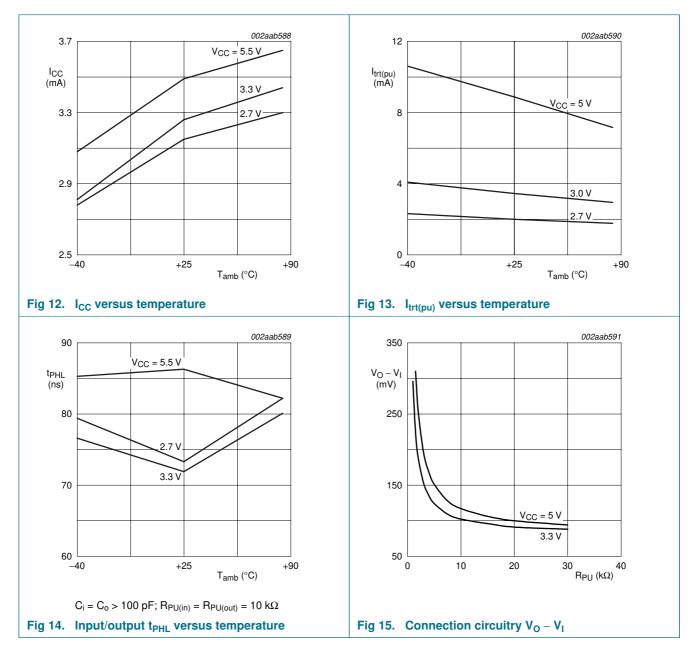

The  $t_{PHL}$  can never be negative because the output does not start to fall until the input is below 0.7V<sub>CC</sub>, and the output turn on has a non-zero delay, and the output has a limited maximum slew rate, and even if the input slew rate is slow enough that the output catches up it will still lag the falling voltage of the input by the offset voltage. The maximum  $t_{PHL}$  occurs when the input is driven LOW with zero delay and the output is still limited by its

turn-on delay and the falling edge slew rate. The output falling edge slew rate is a function of the internal maximum slew rate which is a function of temperature,  $V_{CC}$  and process, as well as the load current and the load capacitance.

#### 8.5 **Rise time accelerators**

During positive bus transitions a 2 mA current source is switched on to quickly slew the SDA and SCL lines HIGH once the input level of 0.6 V for the PCA9511A is exceeded. The rising edge rate should be at least 1.25 V/µs to guarantee turn on of the accelerators. The built-in  $\Delta V/\Delta t$  rise time accelerators on all SDA and SCL lines requires the bus pull-up voltage and supply voltage (V<sub>CC</sub>) to be the same.

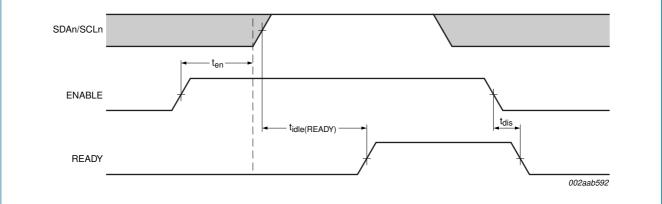

#### 8.6 **READY** digital output

This pin provides a digital flag which is LOW when either ENABLE is LOW or the start-up sequence described earlier in this section has not been completed. READY goes HIGH when ENABLE is HIGH and start-up is complete. The pin is driven by an open-drain pull-down capable of sinking 3 mA while holding 0.4 V on the pin. Connect a resistor of 10 k $\Omega$  to V<sub>CC</sub> to provide the pull-up.

#### 8.7 ENABLE low current disable

Grounding the ENABLE pin disconnects the backplane side from the card side, disables the rise time accelerators, drives READY LOW, disables the bus precharge circuitry, and puts the part in a low current state. When the pin voltage is driven all the way to  $V_{CC}$ , the part waits for data transactions on both the backplane and card sides to be complete before reconnecting the two sides.

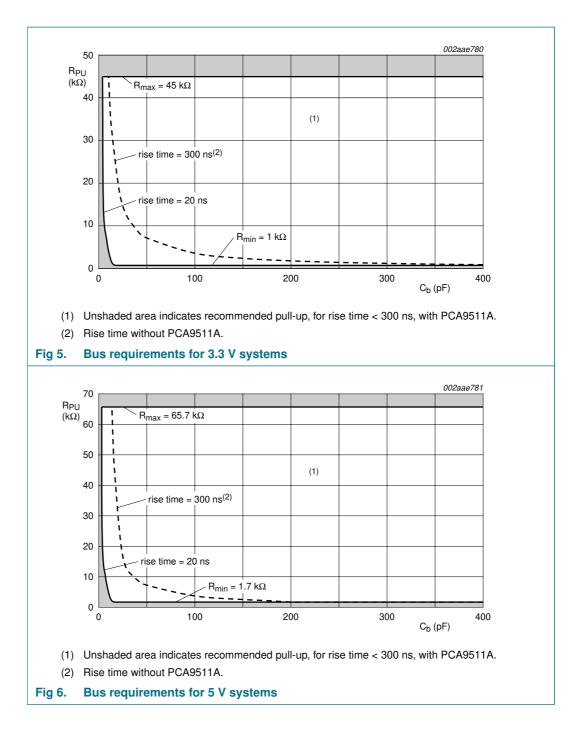

#### 8.8 Resistor pull-up value selection

The system pull-up resistors must be strong enough to provide a positive slew rate of 1.25 V/ $\mu$ s on the SDA and SCL pins, in order to activate the boost pull-up currents during rising edges. Choose maximum resistor value using the formula given in Equation 1:

$$R \le 800 \times 10^3 \left(\frac{V_{CC(min)} - 0.6}{C}\right) \tag{1}$$

where R is the pull-up resistor value in  $\Omega$ ,  $V_{CC(min)}$  is the minimum  $V_{CC}$  voltage in volts, and C is the equivalent bus capacitance in picofarads (pF).

In addition, regardless of the bus capacitance, always choose  $R \leq 65.7 \ k\Omega$  for  $V_{CC} = 5.5 \ V$  maximum,  $R \leq 45 \ k\Omega$  for  $V_{CC} = 3.6 \ V$  maximum. The start-up circuitry requires logic HIGH voltages on SDAOUT and SCLOUT to connect the backplane to the card, and these pull-up values are needed to overcome the precharge voltage. See the curves in Figure 5 and Figure 6 for guidance in resistor pull-up selection.

#### Hot swappable I<sup>2</sup>C-bus and SMBus bus buffer

### 8.9 Hot swapping and capacitance buffering application

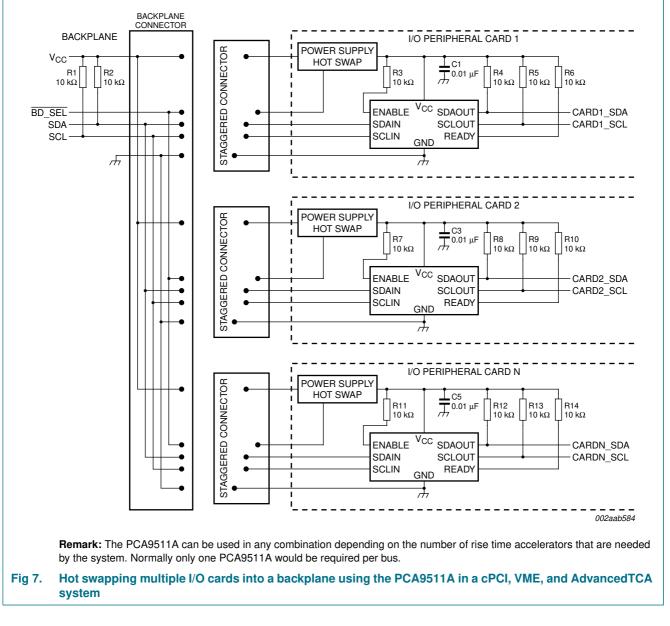

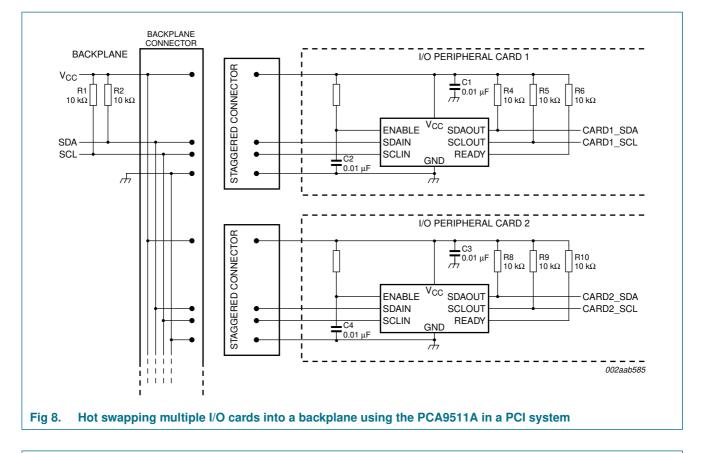

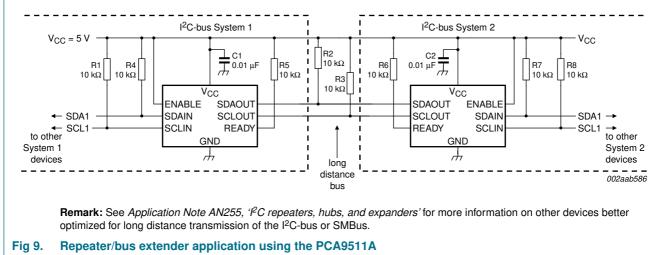

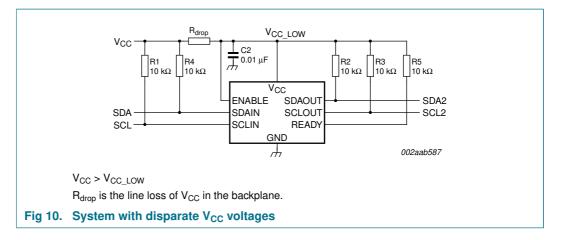

Figure 7 through Figure 10 illustrate the usage of the PCA9511A in applications that take advantage of both its hot swapping and capacitance buffering features. In all of these applications, note that if the I/O cards were plugged directly into the backplane, all of the backplane and card capacitances would add directly together, making rise time and fall time requirements difficult to meet. Placing a bus buffer on the edge of each card, however, isolates the card capacitance from the backplane. For a given I/O card, the PCA9511A drives the capacitance of everything on the card and the backplane must drive only the capacitance of the bus buffer, which is less than 10 pF, the connector, trace, and all additional cards on the backplane.

See *Application Note AN10160, 'Hot Swap Bus Buffer'* for more information on applications and technical assistance.

PCA9511A\_4 Product data sheet

#### Hot swappable I<sup>2</sup>C-bus and SMBus bus buffer

#### Hot swappable I<sup>2</sup>C-bus and SMBus bus buffer

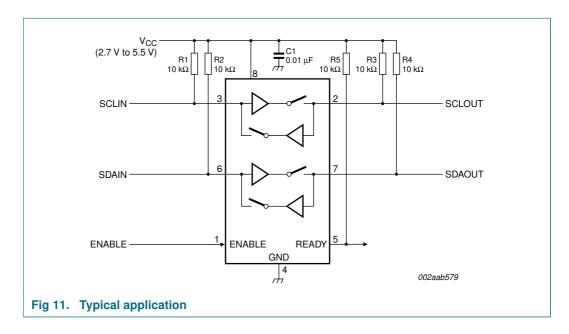

## 9. Application design-in information

### 10. Limiting values

#### Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol              | Parameter                                              | Conditions | Min             | Max  | Unit |

|---------------------|--------------------------------------------------------|------------|-----------------|------|------|

| V <sub>CC</sub>     | supply voltage                                         |            | <u>[1]</u> –0.5 | +7   | V    |

| V <sub>n</sub>      | voltage on SDAIN, SCLIN, SDAOUT, SCLOUT, READY, ENABLE |            | [1] -0.5        | +7   | V    |

| T <sub>oper</sub>   | operating temperature                                  |            | -40             | +85  | °C   |

| T <sub>stg</sub>    | storage temperature                                    |            | -65             | +150 | °C   |

| T <sub>sp</sub>     | solder point temperature                               | 10 s max.  | -               | +300 | °C   |

| T <sub>j(max)</sub> | maximum junction temperature                           |            | -               | +125 | °C   |

|                     |                                                        |            |                 |      |      |

[1] Voltages with respect to pin GND.

## **11. Characteristics**

#### Table 5.Characteristics

$V_{CC}$  = 2.7 V to 5.5 V;  $T_{amb}$  = -40 °C to +85 V; unless otherwise specified.

| Symbol                   | Parameter                              | Conditions                                                                |            | Min                 | Тур                 | Max                | Unit |

|--------------------------|----------------------------------------|---------------------------------------------------------------------------|------------|---------------------|---------------------|--------------------|------|

| Power supp               | ply                                    |                                                                           |            |                     |                     |                    |      |

| V <sub>CC</sub>          | supply voltage                         |                                                                           | [1]        | 2.7                 | -                   | 5.5                | V    |

| I <sub>CC</sub>          | supply current                         |                                                                           | <u>[1]</u> | -                   | 3.5                 | 6                  | mA   |

| I <sub>CC(sd)</sub>      | Shut-down mode supply current          | $V_{\text{ENABLE}} = 0$ V; all other pins at $V_{\text{CC}}$ or GND       |            | -                   | 0.1                 | -                  | μA   |

| Start-up cii             | rcuitry                                |                                                                           |            |                     |                     |                    |      |

| V <sub>pch</sub>         | precharge voltage                      | SDA, SCL floating                                                         | <u>[1]</u> | 0.8                 | 1.1                 | 1.2                | V    |

| V <sub>IH(ENABLE)</sub>  | HIGH-level input voltage on pin ENABLE |                                                                           |            | -                   | $0.5 \times V_{CC}$ | $0.7 	imes V_{CC}$ | V    |

| V <sub>IL(ENABLE)</sub>  | LOW-level input voltage on pin ENABLE  |                                                                           |            | $0.3 \times V_{CC}$ | $0.5 \times V_{CC}$ | -                  | V    |

| I <sub>I(ENABLE)</sub>   | input current on pin<br>ENABLE         | $V_{\text{ENABLE}} = 0 \text{ V to } V_{\text{CC}}$                       |            | -                   | ±0.1                | ±1                 | μA   |

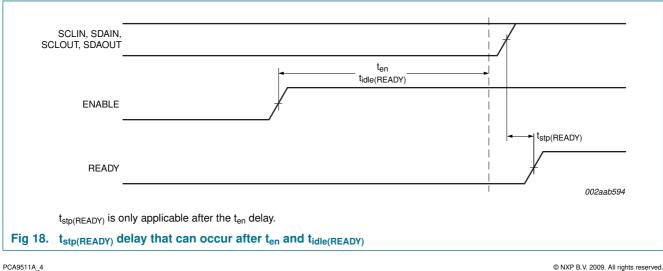

| t <sub>en</sub>          | enable time                            |                                                                           | [2]        | -                   | 110                 | -                  | μs   |

| $t_{idle(READY)}$        | bus idle time to READY active          |                                                                           | <u>[1]</u> | 50                  | 105                 | 200                | μs   |

| t <sub>dis(EN-RDY)</sub> | disable time (ENABLE to READY)         |                                                                           |            | -                   | 30                  | -                  | ns   |

| $t_{stp(READY)}$         | SDAIN to READY delay after STOP        |                                                                           | <u>[3]</u> | -                   | 1.2                 | -                  | μs   |

| t <sub>READY</sub>       | SCLOUT/SDAOUT to<br>READY delay        |                                                                           | <u>[3]</u> | -                   | 0.8                 | -                  | μs   |

| I <sub>LZ(READY)</sub>   | off-state leakage current on pin READY | $V_{\text{ENABLE}} = V_{\text{CC}}$                                       |            | -                   | ±0.3                | -                  | μA   |

| $C_{i(ENABLE)}$          | input capacitance on<br>pin ENABLE     | $V_I = V_{CC}$ or GND                                                     | <u>[4]</u> | -                   | 1.9                 | 4.0                | pF   |

| $C_{o(READY)}$           | output capacitance on<br>pin READY     | $V_I = V_{CC} \text{ or } GND$                                            | <u>[4]</u> | -                   | 2.5                 | 4.0                | pF   |

| V <sub>OL(READY)</sub>   | LOW-level output voltage on pin READY  | $I_{pu} = 3 \text{ mA}; V_{ENABLE} = V_{CC}$                              | <u>[1]</u> | -                   | -                   | 0.4                | V    |

| Rise time a              | ccelerators                            |                                                                           |            |                     |                     |                    |      |

| I <sub>trt(pu)</sub>     | transient boosted pull-up<br>current   | positive transition on SDA, SCL; $V_{CC} = 2.7 V$ ; slew rate = 1.25 V/µs | [5][6]     | 1                   | 2                   | -                  | mA   |

#### Hot swappable I<sup>2</sup>C-bus and SMBus bus buffer

#### Table 5. Characteristics ...continued

$V_{CC}$  = 2.7 V to 5.5 V;  $T_{amb}$  = -40 °C to +85 V; unless otherwise specified.

| V <sub>CC</sub> = 3.3 V $V_{CC} = 3.3 V$ $V_{PLH}$ LOW to HIGH<br>propagation delaySCL to SCL and SDA to SDA;<br>10 kΩ to V <sub>CC</sub> ;<br>CL = 100 pF each side-0-ns $t_{PHL}$ HIGH to LOW<br>propagation delaySCL to SCL and SDA to SDA;<br>10 kΩ to V <sub>CC</sub> ;<br>CL = 100 pF each side-70-ns $C_{I(SCLSDA)}$ SCL and SDA input<br>capacitance(ຢ)-57pF $V_{OL}$ LOW-level output<br>voltage $V_1 = 0 V$ ; SDAn, SCLn pins;<br>$U_{CC} = 5.5 V$ -1-0.4V $V_{OL}$ LOW-level output<br>voltage $V_1 = 0 V$ ; SDAn, SCLn pins; $V_{CC} = 5.5 V$ -1-0.4V $I_{U}$ input leakage currentSDAn, SCLn pins; $V_{CC} = 5.5 V$ -1-0.4V $System characteristics$ -SCL clock frequency(ຢ)0-0.4V $I_{U_I}$ input leakage currentSDAn, SCLn pins; $V_{CC} = 5.5 V$ -1-4.00kH $I_{U_I}$ input leakage currentSDAn, SCLn pins; $V_{CC} = 5.5 V$ -1-4.00kH $I_{U_I}$ input leakage currentSDAn, SCLn pins; $V_{CC} = 5.5 V$ -1-4.00kH $I_{U_I}$ input leakage currentSDAn, SCLn pins; $V_{CC} = 5.5 V$ -1-4.00kH $I_{U_I}$ input leakage currentSDAn, SCLn pins; $V_{CC} = 5.5 V$ -1-4.00kH $I_{U_I}$ ispectedSTARTGold4.00kH $I_{U_$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Symbol              | Parameter                             | Conditions                         |                  | Min                   | Тур | Max | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------|------------------------------------|------------------|-----------------------|-----|-----|------|

| Note:         Internation         V <sub>CC</sub> = 3.3 V         V <sub>CC</sub> = 3.3 V         V <sub>CC</sub> = 3.3 V         V <sub>CC</sub> = 100 PF ach side         Internation         Internatenand internation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Input-output        | ut connection                         |                                    |                  |                       |     |     |      |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V <sub>offset</sub> | offset voltage                        |                                    | <u>[1][7][9]</u> | 0                     | 110 | 175 | mV   |

| propagation delay10 k\Omega to V_{CC};<br>CL = 100 pF each side $C_{I(SCL/SDA)}$ SCL and SDA input<br>capacitance $(1 - 5 7 pF)$ $V_{OL}$ LOW-level output<br>voltage $V_I = 0 V$ ; SDAn, SCLn pins; $(1 0 0.4 V)$ $I_{L1}$ input leakage currentSDAn, SCLn pins; $V_{CC} = 2.7 V$ $-1 - 1 - 1 P$ $I_{L1}$ input leakage currentSDAn, SCLn pins; $V_{CC} = 5.5 V - 1 - 1 P$ $+1 PA$ System characteristics $-1 - 1 P$ $+1 PA$ System characteristics $-1 P$ $-1 P$ $+1 PA$ Super bus free time between a<br>STOP and START<br>condition $(1 0 P - PA)$ $-1 PA$ $H_{D:STA}$ hold time (repeated)<br>START condition $(1 0 P - PA)$ $-1 PA$ $H_{D:STA}$ set-up time for a<br>repeated<br>START condition $(1 0 P - PA)$ $-1 PA$ $H_{D:STA}$ set-up time for a<br>stup time for a<br>stup time for a<br>STOP condition $(1 0 P - PA)$ $-1 PA$ $H_{D:DAT}$ data hold time $(1 0 P - PA)$ $-1 PA$ $H_{D:DAT}$ data set-up time $(1 0 P - PA)$ $-1 PA$ $L_{OW}$ LOW period of the<br>SCL clock $(1 0 P - PA)$ $-1 PA$ $H_{IGH}$ HIGH period of the<br>SCL clock $(1 0 P - PA)$ $-1 PA$ $t_{HIGH}$ HIGH period of the<br>SCL clock $(1 P P - PA)$ $-1 PA$ $t_{T}$ rise time of both SDA and<br>SCL signals $(1 P P - PA)$ $-1 PA$ $t_{T}$ rise time of both SDA $(1 P P - PA)$ $-1 PA$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | t <sub>PLH</sub>    |                                       | 10 k $\Omega$ to V <sub>CC</sub> ; |                  | -                     | 0   | -   | ns   |

| NocconfycapacitanceImage of the state of the sta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | t <sub>PHL</sub>    |                                       | 10 k $\Omega$ to V <sub>CC</sub> ; |                  | -                     | 70  | -   | ns   |

| voltage $l_{sink} = 3 \text{ mA; } V_{CC} = 2.7 \text{ V}$ $l_{L1}$ input leakage currentSDAn, SCLn pins; $V_{CC} = 5.5 \text{ V}$ $-1$ $ +1$ $\mu A$ System characteristicsfscLSCL clock frequency[4]0 $-$ 400kHtsu/Fbus free time between a<br>STOP and START<br>condition[4]1.3 $  \mu s$ tsu/STAhold time (repeated)<br>START condition[4]0.6 $  \mu s$ tsu/STAset-up time for a<br>repeated<br>START condition[4]0.6 $  \mu s$ tsu/STOset-up time for a<br>repeated<br>START condition[4]0.6 $  \mu s$ tsu/STOset-up time for<br>STOP condition[4]0.6 $  \mu s$ tsu/STOset-up time for<br>STOP condition[4]1.3 $  \mu s$ tsu/STOset-up time for<br>STOP condition[4]0.6 $  \mu s$ tsu/STOset-up time for<br>SCL clock[4]1.3 $  \mu s$ tumLMD period of the<br>SCL clock[4]1.3 $  \mu s$ tumLMGHHIGH period of the<br>SCL clock[4] $0.6$ $  \mu s$ tumfall time of both SDA and<br>SCL signals[4] $0.1 \times C_b$ $ 300$ nstumfall time of both SDA[4] $0.1 \times C_b$ $ 300$ ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $C_{i(SCL/SDA)}$    |                                       |                                    | <u>[4]</u>       | -                     | 5   | 7   | pF   |

| System characteristics $f_{SCL}$ SCL clock frequency[4] 0-400kH $t_{BUF}$ bus free time between a<br>STOP and START<br>condition[4] 1.3 $\mu_{SC}$ $t_{HD:STA}$ hold time (repeated)<br>START condition[4] 0.6 $\mu_{SC}$ $t_{SU:STA}$ set-up time for a<br>repeated<br>START condition[4] 0.6 $\mu_{SC}$ $t_{SU:STA}$ set-up time for a<br>repeated<br>STOP condition[4] 0.6 $\mu_{SC}$ $t_{HD:DAT}$ data hold time[4] 300ns $t_{SU:STO}$ set-up time for<br>STOP condition[4] 100-ns $t_{HO,DAT}$ data set-up time[4] 100-ns $t_{LOW}$ LOW period of the<br>SCL clock[4] 0.6 $\mu_{SC}$ $t_{HIGH}$ HIGH period of the<br>SCL clock[4] 0.6 $\mu_{SC}$ $t_{HIGH}$ HIGH period of the<br>SCL clock[4] 0.6 $\mu_{SC}$ $t_{r}$ fall time of both SDA and<br>SCL signals[4] 20 + 0.1 × C_b-300ns $t_r$ rise time of both SDA[4] 20 + 0.1 × C_b-300ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>OL</sub>     | •                                     |                                    | <u>[1]</u>       | 0                     | -   | 0.4 | V    |

| $f_{SCL}$ SCL clock frequency $(4)$ 0-400kH $t_{BUF}$ bus free time between a<br>STOP and START<br>condition $(4)$ $1.3$ $\mu_{SC}$ $t_{HD;STA}$ hold time (repeated)<br>START condition $(4)$ $0.6$ $\mu_{SC}$ $t_{SU,STA}$ set-up time for a<br>repeated<br>START condition $(4)$ $0.6$ $\mu_{SC}$ $t_{SU;STO}$ set-up time for a<br>STOP condition $(4)$ $0.6$ $\mu_{SC}$ $t_{HD;DAT}$ data hold time $(4)$ $300$ $ns$ $t_{LOW}$ LOW period of the<br>SCL clock $(4)$ $1.3$ $\mu_{SC}$ $t_{HIGH}$ HIGH period of the<br>SCL clock $(4)$ $0.6$ $\mu_{SC}$ $t_r$ rise time of both SDA and<br>SCL signals $(4)$ $0.6$ $\mu_{SC}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ILI                 | input leakage current                 | SDAn, SCLn pins; $V_{CC}$ = 5.5 V  |                  | -1                    | -   | +1  | μA   |

| Use the base free time between a<br>STOP and START<br>condition1.3 $\mu s$ $t_{HD,STA}$ hold time (repeated)<br>START condition[4]0.6 $\mu s$ $t_{START}$ set-up time for a<br>repeated<br>START condition[4]0.6 $\mu s$ $t_{SU,STA}$ set-up time for a<br>repeated<br>START condition[4]0.6 $\mu s$ $t_{SU,STA}$ set-up time for<br>STOP condition[4]0.6 $\mu s$ $t_{HD,DAT}$ data hold time[4]300ns $t_{LOW}$ LOW period of the<br>SCL clock[4]1.3 $\mu s$ $t_{HIGH}$ HIGH period of the<br>SCL clock[4]0.6 $\mu s$ $t_r$ fall time of both SDA and<br>SCL signals[4]20 + 0.1 × C_b-300ns $t_r$ rise time of both SDA[4]20 + 0.1 × C_b-300ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | System cha          | aracteristics                         |                                    |                  |                       |     |     |      |

| STOP and START<br>conditionSTOP and START<br>conditionSTOP and START<br>conditionSTART condition $4$ $0.6$ $  \mu s$ $t_{SU;STA}$ set-up time for a<br>repeated<br>START condition $4$ $0.6$ $  \mu s$ $t_{SU;STO}$ set-up time for<br>STOP condition $4$ $0.6$ $  \mu s$ $t_{HD;DAT}$ data hold time $4$ $300$ $  \mu s$ $t_{HD;DAT}$ data set-up time $4$ $100$ $  ns$ $t_{LOW}$ LOW period of the<br>SCL clock $4$ $1.3$ $  \mu s$ $t_{HIGH}$ HIGH period of the<br>SCL clock $4$ $0.6$ $  \mu s$ $t_r$ fall time of both SDA and<br>SCL signals $4$ $20 + 0.1 \times C_b$ $ 300$ ns $t_r$ rise time of both SDA $4$ $20 + 0.1 \times C_b$ $ 300$ ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | f <sub>SCL</sub>    | SCL clock frequency                   |                                    | [4]              | 0                     | -   | 400 | kHz  |

| INSUMSTART condition $t_{SU;STA}$ set-up time for a<br>repeated<br>START condition[4] 0.6 $\mu s$ $t_{SU;STO}$ set-up time for<br>STOP condition[4] 0.6 $\mu s$ $t_{HD;DAT}$ data hold time[4] 300ns $t_{SU;STO}$ data set-up time[4] 100ns $t_{SU;DAT}$ data set-up time[4] 1.3 $\mu s$ $t_{LOW}$ LOW period of the<br>SCL clock[4] 0.6 $\mu s$ $t_{HIGH}$ HIGH period of the<br>SCL clock[4] 0.6 $\mu s$ $t_{r}$ rise time of both SDA and<br>SCL signals[4] 20 + 0.1 × C_b-300ns $t_r$ rise time of both SDA[4] 18] 20 + 0.1 × C_b-300ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | t <sub>BUF</sub>    | STOP and START                        |                                    | <u>[4]</u>       | 1.3                   | -   | -   | μs   |

| repeated<br>START condition $t_{SU;STO}$ set-up time for<br>STOP condition[4] $0.6$ $\mu_s$ $t_{HD;DAT}$ data hold time[4] $300$ $ns$ $t_{SU;DAT}$ data set-up time[4] $100$ $ns$ $t_{LOW}$ LOW period of the<br>SCL clock[4] $1.3$ $\mu_s$ $t_{HIGH}$ HIGH period of the<br>SCL clock[4] $0.6$ $\mu_s$ $t_{f}$ fall time of both SDA and<br>SCL signals[4][8] $20 + 0.1 \times C_b$ - $300$ $ns$ $t_r$ rise time of both SDA[4][8] $20 + 0.1 \times C_b$ - $300$ $ns$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t <sub>hd;sta</sub> |                                       |                                    | <u>[4]</u>       | 0.6                   | -   | -   | μs   |

| STOP condition $t_{HD;DAT}$ data hold time[4] 300ns $t_{SU;DAT}$ data set-up time[4] 100ns $t_{LOW}$ LOW period of the<br>SCL clock[4] 1.3 $\mu_s$ $t_{HIGH}$ HIGH period of the<br>SCL clock[4] 0.6 $\mu_s$ $t_{f}$ fall time of both SDA and<br>SCL signals[4][8] $20 + 0.1 \times C_b$ -300ns $t_r$ rise time of both SDA[4][8] $20 + 0.1 \times C_b$ -300ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | t <sub>su;sta</sub> | repeated                              |                                    | <u>[4]</u>       | 0.6                   | -   | -   | μs   |

| tsu;DATdata set-up timeImage: Market                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | t <sub>SU;STO</sub> | •                                     |                                    | <u>[4]</u>       | 0.6                   | -   | -   | μs   |

| $t_{LOW} = LOW \text{ period of the SCL clock} = \frac{41}{1.3} - \frac{1}{20} + \frac{1}{20$ | t <sub>HD;DAT</sub> | data hold time                        |                                    | [4]              | 300                   | -   | -   | ns   |

| SCL clock $t_{HIGH}$ HIGH period of the<br>SCL clock[4]0.6 $\mu$ s $t_{f}$ fall time of both SDA and<br>SCL signals[4][8]20 + 0.1 × C_b-300ns $t_{r}$ rise time of both SDA[4][8]20 + 0.1 × C_b-300ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t <sub>SU;DAT</sub> | data set-up time                      |                                    |                  |                       | -   | -   | ns   |

| SCL clock[4][8] $20 + 0.1 \times C_b$ -300nstrfall time of both SDA and<br>SCL signals[4][8] $20 + 0.1 \times C_b$ -300nstrrise time of both SDA[4][8] $20 + 0.1 \times C_b$ -300ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | t <sub>LOW</sub>    |                                       |                                    | [4]              | 1.3                   | -   | -   | μs   |

| SCL signals         418         20 + 0.1 × Cb         -         300         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | t <sub>HIGH</sub>   | •                                     |                                    | <u>[4]</u>       | 0.6                   | -   | -   | μs   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | t <sub>f</sub>      |                                       |                                    | [4][8]           | $20 + 0.1 \times C_b$ | -   | 300 | ns   |