Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### INTEGRATED CIRCUITS

## DATA SHEET

# PCA9556 Octal SMBus and I<sup>2</sup>C registered interface

Product data Supersedes data of 2000 Nov 13

## Octal SMBus and I<sup>2</sup>C registered interface

PCA9556

#### **FEATURES**

- SMBus compliance with fixed 3.3V voltage levels

- Operating power supply voltage range of 3.0 V − 5.5 V

- Active high polarity inverter register

- Each I/O is configurable as an input or output

- Active low reset pin

- Low leakage current on power-down

- Noise filter on SCL/SDA inputs

- No glitch on power-up

- Internal power-on reset

- 8 I/O pins which default to 8 inputs

- High impedance open drain on I/O0

- ESD protection exceeds 2000 V HBM per JESD22-A114,

200 V MM per JESD22-A115 and 1000 V CDM per JESD22-C101

- Latch-up testing is done to JESDEC Standard JESD78 which exceeds 100 mA

#### **DESCRIPTION**

The PCA9556 is a silicon CMOS circuit which provides parallel input/output expansion for SMBus applications. The PCA9556 consists of an 8-bit input port register, 8-bit output port register, and an SMBus interface. It has low current consumption and a high impedance open drain output pin, I/O0.

The SMBus system master can reset the PCA9556 in the event of a timeout by asserting a LOW on the reset input. The SMBus system master can also invert the PCA9556 inputs by writing to the active HIGH polarity inversion bits. Finally, the system master can enable the PCA9556's I/Os as either inputs or outputs by writing to the configuration register.

The power-on reset puts the registers in their default state and initializes the SMBus state machine. The RESET pin causes the same reset/initialization to occur without depowering the part.

The PCA9557 8-bit I<sup>2</sup>C SMBus I/O port with reset is the higher performance pin-for-pin replacement for the PCA9556.

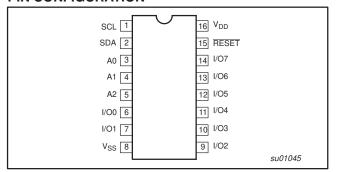

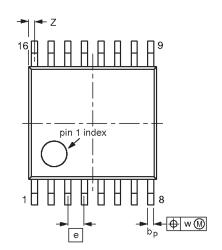

#### **PIN CONFIGURATION**

Figure 1. Pin configuration

#### **PIN DESCRIPTION**

| PIN<br>NUMBER | SYMBOL          | FUNCTION                    |

|---------------|-----------------|-----------------------------|

| 1             | SCL             | Serial clock line           |

| 2             | SDA             | Serial data line            |

| 3             | A0              | Address input 0             |

| 4             | A1              | Address input 1             |

| 5             | A2              | Address input 2             |

| 6             | I/O0            | I/O0 (open drain)           |

| 7             | I/O1            | I/O1                        |

| 8             | V <sub>SS</sub> | Supply GROUND               |

| 9–14          | I/O2–I/O7       | I/O2 to I/O7                |

| 15            | RESET           | External reset (active LOW) |

| 16            | $V_{DD}$        | Supply voltage              |

#### ORDERING INFORMATION

| PACKAGES             | TEMPERATURE RANGE | ORDER CODE | DRAWING NUMBER |

|----------------------|-------------------|------------|----------------|

| 16-Pin Plastic TSSOP | -40 to +85 °C     | PCA9556PW  | SOT403-1       |

Standard packing quantities and other packaging data is available at www.philipslogic.com/packaging. SMBus as specified by the Smart Battery System Implementers Forum is a derivative of the Philips I<sup>2</sup>C patent. I<sup>2</sup>C is a trademark of Philips Semiconductors Corporation.

## Octal SMBus and I<sup>2</sup>C registered interface

PCA9556

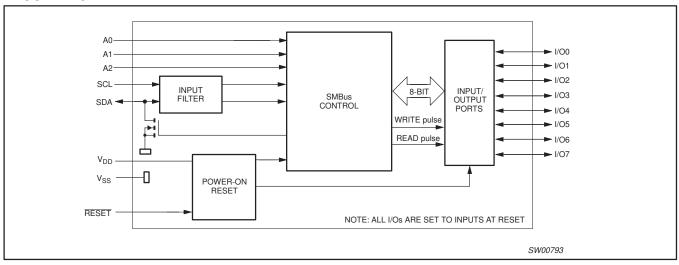

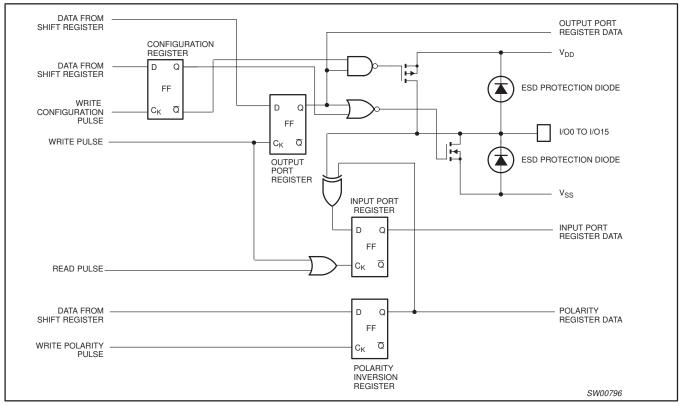

#### **BLOCK DIAGRAM**

Figure 2. Block diagram

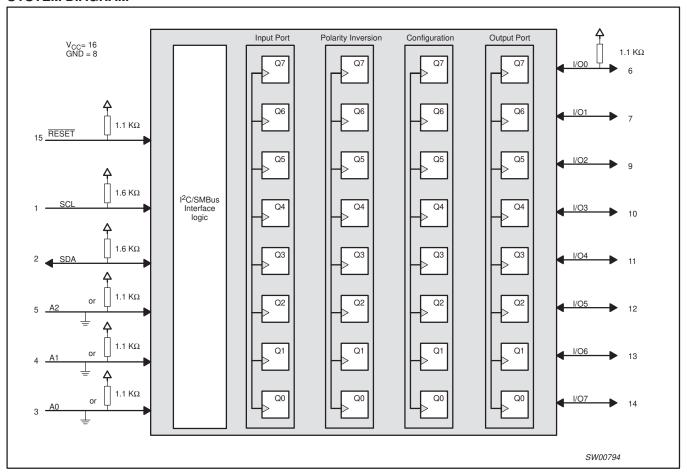

#### **SYSTEM DIAGRAM**

Figure 3. System diagram

## Octal SMBus and I<sup>2</sup>C registered interface

PCA9556

#### **REGISTERS**

#### **Command Byte**

| Command | Protocol        | Function                    |

|---------|-----------------|-----------------------------|

| 0       | Read byte       | Input port register         |

| 1       | Read/write byte | Output port register        |

| 2       | Read/write byte | Polarity inversion register |

| 3       | Read/write byte | Configuration register      |

The command byte is the first byte to follow the address byte during a write transmission. It is used as a pointer to determine which of the following registers will be written or read.

#### Register 0 — Input Port Register

| 17 | 16 | 15 | 14 | 13 | 12 | l1 | 10 |

|----|----|----|----|----|----|----|----|

This register is an read-only port. It reflects the incoming logic levels of the pins, regardless of whether the pin is defined as an input or an output by register 3. Writes to this register have no effect.

#### Register 1 — Output Port Register

| Ī | bit     | 07 | O6 | O5 | O4 | О3 | O2 | 01 | 00 |

|---|---------|----|----|----|----|----|----|----|----|

| ľ | default | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

This register reflects the outgoing logic levels of the pins defined as outputs by register 3. Bit values in this register have no effect on pins defined as inputs. In turn, reads from this register reflect the value that is in the flip-flop controlling the output selection, NOT the actual pin value.

#### Register 2 — Polarity Inversion Register

| bit     | N7 | N6 | N5 | N4 | N3 | N2 | N1 | N0 |

|---------|----|----|----|----|----|----|----|----|

| default | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0  |

This register enables polarity inversion of pins defined as inputs by register 3. If a bit in this register is set (written with '1'), the corresponding port pin's polarity is inverted. If a bit in this register is cleared (written with a '0'), the corresponding port pin's original polarity is retained.

#### Register 3 — Configuration Register

| bit     | C7 | C6 | C5 | C4 | C3 | C2 | C1 | C0 |

|---------|----|----|----|----|----|----|----|----|

| default | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

This register configures the directions of the I/O pins. If a bit in this register is set, the corresponding port pin is enabled as an input with high impedance output driver. If a bit in this register is cleared, the corresponding port pin is enabled as an output.

#### **RESET**

#### **Power-on Reset**

When power is applied to  $V_{DD}$ , an internal power-on reset holds the PCA9556 in a reset state until  $V_{DD}$  has reached  $V_{POR}$ . At that point, the reset condition is released and the PCA9556 registers and SMBus state machine will initialize to their default states.

#### **External Reset**

A reset can be accomplished by holding the RESET pin low for a minimum of  $T_W$ . The PCA9556 registers and SMBus/I²C state machine will be held in their default state until the RESET input is once again high. This input typically requires a pull-up to 3.3 V V $_{\rm CC}$ .

## Octal SMBus and I<sup>2</sup>C registered interface

PCA9556

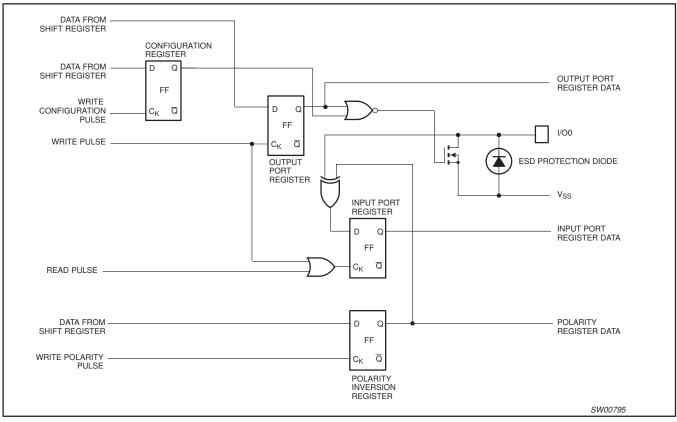

#### SIMPLIFIED SCHEMATIC OF I/O0

NOTE: On power-up or reset, all registers return to default values.

Figure 4. Simplified schematic of I/O0

## Octal SMBus and I<sup>2</sup>C registered interface

PCA9556

#### SIMPLIFIED SCHEMATIC OF I/O1 TO I/O7

NOTE: On power–up or reset, all registers return to default values.

Figure 5. Simplified schematic of I/O1 to I/O7  $\,$

## Octal SMBus and I<sup>2</sup>C registered interface

PCA9556

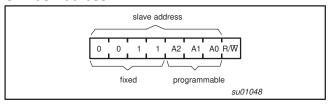

#### **SMBus Address**

Figure 6. PCA9556 address

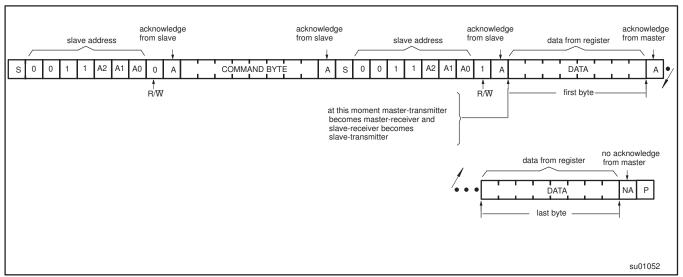

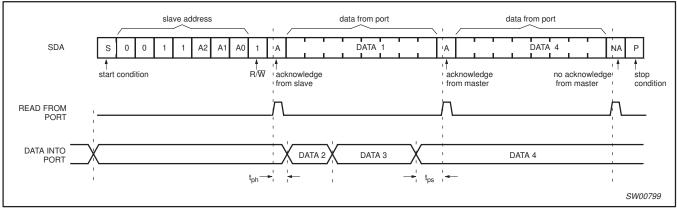

#### **SMBus Transactions**

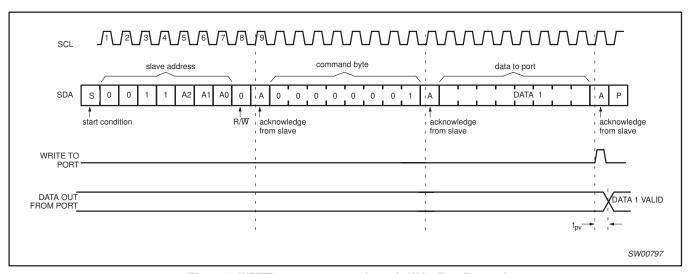

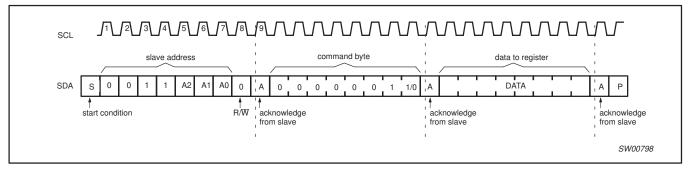

Data is transmitted to the PCA9556 registers using Write Byte transfers (see Figures 7 and 8). Data is read from the PCA9556 registers using Read and Receive Byte transfers (see Figures 9 and 10).

Figure 7. WRITE to output port register via Write Byte Protocol

Figure 8. WRITE to I/O configuration or polarity inversion registers via Write Byte Protocol

## Octal SMBus and I<sup>2</sup>C registered interface

PCA9556

Figure 9. READ from register via Read byte protocol

#### NOTES:

- 1. This figure assumes the command byte has previously been programmed with 00h.

- 2. Transfer of data can be stopped at any moment by a stop condition. When this occurs, data present at the last acknowledge phase is valid (output mode). Input data is lost.

Figure 10. READ input port register via Receive byte protocol

## Octal SMBus and I<sup>2</sup>C registered interface

PCA9556

#### **ABSOLUTE MAXIMUM RATINGS**

In accordance with the Absolute Maximum Rating System (IEC 134).

| SYMBOL            | PARAMETER                                        | CONDITIONS | MIN                   | MAX                   | UNIT |

|-------------------|--------------------------------------------------|------------|-----------------------|-----------------------|------|

| V <sub>DD</sub>   | Supply voltage                                   |            | -0.5                  | +6                    | V    |

| V <sub>I</sub>    | Input voltage                                    |            | V <sub>SS</sub> - 0.5 | V <sub>DD</sub> + 0.5 | V    |

| ΙΙ                | DC input current                                 |            | _                     | ± 20                  | mA   |

| V <sub>I/O</sub>  | DC voltage on an I/O as an input other than I/O0 |            | V <sub>SS</sub> - 0.5 | V <sub>DD</sub> + 0.5 | V    |

| V <sub>I/O0</sub> | DC voltage on I/O0 as an input                   |            | V <sub>SS</sub> - 0.5 | 4.6                   | V    |

|                   | DC input quirent on 1/00                         |            | _                     | +400                  | μΑ   |

| 1/00              | DC input current on I/O0                         |            | _                     | -20                   | mA   |

| I <sub>I/O</sub>  | DC output current on an I/O                      |            | _                     | ± 20                  | mA   |

| P <sub>tot</sub>  | Total power dissipation                          |            | _                     | _                     | mW   |

| Po                | Power dissipation per output                     |            | _                     | _                     | mW   |

| T <sub>stg</sub>  | Storage temperature range                        |            | -65                   | +150                  | °C   |

| T <sub>amb</sub>  | Operating ambient temperature                    |            | -40                   | +85                   | °C   |

#### **HANDLING**

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is desirable to take precautions appropriate to handling MOS devices. Advice can be found in Data Handbook IC24 under "Handling MOS devices".

## Octal SMBus and I<sup>2</sup>C registered interface

PCA9556

#### **DC CHARACTERISTICS**

$V_{DD}$  = 3.0 to 5.5 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -40 to +85 °C; unless otherwise specified.

| OVMDOL                | DADAMETED                                                            | CONDITIONS                                                                                                  | Vı       | <sub>DD</sub> = 3.3 | V                        | ١        | / <sub>DD</sub> = 5 | V                        |      |

|-----------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------|---------------------|--------------------------|----------|---------------------|--------------------------|------|

| SYMBOL                | PARAMETER                                                            | CONDITIONS                                                                                                  | MIN      | TYP                 | MAX                      | MIN      | TYP                 | MAX                      | UNIT |

| Supplies              | -                                                                    | -                                                                                                           |          |                     |                          |          |                     |                          |      |

| $V_{DD}$              | Supply voltage                                                       |                                                                                                             | 3.0      | _                   | 3.6                      | 4.5      |                     | 5.5                      | ٧    |

| I <sub>DD</sub>       | Supply current                                                       | Operating mode; no load;<br>$V_I = V_{DD}$ or $V_{SS}$ ;<br>$f_{SCL} = 100$ kHz                             |          | 300                 | 425                      | _        | 1100                | 1500                     | μА   |

| I <sub>stb</sub>      | Standby current                                                      | Standby mode; no load;<br>V <sub>I</sub> = V <sub>DD</sub> or V <sub>SS</sub> ;<br>f <sub>SCL</sub> = 0 kHz | _        | 25                  | 50                       | -        | 65                  | 100                      | μА   |

| V <sub>POR</sub>      | Power-on reset voltage                                               | $V_{DD} = 3.3 \text{ V}$ ; no load;<br>$V_{I} = V_{DD} \text{ or } V_{SS}$ ; note 1                         | _        | 1.3                 | 2.4                      | -        | 1.3                 | 2.4                      | ٧    |

| Input SCL;            | input/output SDA                                                     |                                                                                                             |          |                     |                          |          |                     |                          |      |

| $V_{IL}$              | LOW level input voltage                                              |                                                                                                             | -0.5     | _                   | 0.8                      | -0.5     | _                   | 0.8                      | V    |

| V <sub>IH</sub>       | HIGH level input voltage                                             |                                                                                                             | 2.1      | _                   | 5.5                      | 2.1      | _                   | 5.5                      | V    |

| I <sub>OL</sub>       | LOW level output current                                             | V <sub>OL</sub> = 0.4 V                                                                                     | 3        | _                   | -                        | 3        | _                   | _                        | mA   |

| ΙL                    | Leakage current                                                      | $V_I = V_{DD} = V_{SS}$                                                                                     | -1       | <u> </u>            | +1                       | -1       | _                   | +1                       | μΑ   |

| C <sub>I</sub>        | Input capacitance                                                    | $V_I = V_{SS}$                                                                                              | <b>—</b> | _                   | 10                       | _        | _                   | 10                       | pF   |

| I/Os                  | •                                                                    |                                                                                                             | -        |                     |                          |          |                     |                          |      |

| V <sub>IL</sub>       | LOW level input voltage                                              |                                                                                                             | -0.5     | _                   | 0.8                      | -0.5     |                     | 0.8                      | V    |

| V <sub>IH</sub>       | HIGH level input voltage                                             |                                                                                                             | 2.0      | _                   | V <sub>DD</sub><br>+ 0.5 | 2.0      | _                   | V <sub>DD</sub><br>+ 0.5 | V    |

| I <sub>IHL(max)</sub> | Maximum allowed input current through protection diode (I/O1 – I/O7) | $V_I \ge V_{DD}$ or $V_I \le V_{SS}$                                                                        | _        | _                   | ±400                     | _        | _                   | ±400                     | μА   |

| I <sub>OL</sub>       | LOW level output current                                             | $V_{OL} = 0.55 \text{ V}; V_{DD} = 3.3 \text{ V};$<br>note 2                                                | 8        | 10                  | _                        | 8        | 10                  | _                        | mA   |

|                       | HIGH level output current except I/O0                                | $V_{OH} = 2.4 \text{ V}; V_{DD} = 3.3 \text{ V};$<br>note 3                                                 | 4        | _                   | _                        | 4        | _                   | _                        | mA   |

| I <sub>OH</sub>       | LUCILIaval autaut augent en 1/00                                     | $V_{DD} = 3.6 \text{ V}; V_{OH} = 4.6 \text{ V}$                                                            |          | _                   | 1                        | _        | _                   | 1                        |      |

|                       | HIGH level output current on I/O0                                    | $V_{DD} = 0 \text{ V}; V_{OH} = 3.3 \text{ V}$                                                              | Τ-       |                     | 1                        | _        |                     | 1                        | μΑ   |

| ΙL                    | Input leakage current                                                | $V_{DD} = 3.6 \text{ V}; V_{I} = 0 \text{ or } V_{DD}$                                                      | -1       | <u> </u>            | 1                        | -1       | _                   | 1                        | μΑ   |

| C <sub>I</sub>        | Input capacitance                                                    |                                                                                                             | T        | <u> </u>            | 10                       | <u> </u> |                     | 10                       | pF   |

| Co                    | Output capacitance                                                   |                                                                                                             | Τ-       | —                   | 10                       | <u> </u> |                     | 10                       | pF   |

| Select Inpu           | uts A0, A1, A2, and RESET                                            |                                                                                                             |          |                     |                          |          |                     |                          |      |

| $V_{IL}$              | LOW level input voltage                                              |                                                                                                             | -0.5     | _                   | 0.8                      | -0.5     | _                   | 0.8                      | V    |

| V <sub>IH</sub>       | HIGH level input voltage                                             |                                                                                                             | 2.0      | _                   | V <sub>DD</sub><br>+ 0.5 | 2.0      |                     | V <sub>DD</sub><br>+ 0.5 | V    |

| ILI                   | Input leakage current                                                |                                                                                                             | -1       |                     | 1                        | -1       | <u> </u>            | 1                        | μА   |

#### NOTES:

- The power-on reset circuit resets the SMBus logic with V<sub>DD</sub> < V<sub>POR</sub> and sets all I/Os to their default values.

The maximum total sink current must be limited to 54 mA at +85 °C, and 80 mA at +70 °C.

The maximum total source current must be limited to 54 mA at +85 °C, and 80 mA at +70 °C.

## Octal SMBus and I<sup>2</sup>C registered interface

PCA9556

#### **AC SPECIFICATIONS**

| SYMBOL              | PARAMETER                                       | LIM | ITS  | UNITS |

|---------------------|-------------------------------------------------|-----|------|-------|

| STWBOL              | PANAMETEN                                       | MIN | MAX  | UNITS |

| f <sub>SBM</sub>    | SMB operating frequency                         | 10  | 100  | KHz   |

| t <sub>BUF</sub>    | Bus free time between stop and start conditions | 4.7 | _    | μs    |

| t <sub>HO:STA</sub> | Hold time after (repeated) start condition      | 4.0 | _    | μs    |

| tsu:sta             | Repeated start condition setup time             | 4.7 | _    | μs    |

| t <sub>HO:DAT</sub> | Data hold time                                  | 300 | _    | ns    |

| t <sub>SU:DAT</sub> | Data setup time                                 | 250 | _    | ns    |

| t <sub>LOW</sub>    | Clock LOW period                                | 4.7 | _    | μs    |

| <sup>t</sup> HIGH   | Clock HIGH period                               | 4.0 | _    | μs    |

| t <sub>F</sub>      | Clock/Data fall time                            | _   | 300  | ns    |

| t <sub>R</sub>      | Clock/Data rise time                            | _   | 1000 | ns    |

| Port Timing         |                                                 |     |      |       |

| t <sub>PV</sub>     | Output data valid                               | _   | 4    | μs    |

| t <sub>PS</sub>     | Input data setup time                           | 0   | _    | μs    |

| t <sub>PH</sub>     | Input data hold time                            | 4   | _    | μs    |

| Reset               |                                                 |     |      |       |

| t <sub>W</sub>      | Reset pulse width                               | 2   | _    | ns    |

## Octal SMBus and I<sup>2</sup>C registered interface

PCA9556

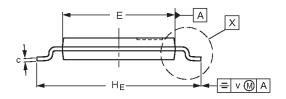

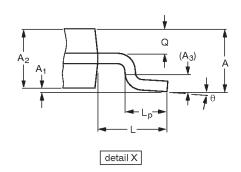

TSSOP16: plastic thin shrink small outline package; 16 leads; body width 4.4 mm

SOT403-1

#### DIMENSIONS (mm are the original dimensions)

| UNIT | A<br>max. | Α1           | A <sub>2</sub> | Α3   | bp           | O          | D <sup>(1)</sup> | E <sup>(2)</sup> | e    | HE         | L   | Lp           | Q          | v   | w    | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|--------------|----------------|------|--------------|------------|------------------|------------------|------|------------|-----|--------------|------------|-----|------|-----|------------------|----------|

| mm   | 1.10      | 0.15<br>0.05 | 0.95<br>0.80   | 0.25 | 0.30<br>0.19 | 0.2<br>0.1 | 5.1<br>4.9       | 4.5<br>4.3       | 0.65 | 6.6<br>6.2 | 1.0 | 0.75<br>0.50 | 0.4<br>0.3 | 0.2 | 0.13 | 0.1 | 0.40<br>0.06     | 8°<br>0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER  | RENCES | EUROPEAN   | ISSUE DATE                       |

|----------|-----|--------|--------|------------|----------------------------------|

| VERSION  | IEC | JEDEC  | EIAJ   | PROJECTION | 1550E DATE                       |

| SOT403-1 |     | MO-153 |        |            | <del>-95-04-04</del><br>99-12-27 |

### Octal SMBus and I<sup>2</sup>C registered interface

PCA9556

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specifications defined by Philips. This specification can be ordered using the code 9398 393 40011.

#### Data sheet status

| Data sheet status <sup>[1]</sup> | Product<br>status <sup>[2]</sup> | Definitions                                                                                                                                                                                                                                                                                                            |

|----------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective data                   | Development                      | This data sheet contains data from the objective specification for product development.  Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                                           |

| Preliminary data                 | Qualification                    | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.                                     |

| Product data                     | Production                       | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Changes will be communicated according to the Customer Product/Process Change Notification (CPCN) procedure SNW-SQ-650A. |

<sup>[1]</sup> Please consult the most recently issued data sheet before initiating or completing a design.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

**Limiting values definition** — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

**Life support** — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

#### Contact information

For additional information please visit

http://www.semiconductors.philips.com. Fax: +31 40 27 24825

For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com.

© Koninklijke Philips Electronics N.V. 2002 All rights reserved. Printed in U.S.A.

Date of release: 03-02

Document order number: 9397 750 09609

Let's make things better.

Philips Semiconductors

<sup>[2]</sup> The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.