# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Rev. 8 — 19 December 2014

**Product data sheet**

#### **General description** 1.

The PCF2127 is a CMOS<sup>1</sup> Real Time Clock (RTC) and calendar with an integrated Temperature Compensated Crystal (Xtal) Oscillator (TCXO) and a 32.768 kHz quartz crystal optimized for very high accuracy and very low power consumption. The PCF2127 has 512 bytes of general-purpose static RAM, a selectable I<sup>2</sup>C-bus or SPI-bus, a backup battery switch-over circuit, a programmable watchdog function, a timestamp function, and many other features.

For a selection of NXP Real-Time Clocks, see Table 94 on page 89

#### **Features and benefits** 2.

- UL Recognized Component

- Operating temperature range from –40 °C to +85 °C

- Temperature Compensated Crystal Oscillator (TCXO) with integrated capacitors

- Typical accuracy:

- PCF2127AT: ±3 ppm from –15 °C to +60 °C

- PCF2127T: ±3 ppm from –30 °C to +80 °C

- Integration of a 32.768 kHz guartz crystal and oscillator in the same package

- Provides year, month, day, weekday, hours, minutes, seconds, and leap year correction

- 512 bytes of general-purpose static RAM

- Timestamp function

- with interrupt capability

- detection of two different events on one multilevel input pin (for example, for tamper detection)

- Two line bidirectional 400 kHz Fast-mode I<sup>2</sup>C-bus interface

- 3 line SPI-bus with separate data input and output (maximum speed 6.5 Mbit/s)

- Battery backup input pin and switch-over circuitry

- Battery backed output voltage

- Battery low detection function

- Extra power fail detection function with input and output pins

- Power-On Reset Override (PORO)

- Oscillator stop detection function

- Interrupt output (open-drain)

The definition of the abbreviations and acronyms used in this data sheet can be found in Section 21. 1.

- Programmable 1 second or 1 minute interrupt

- Programmable watchdog timer with interrupt

- Programmable alarm function with interrupt capability

- Programmable square wave output pin

- Programmable countdown timer with interrupt

- Clock operating voltage: 1.8 V to 4.2 V

- Low supply current: typical 0.70 μA at V<sub>DD</sub> = 3.3 V

#### **Applications** 3.

- Electronic metering for electricity, water, and gas

- Precision timekeeping

- Access to accurate time of the day

- GPS equipment to reduce time to first fix

- Applications that require an accurate process timing

- Products with long automated unattended operation time

#### **Ordering information** 4.

#### Table 1. **Ordering information**

| Type number | Package | Package                                                       |          |  |  |  |  |  |

|-------------|---------|---------------------------------------------------------------|----------|--|--|--|--|--|

|             | Name    | Description                                                   | Version  |  |  |  |  |  |

| PCF2127AT   | SO20    | plastic small outline package; 20 leads;<br>body width 7.5 mm | SOT163-1 |  |  |  |  |  |

| PCF2127T    | SO16    | plastic small outline package; 16 leads;<br>body width 7.5 mm | SOT162-1 |  |  |  |  |  |

## 4.1 Ordering options

#### Table 2. **Ordering options**

| Product type number | Orderable part number | Sales item<br>(12NC) | Delivery form                    | IC<br>revision |

|---------------------|-----------------------|----------------------|----------------------------------|----------------|

| PCF2127AT/2         | PCF2127AT/2Y          | 935299867518         | tape and reel, 13 inch, dry pack | 2              |

| PCF2127T/2          | PCF2127T/2Y           | 935299866518         | tape and reel, 13 inch, dry pack | 2              |

#### **Marking** 5.

#### Table 3. Marking codes

| Product type number | Marking code |

|---------------------|--------------|

| PCF2127AT/2         | PCF2127AT    |

| PCF2127T/2          | PCF2127T     |

PCF2127 Product data sheet

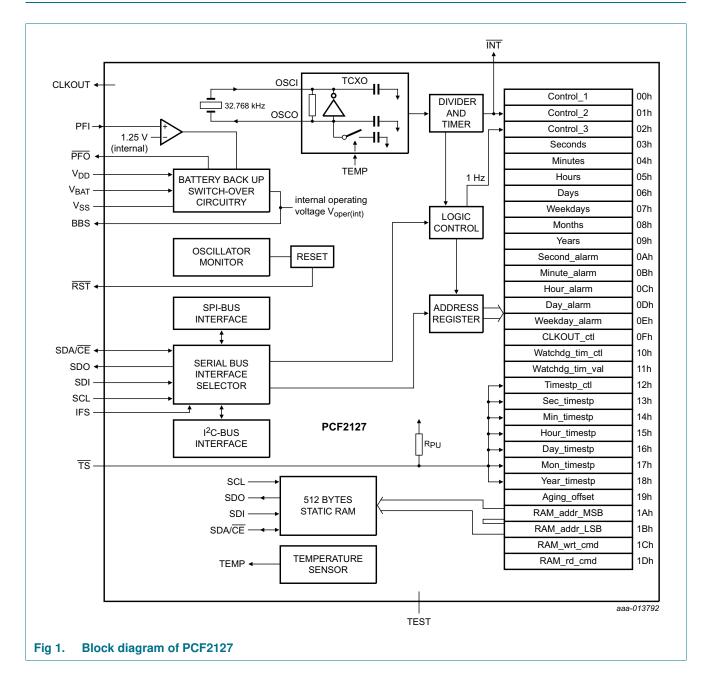

## 6. Block diagram

## 7. Pinning information

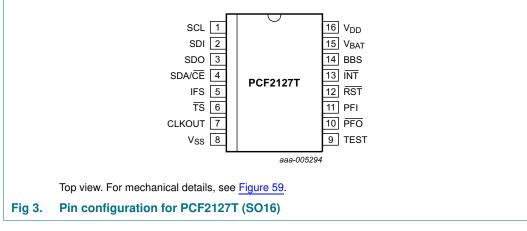

## 7.1 Pinning

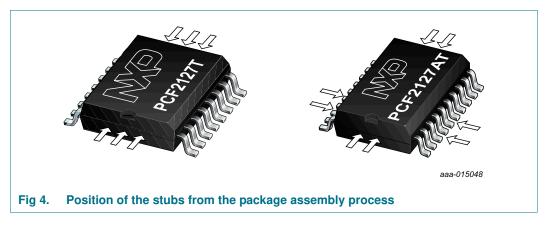

After lead forming and cutting, there remain stubs from the package assembly process. These stubs are present at the edge of the package as illustrated in <u>Figure 4</u>. The stubs are at an electrical potential. To avoid malfunction of the PCF2127, it has to be ensured that they are not shorted with another electrical potential (e.g. by condensation).

## 7.2 Pin description

#### Table 4. Pin description of PCF2127

Input or input/output pins must always be at a defined level (V<sub>SS</sub> or V<sub>DD</sub>) unless otherwise specified.

| Symbol           | Pin       |          | Description                                                                                                           |

|------------------|-----------|----------|-----------------------------------------------------------------------------------------------------------------------|

|                  | PCF2127AT | PCF2127T |                                                                                                                       |

| SCL              | 1         | 1        | combined serial clock input for both I <sup>2</sup> C-bus and SPI-bus                                                 |

| SDI              | 2         | 2        | serial data input for SPI-bus                                                                                         |

|                  |           |          | connect to pin V <sub>SS</sub> if I <sup>2</sup> C-bus is selected                                                    |

| SDO              | 3         | 3        | serial data output for SPI-bus, push-pull                                                                             |

| SDA/CE           | 4         | 4        | combined serial data input and output for the I <sup>2</sup> C-bus and chip enable input (active LOW) for the SPI-bus |

| IFS              | 5         | 5        | interface selector input                                                                                              |

|                  |           |          | connect to pin $V_{SS}$ to select the SPI-bus                                                                         |

|                  |           |          | connect to pin BBS to select the I <sup>2</sup> C-bus                                                                 |

| TS               | 6         | 6        | timestamp input (active LOW) with 200 $k\Omega$ internal pull-up resistor ( $R_{PU})$                                 |

| CLKOUT           | 7         | 7        | clock output (open-drain)                                                                                             |

| V <sub>SS</sub>  | 8         | 8        | ground supply voltage                                                                                                 |

| n.c.             | 9 to 12   | -        | not connected; do not connect; do not use as feed through                                                             |

| TEST             | 13        | 9        | do not connect; do not use as feed through                                                                            |

| PFO              | 14        | 10       | power fail output (open-drain; active LOW)                                                                            |

| PFI              | 15        | 11       | power fail input                                                                                                      |

| RST              | 16        | 12       | reset output (open-drain; active LOW)                                                                                 |

| INT              | 17        | 13       | interrupt output (open-drain; active LOW)                                                                             |

| BBS              | 18        | 14       | output voltage (battery backed)                                                                                       |

| V <sub>BAT</sub> | 19        | 15       | battery supply voltage (backup)                                                                                       |

|                  |           |          | connect to $V_{\mbox{\scriptsize SS}}$ if battery switch-over is not used                                             |

| V <sub>DD</sub>  | 20        | 16       | supply voltage                                                                                                        |

## 8. Functional description

The PCF2127 is a Real Time Clock (RTC) and calendar with an on-chip Temperature Compensated Crystal (Xtal) Oscillator (TCXO) and a 32.768 kHz quartz crystal integrated into the same package (see <u>Section 8.3.3</u>).

Address and data are transferred by a selectable 400 kHz Fast-mode I<sup>2</sup>C-bus or a 3 line SPI-bus with separate data input and output (see <u>Section 9</u>). The maximum speed of the SPI-bus is 6.5 Mbit/s.

The PCF2127 has a backup battery input pin and backup battery switch-over circuit which monitors the main power supply. The backup battery switch-over circuit automatically switches to the backup battery when a power failure condition is detected (see <u>Section 8.6.1</u>). Accurate timekeeping is maintained even when the main power supply is interrupted.

A battery low detection circuit monitors the status of the battery (see <u>Section 8.6.2</u>). When the battery voltage drops below a certain threshold value, a flag is set to indicate that the battery must be replaced soon. This ensures the integrity of the data during periods of battery backup.

### 8.1 Register overview

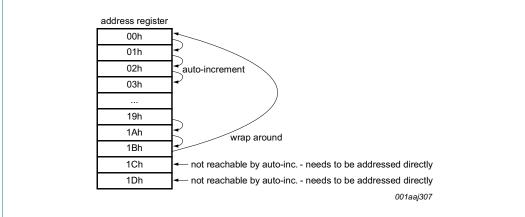

The PCF2127 contains an auto-incrementing address register: the built-in address register will increment automatically after each read or write of a data byte up to the register 1Bh. After register 1Bh, the auto-incrementing will wrap around to address 00h (see Figure 5).

#### Fig 5. Handling address registers

- The first three registers (memory address 00h, 01h, and 02h) are used as control registers (see <u>Section 8.2</u>).

- The memory addresses 03h through to 09h are used as counters for the clock function (seconds up to years). The date is automatically adjusted for months with fewer than 31 days, including corrections for leap years. The clock can operate in 12-hour mode with an AM/PM indication or in 24-hour mode (see Section 8.9).

- The registers at addresses 0Ah through 0Eh define the alarm function. It can be selected that an interrupt is generated when an alarm event occurs (see <u>Section 8.10</u>).

PCF2127

- The register at address 0Fh defines the temperature measurement period and the clock out mode. The temperature measurement can be selected from every 4 minutes (default) down to every 30 seconds (see <u>Table 14</u>). CLKOUT frequencies of 32.768 kHz (default) down to 1 Hz for use as system clock, microcontroller clock, and so on, can be chosen (see <u>Table 15</u>).

- The registers at addresses 10h and 11h are used for the watchdog and countdown timer functions. The watchdog timer has four selectable source clocks allowing for timer periods from less than 1 ms to greater than 4 hours (see <u>Table 58</u>). Either the watchdog timer **or** the countdown timer can be enabled (see <u>Section 8.11</u>). For the watchdog timer, it is possible to select whether an interrupt or a pulse on the reset pin is generated when the watchdog times out. For the countdown timer, it is only possible that an interrupt is generated at the end of the countdown.

- The registers at addresses 12h to 18h are used for the timestamp function. When the trigger event happens, the actual time is saved in the timestamp registers (see <u>Section 8.12</u>).

- The register at address 19h is used for the correction of the crystal aging effect (see <u>Section 8.4.1</u>).

- The registers at addresses 1Ah and 1Bh define the RAM address. The register at address 1Ch (RAM\_wrt\_cmd) is the RAM write command; register 1Dh (RAM\_rd\_cmd) is the RAM read command. Data is transferred to or from the RAM by the serial interface (see <u>Section 8.5</u>).

- The registers Seconds, Minutes, Hours, Days, Months, and Years are all coded in Binary Coded Decimal (BCD) format to simplify application use. Other registers are either bit-wise or standard binary.

When one of the RTC registers is written or read, the content of all counters is temporarily frozen. This prevents a faulty writing or reading of the clock and calendar during a carry condition (see <u>Section 8.9.8</u>).

**PCF2127**

Table 5.

Register overview

Bit positions labeled as - are not implemented and return 0 when read. Bits labeled as T must always be written with logic 0. Bits labeled as X are undefined at

power-on and unchanged by subsequent resets.

| Address                                                                  | Register name    | Bit          |          |       |         |              |                |             |            | Reset value | Reference           |

|--------------------------------------------------------------------------|------------------|--------------|----------|-------|---------|--------------|----------------|-------------|------------|-------------|---------------------|

|                                                                          |                  | 7            | 6        | 5     | 4       | 3            | 2              | 1           | 0          |             |                     |

| Control re                                                               | gisters          |              |          |       |         |              |                |             |            | -           |                     |

| 00h                                                                      | Control_1        | EXT_<br>TEST | Т        | STOP  | TSF1    | POR_<br>OVRD | 12_24          | MI          | SI         | 0000 1000   | Table 7 on page 10  |

| 01h                                                                      | Control_2        | MSF          | WDTF     | TSF2  | AF      | CDTF         | TSIE           | AIE         | CDTIE      | 0000 0000   | Table 9 on page 11  |

| 02h                                                                      | Control_3        | P            | NRMNG[2: | 0]    | BTSE    | BF           | BLF            | BIE         | BLIE       | 0000 0000   | Table 11 on page 12 |

| Time and                                                                 | date registers   |              |          |       |         |              |                |             |            |             |                     |

| 03h                                                                      | Seconds          | OSF          |          |       | SEC     | ONDS (0 to   | o 59)          |             |            | 1XXX XXXX   | Table 28 on page 30 |

| 04h<br>05h<br>06h<br>07h<br>08h<br>09h<br><b>Alarm reg</b><br>0Ah<br>0Bh | Minutes          | -            |          |       | MIN     | UTES (0 to   | 59)            |             |            | - XXX XXXX  | Table 31 on page 3  |

| 05h                                                                      | Hours            | -            | -        | AMPM  | ŀ       | HOURS (1     | to 12) in 12   | -hour mod   | e          | XX XXXX     | Table 33 on page 33 |

|                                                                          |                  |              |          |       | HOUF    | RS (0 to 23) | in 24-hour     | mode        |            | XX XXXX     |                     |

| 06h                                                                      | Days             | -            | -        |       |         | DAYS (       | 1 to 31)       |             |            | XX XXXX     | Table 35 on page 3  |

| 07h                                                                      | Weekdays         | -            | -        | -     | -       | -            | WEE            | KDAYS (0    | to 6)      | XXX         | Table 37 on page 33 |

| 08h                                                                      | Months           | -            | -        | -     |         | MO           | NTHS (1 to     | 12)         |            | X XXXX      | Table 40 on page 34 |

| 09h                                                                      | Years            |              |          |       | YEARS   | (0 to 99)    |                |             |            | XXXX XXXX   | Table 43 on page 3  |

| Alarm reg                                                                | isters           | 1            |          |       |         |              |                |             |            |             |                     |

| 0Ah                                                                      | Second_alarm     | AE_S         |          |       | SECON   | D_ALARM      | (0 to 59)      |             |            | 1XXX XXXX   | Table 45 on page 38 |

| 0Bh                                                                      | Minute_alarm     | AE_M         |          |       | MINUTE  | _ALARM (     | (0 to 59)      |             |            | 1XXX XXXX   | Table 47 on page 38 |

| 0Ch                                                                      | Hour_alarm       | AE_H         | -        | AMPM  | HOU     | JR_ALARM     | l (1 to 12) ir | n 12-hour r | node       | 1 - XX XXXX | Table 49 on page 39 |

|                                                                          |                  |              |          |       | HOUR_AL | ARM (0 to    | 23) in 24-h    | our mode    |            | 1 - XX XXXX |                     |

| 0Dh                                                                      | Day_alarm        | AE_D         | -        |       |         | DAY_ALAF     | RM (1 to 31)   |             |            | 1 - XX XXXX | Table 51 on page 39 |

| 0Eh                                                                      | Weekday_alarm    | AE_W         | -        | -     | -       | -            | WEEKD          | AY_ALARN    | A (0 to 6) | 1 XXX       | Table 53 on page 40 |

| <b>CLKOUT</b> of                                                         | control register |              |          |       |         |              |                |             |            |             |                     |

| 0Fh                                                                      | CLKOUT_ctl       | TCR          | [1:0]    | OTPR  | -       | -            |                | COF[2:0]    |            | 00X 000     | Table 13 on page 12 |

| watchdog                                                                 | registers        |              |          |       |         |              |                |             |            |             |                     |

| 10h                                                                      | Watchdg_tim_ctl  | WD_C         | D[1:0]   | TI_TP | -       | -            | -              | TF[         | [1:0]      | 000 11      | Table 55 on page 4  |

| CLKOUT of<br>OFh<br>watchdog<br>10h<br>11h<br>Timestam<br>12h            | Watchdg_tim_val  |              |          | W     | ATCHDG_ | TIM_VAL[7    | :0]            |             |            | XXXX XXXX   | Table 57 on page 42 |

| Timestam                                                                 | p registers      |              |          |       |         |              |                |             |            |             |                     |

| 12h                                                                      | Timestp_ctl      | TSM          | TSOFF    | -     |         | 1_0_*        | 6_TIMEST       | P[4:0]      |            | 00 - X XXXX | Table 68 on page 50 |

Product data sheet PCF2127

# **NXP Semiconductors**

# **PCF2127**

Accurate RTC with integrated quartz crystal for industrial applications

#### Table 5. Register overview ...continued

Bit positions labeled as - are not implemented and return 0 when read. Bits labeled as T must always be written with logic 0. Bits labeled as X are undefined at power-on and unchanged by subsequent resets.

| Address    | Register name | Bit |   |      |                          |              |               |            |      | Reset value | Reference          |

|------------|---------------|-----|---|------|--------------------------|--------------|---------------|------------|------|-------------|--------------------|

|            |               | 7   | 6 | 5    | 4                        | 3            | 2             | 1          | 0    | _           |                    |

| 13h        | Sec_timestp   | -   |   |      | SECOND_TIMESTP (0 to 59) |              |               |            |      |             | Table 70 on page 5 |

| 14h        | Min_timestp   | -   |   |      | MINUTE                   |              | 9 (0 to 59)   |            |      | - XXX XXXX  | Table 72 on page 5 |

| 15h        | Hour_timestp  | -   | - | AMPM | HOL                      | JR_TIMEST    | P (1 to 12)   | in 12-hour | mode | XX XXXX     | Table 74 on page 5 |

|            |               |     |   |      | HOUR_TI                  | MESTP (0 1   | to 23) in 24- | hour mode  | ;    | XX XXXX     |                    |

| 16h        | Day_timestp   | -   | - |      |                          | DAY_TIME     | STP (1 to 31  | 1)         |      | XX XXXX     | Table 76 on page 5 |

| 17h        | Mon_timestp   | -   | - | -    |                          | MONTH        | _TIMESTP      | (1 to 12)  |      | X XXXX      | Table 78 on page 5 |

| 18h        | Year_timestp  |     |   | Y    | EAR_TIME                 | ESTP (0 to 9 | 99)           |            |      | XXXX XXXX   | Table 80 on page 5 |

| Aging offs | set register  |     |   |      |                          |              |               |            |      |             | 1                  |

| 19h        | Aging_offset  | -   | - | -    | -                        |              | AO            | [3:0]      |      | 1000        | Table 17 on page 1 |

| RAM regis  | sters         |     |   |      |                          |              |               |            |      |             |                    |

| 1Ah        | RAM_addr_MSB  | -   | - | -    | -                        | -            | -             | -          | RA8  | 0           | Table 20 on page   |

| 1Bh        | RAM_addr_LSB  |     |   | 1    | RA[7:0]                  |              |               |            |      | 0000 0000   | Table 22 on page   |

| 1Ch        | RAM_wrt_cmd   | Х   | Х | Х    | Х                        | Х            | Х             | Х          | Х    | XXXX XXXX   | Table 23 on page   |

| 1Dh        | RAM_rd_cmd    | Х   | Х | Х    | Х                        | Х            | Х             | Х          | Х    | XXXX XXXX   | Table 24 on page 1 |

Product data sheet

8

Rev. 8 ion provided in this document is subject to legal disclaim 19 December 2014

#### 8.2 Control registers

The first 3 registers of the PCF2127, with the addresses 00h, 01h, and 02h, are used as control registers.

#### 8.2.1 Register Control\_1

# Table 6. Control\_1 - control and status register 1 (address 00h) bit allocation Bits labeled as T must always be written with logic 0.

|                |              | , | 0    |      |              |       |    |    |

|----------------|--------------|---|------|------|--------------|-------|----|----|

| Bit            | 7            | 6 | 5    | 4    | 3            | 2     | 1  | 0  |

| Symbol         | EXT_<br>TEST | Т | STOP | TSF1 | POR_<br>OVRD | 12_24 | MI | SI |

| Reset<br>value | 0            | 0 | 0    | 0    | 1            | 0     | 0  | 0  |

## Table 7. Control\_1 - control and status register 1 (address 00h) bit description

Bits labeled as T must always be written with logic 0.

| Bit | Symbol   | Value | Description                                                                                                    | Reference             |  |  |

|-----|----------|-------|----------------------------------------------------------------------------------------------------------------|-----------------------|--|--|

| 7   | EXT_TEST | 0     | normal mode                                                                                                    | Section 8.14          |  |  |

|     |          | 1     | external clock test mode                                                                                       | -                     |  |  |

| 6   | Т        | 0     | unused                                                                                                         | -                     |  |  |

| 5   | STOP     | 0     | RTC source clock runs                                                                                          | Section 8.15          |  |  |

|     |          | 1     | RTC clock is stopped;                                                                                          |                       |  |  |

|     |          |       | RTC divider chain flip-flops are asynchronously<br>set logic 0;                                                |                       |  |  |

|     |          |       | CLKOUT at 32.768 kHz, 16.384 kHz, or 8.192 kHz is still available                                              |                       |  |  |

| 4   | TSF1     | 0     | 0 no timestamp interrupt generated                                                                             |                       |  |  |

|     |          | 1     | flag set when $\overline{\text{TS}}$ input is driven to an intermediate level between power supply and ground; | -                     |  |  |

|     |          |       | flag must be cleared to clear interrupt                                                                        |                       |  |  |

| 3   | POR_OVRD | 0     | Power-On Reset Override (PORO) facility disabled;                                                              | Section 8.8.2         |  |  |

|     |          |       | set logic 0 for normal operation                                                                               |                       |  |  |

|     |          | 1     | Power-On Reset Override (PORO) sequence reception enabled                                                      |                       |  |  |

| 2   | 12_24    | 0     | 24-hour mode selected                                                                                          | Table 33,             |  |  |

|     |          | 1     | 12-hour mode selected                                                                                          | Table 49,<br>Table 74 |  |  |

| 1   | MI       | 0     | minute interrupt disabled                                                                                      | Section 8.13.1        |  |  |

|     |          | 1     | minute interrupt enabled                                                                                       |                       |  |  |

| 0   | SI       | 0     | second interrupt disabled                                                                                      |                       |  |  |

|     |          | 1     | second interrupt enabled                                                                                       | 1                     |  |  |

## 8.2.2 Register Control\_2

| Table 8. | Control_2 - control and statu | s register 2 (address 01h | ) bit allocation |

|----------|-------------------------------|---------------------------|------------------|

|          |                               |                           | / Sit ano oution |

| Bit            | 7   | 6    | 5    | 4  | 3    | 2    | 1   | 0     |

|----------------|-----|------|------|----|------|------|-----|-------|

| Symbol         | MSF | WDTF | TSF2 | AF | CDTF | TSIE | AIE | CDTIE |

| Reset<br>value | 0   | 0    | 0    | 0  | 0    | 0    | 0   | 0     |

#### Table 9. Control\_2 - control and status register 2 (address 01h) bit description

| Bit | Symbol | Value | Description                                                | Reference      |  |

|-----|--------|-------|------------------------------------------------------------|----------------|--|

| 7   | MSF    | 0     | no minute or second interrupt generated                    | Section 8.13   |  |

|     |        | 1     | flag set when minute or second interrupt generated;        | -              |  |

|     |        |       | flag must be cleared to clear interrupt                    |                |  |

| 6   | WDTF   | 0     | no watchdog timer interrupt or reset generated             | Section 8.13.4 |  |

|     |        | 1     | flag set when watchdog timer interrupt or reset generated; |                |  |

|     |        |       | flag cannot be cleared by command (read-only)              |                |  |

| 5   | TSF2   | 0     | no timestamp interrupt generated                           | Section 8.12.1 |  |

|     |        | 1     | 1 flag set when TS input is driven to ground;              |                |  |

|     |        |       | flag must be cleared to clear interrupt                    |                |  |

| 4   | AF     | 0     | no alarm interrupt generated                               | Section 8.10.6 |  |

|     |        | 1     | flag set when alarm triggered;                             | -              |  |

|     |        |       | flag must be cleared to clear interrupt                    |                |  |

| 3   | CDTF   | 0     | no countdown timer interrupt generated                     | Section 8.11.4 |  |

|     |        | 1     | flag set when countdown timer interrupt generated;         | -              |  |

|     |        |       | flag must be cleared to clear interrupt                    |                |  |

| 2   | TSIE   | 0     | no interrupt generated from timestamp flag                 | Section 8.13.6 |  |

|     |        | 1     | interrupt generated when timestamp flag set                | -              |  |

| 1   | AIE    | 0     | no interrupt generated from the alarm flag                 | Section 8.13.5 |  |

|     |        | 1     | interrupt generated when alarm flag set                    |                |  |

| 0   | CDTIE  | 0     | no interrupt generated from countdown timer flag           | Section 8.13.2 |  |

|     |        | 1     | interrupt generated when countdown timer flag set          | =              |  |

PCF2127

#### 8.2.3 Register Control\_3

#### Table 10. Control\_3 - control and status register 3 (address 02h) bit allocation

| Bit            | 7           | 6 | 5 | 4    | 3  | 2   | 1   | 0    |

|----------------|-------------|---|---|------|----|-----|-----|------|

| Symbol         | PWRMNG[2:0] |   |   | BTSE | BF | BLF | BIE | BLIE |

| Reset<br>value | 0           | 0 | 0 | 0    | 0  | 0   | 0   | 0    |

#### Table 11. Control\_3 - control and status register 3 (address 02h) bit description

| Bit    | Symbol      | Value                  | Description                                                                                         | Reference             |

|--------|-------------|------------------------|-----------------------------------------------------------------------------------------------------|-----------------------|

| 7 to 5 | PWRMNG[2:0] | see<br><u>Table 25</u> | control of the battery switch-over, battery low detection, and extra power fail detection functions | Section 8.6           |

| 4      | BTSE        | 0                      | no timestamp when battery switch-over occurs                                                        | Section 8.12.4        |

|        |             | 1                      | time-stamped when battery switch-over occurs                                                        |                       |

| 3      | BF          | 0                      | no battery switch-over interrupt generated                                                          | Section 8.6.1         |

|        |             | 1                      | flag set when battery switch-over occurs;                                                           | and<br>Section 8.12.4 |

|        |             |                        | flag must be cleared to clear interrupt                                                             | <u>Section 6.12.4</u> |

| 2      | BLF         | 0                      | battery status ok;                                                                                  | Section 8.6.2         |

|        |             |                        | no battery low interrupt generated                                                                  |                       |

|        |             | 1                      | battery status low;                                                                                 |                       |

|        |             |                        | flag cannot be cleared by command                                                                   |                       |

| 1      | BIE         | 0                      | no interrupt generated from the battery flag (BF)                                                   | Section 8.13.7        |

|        |             | 1                      | interrupt generated when BF is set                                                                  |                       |

| 0      | BLIE        | 0                      | no interrupt generated from battery low flag (BLF)                                                  | Section 8.13.8        |

|        |             | 1                      | interrupt generated when BLF is set                                                                 |                       |

### 8.3 Register CLKOUT\_ctl

#### Table 12. CLKOUT\_ctl - CLKOUT control register (address 0Fh) bit allocation

Bit positions labeled as - are not implemented and return 0 when read. Bits labeled as X are undefined at power-on and unchanged by subsequent resets.

| Bit            | 7   | 6     | 5    | 4 | 3 | 2 | 1        | 0 |

|----------------|-----|-------|------|---|---|---|----------|---|

| Symbol         | TCR | [1:0] | OTPR | - | - |   | COF[2:0] |   |

| Reset<br>value | 0   | 0     | Х    | - | - | 0 | 0        | 0 |

#### Table 13. CLKOUT ctl - CLKOUT control register (address 0Fh) bit description

Bit positions labeled as - are not implemented and return 0 when read. Bits labeled as X are undefined at power-on and unchanged by subsequent resets.

| Bit    | Symbol   | Value        | Description                    |

|--------|----------|--------------|--------------------------------|

| 7 to 6 | TCR[1:0] | see Table 14 | temperature measurement period |

| 5      | OTPR     | 0            | no OTP refresh                 |

|        |          | 1            | OTP refresh performed          |

| 4 to 3 | -        | -            | unused                         |

| 2 to 0 | COF[2:0] | see Table 15 | CLKOUT frequency selection     |

#### 8.3.1 Temperature compensated crystal oscillator

The frequency of tuning fork quartz crystal oscillators is temperature-dependent. In the PCF2127, the frequency deviation caused by temperature variation is corrected by adjusting the load capacitance of the crystal oscillator.

The load capacitance is changed by switching between two load capacitance values using a modulation signal with a programmable duty cycle. In order to compensate the spread of the quartz parameters every chip is factory calibrated.

The frequency accuracy can be evaluated by measuring the frequency of the square wave signal available at the output pin CLKOUT. However, the selection of  $f_{CLKOUT} = 32.768$  kHz (default value) leads to inaccurate measurements. Accurate frequency measurement occurs when  $f_{CLKOUT} = 16.384$  kHz or lower is selected (see Table 15).

#### 8.3.1.1 Temperature measurement

The PCF2127 has a temperature sensor circuit used to perform the temperature compensation of the frequency. The temperature is measured immediately after power-on and then periodically with a period set by the temperature conversion rate TCR[1:0] in the register CLKOUT\_ctl.

| TCR[1:0] | Temperature measurement period |

|----------|--------------------------------|

| 00 [1]   | 4 min                          |

| 01       | 2 min                          |

| 10       | 1 min                          |

| 11       | 30 seconds                     |

#### Table 14. Temperature measurement period

[1] Default value.

#### 8.3.2 OTP refresh

Each IC is calibrated during production and testing of the device. The calibration parameters are stored on EPROM cells called One Time Programmable (OTP) cells. It is recommended to process an OTP refresh once after the power is up and the oscillator is operating stable. The OTP refresh takes less than 100 ms to complete.

To perform an OTP refresh, bit OTPR has to be cleared (set to logic 0) and then set to logic 1 again.

#### 8.3.3 Clock output

A programmable square wave is available at pin CLKOUT. Operation is controlled by the COF[2:0] control bits in register CLKOUT\_ctl. Frequencies of 32.768 kHz (default) down to 1 Hz can be generated for use as system clock, microcontroller clock, charge pump input, or for calibrating the oscillator.

CLKOUT is an open-drain output and enabled at power-on. When disabled, the output is high-impedance.

| Table 15. | CLKOUT | frequency | selection |

|-----------|--------|-----------|-----------|

|-----------|--------|-----------|-----------|

| COF[2:0]   | CLKOUT frequency (Hz) | Typical duty cycle <sup>[1]</sup> |

|------------|-----------------------|-----------------------------------|

| 000 [2][3] | 32768                 | 60 : 40 to 40 : 60                |

| 001        | 16384                 | 50 : 50                           |

| 010        | 8192                  | 50 : 50                           |

| 011        | 4096                  | 50 : 50                           |

| 100        | 2048                  | 50 : 50                           |

| 101        | 1024                  | 50 : 50                           |

| 110        | 1                     | 50 : 50                           |

| 111        | CLKOUT = high-Z       | -                                 |

[1] Duty cycle definition: % HIGH-level time : % LOW-level time.

[2] Default value.

[3] The specified accuracy of the RTC can be only achieved with CLKOUT frequencies not equal to 32.768 kHz or if CLKOUT is disabled.

The duty cycle of the selected clock is not controlled, however, due to the nature of the clock generation all but the 32.768 kHz frequencies are 50 : 50.

## 8.4 Register Aging\_offset

## Table 16. Aging\_offset - crystal aging offset register (address 19h) bit allocation Bit positions labeled as - are not implemented and return 0 when read.

| Bit            | 7 | 6 | 5 | 4 | 3       | 2 | 1 | 0 |

|----------------|---|---|---|---|---------|---|---|---|

| Symbol         | - | - | - | - | AO[3:0] |   |   |   |

| Reset<br>value | - | - | - | - | 1       | 0 | 0 | 0 |

# Table 17. Aging\_offset - crystal aging offset register (address 19h) bit description Bit positions labeled as - are not implemented and return 0 when read.

| Bit    | Symbol  | Value               | Description        |

|--------|---------|---------------------|--------------------|

| 7 to 4 | -       | -                   | unused             |

| 3 to 0 | AO[3:0] | see <u>Table 18</u> | aging offset value |

#### 8.4.1 Crystal aging correction

The PCF2127 has an offset register Aging\_offset to correct the crystal aging effects<sup>2</sup>.

The accuracy of the frequency of a quartz crystal depends on its aging. The aging offset adds an adjustment, positive or negative, in the temperature compensation circuit which allows correcting the aging effect.

At 25 °C, the aging offset bits allow a frequency correction of typically 1 ppm per AO[3:0] value, from -7 ppm to +8 ppm.

PCF2127

<sup>2.</sup> For further information, refer to the application note Ref. 3 "AN11266".

| AO[3:0] |        | ppm   |  |

|---------|--------|-------|--|

| Decimal | Binary |       |  |

| 0       | 0000   | +8    |  |

| 1       | 0001   | +7    |  |

| 2       | 0010   | +6    |  |

| 3       | 0011   | +5    |  |

| 4       | 0100   | +4    |  |

| 5       | 0101   | +3    |  |

| 6       | 0110   | +2    |  |

| 7       | 0111   | +1    |  |

| 8       | 1000   | [1] 0 |  |

| 9       | 1001   | -1    |  |

| 10      | 1010   | -2    |  |

| 11      | 1011   | -3    |  |

| 12      | 1100   | -4    |  |

| 13      | 1101   | -5    |  |

| 14      | 1110   | -6    |  |

| 15      | 1111   | -7    |  |

Table 18. Frequency correction at 25 °C, typical

[1] Default value.

## 8.5 General purpose 512 bytes static RAM

The PCF2127 contains a general purpose 512 bytes static RAM. This integrated SRAM is battery backed and can therefore be used to store data which is essential for the application to survive a power outage.

9 bits, RA[8:0], define the RAM address pointer in registers RAM\_addr\_MSB and RAM\_addr\_LSB. The register address pointer increments after each read or write automatically up to 1Bh and then wraps around to address 00h (see Figure 5 on page 6).

Data is transferred to or from the RAM by the interface. To write to the RAM, the register RAM\_wrt\_cmd, to read from the RAM the register RAM\_rd\_cmd must be addressed explicitly.

#### **NXP Semiconductors**

#### Accurate RTC with integrated quartz crystal for industrial applications

#### 8.5.1 Register RAM\_addr\_MSB

#### Table 19. RAM\_addr\_MSB - RAM address MSB register (address 1Ah) bit allocation

Bit positions labeled as - are not implemented and return 0 when read.

| Bit            | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|----------------|---|---|---|---|---|---|---|-----|

| Symbol         | - | - | - | - | - | - | - | RA8 |

| Reset<br>value | - | - | - | - | - | - | - | 0   |

#### Table 20. RAM\_addr\_MSB - RAM address MSB register (address 1Ah) bit description

Bit positions labeled as - are not implemented and return 0 when read.

| Bit    | Symbol | Description                            |

|--------|--------|----------------------------------------|

| 7 to 1 | -      | unused                                 |

| 0      | RA8    | RAM address, MSB (9 <sup>th</sup> bit) |

#### 8.5.2 Register RAM\_addr\_LSB

#### Table 21. RAM\_addr\_LSB - RAM address LSB register (address 1Bh) bit allocation

| Bit            | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|----------------|---------|---|---|---|---|---|---|---|--|

| Symbol         | RA[7:0] |   |   |   |   |   |   |   |  |

| Reset<br>value | 0       | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

# Table 22. RAM\_addr\_LSB - RAM address LSB register (address 1Bh) bit description Bit Symbol

| Bit    | Symbol  | Description                                               |

|--------|---------|-----------------------------------------------------------|

| 7 to 0 | RA[7:0] | RAM address, LSB (1 <sup>st</sup> to 8 <sup>th</sup> bit) |

#### 8.5.3 Register RAM\_wrt\_cmd

#### Table 23. RAM\_wrt\_cmd - RAM write command register (address 1Ch) bit description

| Bit    | Symbol | Description                 |

|--------|--------|-----------------------------|

| 7 to 0 | -      | data to be written into RAM |

#### 8.5.4 Register RAM\_rd\_cmd

#### Table 24. RAM\_rd\_cmd - RAM read command register (address 1Dh) bit description

| Bit    | Symbol | Description              |

|--------|--------|--------------------------|

| 7 to 0 | -      | data to be read from RAM |

#### 8.5.5 Operation examples

#### 8.5.5.1 Writing to the RAM

- 1. Set RAM address:

- Select register RAM\_addr\_MSB (send address 1Ah).

- Set value for bit RA8 (data byte of register 1Ah).

Note: register address will be incremented automatically to 1Bh.

- Set value for array RA[7:0] (data byte of register 1Bh).

- 2. Send RAM write command:

- Select register RAM\_wrt\_cmd (send address 1Ch).

- 3. Write data into the RAM:

- Write n data byte into RAM.

For details, see Figure 46 on page 69.

#### 8.5.5.2 Reading from the RAM

- 1. Set RAM address:

- Select register RAM\_addr\_MSB (send address 1Ah).

- Set value for bit RA8 (data byte of register 1Ah).

Note: register address will be incremented automatically to 1Bh.

- Set value for array RA[7:0] (data byte of register 1Bh).

- 2. Send RAM read command:

- Select register RAM\_rd\_cmd (send address 1Dh).

- 3. Read from the RAM:

- Read n data byte from the RAM.

For details, see Figure 47 on page 70.

#### 8.6 Power management functions

The PCF2127 has two power supplies:

V<sub>DD</sub> — the main power supply

$V_{BAT}$  — the battery backup supply

Internally, the PCF2127 is operating with the internal operating voltage  $V_{oper(int)}$  which is also available as  $V_{BBS}$  on the battery backed output voltage pin, BBS. Depending on the condition of the main power supply and the selected power management function,  $V_{oper(int)}$  is either on the potential of  $V_{DD}$  or  $V_{BAT}$  (see Section 8.6.4).

Three power management functions are implemented:

**Battery switch-over function.** monitoring the main power supply  $V_{DD}$  and switching to  $V_{BAT}$  in case a power fail condition is detected (see <u>Section 8.6.1</u>).

**Battery low detection function.** monitoring the status of the battery,  $V_{BAT}$  (see Section 8.6.2).

**Extra power fail detection function.** monitoring the voltage at the power fail input pin, PFI (see <u>Section 8.6.3</u>).

The power management functions are controlled by the control bits PWRMNG[2:0] (see <u>Table 25</u>) in register Control\_3 (see <u>Table 11</u>):

| PWRMNG[2:0] |     | Function                                                                             |

|-------------|-----|--------------------------------------------------------------------------------------|

| 000         | [1] | battery switch-over function is enabled in standard mode;                            |

|             |     | battery low detection function is enabled;                                           |

|             |     | extra power fail detection function is enabled                                       |

| 001         |     | battery switch-over function is enabled in standard mode;                            |

|             |     | battery low detection function is disabled;                                          |

|             |     | extra power fail detection function is enabled                                       |

| 010         |     | battery switch-over function is enabled in standard mode;                            |

|             |     | battery low detection function is disabled;                                          |

|             |     | extra power fail detection function is disabled                                      |

| 011         |     | battery switch-over function is enabled in direct switching mode;                    |

|             |     | battery low detection function is enabled;                                           |

|             |     | extra power fail detection function is enabled                                       |

| 100         |     | battery switch-over function is enabled in direct switching mode;                    |

|             |     | battery low detection function is disabled;                                          |

|             |     | extra power fail detection function is enabled                                       |

| 101         |     | battery switch-over function is enabled in direct switching mode;                    |

|             |     | battery low detection function is disabled;                                          |

|             |     | extra power fail detection function is disabled                                      |

| 110         | [2] | battery switch-over function is disabled - only one power supply $(V_{DD})$ ;        |

|             |     | battery low detection function is disabled;                                          |

|             |     | extra power fail detection function is enabled                                       |

| 111         | [2] | battery switch-over function is disabled - only one power supply $(V_{\text{DD}})$ ; |

|             |     | battery low detection function is disabled;                                          |

|             |     | extra power fail detection function is disabled                                      |

Table 25. Power management control bit description

[1] Default value.

[2] When the battery switch-over function is disabled, the PCF2127 works only with the power supply  $V_{DD}$ . V<sub>BAT</sub> must be put to ground and the battery low detection function is disabled.

#### 8.6.1 Battery switch-over function

The PCF2127 has a backup battery switch-over circuit which monitors the main power supply  $V_{DD}$ . When a power failure condition is detected, it automatically switches to the backup battery.

One of two operation modes can be selected:

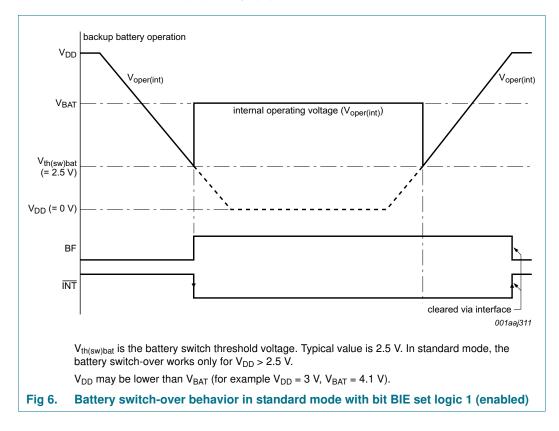

**Standard mode** — the power failure condition happens when:

$V_{DD} < V_{BAT}$  AND  $V_{DD} < V_{th(sw)bat}$

$V_{th(sw)bat}$  is the battery switch threshold voltage. Typical value is 2.5 V. The battery switch-over in standard mode works only for  $V_{DD} > 2.5$  V

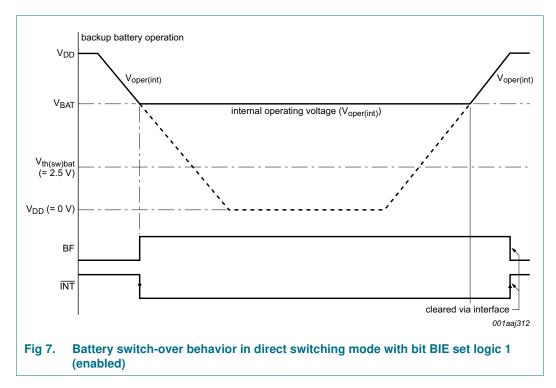

**Direct switching mode** — the power failure condition happens when  $V_{DD} < V_{BAT}$ . Direct switching from  $V_{DD}$  to  $V_{BAT}$  without requiring  $V_{DD}$  to drop below  $V_{th(sw)bat}$

When a power failure condition occurs and the power supply switches to the battery, the following sequence occurs:

- 1. The battery switch flag BF (register Control\_3) is set logic 1.

- An interrupt is generated if the control bit BIE (register Control\_3) is enabled (see <u>Section 8.13.7</u>).

- 3. If the control bit BTSE (register Control\_3) is logic 1, the timestamp registers store the time and date when the battery switch occurred (see <u>Section 8.12.4</u>).

- 4. The battery switch flag BF is cleared by command; it must be cleared to clear the interrupt.

The interface is disabled in battery backup operation:

- Interface inputs are not recognized, preventing extraneous data being written to the device

- Interface outputs are high-impedance

For further information about I<sup>2</sup>C-bus communication and battery backup operation, see <u>Section 9.3 on page 70</u>.

#### 8.6.1.1 Standard mode

If  $V_{DD} > V_{BAT}$  OR  $V_{DD} > V_{th(sw)bat}$ :  $V_{oper(int)}$  is at  $V_{DD}$  potential.

If V<sub>DD</sub> < V<sub>BAT</sub> AND V<sub>DD</sub> < V<sub>th(sw)bat</sub>: V<sub>oper(int)</sub> is at V<sub>BAT</sub> potential.

#### 8.6.1.2 Direct switching mode

If  $V_{DD} > V_{BAT}$ :  $V_{oper(int)}$  is at  $V_{DD}$  potential.

If  $V_{DD} < V_{BAT}$ :  $V_{oper(int)}$  is at  $V_{BAT}$  potential.

The direct switching mode is useful in systems where  $V_{DD}$  is always higher than  $V_{BAT}$ . This mode is not recommended if the  $V_{DD}$  and  $V_{BAT}$  values are similar (for example,  $V_{DD}$  = 3.3 V,  $V_{BAT} \ge 3.0$  V). In direct switching mode, the power consumption is reduced compared to the standard mode because the monitoring of  $V_{DD}$  and  $V_{th(sw)bat}$  is not performed.

#### 8.6.1.3 Battery switch-over disabled: only one power supply (V<sub>DD</sub>)

When the battery switch-over function is disabled:

- The power supply is applied on the  $V_{DD}$  pin

- The V<sub>BAT</sub> pin must be connected to ground

- V<sub>oper(int)</sub> is at V<sub>DD</sub> potential

- The battery flag (BF) is always logic 0

#### 8.6.1.4 Battery switch-over architecture

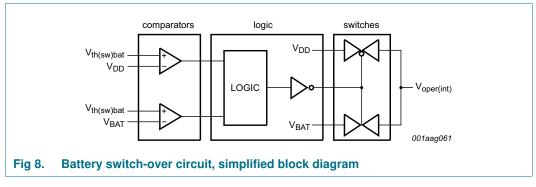

The architecture of the battery switch-over circuit is shown in Figure 8.

V<sub>oper(int)</sub> is at V<sub>DD</sub> or V<sub>BAT</sub> potential.

**Remark:** It has to be assured that there are decoupling capacitors on the pins  $V_{\text{DD}}, V_{\text{BAT}},$  and BBS.

#### 8.6.2 Battery low detection function

The PCF2127 has a battery low detection circuit which monitors the status of the battery  $V_{\text{BAT}}.$

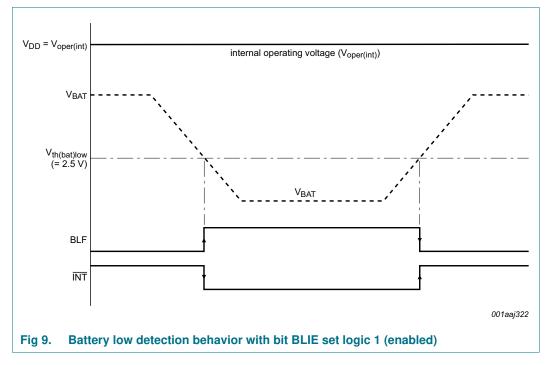

When V<sub>BAT</sub> drops below the threshold value V<sub>th(bat)low</sub> (typically 2.5 V), the BLF flag (register Control\_3) is set to indicate that the battery is low and that it must be replaced. Monitoring of the battery voltage also occurs during battery operation.

An unreliable battery cannot prevent that the supply voltage drops below  $V_{low}$  (typical 1.2 V) and with that the data integrity gets lost. (For further information about  $V_{low}$  see <u>Section 8.7</u>.)

When  $V_{BAT}$  drops below the threshold value  $V_{th(bat)low}$ , the following sequence occurs (see Figure 9):

- 1. The battery low flag BLF is set logic 1.

- An interrupt is generated if the control bit BLIE (register Control\_3) is enabled (see <u>Section 8.13.8</u>).

- 3. The flag BLF remains logic 1 until the battery is replaced. BLF cannot be cleared by command. It is automatically cleared by the battery low detection circuit when the battery is replaced or when the voltage rises again above the threshold value. This could happen if a super capacitor is used as a backup source and the main power is applied again.

# **PCF2127**

#### Accurate RTC with integrated quartz crystal for industrial applications

#### 8.6.3 Extra power fail detection function

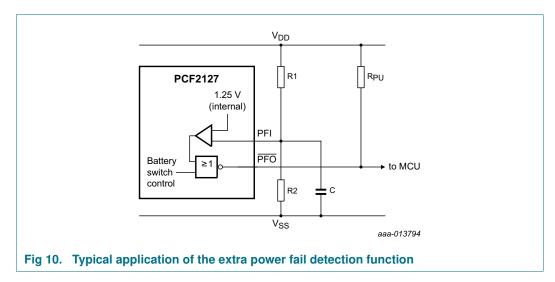

The PCF2127 has an extra power fail detection circuit which compares the voltage at the power fail input pin PFI to an internal reference voltage equal to 1.25 V.

If  $V_{PFI} < 1.25$  V, the power fail output  $\overline{PFO}$  is driven LOW.  $\overline{PFO}$  is an open-drain, active LOW output which requires an external pull-up resistor in any application.

The extra power fail detection function is typically used as a low voltage detection for the main power supply  $V_{DD}$  (see Figure 10).

Usually R1 and R2 should be chosen such that the voltage at pin PFI

- is higher than 1.25 V at start-up

- falls below 1.25 V when V<sub>DD</sub> falls below a desired threshold voltage, V<sub>th(uvp)</sub>, defined by <u>Equation 1</u>:

$$V_{th(uvp)} = \left(\frac{R_1}{R_2} + I\right) \times I.25V \tag{1}$$

$V_{th(uvp)}$  value is usually set to a value that there are several milliseconds before  $V_{DD}$  falls below the minimum operating voltage of the system, in order to allow the microcontroller to perform early backup operations, like terminating the communication with the PCF2127.

The value of C is determined from Equation 2:

$$C = \frac{0.02}{(R_1/R_2)} \left[\frac{As}{V}\right]$$

(2)

If the extra power fail detection function is not used, pin PFI must be connected to  $V_{SS}$  and pin PFO must be left open circuit.

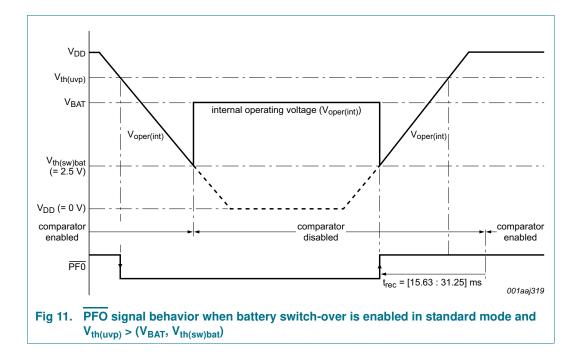

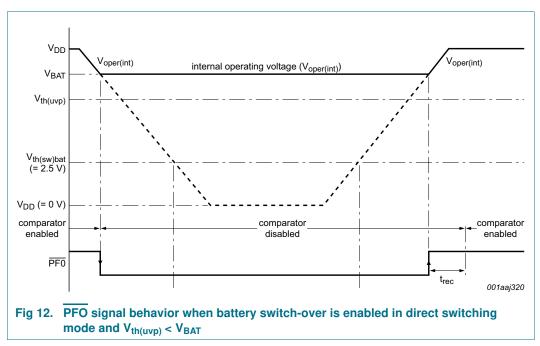

#### 8.6.3.1 Extra power fail detection when the battery switch-over function is enabled

- When the power switches to the backup battery supply V<sub>BAT</sub>, the power fail comparator is switched off and the power fail output at pin PFO goes (or remains) LOW

- When the power switches back to the main  $V_{DD}$ , the pin  $\overline{PFO}$  is not driven LOW anymore. It is pulled HIGH through the external pull-up resistance for a certain time (t<sub>rec</sub> = 15.63 ms to 31.25 ms). Then the power fail comparator is enabled again

For illustration, see Figure 11 and Figure 12.

#### **NXP Semiconductors**

# **PCF2127**

#### Accurate RTC with integrated quartz crystal for industrial applications