# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Freescale Semiconductor

Data Sheet: Technical Data

Document Number: MCF52277 Rev. 8, 09/2009

RoHS

# MCF52277

n

MAPBGA-196 15mm x 15mm

# MCF5227*x* ColdFire<sup>®</sup> Microprocessor Data Sheet

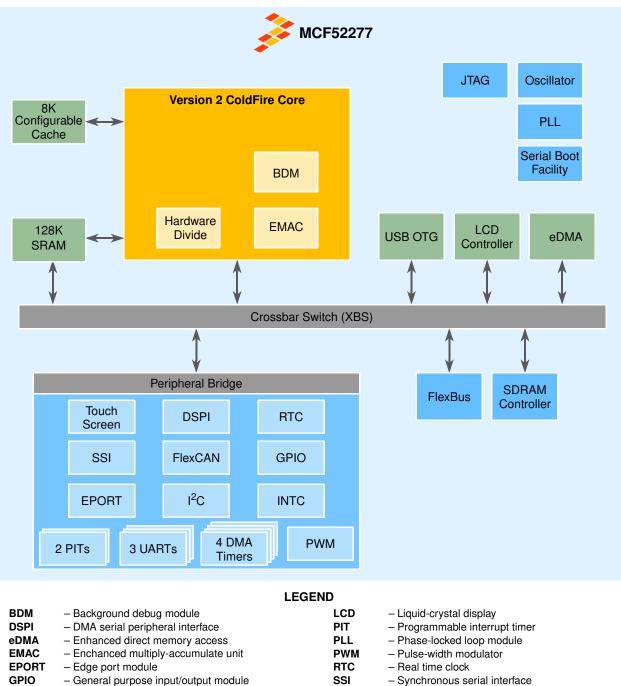

### Features

- Version 2 ColdFire<sup>®</sup> Core with EMAC

- Up to 159 Dhrystone 2.1 MIPS @ 166.67 MHz

- 8 Kbytes configurable cache (instruction only, data only, or split instruction/data)

- 128 Kbytes internal SRAM

- Support for booting from SPI-compatible flash, EEPROM, and FRAM devices

- Crossbar switch technology (XBS) for concurrent access to peripherals or RAM from multiple bus masters

- 16 channel DMA controller

- 16- or 32-bit SDR/DDR controller

- USB 2.0 On-the-Go controller

- Liquid crystal display controller with support up to 800 × 600 pixels

- ADC and touchscreen controller

- FlexCAN module

- 4 32-bit timers with DMA support

- DMA supported serial peripheral interface (DSPI)

- 3 UARTs

- I<sup>2</sup>C bus interface

- Synchronous serial interface (SSI)

- Plus-width modulator (PWM)

- Real-time clock (RTC)

- Two programmable interrupt controllers (PIT)

Freescale reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

© Freescale Semiconductor, Inc., 2009. All rights reserved.

# NP

# **Table of Contents**

| 1<br>2<br>3 | Orde  | 5227x Family Comparison           |

|-------------|-------|-----------------------------------|

|             | 3.1   | PLL Power Filtering               |

|             | 3.2   | USB Power Filtering               |

|             | 3.3   | ADC Power Filtering               |

|             | 3.4   | Supply Voltage Sequencing         |

|             |       | 3.4.1 Power Up Sequence           |

|             |       | 3.4.2 Power Down Sequence         |

|             | 3.5   | Power Consumption Specifications7 |

| 4           | Pin A | Assignments and Reset States      |

|             | 4.1   | Signal Multiplexing               |

|             | 4.2   | Pinout—176 LQFP14                 |

|             | 4.3   | Pinout—196 MAPBGA15               |

| 5           | Elect | rical Characteristics             |

|             | 5.1   | Maximum Ratings16                 |

|             | 5.2   | Thermal Characteristics           |

|             | 5.3   | ESD Protection                    |

|             | 5.4   | DC Electrical Specifications      |

|   | 5.5<br>5.6 | Oscillator and PLL Electrical Characteristics   |

|---|------------|-------------------------------------------------|

|   | 5.0<br>5.7 |                                                 |

|   | 5.7        | External Interface Timing Specifications        |

|   |            |                                                 |

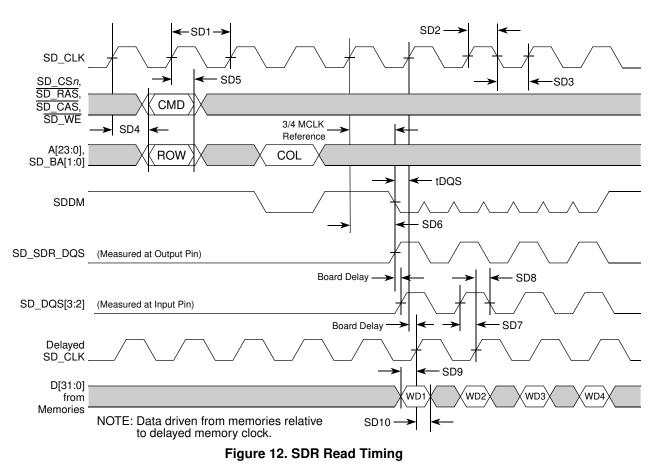

|   |            | 5.7.2 SDRAM Bus                                 |

|   | 5.8        | General Purpose I/O Timing                      |

|   | 5.9        | Reset and Configuration Override Timing 29      |

|   | 5.10       | LCD Controller Timing Specifications            |

|   | 5.11       | USB On-The-Go Specifications                    |

|   | 5.12       | SSI Timing Specifications                       |

|   | 5.13       | I <sup>2</sup> C Timing Specifications          |

|   | 5.14       | DMA Timer Timing Specifications                 |

|   | 5.15       | DSPI Timing Specifications                      |

|   | 5.16       | SBF Timing Specifications                       |

|   | 5.17       | JTAG and Boundary Scan Timing Specifications 40 |

|   | 5.18       |                                                 |

| 6 | Packa      | age Information                                 |

| 7 |            | uct Documentation                               |

| 8 |            | sion History                                    |

| - |            |                                                 |

- **I<sup>2</sup>C** Inter-intergrated circuit

- **INTC** Interrupt controller

- JTAG Joint Test Action Group interface

UART

### MCF5227x ColdFire<sup>®</sup> Microprocessor Data Sheet, Rev. 8

- Universal asynchronous receiver/transmitter

USB OTG - Universal Serial Bus On-the-Go controller

MCF5227x Family Comparison

# 1 MCF5227x Family Comparison

The following table compares the various device derivatives available within the MCF5227*x* family.

### Table 1. MCF5227x Family Configurations

| Module                                                                   | MCF52274      | MCF52277         |

|--------------------------------------------------------------------------|---------------|------------------|

| ColdFire Version 2 Core with EMAC<br>(Enhanced Multiply-Accumulate Unit) | •             | •                |

| Core (System) Clock                                                      | up to 120 MHz | up to 166.67 MHz |

| Peripheral and External Bus Clock<br>(Core clock ÷ 2)                    | up to 60 MHz  | up to 83.33 MHz  |

| Performance (Dhrystone/2.1 MIPS)                                         | up to 114     | up to 159        |

| Static RAM (SRAM)                                                        | 128 k         | Cbytes           |

| Configurable Cache                                                       | 8 Kt          | oytes            |

| ASP Touchscreen Controller                                               | •             | •                |

| LCD Controller                                                           | 12-bit color  | 18-bit color     |

| USB 2.0 On-the-Go                                                        | •             | •                |

| FlexBus External Interface                                               | •             | •                |

| SDR/DDR SDRAM Controller                                                 | •             | •                |

| FlexCAN 2.0B communication module                                        | •             | •                |

| Real Time Clock                                                          | •             | •                |

| Watchdog Timer                                                           | •             | •                |

| 16-channel Direct Memory Access (DMA)                                    | •             | •                |

| Interrupt Controllers (INTC)                                             | 1             | 1                |

| Synchronous Serial Interface (SSI)                                       | •             | •                |

| l <sup>2</sup> C                                                         | •             | •                |

| DSPI                                                                     | •             | •                |

| UARTs                                                                    | 3             | 3                |

| 32-bit DMA Timers                                                        | 4             | 4                |

| Periodic Interrupt Timers (PIT)                                          | 2             | 2                |

| PWM Module                                                               | •             | •                |

| Edge Port Module (EPORT)                                                 | •             | •                |

| General Purpose I/O Module (GPIO)                                        | •             | •                |

| JTAG - IEEE <sup>®</sup> 1149.1 Test Access Port                         | •             | •                |

| Package                                                                  | 176 LQFP      | 196 MAPBGA       |

# 2 Ordering Information

Table 2. Orderable Part Numbers

| Freescale Part<br>Number | Description                  |            | Speed      | Temperature                      |  |

|--------------------------|------------------------------|------------|------------|----------------------------------|--|

| MCF52274CLU120           | MCF52274 RISC Microprocessor | 176 LQFP   | 120 MHz    | $-40^{\circ}$ to $+85^{\circ}$ C |  |

| MCF52277CVM160           | MCF52277 RISC Microprocessor | 196 MAPBGA | 166.67 MHz | $-40^{\circ}$ to $+85^{\circ}$ C |  |

# 3 Hardware Design Considerations

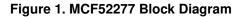

# 3.1 PLL Power Filtering

To further enhance noise isolation, an external filter is strongly recommended for PLL analog  $V_{DD}$  pins. The filter shown in Figure 2 should be connected between the board  $V_{DD}$  and the PLLV<sub>DD</sub> pins. The resistor and capacitors should be placed as close to the dedicated PLLV<sub>DD</sub> pin as possible.

Figure 2. System PLL V<sub>DD</sub> Power Filter

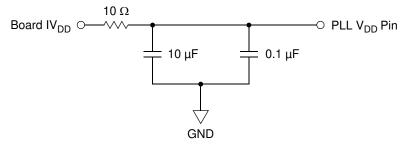

## 3.2 USB Power Filtering

To minimize noise, external filters are required for each of the USB power pins. The filter shown in Figure 3 should be connected between the board  $EV_{DD}$  and the USBV<sub>DD</sub> pin. The resistor and capacitors should be placed as close to the dedicated USBV<sub>DD</sub> pin as possible.

Figure 3. USB V<sub>DD</sub> Power Filter

### NOTE

In addition to the above filter circuitry, a 0.01 F capacitor is also recommended in parallel with those shown.

Hardware Design Considerations

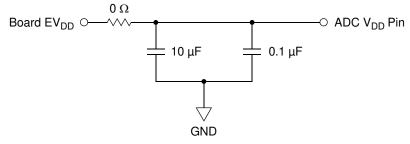

# 3.3 ADC Power Filtering

To minimize noise, an external filters is required for the  $ADCV_{DD}$  power pin. The filter shown in Figure 4 should be connected between the board  $EV_{DD}$  and the  $ADCV_{DD}$  pin. The resistor and capacitors should be placed as close to the dedicated  $ADCV_{DD}$  pin as possible.

Figure 4. ADC V<sub>DD</sub> Power Filter

# 3.4 Supply Voltage Sequencing

The relationship between SDV<sub>DD</sub> and EV<sub>DD</sub> is non-critical during power-up and power-down sequences. Both SDV<sub>DD</sub> (2.5V or 3.3V) and EV<sub>DD</sub> are specified relative to IV<sub>DD</sub>.

### 3.4.1 Power Up Sequence

If  $EV_{DD}/SDV_{DD}$  are powered up with  $IV_{DD}$  at 0 V, then the sense circuits in the I/O pads will cause all pad output drivers connected to the  $EV_{DD}/SDV_{DD}$  to be in a high impedance state. There is no limit on how long after  $EV_{DD}/SDV_{DD}$  powers up before  $IV_{DD}$  must powered up.  $IV_{DD}$  should not lead the  $EV_{DD}$ ,  $SDV_{DD}$  or  $PLLV_{DD}$  by more than 0.4 V during power ramp-up, or there will be high current in the internal ESD protection diodes. The rise times on the power supplies should be slower than 500 us to avoid turning on the internal ESD protection clamp diodes.

### 3.4.2 Power Down Sequence

If  $IV_{DD}/PLLV_{DD}$  are powered down first, then sense circuits in the I/O pads will cause all output drivers to be in a high impedance state. There is no limit on how long after  $IV_{DD}$  and  $PLLV_{DD}$  power down before  $EV_{DD}$  or  $SDV_{DD}$  must power down.  $IV_{DD}$  should not lag  $EV_{DD}$ ,  $SDV_{DD}$ , or  $PLLV_{DD}$  going low by more than 0.4 V during power down or there will be undesired high current in the ESD protection diodes. There are no requirements for the fall times of the power supplies.

The recommended power down sequence is as follows:

- 1. Drop  $IV_{DD}$ /PLLV<sub>DD</sub> to 0 V.

- 2. Drop  $EV_{DD}/SDV_{DD}$  supplies.

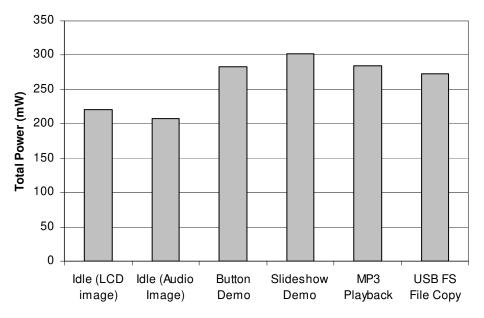

# 3.5 Power Consumption Specifications

All application power consumption data is lab data measured on an M52277EVB running the Freescale Linux BSP.

| Core<br>Freq. |                   | Idle (LCD<br>image) | ldle (audio<br>image) | Button<br>Demo | Slideshow<br>Demo | MP3<br>Playback | USB FS<br>File Copy | Units |

|---------------|-------------------|---------------------|-----------------------|----------------|-------------------|-----------------|---------------------|-------|

|               | IV <sub>DD</sub>  | 61.4                | 59.2                  | 84.7           | 96.5              | 89.2            | 89.5                |       |

| 100 1411      | EV <sub>DD</sub>  | 28.87               | 25.73                 | 35.3           | 34.6              | 33.46           | 29.86               | mA    |

| 160 MHz       | SDV <sub>DD</sub> | 18.8                | 18.57                 | 21.8           | 23.9              | 22.66           | 22.2                |       |

|               | Total Power       | 221.211             | 207.135               | 282.78         | 301.95            | 285.006         | 272.748             | mW    |

### Table 3. MCF52277 Application Power Consumption<sup>1</sup>

<sup>1</sup> All voltage rails at nominal values:  $IV_{DD} = 1.5 V$ ,  $EV_{DD} = 3.3 V$ , and  $SDV_{DD} = 1.8 V$ .

Figure 5. Power Consumption in Various Applications

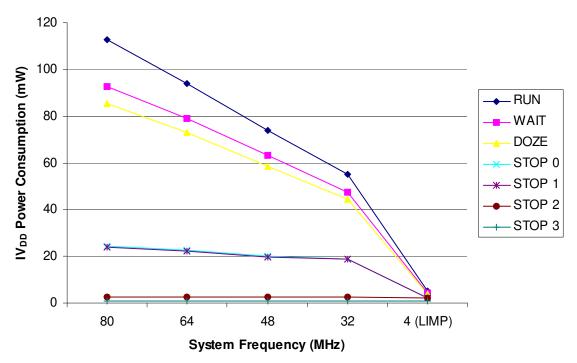

All current consumption data is lab data measured on a single device using an evaluation board. Table 4 shows the typical power consumption in low-power modes. These current measurements are taken after executing a STOP instruction.

Table 4. Current Consumption in Low-Power Modes<sup>1,2</sup>

|      |                       | System Frequency |       |       |       |                        |  |  |

|------|-----------------------|------------------|-------|-------|-------|------------------------|--|--|

| Mode | Voltage Supply        | 80MHz            | 64MHz | 48MHz | 32MHz | 4MHz<br>(LIMP<br>mode) |  |  |

| RUN  | IV <sub>DD</sub> (mA) | 75.1             | 62.7  | 49.2  | 36.6  | 3.5                    |  |  |

| non  | Power (mW)            | 112.65           | 94.05 | 73.80 | 54.90 | 5.25                   |  |  |

| WAIT | IV <sub>DD</sub> (mA) | 61.9             | 52.8  | 42.0  | 31.7  | 2.9                    |  |  |

|      | Power (mW)            | 92.85            | 79.20 | 63.00 | 47.55 | 4.35                   |  |  |

MCF5227x ColdFire<sup>®</sup> Microprocessor Data Sheet, Rev. 8

#### Hardware Design Considerations

|        |                       | System Frequency |       |       |       |                        |  |  |  |

|--------|-----------------------|------------------|-------|-------|-------|------------------------|--|--|--|

| Mode   | Voltage Supply        | 80MHz            | 64MHz | 48MHz | 32MHz | 4MHz<br>(LIMP<br>mode) |  |  |  |

| DOZE   | IV <sub>DD</sub> (mA) | 57.0             | 48.8  | 38.9  | 29.7  | 2.7                    |  |  |  |

| DOZE   | Power (mW)            | 85.50            | 73.20 | 58.35 | 44.55 | 4.05                   |  |  |  |

| STOP 0 | IV <sub>DD</sub> (mA) | 16.1             | 15.1  | 13.4  | 12.5  | 1.3                    |  |  |  |

| 310F U | Power (mW)            | 24.15            | 22.65 | 20.10 | 18.75 | 1.95                   |  |  |  |

| STOP 1 | IV <sub>DD</sub> (mA) | 15.9             | 14.9  | 13.2  | 12.4  | 1.3                    |  |  |  |

| 310F 1 | Power (mW)            | 23.85            | 22.35 | 19.80 | 18.60 | 1.95                   |  |  |  |

| STOP 2 | IV <sub>DD</sub> (mA) | 1.8              | 1.8   | 1.8   | 1.8   | 1.3                    |  |  |  |

| STOP 2 | Power (mW)            | 2.70             | 2.70  | 2.70  | 2.70  | 1.95                   |  |  |  |

| STOP 3 | IV <sub>DD</sub> (mA) | 0.5              | 0.5   | 0.5   | 0.5   | 0.5                    |  |  |  |

| STOP 3 | Power (mW)            | 0.75             | 0.75  | 0.75  | 0.75  | 0.75                   |  |  |  |

Table 4. Current Consumption in Low-Power Modes<sup>1,2</sup> (continued)

<sup>1</sup> All values are measured on an M52277EVB with nominal core voltage(IV<sub>DD</sub> = 1.5 V). Tests performed at room temperature. All peripheral clocks on prior to entering low-power mode

<sup>2</sup> Refer to the Power Management chapter in the *MCF52277 Reference Manual* for more information on low-power modes.

Figure 6. IV<sub>DD</sub> Power Consumption in Low-Power Modes

## 4.1 Signal Multiplexing

The following table lists all the MCF5227*x* pins grouped by function. The direction column is the direction for the primary function of the pin only. Refer to Section 4, "Pin Assignments and Reset States," for package diagrams. For a more detailed discussion of the MCF5227*x* signals, consult the *MCF52277 Reference Manual* (MCF52277RM).

### NOTE

In this table and throughout this document a single signal within a group is designated without square brackets (i.e., FB\_A23), while designations for multiple signals within a group use brackets (i.e., FB\_A[23:21]) and is meant to include all signals within the two bracketed numbers when these numbers are separated by a colon.

### NOTE

The primary functionality of a pin is not necessarily its default functionality. Most pins that are muxed with GPIO will default to their GPIO functionality. See Table 5 for a list of the exceptions.

Table 5. Special-Case Default Signal Functionality

| Pin            | Default Signal |

|----------------|----------------|

| FB_BE/BWE[3:0] | FB_BE/BWE[3:0] |

| FB_CS[3:0]     | FB_CS[3:0]     |

| FB_OE          | FB_OE          |

| FB_TA          | FB_TA          |

| FB_R/W         | FB_R/W         |

| FB_TS          | FB_TS          |

| Signal Name  | GPIO           | Alternate 1 | Alternate 2 | Pull-up (U) <sup>1</sup><br>Pull-down (D) | Direction <sup>2</sup> | Voltage Domain | MCF52274<br>176 LQFP | MCF52277<br>196 MAPBGA |  |

|--------------|----------------|-------------|-------------|-------------------------------------------|------------------------|----------------|----------------------|------------------------|--|

|              | Reset          |             |             |                                           |                        |                |                      |                        |  |

| RESET        | _              | _           | _           | U                                         | Ι                      | EVDD           | 103                  | J11                    |  |

| RSTOUT       | —              | —           | —           | —                                         | 0                      | EVDD           | 102                  | K11                    |  |

|              |                |             | Clock       |                                           |                        |                |                      |                        |  |

| EXTAL        |                | _           | _           |                                           | Ι                      | EVDD           | 106                  | F14                    |  |

| XTAL         | —              | —           | —           | U <sup>3</sup>                            | 0                      | EVDD           | 105                  | G14                    |  |

|              | Mode Selection |             |             |                                           |                        |                |                      |                        |  |

| BOOTMOD[1:0] | _              | _           | —           | —                                         | Ι                      | EVDD           | 110, 109             | G10, H10               |  |

| Signal Name    | GPIO     | Alternate 1 | Alternate 2    | Pull-up (U) <sup>1</sup><br>Pull-down (D) | Direction <sup>2</sup> | Voltage Domain | MCF52274<br>176 LQFP | MCF52277<br>196 MAPBGA                                |  |  |  |

|----------------|----------|-------------|----------------|-------------------------------------------|------------------------|----------------|----------------------|-------------------------------------------------------|--|--|--|

|                | FlexBus  |             |                |                                           |                        |                |                      |                                                       |  |  |  |

| FB_A[23:22]    |          | FB_CS[5:4]  | —              | —                                         | 0                      | SDVDD          | 143, 142             | C11, D11                                              |  |  |  |

| FB_A[21:16]    | _        | —           | —              | -                                         | 0                      | SDVDD          | 141–139, 137–135     | A12, B12, C12,<br>B13, A13, A14                       |  |  |  |

| FB_A[15:14]    | _        | SD_BA[1:0]  | —              | _                                         | 0                      | SDVDD          | 131, 130             | B14, C13                                              |  |  |  |

| FB_A[13:11]    | _        | SD_A[13:11] | _              | —                                         | 0                      | SDVDD          | 129–127              | C14, D12, D13                                         |  |  |  |

| FB_A10         | —        | —           | —              |                                           | 0                      | SDVDD          | 126                  | D14                                                   |  |  |  |

| FB_A[9:0]      |          | SD_A[9:0]   | _              |                                           | 0                      | SDVDD          | 125–116              | E11–E14,<br>F11–F13, G11,<br>G12, H11                 |  |  |  |

| FB_D[31:16]    | _        | SD_D[31:16] | _              |                                           | I/O                    | SDVDD          | 30–37, 49–56         | J4, K1–K4, L1–L3,<br>M3, N3, P3,M4,<br>N4, P4, L5, M5 |  |  |  |

| FB_D[15:0]     | _        | FB_D[31:16] | _              |                                           | I/O                    | SDVDD          | 19–26, 60–67         | G1–G4, H1–H4,<br>M6, N6, P6, L7,<br>M7, N7, P7, L8    |  |  |  |

| FB_CLK         | _        | —           | —              |                                           | 0                      | SDVDD          | 42                   | P1                                                    |  |  |  |

| FB_BE/BWE[3:0] | PBE[3:0] | SD_DQM[3:0] | —              | _                                         | 0                      | SDVDD          | 29, 57, 27, 59       | J3, N5, J1, L6                                        |  |  |  |

| FB_CS[3:2]     | PCS[3:2] | —           | —              | —                                         | 0                      | SDVDD          | —                    | B11, A11                                              |  |  |  |

| FB_CS1         | PCS1     | SD_CS1      | —              | —                                         | 0                      | SDVDD          | 144                  | D10                                                   |  |  |  |

| FB_CS0         | PCS0     | —           | —              | -                                         | 0                      | SDVDD          | 145                  | C10                                                   |  |  |  |

| FB_OE          | PFBCTL3  | —           | —              | —                                         | 0                      | SDVDD          | 69                   | N8                                                    |  |  |  |

| FB_TA          | PFBCTL2  | —           | —              | U                                         | Ι                      | SDVDD          | 115                  | H12                                                   |  |  |  |

| FB_R/W         | PFBCTL1  |             | —              | —                                         | 0                      | SDVDD          | 68                   | M8                                                    |  |  |  |

| FB_TS          | PFBCTL0  | DACK0       | —              | —                                         | 0                      | SDVDD          | 15                   | F4                                                    |  |  |  |

|                |          | SD          | RAM Controller |                                           |                        |                |                      |                                                       |  |  |  |

| SD_A10         | _        | —           | —              | —                                         | 0                      | SDVDD          | 46                   | L4                                                    |  |  |  |

| SD_CAS         | _        | —           | _              | -                                         | 0                      | SDVDD          | 47                   | N2                                                    |  |  |  |

| SD_CKE         | _        | —           | _              |                                           | 0                      | SDVDD          | 17                   | F2                                                    |  |  |  |

| SD_CLK         | _        | —           | —              | —                                         | 0                      | SDVDD          | 40                   | M1                                                    |  |  |  |

| SD_CLK         | _        | —           | —              | —                                         | 0                      | SDVDD          | 41                   | N1                                                    |  |  |  |

| SD_CS0         | _        | —           | —              | —                                         | 0                      | SDVDD          | 18                   | F1                                                    |  |  |  |

| SD_DQS[3:2]    | —        | _           | —              | -                                         | I/O                    | SDVDD          | 28, 58               | J2, P5                                                |  |  |  |

| SD_RAS         | —        | —           | —              | —                                         | 0                      | SDVDD          | 48                   | P2                                                    |  |  |  |

| Signal Name               | GPIO        | Alternate 1  | Alternate 2                     | Pull-up (U) <sup>1</sup><br>Pull-down (D) | Direction <sup>2</sup> | Voltage Domain | MCF52274<br>176 LQFP | MCF52277<br>196 MAPBGA |

|---------------------------|-------------|--------------|---------------------------------|-------------------------------------------|------------------------|----------------|----------------------|------------------------|

| SD_SDR_DQS                | —           | _            |                                 | —                                         | 0                      | SDVDD          | 38                   | M2                     |

| SD_WE                     | —           | _            | _                               | —                                         | 0                      | SDVDD          | 16                   | F3                     |

|                           | •           | Extern       | al Interrupts Port <sup>4</sup> |                                           |                        |                |                      |                        |

| IRQ7                      | PIRQ7       | _            |                                 | —                                         | I                      | EVDD           | 162                  | D7                     |

| IRQ4                      | PIRQ4       | DREQ0        | DSPI_PCS4                       | 5                                         | I                      | EVDD           | 161                  | C7                     |

| IRQ1                      | PIRQ1       | USB_CLKIN    | SSI_CLKIN                       | —                                         | I                      | EVDD           | 160                  | B7                     |

|                           |             | LC           | CD Controller <sup>6</sup>      |                                           |                        |                |                      |                        |

| LCD_D[17:16] <sup>6</sup> | PLCDDH[1:0] | LCD_D[11:10] | _                               | _                                         | 0                      | EVDD           | 9, 8                 | E3, E4                 |

| LCD_D[15:14] <sup>6</sup> | PLCDDM[7:6] | LCD_D[9:8]   |                                 | —                                         | 0                      | EVDD           | 7, 6                 | D1, D2                 |

| LCD_D13                   | PLCDDM5     | CANTX        | _                               | —                                         | 0                      | EVDD           | _                    | C1                     |

| LCD_D12                   | PLCDDM4     | CANRX        | _                               | —                                         | 0                      | EVDD           | _                    | C2                     |

| LCD_D[11:8] <sup>6</sup>  | PLCDDM[3:0] | LCD_D[7:4]   | —                               | —                                         | 0                      | EVDD           | 5–2                  | D3, C3, D4, B1         |

| LCD_D7                    | PLCDDL7     | PWM7         | —                               | —                                         | 0                      | EVDD           | _                    | B2                     |

| LCD_D6                    | PLCDDL6     | PWM5         |                                 | —                                         | 0                      | EVDD           | _                    | A1                     |

| LCD_D[5:2] <sup>6</sup>   | PLCDDL[5:2] | LCD_D[3:0]   | _                               | —                                         | 0                      | EVDD           | 175–172              | A2, A3, B3, A4         |

| LCD_D1                    | PLCDDL1     | PWM3         | _                               | —                                         | 0                      | EVDD           | _                    | B4                     |

| LCD_D0                    | PLCDDL0     | PWM1         |                                 | —                                         | 0                      | EVDD           | _                    | C4                     |

| LCD_ACD/<br>LCD_OE        | PLCDCTL3    | LCD_SPL_SPR  | _                               | —                                         | 0                      | EVDD           | 169                  | B5                     |

| LCD_FLM/<br>LCD_VSYNC     | PLCDCTL2    |              | _                               | —                                         | 0                      | EVDD           | 10                   | E2                     |

| LCD_LP/<br>LCD_HSYNC      | PLCDCTL1    |              |                                 | —                                         | 0                      | EVDD           | 11                   | E1                     |

| LCD_LSCLK                 | PLCDCTL0    | —            | _                               | —                                         | 0                      | EVDD           | 170                  | A5                     |

|                           | 1           | U            | SB On-the-Go                    |                                           |                        |                |                      | 1                      |

| USB_DM                    | —           | _            | _                               | —                                         | 0                      | USB<br>VDD     | 149                  | A9                     |

| USB_DP                    | _           | _            |                                 | —                                         | 0                      | USB<br>VDD     | 150                  | A10                    |

|                           |             | Re           | al Time Clock                   | •                                         |                        |                |                      |                        |

| RTC_EXTAL                 | —           | —            |                                 | _                                         | I                      | EVDD           | 100                  | J14                    |

| RTC_XTAL                  | —           | _            | —                               | —                                         | 0                      | EVDD           | 99                   | K14                    |

### Table 6. MCF5227x Signal Information and Muxing (continued)

| Signal Name               | GPIO    | Alternate 1 | Alternate 2           | Pull-up (U) <sup>1</sup><br>Pull-down (D) | Direction <sup>2</sup> | Voltage Domain | MCF52274<br>176 LQFP | MCF52277<br>196 MAPBGA                       |  |  |  |

|---------------------------|---------|-------------|-----------------------|-------------------------------------------|------------------------|----------------|----------------------|----------------------------------------------|--|--|--|

| Touchscreen Controller    |         |             |                       |                                           |                        |                |                      |                                              |  |  |  |

| ADC_IN[7:0]               | _       | _           | _                     | _                                         | I                      | VDD_<br>ADC    | 82–85, 87–90         | P12, N12, P13,<br>N13, P14, N14,<br>M13, M14 |  |  |  |

| ADC_REF                   |         | _           | —                     | —                                         | I                      | VDD_<br>ADC    | 86                   | M12                                          |  |  |  |

|                           |         |             | l <sup>2</sup> C      |                                           |                        |                |                      |                                              |  |  |  |

| I2C_SCL                   | PI2C1   | CANTX       | U2TXD                 | U                                         | I/O                    | EVDD           | 168                  | C5                                           |  |  |  |

| I2C_SDA                   | PI2C0   | CANRX       | U2RXD                 | U                                         | I/O                    | EVDD           | 167                  | D5                                           |  |  |  |

|                           |         |             | DSPI <sup>7</sup>     |                                           | •                      |                |                      |                                              |  |  |  |

| DSPI_PCS0/SS              | PDSPI3  | U2RTS       | —                     | U                                         | I/O                    | EVDD           | 152                  | B9                                           |  |  |  |

| DSPI_SIN                  | PDSPI2  | U2RXD       | SBF_DI                | 8                                         | I                      | EVDD           | 155                  | D8                                           |  |  |  |

| DSPI_SOUT                 | PDSPI1  | U2TXD       | SBF_D0                | —                                         | 0                      | EVDD           | 154                  | D9                                           |  |  |  |

| DSPI_SCK                  | PDSPI0  | U2CTS       | SBF_CK                | —                                         | I/O                    | EVDD           | 153                  | C9                                           |  |  |  |

|                           |         |             | UARTs                 |                                           |                        |                |                      |                                              |  |  |  |

| U1CTS                     | PUART7  | SSI_BCLK    | LCD_CLS               | —                                         | I                      | EVDD           | 156                  | C8                                           |  |  |  |

| U1RTS                     | PUART6  | SSI_FS      | LCD_PS                | —                                         | 0                      | EVDD           | 157                  | B8                                           |  |  |  |

| U1TXD                     | PUART5  | SSI_TXD     | —                     | —                                         | 0                      | EVDD           | 159                  | A7                                           |  |  |  |

| U1RXD                     | PUART4  | SSI_RXD     | —                     | —                                         | I                      | EVDD           | 158                  | A8                                           |  |  |  |

| UOCTS                     | PUART3  | DT1OUT      | USB_VBUS_EN           | _                                         | I                      | EVDD           | 97                   | K12                                          |  |  |  |

| UORTS                     | PUART2  | DT1IN       | USB_VBUS_OC           | —                                         | 0                      | EVDD           | 98                   | J12                                          |  |  |  |

| U0TXD                     | PUART1  | CANTX       | —                     | _                                         | 0                      | EVDD           | 95                   | L12                                          |  |  |  |

| U0RXD                     | PUART0  | CANRX       | —                     | —                                         | Ι                      | EVDD           | 96                   | K13                                          |  |  |  |

|                           |         |             | DMA Timers            |                                           |                        |                |                      |                                              |  |  |  |

| DT3IN                     | PTIMER3 | DT3OUT      | SSI_MCLK              | _                                         | I                      | EVDD           | 163                  | D6                                           |  |  |  |

| DT2IN/SBF_CS <sup>7</sup> | PTIMER2 | DT2OUT      | DSPI_PCS2             |                                           | Ι                      | EVDD           | 164                  | C6                                           |  |  |  |

| DT1IN                     | PTIMER1 | DT1OUT      | LCD_CONTRAST          | —                                         | I                      | EVDD           | 165                  | B6                                           |  |  |  |

| DT0IN                     | PTIMER0 | DT0OUT      | LCD_REV               | —                                         | Ι                      | EVDD           | 166                  | A6                                           |  |  |  |

|                           |         |             | BDM/JTAG <sup>9</sup> | _                                         | _                      | _              |                      |                                              |  |  |  |

| PST[3:0]                  | —       | _           | —                     | —                                         | 0                      | EVDD           | —                    | L9, M9, N9, P9                               |  |  |  |

| DDATA[3:0]                | _       | _           | —                     | —                                         | 0                      | EVDD           | —                    | L10, M10, N10,<br>P10                        |  |  |  |

| Signal Name | GPIO | Alternate 1 | Alternate 2   | Pull-up (U) <sup>1</sup><br>Pull-down (D) | Direction <sup>2</sup> | Voltage Domain | MCF52274<br>176 LQFP                | MCF52277<br>196 MAPBGA                |

|-------------|------|-------------|---------------|-------------------------------------------|------------------------|----------------|-------------------------------------|---------------------------------------|

| ALLPST      |      | _           | _             | —                                         | 0                      | EVDD           | 76                                  | —                                     |

| JTAG_EN     | —    | _           | —             | D                                         | I                      | EVDD           | 79                                  | K10                                   |

| PSTCLK      | —    | TCLK        | —             | U                                         | 0                      | EVDD           | 74                                  | P8                                    |

| DSI         | _    | TDI         | —             | U                                         | Ι                      | EVDD           | 78                                  | M11                                   |

| DSO         | _    | TDO         | —             | —                                         | 0                      | EVDD           | 81                                  | L11                                   |

| BKPT        | —    | TMS         | —             | U                                         | Ι                      | EVDD           | 80                                  | N11                                   |

| DSCLK       | _    | TRST        | —             | U                                         | Ι                      | EVDD           | 77                                  | P11                                   |

|             |      |             | Test          | •                                         | •                      | •              |                                     |                                       |

| TEST        | —    | _           | _             | D                                         | Ι                      | EVDD           | 134                                 | E10                                   |

|             |      | Po          | ower Supplies |                                           |                        |                |                                     |                                       |

| IVDD        | _    |             |               | —                                         |                        | —              | 39, 75, 114, 138,<br>171            | K5, F10, E5, J10                      |

| EVDD        | —    |             | _             | —                                         | —                      |                | 12, 72, 73, 94, 111,<br>148, 176    | E6, E7, F5, F6, G5,<br>H9, J9, K8, K9 |

| SD_VDD      | —    |             | _             | —                                         |                        | —              | 14, 43, 44, 70, 113,<br>132, 146    | E8, E9, F9, G9, H5,<br>J5, J6, K6, K7 |

| VDD_OSC     |      | _           | —             | —                                         | —                      | _              | 108                                 | G13                                   |

| VDD_PLL     | _    | _           | —             | _                                         | —                      | _              | 104                                 | H14                                   |

| VDD_USB     |      | _           | _             | —                                         | —                      | —              | 151                                 | B10                                   |

| VDD_RTC     |      | _           | _             | —                                         | —                      | —              | 101                                 | J13                                   |

| VDD_ADC     | _    | _           | —             | —                                         | —                      |                | 91                                  | L13                                   |

| VSS         | —    | _           | _             | —                                         |                        |                | 1, 13, 45, 71, 93,<br>112, 133, 147 | F7, F8, G6–G8,<br>H6–H8, J7, J8       |

| VSS_OSC     | _    | _           | _             | —                                         | —                      |                | 107                                 | H13                                   |

| VSS_ADC     | —    |             | —             |                                           |                        |                | 92                                  | L14                                   |

### Table 6. MCF5227x Signal Information and Muxing (continued)

<sup>1</sup> Pull-ups are generally only enabled on pins with their primary function, except as noted.

<sup>2</sup> Refers to pin's primary function.

<sup>3</sup> Enabled only in oscillator bypass mode (internal crystal oscillator is disabled).

<sup>4</sup> GPIO functionality is determined by the edge port module. The GPIO module is only responsible for assigning the alternate functions.

<sup>5</sup> Pull-up when  $\overline{\text{DREQ}}$  controls the pin.

<sup>6</sup> The 176 LQFP device only supports a 12-bit LCD data bus.

<sup>7</sup> DSPI or SBF signal functionality is controlled by RESET. When asserted, these pins are configured for serial boot; when negated, the pins are configured for DSPI.

<sup>8</sup> Pull-up when the serial boot facility (SBF) controls the pin.

<sup>9</sup> If JTAG\_EN is asserted, these pins default to alternate 1 (JTAG) functionality. The GPIO module is not responsible for assigning these pins.

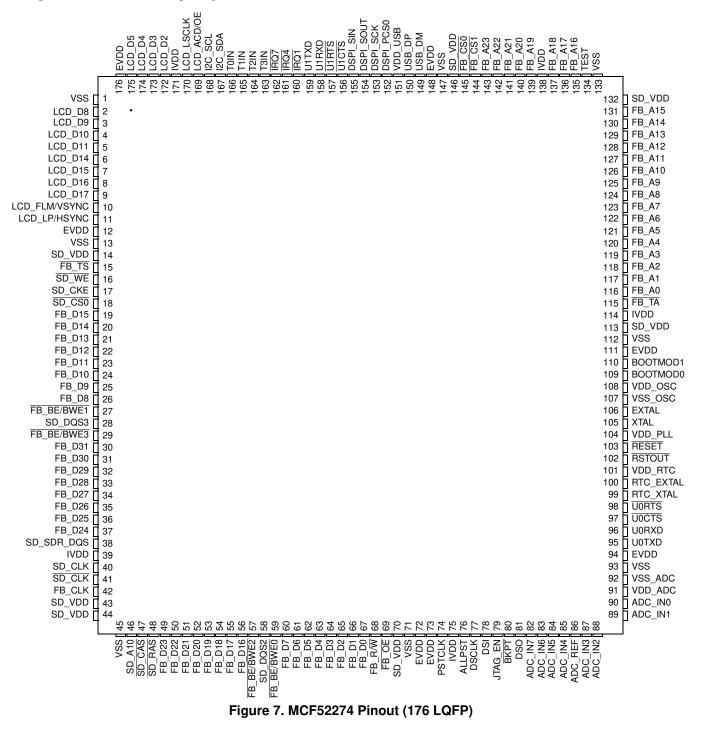

### 4.2 Pinout—176 LQFP

The pinout for the MCF52274 package is shown below.

# 4.3 Pinout—196 MAPBGA

The pinout for the MCF52277 package is shown below.

|   | 1                | 2                 | 3              | 4       | 5              | 6              | 7     | 8        | 9             | 10           | 11     | 12          | 13          | 14            |   |

|---|------------------|-------------------|----------------|---------|----------------|----------------|-------|----------|---------------|--------------|--------|-------------|-------------|---------------|---|

| A | LCD_D6           | LCD_D5            | LCD_D4         | LCD_D2  | LCD_<br>LSCLK  | T0IN           | U1TXD | U1RXD    | USB_DM        | USB_DP       | FB_CS2 | FB_A21      | FB_A17      | FB_A16        | A |

| в | LCD_D8           | LCD_D7            | LCD_D3         | LCD_D1  | LCD_<br>ACD/OE | T1IN           | IRQ_1 | U1RTS    | DSPI_<br>PCS0 | VDD_<br>USB  | FB_CS3 | FB_A20      | FB_A18      | FB_A15        | в |

| с | LCD_D13          | LCD_D12           | LCD_D10        | LCD_D0  | I2C_SCL        | T2IN           | IRQ_4 | U1CTS    | DSPI_<br>SCK  | FB_CS0       | FB_A23 | FB_A19      | FB_A14      | FB_A13        | с |

| D | LCD_D15          | LCD_D14           | LCD_D11        | LCD_D9  | I2C_SDA        | T3IN           | IRQ_7 | DSPI_SIN | DSPI_<br>SOUT | FB_CS1       | FB_A22 | FB_A12      | FB_A11      | FB_A10        | D |

| E | LCD_LP/<br>HSYNC | LCD_FLM/<br>VSYNC | LCD_D17        | LCD_D16 | IVDD           | EVDD           | EVDD  | SDVDD    | SDVDD         | TEST         | FB_A9  | FB_A8       | FB_A7       | FB_A6         | Е |

| F | SD_CS0           | SD_CKE            | SD_WE          | FB_TS   | EVDD           | EVDD           | VSS   | VSS      |               | IVDD         | FB_A5  | FB_A4       | FB_A3       | EXTAL         | F |

| G | FB_D15           | FB_D14            | FB_D13         | FB_D12  | EVDD           | VSS            | VSS   | VSS      |               | BOOT<br>MOD1 | FB_A2  | FB_A1       | VDD_<br>OSC | XTAL          | G |

| н | FB_D11           | FB_D10            | FB_D9          | FB_D8   |                | VSS            | VSS   | VSS      | EVDD          | BOOT<br>MOD0 | FB_A0  | FB_TA       | VSS_<br>OSC | VDD_<br>PLL   | н |

| J | FB_BE/<br>BWE1   | SD_DQS3           | FB_BE/<br>BWE3 | FB_D31  |                |                | VSS   | VSS      | EVDD          | IVDD         | RESET  | UORTS       | VDD_<br>RTC | RTC_<br>EXTAL | J |

| к | FB_D30           | FB_D29            | FB_D28         | FB_D27  | IVDD           |                |       | EVDD     | EVDD          | JTAG_EN      | RSTOUT | UOCTS       | U0RXD       | RTC_<br>XTAL  | к |

| L | FB_D26           | FB_D25            | FB_D24         | SD_A10  | FB_D17         | FB_BE/<br>BWE0 | FB_D4 | FB_D0    | PST3          | DDATA3       | TDO    | U0TXD       | VDD_<br>ADC | VSS_<br>ADC   | L |

| М | SD_CLK           | SD_<br>SDR_DQS    | FB_D23         | FB_D20  | FB_D16         | FB_D7          | FB_D3 | FB_R/W   | PST2          | DDATA2       | TDI    | ADC_<br>REF | ADC_IN1     | ADC_IN0       | М |

| N | SD_CLK           | SD_CAS            | FB_D22         | FB_D19  | FB_BE/<br>BWE2 | FB_D6          | FB_D2 | FB_OE    | PST1          | DDATA1       | TMS    | ADC_IN6     | ADC_IN4     | ADC_IN2       | N |

| Ρ | FB_CLK           | SD_RAS            | FB_D21         | FB_D18  | SD_<br>DQS0    | FB_D5          | FB_D1 | TCLK     | PST0          | DDATA0       | TRST   | ADC_IN7     | ADC_IN5     | ADC_IN3       | Ρ |

|   | 1                | 2                 | 3              | 4       | 5              | 6              | 7     | 8        | 9             | 10           | 11     | 12          | 13          | 14            |   |

### Figure 8. MCF52277 Pinout (196 MAPBGA)

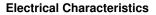

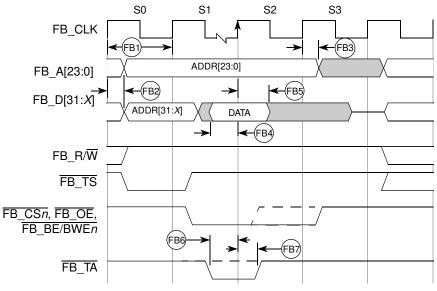

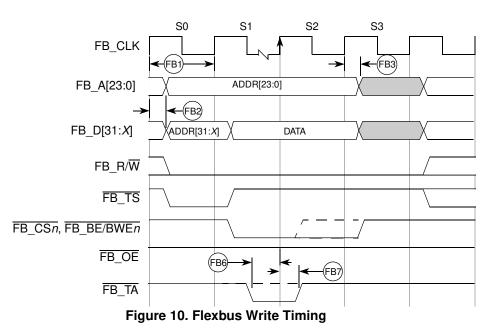

# 5 Electrical Characteristics

This document contains electrical specification tables and reference timing diagrams for the MCF5227x microprocessor. This section contains detailed information on DC/AC electrical characteristics and AC timing specifications.

The electrical specifications are preliminary and are from previous designs or design simulations. These specifications may not be fully tested or guaranteed at this early stage of the product life cycle, however for production silicon these specifications will be met. Finalized specifications will be published after complete characterization and device qualifications have been completed.

### NOTE

The parameters specified in this MCU document supersede any values found in the module specifications.

# 5.1 Maximum Ratings

### Table 7. Absolute Maximum Ratings<sup>1, 2</sup>

| Characteristic                                                                             | Symbol                                               | Value        | Unit |

|--------------------------------------------------------------------------------------------|------------------------------------------------------|--------------|------|

| Core Supply Voltage                                                                        | IV <sub>DD</sub>                                     | -0.5 to +2.0 | V    |

| CMOS Pad Supply Voltage                                                                    | EV <sub>DD</sub>                                     | -0.3 to +4.0 | V    |

| DDR/Memory Pad Supply Voltage                                                              | SDV <sub>DD</sub>                                    | -0.3 to +4.0 | V    |

| Oscillator Supply Voltage                                                                  | OSCV <sub>DD</sub>                                   | -0.3 to +4.0 | V    |

| PLL Supply Voltage                                                                         | PLLV <sub>DD</sub>                                   | -0.3 to +2.0 | V    |

| RTC Supply Voltage                                                                         | RTCV <sub>DD</sub>                                   | -0.5 to +2.0 | V    |

| Digital Input Voltage <sup>3</sup>                                                         | V <sub>IN</sub>                                      | -0.3 to +3.6 | V    |

| Instantaneous Maximum Current<br>Single pin limit (applies to all pins) <sup>3, 4, 5</sup> | ۱ <sub>D</sub>                                       | 25           | mA   |

| Operating Temperature Range (Packaged)                                                     | T <sub>A</sub><br>(T <sub>L</sub> – T <sub>H</sub> ) | -40 to +85   | °C   |

| Storage Temperature Range                                                                  | T <sub>stg</sub>                                     | -55 to +150  | °C   |

<sup>1</sup> Functional operating conditions are given in Section 5.4, "DC Electrical Specifications." Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Continued operation at these levels may affect device reliability or cause permanent damage to the device.

<sup>2</sup> This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either V<sub>SS</sub> or EV<sub>DD</sub>).

<sup>3</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

$^4$  All functional non-supply pins are internally clamped to V<sub>SS</sub> and EV<sub>DD</sub>.

<sup>5</sup> Power supply must maintain regulation within operating  $EV_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{in} > EV_{DD}$ ) is greater than  $I_{DD}$ , the injection current may flow out of  $EV_{DD}$  and could result in external power supply going out of regulation. Insure external  $EV_{DD}$  load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power (ex; no clock). Power supply must maintain regulation within operating  $EV_{DD}$  range during instantaneous and operating maximum current conditions.

## 5.2 Thermal Characteristics

| Characteristic                          |                         | Symbol         | 196<br>MAPBGA     | 176<br>LQFP       | Unit |

|-----------------------------------------|-------------------------|----------------|-------------------|-------------------|------|

| Junction to ambient, natural convection | Four layer board (2s2p) | $\theta_{JA}$  | 38 <sup>1,2</sup> | 48 <sup>1,2</sup> | °C/W |

| Junction to ambient (@200 ft/min)       | Four layer board (2s2p) | $\theta_{JMA}$ | 34 <sup>1,2</sup> | 42 <sup>1,2</sup> | °C/W |

| Junction to board                       |                         | $\theta_{JB}$  | 27 <sup>3</sup>   | 37 <sup>3</sup>   | °C/W |

| Junction to case                        |                         | $\theta_{JC}$  | 17 <sup>4</sup>   | 14 <sup>4</sup>   | °C/W |

| Junction to top of package              |                         | $\Psi_{jt}$    | 4 <sup>1,5</sup>  | 3 <sup>1,5</sup>  | °C/W |

| Maximum operating junction temperature  | )                       | Тj             | 105               | 105               | °C   |

#### **Table 8. Thermal Characteristics**

$\theta_{JA}$ ,  $\theta_{JMA}$  and  $\Psi_{jt}$  parameters are simulated in conformance with EIA/JESD Standard 51-2 for natural convection. Freescale recommends the use of  $\theta_{JmA}$  and power dissipation specifications in the system design to prevent device junction temperatures from exceeding the rated specification. System designers should be aware that device junction temperatures can be significantly influenced by board layout and surrounding devices. Conformance to the device junction temperature specification can be verified by physical measurement in the customer's system using the  $\Psi_{it}$  parameter, the device power dissipation, and the method described in EIA/JESD Standard 51-2.

<sup>2</sup> Per JEDEC JESD51-6 with the board horizontal.

<sup>3</sup> Thermal resistance between the die and the printed circuit board in conformance with JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

<sup>4</sup> Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

<sup>5</sup> Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written in conformance with Psi-JT.

The average chip-junction temperature (T<sub>J</sub>) in °C can be obtained from:

$$T_J = T_A + (P_D \times \Theta_{JMA})$$

Eqn. 1

Where:

For most applications  $P_{I/O} < P_{INT}$  and can be ignored. An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:

$$P_D = \frac{K}{(T_J + 273 \,^{\circ}C)}$$

Eqn. 2

Solving equations 1 and 2 for K gives:

$$K = P_D \times (T_A \times 273^{\circ}C) + Q_{JMA} \times P_D^2$$

Eqn. 3

where K is a constant pertaining to the particular part. K can be determined from Equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving Equation 1 and Equation 2 iteratively for any value of  $T_A$ .

MCF5227x ColdFire<sup>®</sup> Microprocessor Data Sheet, Rev. 8

Freescale Semiconductor

# 5.3 ESD Protection

| Characteristic                  | Symbol | Value | Unit |

|---------------------------------|--------|-------|------|

| ESD Target for Human Body Model | HBM    | 2000  | V    |

Table 9. ESD Protection Characteristics<sup>1,2</sup>

<sup>1</sup> All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

<sup>2</sup> A device is defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing is performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

# 5.4 DC Electrical Specifications

### Table 10. DC Electrical Specifications

| Characteristic                                                                                                                                                                     | Symbol             | Min                                                                     | Max                                                                           | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|

| Core Supply Voltage                                                                                                                                                                | IV <sub>DD</sub>   | 1.4                                                                     | 1.6                                                                           | V    |

| PLL Supply Voltage                                                                                                                                                                 | PLLV <sub>DD</sub> | 1.4                                                                     | 1.6                                                                           | V    |

| RTC Supply Voltage                                                                                                                                                                 | RTCV <sub>DD</sub> | 1.4                                                                     | 1.6                                                                           | V    |

| CMOS Pad Supply Voltage                                                                                                                                                            | EV <sub>DD</sub>   | 3.0                                                                     | 3.6                                                                           | V    |

| SDRAM and FlexBus Supply Voltage<br>Mobile DDR/Bus Pad Supply Voltage (nominal 1.8V)<br>DDR/Bus Pad Supply Voltage (nominal 2.5V)<br>SDR/Bus Pad Supply Voltage (nominal 3.3V)     | SDV <sub>DD</sub>  | 1.7<br>2.25<br>3.0                                                      | 1.95<br>2.75<br>3.6                                                           | V    |

| USB Supply Voltage                                                                                                                                                                 | USBV <sub>DD</sub> | 3.0                                                                     | 3.6                                                                           | V    |

| Oscillator Supply Voltage                                                                                                                                                          | OSCV <sub>DD</sub> | 3.0                                                                     | 3.6                                                                           | V    |

| CMOS Input High Voltage                                                                                                                                                            | EVIH               | 2                                                                       | EV <sub>DD</sub> + 0.3                                                        | V    |

| CMOS Input Low Voltage                                                                                                                                                             | EVIL               | V <sub>SS</sub> – 0.3                                                   | 0.8                                                                           | V    |

| CMOS Output High Voltage<br>I <sub>OH</sub> = -5.0 mA                                                                                                                              | EV <sub>OH</sub>   | EV <sub>DD</sub> -0.4                                                   | _                                                                             | V    |

| CMOS Output Low Voltage<br>I <sub>OL</sub> = 5.0 mA                                                                                                                                | EV <sub>OL</sub>   | —                                                                       | 0.4                                                                           | V    |

| SDRAM and FlexBus Input High Voltage<br>Mobile DDR/Bus Input High Voltage (nominal 1.8V)<br>DDR/Bus Pad Supply Voltage (nominal 2.5V)<br>SDR/Bus Pad Supply Voltage (nominal 3.3V) | SDV <sub>IH</sub>  | 1.35<br>1.7<br>2                                                        | SDV <sub>DD</sub> + 0.3<br>SDV <sub>DD</sub> + 0.3<br>SDV <sub>DD</sub> + 0.3 | V    |

| SDRAM and FlexBus Input Low Voltage<br>Mobile DDR/Bus Input High Voltage (nominal 1.8V)<br>DDR/Bus Pad Supply Voltage (nominal 2.5V)<br>SDR/Bus Pad Supply Voltage (nominal 3.3V)  | SDV <sub>IL</sub>  | V <sub>SS</sub> - 0.3<br>V <sub>SS</sub> - 0.3<br>V <sub>SS</sub> - 0.3 | 0.45<br>0.8<br>0.8                                                            | V    |

| Characteristic                                                                                                                                                                                                                 | Symbol            | Min               | Max               | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|------|

| SDRAM and FlexBus Output High Voltage<br>Mobile DDR/Bus Input High Voltage (nominal 1.8V)<br>DDR/Bus Pad Supply Voltage (nominal 2.5V)<br>SDR/Bus Pad Supply Voltage (nominal 3.3V)<br>I <sub>OH</sub> = -5.0 mA for all modes | SDV <sub>OH</sub> | 1.4<br>2.1<br>2.4 |                   | V    |

| SDRAM and FlexBus Output Low Voltage<br>Mobile DDR/Bus Input High Voltage (nominal 1.8V)<br>DDR/Bus Pad Supply Voltage (nominal 2.5V)<br>SDR/Bus Pad Supply Voltage (nominal 3.3V)<br>I <sub>OL</sub> = 5.0 mA for all modes   | SDV <sub>OL</sub> | <br><br>          | 0.3<br>0.3<br>0.5 | V    |

| Input Leakage Current<br>$V_{in} = V_{DD}$ or $V_{SS}$ , Input-only pins                                                                                                                                                       | l <sub>in</sub>   | -1.0              | 1.0               | μΑ   |

| Weak Internal Pull-Up Device Current, tested at V <sub>IL</sub> Max. <sup>1</sup>                                                                                                                                              | I <sub>APU</sub>  | -10               | -130              | μA   |

| Input Capacitance <sup>2</sup><br>All input-only pins<br>All input/output (three-state) pins                                                                                                                                   | C <sub>in</sub>   |                   | 7<br>7            | pF   |

### Table 10. DC Electrical Specifications (continued)

<sup>1</sup> Refer to the signals section for pins having weak internal pull-up devices.

<sup>2</sup> This parameter is characterized before qualification rather than 100% tested.

# 5.5 Oscillator and PLL Electrical Characteristics

| Table 11. | PLL E | lectrical | Characteristics |

|-----------|-------|-----------|-----------------|

|-----------|-------|-----------|-----------------|

| Num | Characteristic                                                                            | Symbol                                           | Min                                                  | Max                                                  | Unit       |

|-----|-------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------|------------------------------------------------------|------------|

| 1   | PLL Reference Frequency Range<br>Crystal reference<br>External reference                  | f <sub>ref_crystal</sub><br>f <sub>ref_ext</sub> | 16<br>16                                             | 25 <sup>1</sup><br>66.67 <sup>1</sup>                | MHz<br>MHz |

| 2   | Core/system frequency<br>CLKOUT Frequency                                                 | f <sub>sys</sub><br>f <sub>sys/2</sub>           | 512 Hz <sup>2</sup><br>256 Hz <sup>2</sup>           | 166.67<br>83.33                                      | MHz<br>MHz |

| 3   | Crystal Start-up Time <sup>3,4</sup>                                                      | t <sub>cst</sub>                                 | —                                                    | 10                                                   | ms         |

| 4   | EXTAL Input High Voltage<br>Crystal Mode <sup>5</sup><br>All other modes (External, Limp) | V <sub>IHEXT</sub><br>V <sub>IHEXT</sub>         | V <sub>XTAL</sub> + 0.4<br>E <sub>VDD</sub> /2 + 0.4 | _                                                    | V<br>V     |

| 5   | EXTAL Input Low Voltage<br>Crystal Mode <sup>5</sup><br>All other modes (External, Limp)  | V <sub>ILEXT</sub><br>V <sub>ILEXT</sub>         | _                                                    | V <sub>XTAL</sub> - 0.4<br>E <sub>VDD</sub> /2 - 0.4 | V<br>V     |

| 7   | PLL Lock Time <sup>3,6</sup>                                                              | t <sub>ipii</sub>                                | —                                                    | 50000                                                | CLKIN      |

| 8   | Duty cycle of reference <sup>3</sup>                                                      | t <sub>dc</sub>                                  | 40                                                   | 60                                                   | %          |

| 9   | XTAL Current                                                                              | I <sub>XTAL</sub>                                | 1                                                    | 3                                                    | mA         |

| 10  | Total on-chip stray capacitance on XTAL                                                   | C <sub>S_XTAL</sub>                              | —                                                    | 1.5                                                  | pF         |

| 11  | Total on-chip stray capacitance on EXTAL                                                  | C <sub>S_EXTAL</sub>                             | —                                                    | 1.5                                                  | pF         |

| 12  | Crystal capacitive load                                                                   | CL                                               | See crys                                             | stal spec                                            |            |

| Num | Characteristic                                                                                                                                 | Symbol                                      | Min  | Max                                                                                         | Unit                                         |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------|---------------------------------------------------------------------------------------------|----------------------------------------------|

| 13  | Discrete load capacitance for XTAL<br>Discrete load capacitance for EXTAL                                                                      | C <sub>L_XTAL</sub><br>C <sub>L_EXTAL</sub> | _    | $\begin{array}{c} 2\times (C_L-\\ C_{S\_XTAL}-\\ C_{S\_EXTAL}-\\ C_{S\_PCB})^7 \end{array}$ | pF                                           |

| 14  | Frequency un-LOCK Range                                                                                                                        | f <sub>UL</sub>                             | -4.0 | 4.0                                                                                         | % f <sub>sys</sub>                           |

| 15  | Frequency LOCK Range                                                                                                                           | f <sub>LCK</sub>                            | -2.0 | 2.0                                                                                         | % f <sub>sys</sub>                           |

| 17  | CLKOUT period jitter <sup>4, 5, 8</sup> measured at f <sub>sys</sub> max<br>Peak-to-peak jitter (Clock edge to clock edge)<br>Long-term jitter | C <sub>jitter</sub>                         |      | 10<br>TBD                                                                                   | % f <sub>sys/2</sub><br>% f <sub>sys/2</sub> |

| 19  | VCO frequency ( $f_{vco} = f_{ref} \times PFDR$ )                                                                                              | f <sub>vco</sub>                            | 350  | 540                                                                                         | MHz                                          |

Although these are the allowable frequency ranges, do not violate the VCO frequency range of the PLL. See the 1 MCF5227x Reference Manual for more details.

$^2~$  The minimum system frequency is the minimum input clock divided by the maximum low-power divider (16 MHz  $\div$  32,768). When the PLL is enabled, the minimum system frequency (f<sub>sys</sub>) is 37.5 MHz.

<sup>3</sup> This parameter is guaranteed by characterization before gualification rather than 100% tested. Applies to external clock reference only.

- <sup>4</sup> Proper PC board layout procedures must be followed to achieve specifications.

- <sup>5</sup> This parameter is guaranteed by design rather than 100% tested.

- <sup>6</sup> This specification is the PLL lock time only and does not include oscillator start-up time..

- 7

$C_{S\_PCB}$  is the measured PCB stray capacitance on EXTAL and XTAL. Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum  $f_{sys}$ . Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the PLL circuitry via PLL V<sub>DD</sub>, EV<sub>DD</sub>, and V<sub>SS</sub> and variation in crystal oscillator frequency increase the Cjitter percentage for a given interval.

#### 5.6 ASP Electrical Characteristics

Table 12 lists the electrical specifications for the ASP module.

| Characteristic                 | Symbol               | Min | Typical | Max              | Unit             |

|--------------------------------|----------------------|-----|---------|------------------|------------------|

| ASP Analog Supply Voltage      | V <sub>DDA</sub>     | 3.0 | -       | 3.6              | V                |

| Input Voltage Range            | V <sub>ADIN</sub>    | 0   |         | V <sub>DDA</sub> | V                |

| Operating Current Consumption  | I <sub>DDA_ON</sub>  |     | 700     | _                | uA               |

| Power-down Current Consumption | I <sub>DDA_OFF</sub> |     | 1       | —                | uA               |

| Resolution                     | R <sub>ES</sub>      |     |         | 12               | bits             |

| Sampling rate                  |                      |     |         | 125              | kS/s             |

| Integral Non-linearity         | INL                  |     | ±8      | ±24              | lsb <sup>1</sup> |

| Differential Non-linearity     | DNL                  |     | ±2      | ±24              | lsb <sup>1</sup> |

| ADC Internal Clock Frequency   | t <sub>AIC</sub>     | 2   | —       | 8                | MHz              |

| Conversion Range               | R <sub>AD</sub>      | 0   | —       | V <sub>DDA</sub> | V                |

| Characteristic            | Symbol           | Min | Typical | Max  | Unit                       |

|---------------------------|------------------|-----|---------|------|----------------------------|

| Conversion Time           | t <sub>ADC</sub> | 15  | _       | 32   | t <sub>AIC</sub><br>cycles |

| Sample Time               | t <sub>ADS</sub> | 3   | _       | 20   | t <sub>AIC</sub><br>cycles |

| Multiplexer Settling Time | t <sub>AMS</sub> |     | _       | 3    | t <sub>AIC</sub><br>cycles |

| Zero-scale Error          | ZE               |     | ±4      | ±12  | lsb <sup>1</sup>           |

| Full-scale Error          | FE               |     | ±320    | ±370 | lsb <sup>1</sup>           |

| Input Capacitance         | C <sub>AIN</sub> |     | —       | 34   | pF                         |

### Table 12. ASP Electrical Characteristics (continued)