### imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Tiny Real-Time Clock/calendar with alarm function, battery switch-over, time stamp input, and I<sup>2</sup>C-bus

Rev. 4.1 — 27 November 2015

**Product data sheet**

### 1. General description

The PCF85263A is a CMOS<sup>1</sup> Real-Time Clock (RTC) and calendar optimized for low power consumption and with automatic switching to battery on main power loss. The RTC can also be configured as a stop-watch (elapsed time counter). Three time log registers triggered from battery switch-over as well as input driven events. Featuring clock output and two independent interrupt signals, two alarms, I<sup>2</sup>C interface and quartz crystal calibration.

For a selection of NXP Real-Time Clocks, see Table 72 on page 90

### 2. Features and benefits

- UL Recognized Component (PCF85263ATL)

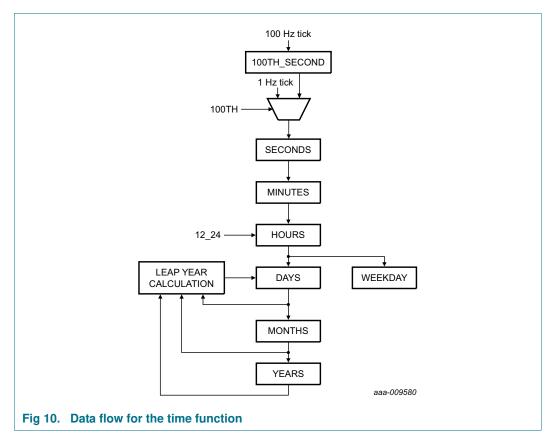

- Provides year, month, day, weekday, hours, minutes, seconds and 100th seconds based on a 32.768 kHz quartz crystal

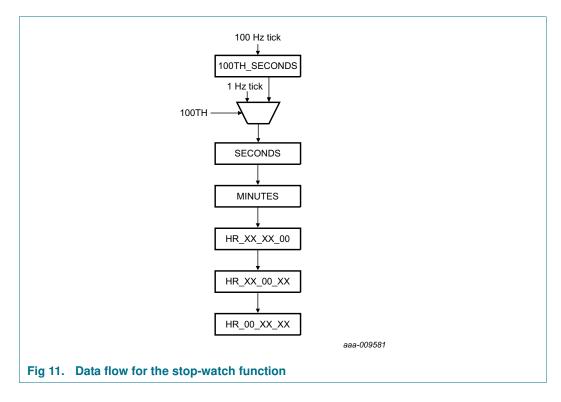

- Stop-watch mode for elapsed time counting. From 100th seconds to 999999 hours

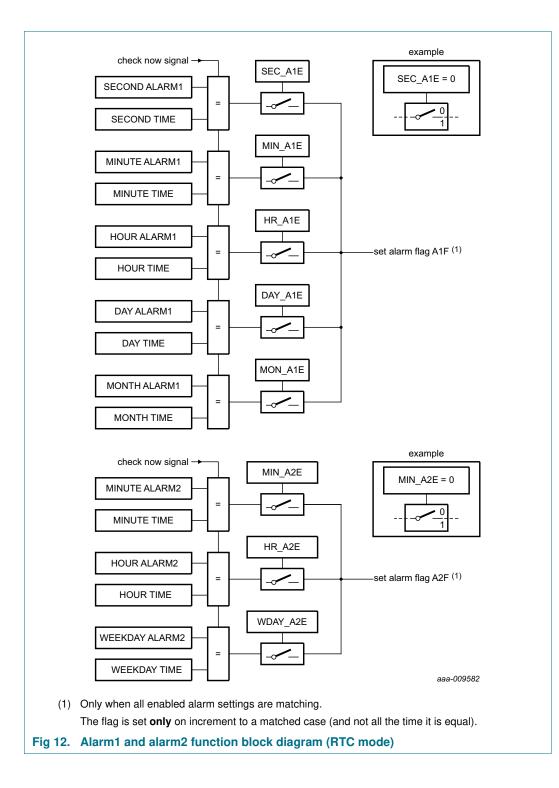

- Two independent alarms

- Battery back-up circuit

- WatchDog timer

- Three timestamp registers

- Two independent interrupt generators plus predefined interrupts at every second, minute, or hour

- Frequency adjustment via programmable offset register

- Clock operating voltage: 0.9 V to 5.5 V

- Low current; typical 0.28 μA at V<sub>DD</sub> = 3.0 V and T<sub>amb</sub> = 25 °C

- 400 kHz two-line I<sup>2</sup>C-bus interface (at V<sub>DD</sub> = 1.8 V to 5.5 V)

- Programmable clock output for peripheral devices (32.768 kHz, 16.384 kHz, 8.192 kHz, 4.096 kHz, 2.048 kHz, 1.024 kHz, and 1 Hz)

- Configurable oscillator circuit for a wide variety of quartzes: C<sub>L</sub> = 6 pF, C<sub>L</sub> = 7 pF, and C<sub>L</sub> = 12.5 pF

### 3. Applications

- Printers and copiers

- Electronic metering

- Digital cameras

<sup>1.</sup> The definition of the abbreviations and acronyms used in this data sheet can be found in Section 24.

### Tiny RTC with alarm, battery switch-over, and I<sup>2</sup>C-bus

- White goods

- Elapsed time counter

- Network powered devices

- Battery backed up systems

- Data loggers

- Digital voice recorders

- Mobile equipment

- Accurate high duration timer

### 4. Ordering information

### Table 1. Ordering information

| Type number  | Package    | Package                                                                                                                          |           |  |  |  |  |  |  |  |

|--------------|------------|----------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|--|--|

|              | Name       | Description                                                                                                                      | Version   |  |  |  |  |  |  |  |

| PCF85263AT   | SO8        | plastic small outline package; 8 leads;<br>body width 3.9 mm                                                                     | SOT96-1   |  |  |  |  |  |  |  |

| PCF85263ATL  | DFN2626-10 | plastic thermal enhanced extremely<br>thin small outline package; no leads;<br>10 terminals; body $2.6 \times 2.6 \times 0.5$ mm | SOT1197-1 |  |  |  |  |  |  |  |

| PCF85263ATT  | TSSOP8     | plastic thin shrink small outline package; 8 leads; body width 3 mm                                                              | SOT505-1  |  |  |  |  |  |  |  |

| PCF85263ATT1 | TSSOP10    | plastic thin shrink small outline package; 10 leads; body width 3 mm                                                             | SOT552-1  |  |  |  |  |  |  |  |

### 4.1 Ordering options

### Table 2. Ordering options

| Product type number | Orderable part number | Sales item<br>(12NC) | Delivery form          | IC<br>revision |

|---------------------|-----------------------|----------------------|------------------------|----------------|

| PCF85263AT/A        | PCF85263AT/AJ         | 935302207118         | tape and reel, 13 inch | 1              |

| PCF85263ATL/A       | PCF85263ATL/AX        | 935302602115         | tape and reel, 7 inch  | 1              |

| PCF85263ATT/A       | PCF85263ATT/AJ        | 935304459118         | tape and reel, 13 inch | 1              |

| PCF85263ATT1/A      | PCF85263ATT1/AJ       | 935304461118         | tape and reel, 13 inch | 1              |

### 5. Marking

| Product type number | Marking code |  |

|---------------------|--------------|--|

| PCF85263AT/A        | 85263A       |  |

| PCF85263ATL/A       | 263A         |  |

| PCF85263ATT/A       | 263A         |  |

| PCF85263ATT1/A      | 263A         |  |

### Tiny RTC with alarm, battery switch-over, and I<sup>2</sup>C-bus

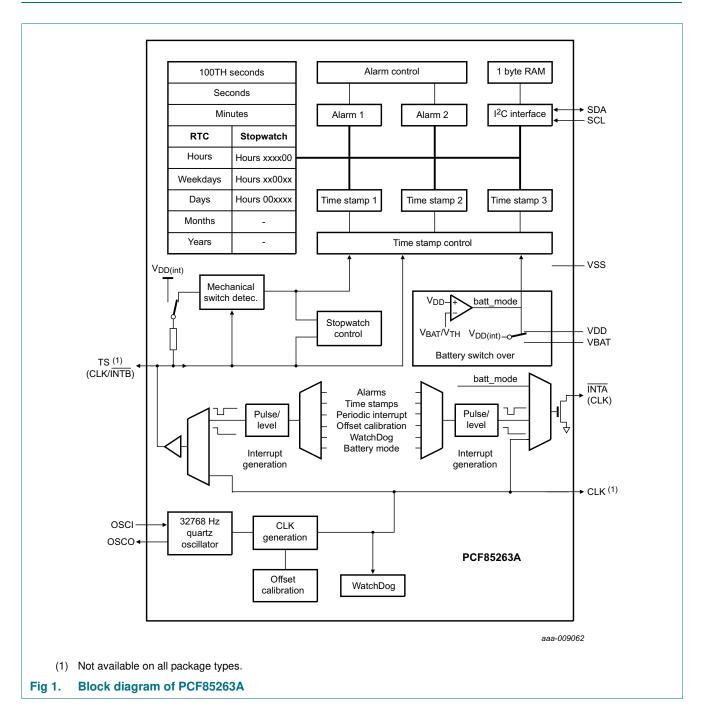

### 6. Block diagram

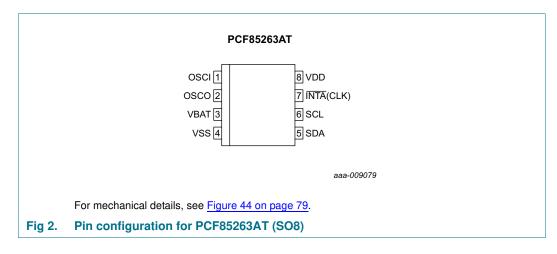

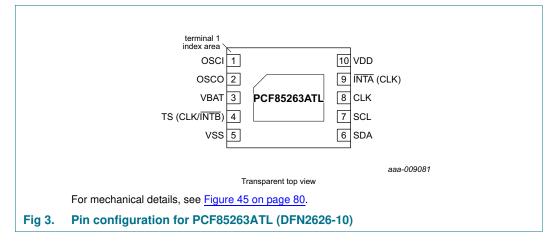

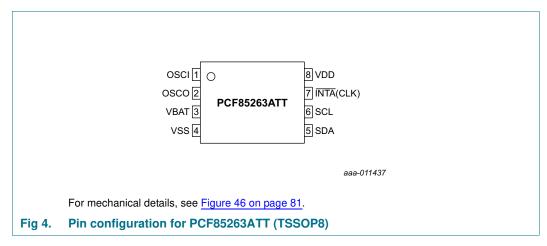

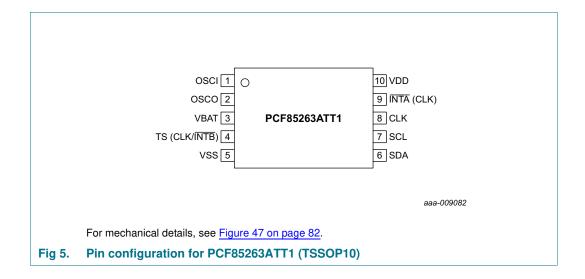

### 7. Pinning information

### 7.1 Pinning

### Tiny RTC with alarm, battery switch-over, and I<sup>2</sup>C-bus

### NXP Semiconductors

## Tiny RTC with alarm, battery switch-over, and I<sup>2</sup>C-bus

PCF85263A

### 7.2 Pin description

### Table 4. Pin description

Input or input/output pins must always be at a defined level (V<sub>SS</sub> or V<sub>DD</sub>) unless otherwise specified.

| Symbol        | Pin                 |                             |                         |                           | Туре             | Description                                  |                                                           |

|---------------|---------------------|-----------------------------|-------------------------|---------------------------|------------------|----------------------------------------------|-----------------------------------------------------------|

|               | PCF85263AT<br>(SO8) | PCF85263ATL<br>(DFN2626-10) | PCF85263ATT<br>(TSSOP8) | PCF85263ATT1<br>(TSSOP10) | _                | Primary use                                  | Secondary use                                             |

| OSCI          | 1                   | 1                           | 1                       | 1                         | input            | oscillator input                             | -                                                         |

| OSCO          | 2                   | 2                           | 2                       | 2                         | output           | oscillator output                            | -                                                         |

| VBAT          | 3                   | 3                           | 3                       | 3                         | supply           | battery backup supply voltage <sup>[1]</sup> | -                                                         |

| TS (CLK/INTB) | -                   | 4                           | -                       | 4                         | input/           | can be configured with TS                    | SPM[1:0] <sup>[2]</sup>                                   |

|               |                     |                             |                         |                           | output           | timestamp input                              | INTB and CLK output<br>(push-pull); stop-watch<br>control |

| VSS           | 4                   | 5 <u>[3]</u>                | 4                       | 5                         | supply           | ground supply voltage                        | -                                                         |

| SDA           | 5                   | 6                           | 5                       | 6                         | input/<br>output | serial data line                             | -                                                         |

| SCL           | 6                   | 7                           | 6                       | 7                         | input            | serial clock input                           | -                                                         |

| CLK           | -                   | 8                           | -                       | 8                         | output           | CLK (push-pull)                              | -                                                         |

| INTA (CLK)    | 7                   | 9                           | 7                       | 9                         | output           | can be configured with IN                    | TAPM[1:0][4]                                              |

|               |                     |                             |                         |                           |                  | interrupt output<br>(open-drain)             | CLK output (open-drain                                    |

| VDD           | 8                   | 10                          | 8                       | 10                        | supply           | supply voltage                               | -                                                         |

[1] Connect to V<sub>DD</sub> if not used.

See Table 7 and Table 47. [2]

[3] The die paddle (exposed pad) is connected to V<sub>SS</sub> through high ohmic (non-conductive) silicon attach and should be electrically isolated. It is good engineering practice to solder the exposed pad to an electrically isolated PCB copper pad as shown in Figure 45 "Package outline SOT1197-1 (DFN2626-10), PCF85263ATL" for better heat transfer but it is not required as the RTC doesn't consume much power. In no case should traces be run under the package exposed pad.

See Table 7 and Table 49. [4]

Product data sheet

PCF85263/

© NXP Semiconductors N.V. 2015. All rights reserved. 6 of 100

### **Functional description** 8.

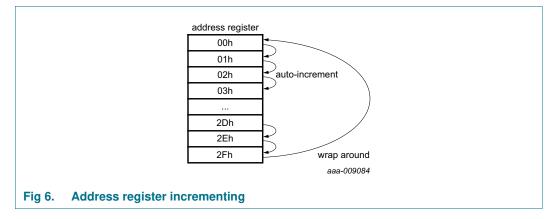

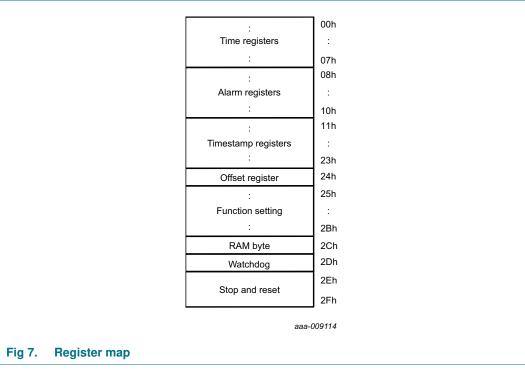

The PCF85263A contains 8-bit registers for time information, for timestamp information and registers for system configuration. Included is an auto-incrementing register address, an on-chip 32.768 kHz oscillator with integrated capacitors, a frequency divider which provides the source clock for the Real-Time Clock (RTC) and calender, and an I<sup>2</sup>C-bus interface with a maximum data rate of 400 kbit/s.

The built-in address register will increment automatically after each read or write of a data byte. After register 2Fh, the auto-incrementing will wrap around to address 00h (see Figure 6).

All registers (see Table 5 on page 9, Table 6 on page 11, and Table 7 on page 13) are designed as addressable 8-bit parallel registers although not all bits are implemented. Figure 7 gives an overview of the address map.

The 100th seconds, seconds, minutes, hours, days, months, and years as well as the corresponding alarm registers are all coded in Binary Coded Decimal (BCD) format. When one of the RTC registers is read, the contents of all time counters are frozen. Therefore, faulty reading of the clock and calendar during a carry condition is prevented.

### 8.1 Registers organization overview

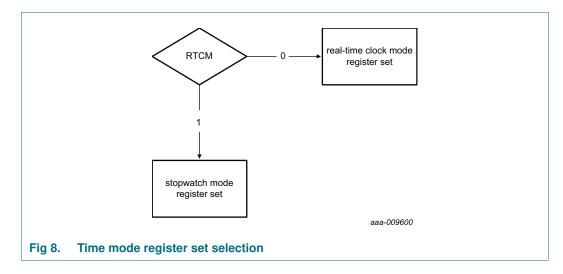

### 8.1.1 Time mode registers

The PCF85263A has two time mode register sets, one for the real-time clock mode and one for the stopwatch clock mode. The access to these registers can be switched by the RTCM bit in the Function control register (28h), see <u>Table 7 on page 13</u> and <u>Table 54 on page 55</u>.

### 8.1.1.1 RTC mode time registers overview (RTCM = 0)

### 8.1.1.1 RTC mode t Table 5. RTC mode time registers

Bit positions labeled as - are not implemented. After reset, all registers are set according to Table 62 on page 59.

| Address          | Register name      | Bit         |              |               |                    |                |              |               |       | Reference      |

|------------------|--------------------|-------------|--------------|---------------|--------------------|----------------|--------------|---------------|-------|----------------|

|                  |                    | 7           | 6            | 5             | 4                  | 3              | 2            | 1             | 0     |                |

| RTC time         | and date registers | ;           |              |               | 1                  |                |              |               |       |                |

| 00h              | 100th_seconds      | 100TH_SEC   | ONDS (0 to 9 | 0 to 99)      |                    |                |              |               |       |                |

| 01h              | Seconds            | OS          | SECONDS      | (0 to 59)     |                    |                |              |               |       |                |

| 02h              | Minutes            | EMON        | MINUTES (    | 0 to 59)      |                    |                |              |               |       |                |

| 03h              | Hours              | -           | -            | AMPM          | HOURS (1 t         | o 12) in 12 ho | ur mode      |               |       |                |

|                  |                    |             |              | HOURS (0      | to 23) in 24 hoι   | ır mode        |              |               |       |                |

| 04h              | Days               | -           | -            | DAYS (1 to    | 31)                |                |              |               |       |                |

| 05h              | Weekdays           | -           | -            | -             | -                  | -              | WEEKDAY      | 'S (0 to 6)   |       |                |

| 06h              | Months             | -           | -            | -             | MONTHS (1          | to 12)         |              |               |       |                |

| 07h              | Years              | YEARS (0 to | 99)          |               | 1                  |                |              |               |       |                |

| <b>RTC</b> alarn | า1                 |             |              |               |                    |                |              |               |       |                |

| 08h              | Second_alarm1      | -           | SEC_ALAF     | RM1 (0 to 59) |                    |                |              |               |       | Section 8.4    |

| 09h              | Minute_alarm1      | -           | MIN_ALAR     | M1 (0 to 59)  |                    |                |              |               |       |                |

| 0Ah              | Hour_alarm1        | -           | -            | AMPM          | HR_ALARM           | 1 (1 to 12) in | 12 hour mode |               |       |                |

|                  |                    |             |              | HR_ALARN      | /11 (0 to 23) in 2 | 4 hour mode    |              |               |       |                |

| 0Bh              | Day_alarm1         | -           | -            | DAY_ALAR      | M1 (1 to 31)       |                |              |               |       |                |

| 0Ch              | Month_alarm1       | -           | -            | -             | MON_ALAR           | M1 (1 to 12)   |              |               |       |                |

| <b>RTC</b> alarn | 12                 |             |              |               |                    |                |              |               |       |                |

| 0Dh              | Minute_alarm2      | -           | MIN_ALAR     | M2 (0 to 59)  |                    |                |              |               |       | Section 8.4    |

| 0Eh              | Hour_alarm2        | -           | -            | AMPM          | HR_ALARM           | 2 (1 to 12) in | 12 hour mode |               |       |                |

| 0Fh              | Weekday_alarm<br>2 | -           | -            | -             | -                  | -              | WDAY_AL      | ARM2 (0 to 6) |       |                |

| RTC alarn        | n enables          |             |              | 1             |                    |                |              |               |       | 1              |

| 10h              | Alarm enables      | WDAY A2E    | HR A2E       | MIN A2E       | MON A1E            | DAY A1E        | HR A1E       | MIN A1E       | SEC A | 1E Section 8.4 |

NXP Semiconductors

N.V. 2015. All rights reserved. 9 of 100

Product data sheet

Rev. 4.1 — 27 November 2015

## **NXP Semiconductors**

Tiny RTC with alarm, battery switch-over, and I<sup>2</sup>C-bus

PCF85263A

Table 5.

RTC mode time registers ...continued

Bit positions labeled as - are not implemented. After reset, all registers are set according to Table 62 on page 59.

| Address                                                                 | Register name   | Bit     |               |                      |                |              |                 |          |    | Reference   |

|-------------------------------------------------------------------------|-----------------|---------|---------------|----------------------|----------------|--------------|-----------------|----------|----|-------------|

|                                                                         |                 | 7       | 6             | 5                    | 4              | 3            | 2               | 1        | 0  |             |

| <b>RTC times</b>                                                        | stamp1 (TSR1)   |         |               | I.                   |                | I            |                 |          |    |             |

| 11h                                                                     | TSR1_seconds    | -       | TSR1_S        | R1_SECONDS (0 to 59) |                |              |                 |          |    |             |

| 12h                                                                     | TSR1_minutes    | -       | TSR1_M        | INUTES (0 to 5       | UTES (0 to 59) |              |                 |          |    |             |

| 13h                                                                     | TSR1_hours      | -       | -             | AMPM                 | TSR1_HC        | OURS (1 to 1 | 2) in 12 hour r | node     |    |             |

|                                                                         |                 |         |               | TSR1_H               | OURS (0 to 23) | in 24 hour n | node            |          |    |             |

| 14h                                                                     | TSR1_days       | -       | -             | TSR1_DA              | AYS (1 to 31)  |              |                 |          |    |             |

| 15h                                                                     | TSR1_months     | -       | -             | -                    | TSR1_M         | ONTHS (1 to  | 12)             |          |    |             |

| 16h                                                                     | TSR1_years      | TSR1_YI | EARS (0 to 99 | ))                   |                |              |                 |          |    |             |

| RTC times                                                               | stamp2 (TSR2)   |         |               |                      |                |              |                 |          |    |             |

| RTC times<br>17h<br>18h<br>19h<br>1Ah<br>1Bh<br>1Ch<br>RTC times<br>1Dh | TSR2_seconds    | -       | TSR2_S        | ECONDS (0 to         | 59)            |              |                 |          |    | Section 8.7 |

| 18h                                                                     | TSR2_minutes    | -       | TSR2_M        | IINUTES (0 to 5      | 59)            |              |                 |          |    |             |

| 19h                                                                     | TSR2_hours      | -       | -             | AMPM                 | TSR2_HC        | OURS (1 to 1 | 2) in 12 hour r | node     |    |             |

| -                                                                       |                 |         |               | TSR2_H               | OURS (0 to 23) | in 24 hour n | node            |          |    |             |

| 1Ah                                                                     | TSR2_days       | -       | -             | TSR2_DA              | AYS (1 to 31)  |              |                 |          |    |             |

| 1Bh                                                                     | TSR2_months     | -       | -             | -                    | TSR2_M         | ONTHS (1 to  | 12)             |          |    |             |

| 1Ch                                                                     | TSR2_years      | TSR2_YI | EARS (0 to 99 | ))                   |                |              |                 |          |    |             |

| RTC times                                                               | stamp3 (TSR3)   |         |               |                      |                |              |                 |          |    |             |

| 1Dh                                                                     | TSR3_seconds    | -       | TSR3_S        | ECONDS (0 to         | 59)            |              |                 |          |    | Section 8.7 |

| 1Eh                                                                     | TSR3_minutes    | -       | TSR3_M        | INUTES (0 to 5       | 59)            |              |                 |          |    |             |

| 1Fh                                                                     | TSR3_hours      | -       | -             | AMPM                 | TSR3_HC        | OURS (1 to 1 | 2) in 12 hour r | node     |    |             |

|                                                                         |                 |         |               | TSR3_H               | OURS (0 to 23) | in 24 hour n | node            |          |    |             |

| 20h                                                                     | TSR3_days       | -       | -             | TSR3_DA              | AYS (1 to 31)  |              |                 |          |    |             |

| 21h                                                                     | TSR3_months     | -       | -             | -                    | TSR3_M0        | ONTHS (1 to  | 12)             |          |    |             |

| 22h<br>RTC times<br>23h                                                 | TSR3_years      | TSR3_YI | EARS (0 to 99 | )                    |                |              |                 |          |    |             |

| RTC times                                                               | stamp mode cont | rol     |               |                      |                |              |                 |          |    |             |

| 23h                                                                     | TSR_mode        | TSR3M[1 | l:0]          | -                    | TSR2M[2        | :0]          |                 | TSR1M[1: | 0] | Section 8.7 |

PCF852 Product data sheet

Rev. 4.1 — 27 November 2015

5. All rights reserved. 10 of 100

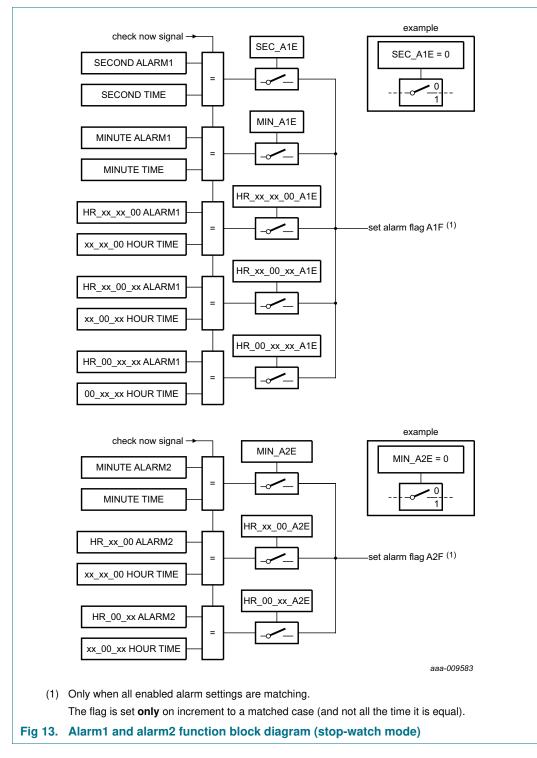

### 8.1.1.2 Stop-watch mode time registers (RTCM = 1)

Table 6.Stop-watch mode time registersBit positions labeled as - are not implemented. After reset, all registers are set according to Table 62 on page 59.

| Address   | Register name    | Bit              |                  |           |                     |                     |                     |         |         | Reference   |

|-----------|------------------|------------------|------------------|-----------|---------------------|---------------------|---------------------|---------|---------|-------------|

|           |                  | 7                | 6                | 5         | 4                   | 3                   | 2                   | 1       | 0       |             |

| Stop-wate | h time registers | 1                |                  |           |                     |                     |                     |         |         |             |

| 00h       | 100th_seconds    | 100TH_SEC        | ONDS (0 to 99    | 9)        |                     |                     |                     |         |         | Section 8.3 |

| 01h       | Seconds          | OS               | SECONDS (        | 0 to 59)  |                     |                     |                     |         |         |             |

| 02h       | Minutes          | EMON             | MINUTES (0       | ) to 59)  |                     |                     |                     |         |         |             |

| 03h       | Hours_xx_xx_00   | HR_XX_XX_        | 00 (0 to 99)     |           |                     |                     |                     |         |         |             |

| 04h       | Hours_xx_00_xx   | HR_XX_00_        | XX (0 to 99)     |           |                     |                     |                     |         |         |             |

| 05h       | Hours_00_xx_xx   | HR_00_XX_        | XX (0 to 99)     |           |                     |                     |                     |         |         |             |

| 06h       | not used         | -                | -                | -         | -                   | -                   | -                   | -       | -       |             |

| 07h       | not used         | -                | -                | -         | -                   | -                   | -                   | -       | -       |             |

| Stop-wate | h alarm1         | 1                |                  |           |                     |                     |                     |         |         |             |

| 08h       | Second_alm1      | -                | SEC_ALM1         | (0 to 59) |                     |                     |                     |         |         | Section 8.4 |

| 09h       | Minute_alm1      | -                | MIN_ALM1 (       | (0 to 59) |                     |                     |                     |         |         |             |

| 0Ah       | Hr_xx_xx_00_alm1 | HR_XX_XX_        | 00_ALM1 (0 t     | to 99)    |                     |                     |                     |         |         |             |

| 0Bh       | Hr_xx_00_xx_alm1 | HR_XX_00_        | XX_ALM1 (0 t     | to 99)    |                     |                     |                     |         |         |             |

| 0Ch       | Hr_00_xx_xx_alm1 | HR_00_XX_2       | XX_ALM1 (0 t     | to 99)    |                     |                     |                     |         |         |             |

| Stop-wate | h alarm2         |                  |                  |           |                     |                     |                     |         |         | Ċ           |

| 0Dh       | Minute_alm2      | -                | MIN_ALM2 (       | (0 to 59) |                     |                     |                     |         |         | Section 8.4 |

| 0Eh       | Hr_xx_00_alm2    | HR_XX_00_        | ALM2 (0 to 99    | ))        |                     |                     |                     |         |         |             |

| 0Fh       | Hr_00_xx_alm2    | HR_00_XX_        | ALM2 (0 to 99    | ))        |                     |                     |                     |         |         |             |

| Stop-wate | h alarm enables  | ·                |                  |           |                     |                     |                     |         |         |             |

| 10h       | Alarm_enables    | HR_00_XX<br>_A2E | HR_XX_00<br>_A2E | MIN_A2E   | HR_00_XX<br>_XX_A1E | HR_XX_00<br>_XX_A1E | HR_XX_XX<br>_00_A1E | MIN_A1E | SEC_A1E | Section 8.4 |

| L         |                  |                  |                  | 1         | 1                   |                     |                     | 1       |         |             |

PCF85263A Product data sheet

NXP Semiconductors N.V. 2015. All rights reserved. 11 of 100

Tiny RTC with alarm, battery switch-over, and I<sup>2</sup>C-bus PCF85263A

## **NXP Semiconductors**

## PCF85263A

# Tiny RTC with alarm, battery switch-over, and I<sup>2</sup>C-bus

### P

Table 6.

Stop-watch mode time registers ...continued

Bit positions labeled as - are not implemented. After reset, all registers are set according to Table 62 on page 59. ...continued

| Address   | Register name       | Bit        |                           |               |       |       |   |       |       |             |  |

|-----------|---------------------|------------|---------------------------|---------------|-------|-------|---|-------|-------|-------------|--|

|           |                     | 7          | 6                         | 5             | 4     | 3     | 2 | 1     | 0     |             |  |

| Stop-watc | h timestamp1 (TSR1) | )          |                           | I             |       |       |   |       |       | I           |  |

| 11h       | TSR1_seconds        | -          | TSR1_S                    | ECONDS (0 to  | o 59) |       |   |       |       | Section 8.7 |  |

| 12h       | TSR1_minutes        | -          | TSR1_MINUTES (0 to 59)    |               |       |       |   |       |       |             |  |

| 13h       | TSR1_hr_xx_xx_00    | TSR1_HR_2  | SR1_HR_XX_XX_00 (0 to 99) |               |       |       |   |       |       |             |  |

| 14h       | TSR1_hr_xx_00_xx    | TSR1_HR_2  | XX_00_XX                  | (0 to 99)     |       |       |   |       |       |             |  |

| 15h       | TSR1_hr_00_xx_xx    | TSR1_HR_0  | 00_XX_XX                  | (0 to 99)     |       |       |   |       |       |             |  |

| 16h       | not used            | -          | -                         | -             | -     | -     | - | -     | -     |             |  |

| Stop-watc | h timestamp2 (TSR2  | )          |                           | I             |       |       |   |       |       |             |  |

| 17h       | TSR2_seconds        | -          | TSR2_S                    | ECONDS (0 to  | o 59) |       |   |       |       | Section 8.7 |  |

| 18h       | TSR2_minutes        | -          | TSR2_M                    | IINUTES (0 to | 59)   |       |   |       |       |             |  |

| 19h       | TSR2_hr_xx_xx_00    | TSR2_HR_2  | X_X_00                    | (0 to 99)     |       |       |   |       |       |             |  |

| 1Ah       | TSR2_hr_xx_00_xx    | TSR2_HR_2  | XX_00_XX                  | (0 to 99)     |       |       |   |       |       |             |  |

| 1Bh       | TSR2_hr_00_xx_xx    | TSR2_HR_0  | 00_XX_XX                  | (0 to 99)     |       |       |   |       |       |             |  |

| 1Ch       | not used            | -          | -                         | -             | -     | -     | - | -     | -     |             |  |

| Stop-watc | h timestamp3 (TSR3  | )          |                           | i             |       |       |   |       |       | ŀ           |  |

| 1Dh       | TSR3_seconds        | -          | TSR3_S                    | ECONDS (0 to  | o 59) |       |   |       |       | Section 8.7 |  |

| 1Eh       | TSR3_minutes        | -          | TSR3_M                    | IINUTES (0 to | 59)   |       |   |       |       |             |  |

| 1Fh       | TSR3_hr_xx_xx_00    | TSR3_HR_2  | X_X_00                    | (0 to 99)     |       |       |   |       |       |             |  |

| 20h       | TSR3_hr_xx_00_xx    | TSR3_HR_2  | XX_00_XX                  | (0 to 99)     |       |       |   |       |       |             |  |

| 21h       | TSR3_hr_00_xx_xx    | TSR3_HR_0  | 00_XX_XX                  | (0 to 99)     |       |       |   |       |       |             |  |

| 22h       | not used            | -          | -                         | -             | -     | -     | - | -     | -     |             |  |

| Stop-watc | h timestamp mode c  | ontrol     |                           |               |       |       |   |       |       |             |  |

| 23h       | TSR_mode            | TSR3M[1:0] |                           | -             | TSR2M | [2:0] |   | TSR1M | [1:0] | Section 8.7 |  |

Product data sheet

Rev. 4.1 — 27 November 2015

iconductors N.V. 2015. All rights reserved.

## **NXP Semiconductors**

## Tiny RTC with alarm, battery switch-over, and I<sup>2</sup>C-bus PCF85263A

### 8.1.2 Control registers overview

### PCF85263A

Table 7.Control and function registers overviewBit positions labeled as - are not implemented. After reset, all registers are set according to <a href="#">Table 62 on page 59</a>.

| Address    | Register name  | Bit       |          |       |       |           |          |          |       | Reference    |

|------------|----------------|-----------|----------|-------|-------|-----------|----------|----------|-------|--------------|

|            |                | 7         | 6        | 5     | 4     | 3         | 2        | 1        | 0     |              |

| Offset reg | jister         |           |          |       |       |           |          |          |       |              |

| 24h        | Offset         | OFFSET[7: | 0]       |       |       |           |          |          |       | Section 8.8  |

| Control re | egisters       |           |          |       |       |           |          |          |       |              |

| 25h        | Oscillator     | CLKIV     | OFFM     | 12_24 | LOWJ  | OSCD[1:0] |          | CL[1:0]  |       | Section 8.10 |

| 26h        | Battery_switch | -         | -        | -     | BSOFF | BSRR      | BSM[1:0] |          | BSTH  | Section 8.11 |

| 27h        | Pin_IO         | CLKPM     | TSPULL   | TSL   | TSIM  | TSPM[1:0] |          | INTAPM[1 | 0]    | Section 8.12 |

| 28h        | Function       | 100TH     | PI[1:0]  | I     | RTCM  | STOPM     | COF[2:0] | I        |       | Section 8.13 |

| 29h        | INTA_enable    | ILPA      | PIEA     | OIEA  | A1IEA | A2IEA     | TSRIEA   | BSIEA    | WDIEA | Section 8.9  |

| 2Ah        | INTB_enable    | ILPB      | PIEB     | OIEB  | A1IEB | A2IEB     | TSRIEB   | BSIEB    | WDIEB | Section 8.9  |

| 2Bh        | Flags          | PIF       | A2F      | A1F   | WDF   | BSF       | TSR3F    | TSR2F    | TSR1F | Section 8.14 |

| RAM byte   | )              |           |          | I     |       |           |          | I        |       |              |

| 2Ch        | RAM_byte       | B[7:0]    |          |       |       |           |          |          |       | Section 8.6  |

| WatchDog   | g registers    |           |          |       |       |           |          |          |       | I            |

| 2Dh        | WatchDog       | WDM       | WDR[4:0] |       |       |           |          | WDS[1:0] |       | Section 8.5  |

| Stop       |                |           |          |       |       |           |          |          |       | I            |

| 2Eh        | Stop_enable    | -         | -        | -     | -     | -         | -        | -        | STOP  | Section 8.16 |

| Reset      |                |           |          |       |       |           |          |          |       | L            |

| 2Fh        | Resets         | CPR       | 0        | 1     | 0     | SR        | 1        | 0        | CTS   | Section 8.15 |

### Product data sheet

Rev. 4.1 ---In this document is 27 November 2015

© NXP Semiconductors N.V. 2015. All rights reserved. 13 of 100

### 8.2 RTC mode time and date registers

RTC mode is enabled by setting RTCM = 0. These registers are coded in the BCD format to simplify application use.

Default state is:

Time — 00:00:00.00

Date — 2000 01 01

Weekday — Saturday

Monitor bits — OS = 1, EMON = 0

### Table 8. Time and date registers in RTC mode (RTCM = 0)

Bit positions labeled as - are not implemented and return 0 when read.

| Address | Register name                | Upper-o | Jpper-digit (ten's place) |        |        | Digit (unit place) |        |       |       |  |

|---------|------------------------------|---------|---------------------------|--------|--------|--------------------|--------|-------|-------|--|

|         |                              | Bit 7   | Bit 6                     | Bit 5  | Bit 4  | Bit 3              | Bit 2  | Bit 1 | Bit 0 |  |

| 00h     | 100th_seconds <sup>[1]</sup> | 0 to 9  |                           |        |        | 0 to 9             |        |       |       |  |

| 01h     | Seconds                      | OS      | 0 to 5                    |        |        | 0 to 9             |        |       |       |  |

| 02h     | Minutes                      | EMON    | 0 to 5                    |        |        | 0 to 9             |        |       |       |  |

| 03h     | Hours <sup>[2]</sup>         | -       | -                         | AMPM   | 0 to 1 | 0 to 9             |        |       |       |  |

|         |                              |         |                           | 0 to 2 |        | 0 to 9             |        |       |       |  |

| 04h     | Days <sup>[3]</sup>          | -       | -                         | 0 to 3 |        | 0 to 9             |        |       |       |  |

| 05h     | Weekdays                     | -       | -                         | -      | -      | -                  | 0 to 6 |       |       |  |

| 06h     | Months                       | -       | -                         | -      | 0 to 1 | 0 to 9             |        |       |       |  |

| 07h     | Years                        | 0 to 9  |                           |        |        | 0 to 9             |        |       |       |  |

[1] The 100th\_seconds register is only available when the 100TH mode is enabled, see <u>Section 8.13.1</u>. When the 100TH mode is disabled, this register always returns 0.

- [2] Hour mode is set by the 12\_24 bit in the Oscillator register, see Section 8.10 on page 42.

- [3] If the year counter contains a value, which is exactly divisible by 4, the PCF85263A compensates for leap years by adding a 29th day to February.

### 8.2.1 Definition of BCD

The Binary-Coded Decimal (BCD) is an encoding of numbers where each digit is represented by a separate bit field. Each bit field may only contain the values 0 to 9. In this way, decimal numbers and counting is implemented.

Example: 59 encoded as an entire number is represented by 3Bh or 111011. In BCD the 5 is represented as 5h or 0101 and the 9 as 9h or 1001 which combines to 59h.

| Upper- | digit (ten'                                    | s place)                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                       | Digit (u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Digit (unit place)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|--------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit 7  | Bit 6                                          | Bit 5                                                                                                                                                                                                                                                  | Bit 4                                                                                                                                                                                                                                                                                                                                                                                                 | Bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 0      | 0                                              | 0                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 0      | 0                                              | 0                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

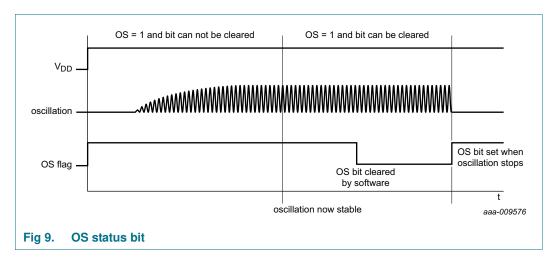

| 0      | 0                                              | 1                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |