Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **INTEGRATED CIRCUITS**

# DATA SHEET

# **PCK2111**

1:10 LVDS clock distribution device

Product Data Supersedes data of 2002 May 14

#### 1:10 LVDS clock distribution device

**PCK2111**

#### **FEATURES**

- 100 ps part-to-part skew

- 35 ps output-to-output skew

- Differential design

- Meets LVDS specification for driver outputs and receiver inputs

- Reference voltage available output V<sub>BB</sub>

- Low voltage V<sub>CC</sub> range of +2.375 V to 2.625 V

- High signalling rate capability (above 622 MHz)

- Supports open, short, and terminated input fail-safe (HIGH output state)

- Programmable drivers power off control

- PCK2111 is identical to and replaces PTN2111

- Available in LQFP32 package

#### **DESCRIPTION**

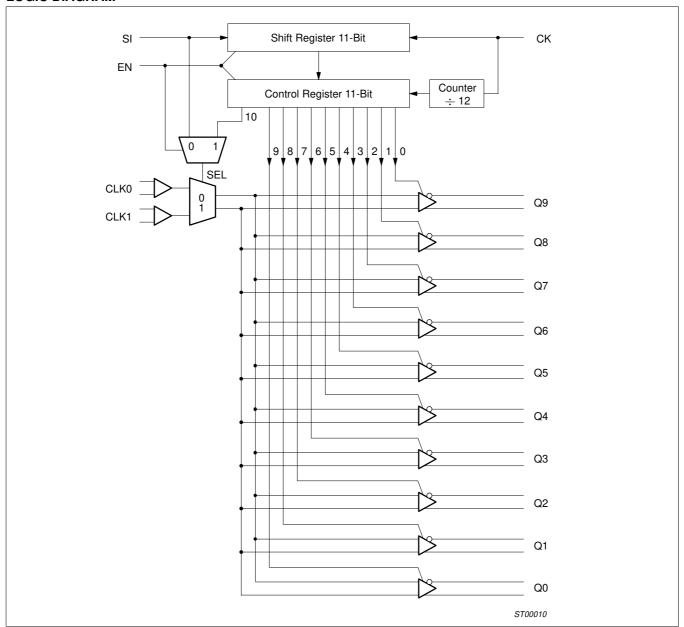

The PCK2111 is a low skew programmable 1:10 LVDS clock distribution device. The selected input signal is fanned out to 10 identical differential outputs.

The PCK2111 features an 11-bit Shift Register with a serial-in and a Control Register. The purpose of the Control Register is to enable or power off each output clock channel and to select the clock input.

The PCK2111 is specifically designed, modeled and produced with low skew as the key goal. Optimal design and layout serve to minimize gate-to-gate skew within a device. The final result is a dependable guaranteed low skew device.

The PCK2111 can be used for high performance clock distribution in +2.5 V systems with LVDS levels. Designers can take advantage of the device's performance to distribute low skew clocks across the backplane or the board.

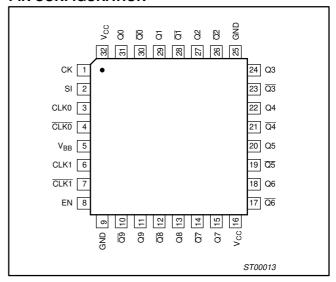

#### PIN CONFIGURATION

#### PIN DESCRIPTION

| PIN NUMBER                                   | SYMBOL          | NAME AND FUNCTION                  |  |  |  |

|----------------------------------------------|-----------------|------------------------------------|--|--|--|

| 1                                            | CK              | Control register clock             |  |  |  |

| 2                                            | SI              | Control register serial-in/CLK_SEL |  |  |  |

| 3                                            | CLK0            | Differential input                 |  |  |  |

| 4                                            | CLK0            | Differential input                 |  |  |  |

| 5                                            | $V_{BB}$        | Output reference voltage           |  |  |  |

| 6                                            | CLK1            | Differential input                 |  |  |  |

| 7                                            | CLK1            | Differential input                 |  |  |  |

| 8                                            | EN              | Device enable/program              |  |  |  |

| 9, 25                                        | GND             | Ground                             |  |  |  |

| 16, 32                                       | V <sub>CC</sub> | Supply voltage                     |  |  |  |

| 31, 29, 27, 24,<br>22, 20, 18, 15,<br>13, 11 | Q[0:9]          | Differential outputs               |  |  |  |

| 30, 28, 26, 23,<br>21, 19, 17, 14,<br>12, 10 | Q[0:9]          | Differential outputs               |  |  |  |

| TYPE NUMBER | NAME   | DESCRIPTION                                                          | VERSION  |

|-------------|--------|----------------------------------------------------------------------|----------|

| PCK2111BD   | LQFP32 | Plastic low profile quad flat package; 32 leads; body 7 x 7 x 1.4 mm | SOT358-1 |

2

### 1:10 LVDS clock distribution device

PCK2111

#### **LOGIC DIAGRAM**

### 1:10 LVDS clock distribution device

PCK2111

#### **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied.

| SYMBOL           | PARAMETER                                                 | LIMITS      | UNIT |

|------------------|-----------------------------------------------------------|-------------|------|

| V <sub>CC</sub>  | Supply voltage                                            | -0.3 to 2.8 | V    |

| I <sub>OSD</sub> | Driver short circuit current                              | continuous  |      |

| ESD              | Electrostatic discharge (Human Body Model 1.5 kΩ, 100 pF) | >2          | kV   |

| $T_{j}$          | Junction temperature                                      | 150         | °C   |

#### RECOMMENDED OPERATING CONDITIONS

| SYMBOL           | PARAMETER                                       | MIN   | MAX             | UNIT |

|------------------|-------------------------------------------------|-------|-----------------|------|

| V <sub>CC</sub>  | Supply voltage                                  | 2.375 | 2.625           | V    |

| V <sub>IR</sub>  | Receiver input voltage                          | GND   | V <sub>CC</sub> |      |

| T <sub>amb</sub> | Operating ambient temperature range in free air | -40   | +85             | °C   |

#### DC ELECTRICAL CHARACTERISTICS

$T_{amb}$  = -40 °C to +85 °C unless otherwise specified;  $V_{CC}$  = 2.5 V ±5% (Notes 1, 2)

| SYMBOL           | PARAMETER                        | CONDITIONS                                                    | MIN   | TYP <sup>2</sup> | MAX   | UNIT |

|------------------|----------------------------------|---------------------------------------------------------------|-------|------------------|-------|------|

| Driver           | •                                | <u> </u>                                                      |       | •                | •     | •    |

| V <sub>OD</sub>  | Output differential voltage      | R <sub>L</sub> = 100 Ω                                        | 250   | 350              | 450   | mV   |

| $\Delta V_{OD}$  | V <sub>OD</sub> magnitude change | R <sub>L</sub> = 100 Ω                                        | _     | _                | 50    | mV   |

| Vos              | Offset voltage                   | R <sub>L</sub> = 100 Ω                                        | 1.125 | 1.25             | 1.375 | V    |

| $\Delta V_{OS}$  | V <sub>OS</sub> magnitude change | R <sub>L</sub> = 100 Ω                                        | _     | _                | 50    | mV   |

| 1                | Output about airevit arresent    | V <sub>O</sub> = 0 V                                          | _     | 15               | 40    | mA   |

| I <sub>OSD</sub> | Output short circuit current     | V <sub>OD</sub> = 0 V                                         |       | 7                | 15    | mA   |

| Receiver         | •                                |                                                               |       |                  |       |      |

| $V_{IDH}$        | Input threshold HIGH             |                                                               | _     | _                | 100   | mV   |

| $V_{IDL}$        | Input threshold LOW              |                                                               | -100  | _                | _     | mV   |

| 1                | Innut ourrent                    | V <sub>IN</sub> = 0 V                                         | _     | 50               | 100   | μΑ   |

| I <sub>IN</sub>  | Input current                    | $V_{IN} = V_{CC}$                                             | _     | 50               | 100   | μΑ   |

| Device           |                                  |                                                               |       |                  |       |      |

| $V_{BB}$         | Output reference voltage         | V <sub>CC</sub> = 2.5 V;<br>∥ <sub>OUT</sub>  ≤ 100 μA        | 1.15  | 1.25             | 1.35  | ٧    |

| I <sub>CCD</sub> | Power supply current             | All drivers enabled and loaded; input frequency = 800 MHz     | _     | 190              | 230   | mA   |

| C <sub>IN</sub>  | Input capacitance                | V <sub>IN</sub> = 0 V to V <sub>CC</sub>                      | _     | 5                | _     | pF   |

| C <sub>OUT</sub> | Output capacitance               |                                                               | _     | 5                | _     | pF   |

| V <sub>IH</sub>  | Logic input HIGH threshold       | V <sub>CC</sub> = 2.5 V                                       | 2     | _                | _     | V    |

| $V_{IL}$         | Logic input LOW threshold        | V <sub>CC</sub> = 2.5 V                                       | _     | _                | 0.8   | V    |

| II               | Logic input current              | $V_{CC} = 2.5 \text{ V};$<br>$V_{IN} = V_{CC} \text{ or GND}$ | _     | _                | ±10   | μΑ   |

#### NOTES:

- 1. All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to device ground unless otherwise specified.

- 2. All typical values are given for  $V_{CC}$  = +2.5 V and  $T_{amb}$  = +25 °C, unless otherwise specified. 3.  $C_L$  includes probe and fixture capacitance.

- 4. Generator waveforms for all tests unless otherwise specified: f = 1 MHz, Z<sub>O</sub> = 50 Ω, 50% duty cycle.

5. The PCK2111 is a current mode device, and only functions to datasheet specifications when a resistive load is applied to the drives outputs.

### 1:10 LVDS clock distribution device

PCK2111

AC ELECTRICAL CHARACTERISTICS (LVDS) T<sub>amb</sub> = -40  $^{\circ}$ C to +85  $^{\circ}$ C unless otherwise specified; V<sub>CC</sub> = 2.5 V  $\pm$ 5% (Note 1)

| SYMBOL                               | PARAMETER                   | CONDITIONS                     | MIN | TYP | MAX | UNIT |

|--------------------------------------|-----------------------------|--------------------------------|-----|-----|-----|------|

| t <sub>TLH</sub>                     | Transition time LOW to HIGH | $R_L = 100 \Omega; C_L = 5 pF$ | 1   | 460 | 560 | ps   |

| t <sub>THL</sub>                     | Transition time HIGH to LOW | $R_L = 100 \Omega; C_L = 5 pF$ |     | 460 | 560 | ps   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay to output |                                | 1   | 1   | 2   | ns   |

| f <sub>MAX</sub>                     | Maximum input frequency     |                                | 650 | 800 | _   | MHz  |

|                                      | Within-device skew          |                                |     | 35  | _   | ps   |

| t <sub>skew</sub>                    | Part-to-part skew           |                                |     | 100 | _   | ps   |

|                                      | Pulse skew                  |                                | _   | 50  | _   | ps   |

| t <sub>JITTER</sub>                  | Cycle-to-cycle jitter       |                                | _   | _   | 1   | ps   |

5

#### NOTE:

<sup>1.</sup> Generator waveforms for all tests unless otherwise specified: f = 1 MHz,  $Z_{O}$  = 50  $\Omega$ , 50% duty cycle.

#### 1:10 LVDS clock distribution device

PCK2111

#### **CONTROL REGISTER SPECIFICATION**

The PCK2111 is provided with an 11-bit shift register with a serial-in and a Control Register. The purpose is to enable or power-off each output clock channel and to select the clock input. The PCK2111 provides two working modes: Programmed mode, and Standard mode.

#### Programmed Mode (EN = 1)

The shift register has a serial input to load the working configuration. Once the configuration is loaded with 11 clock pulses, another clock pulse loads the configuration into the Control Register. To restart the configuration of the shift register, a reset of the state machine must be done with a clock pulse on CK, and the EN set to LOW. The Control Register can be configured only one time after each reset. D0 is the first bit shifted in, D10 is the last bit shifted in. Bit D0 controls Q9, D9 controls Q0, and D10 controls CLKIN.

#### Standard Mode (EN = 0)

In Standard Mode, the PCK2111 is not programmable. All clock buffer outputs are enabled. The LVDS clock input is selected from Clock0 or Clock1 with the SI pin, as shown in the Truth Table.

#### **Table 1. Truth Table of State Machine Inputs**

| EN | SI | CK | OUTPUT                                                                  |

|----|----|----|-------------------------------------------------------------------------|

| L  | L  | X  | All outputs enabled,<br>Clock0 selected,<br>Control Register disabled.  |

| L  | Н  | X  | All outputs enabled,<br>Clock1 selected,<br>Control Register disabled.  |

| Н  | L  |    | First stage stores "L", other stages store the data of previous stage.  |

| Н  | Н  |    | First stage stores "H", other stages store the data of previous stage.  |

| L  | Х  | 5  | Reset of the state machine,<br>Shift register, and Control<br>Register. |

#### Table 2. Configuration of the Control Register

| Control Register bit | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 | D9 | D10     |

|----------------------|----|----|----|----|----|----|----|----|----|----|---------|

| Function             | Q9 | Q8 | Q7 | Q6 | Q5 | Q4 | Q3 | Q2 | Q1 | Q0 | CLK_SEL |

#### Table 3. Truth Table of the Control Register

| D10 | Dn[0:9] | Qn[0:9]            |

|-----|---------|--------------------|

| L   | Н       | Clock0             |

| Н   | Н       | Clock1             |

| X   | Ĺ       | Qn output disabled |

X = Don't Care

#### AC ELECTRICAL CHARACTERISTICS (Control Register)

| SYMBOL           | PARAMETER                           | MIN | TYP | MAX | UNIT |     |

|------------------|-------------------------------------|-----|-----|-----|------|-----|

| $f_{MAX}$        | Maximum frequency of shift register |     | 50  | _   | _    | MHz |

| t <sub>s</sub>   | Clock to SI setup time              |     | _   | _   | 4.0  | ns  |

| t <sub>h</sub>   | Clock to SI hold time               |     | _   | _   | 1.0  | ns  |

| t <sub>rem</sub> | Enable to clock removal time        |     | _   | _   | 4.0  | ns  |

| t <sub>w</sub>   | Minimum clock pulse width           |     | 5   | _   | _    | ns  |

### 1:10 LVDS clock distribution device

PCK2111

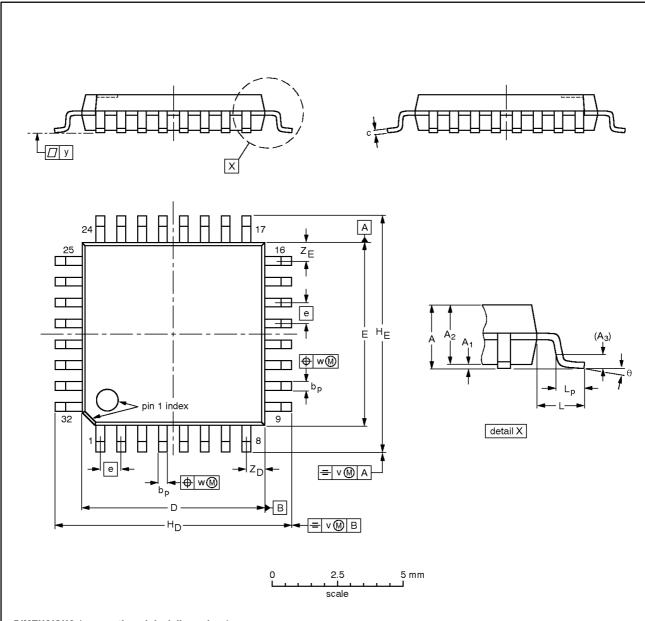

LQFP32: plastic low profile quad flat package; 32 leads; body 7 x 7 x 1.4 mm

SOT358-1

#### DIMENSIONS (mm are the original dimensions)

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | Ьp         | С            | D <sup>(1)</sup> | E <sup>(1)</sup> | e   | Н <sub>D</sub> | HE           | ٦   | Lp           | >   | ¥    | у   | Z <sub>D</sub> <sup>(1)</sup> | Z <sub>E</sub> <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|----------------|------------|--------------|------------------|------------------|-----|----------------|--------------|-----|--------------|-----|------|-----|-------------------------------|-------------------------------|----------|

| mm   | 1.60      | 0.20<br>0.05   | 1.45<br>1.35   | 0.25           | 0.4<br>0.3 | 0.18<br>0.12 | 7.1<br>6.9       | 7.1<br>6.9       | 0.8 | 9.15<br>8.85   | 9.15<br>8.85 | 1.0 | 0.75<br>0.45 | 0.2 | 0.25 | 0.1 | 0.9<br>0.5                    | 0.9<br>0.5                    | 7°<br>0° |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE   |        | REFER  | EUROPEAN | ICCUE DATE |                                  |  |

|-----------|--------|--------|----------|------------|----------------------------------|--|

| VERSION   | IEC    | JEDEC  | EIAJ     | PROJECTION | ISSUE DATE                       |  |

| SOT358 -1 | 136E03 | MS-026 |          |            | <del>99-12-27-</del><br>00-01-19 |  |

### 1:10 LVDS clock distribution device

PCK2111

#### **REVISION HISTORY**

| Rev | Date     | Description                                                           |  |

|-----|----------|-----------------------------------------------------------------------|--|

| _2  | 20021216 | Product data (9397 750 10861); ECN 853-2345 29262 of 09 December 2002 |  |

|     |          | Modifications:                                                        |  |

|     |          | Addition of jitter specification to datasheet.                        |  |

| _1  | 20020514 | Product data (9397 750 09823); ECN 853-2345 28198 of 14 May 2002.     |  |

#### 1:10 LVDS clock distribution device

PCK2111

#### Data sheet status

| Level | Data sheet status[1] | Product<br>status <sup>[2] [3]</sup> | Definitions                                                                                                                                                                                                                                                                                    |

|-------|----------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I     | Objective data       | Development                          | This data sheet contains data from the objective specification for product development.  Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                   |

| II    | Preliminary data     | Qualification                        | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.             |

| III   | Product data         | Production                           | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). |

- [1] Please consult the most recently issued data sheet before initiating or completing a design.

- The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

- [3] For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.

#### **Definitions**

Short-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Life support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes in the products—including circuits, standard cells, and/or software—described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

#### Contact information

For additional information please visit

http://www.semiconductors.philips.com. Fax: +31 40 27 24825 © Koninklijke Philips Electronics N.V. 2002 All rights reserved. Printed in U.S.A.

Date of release: 12-02

Document order number: 9397 750 10861

For sales offices addresses send e-mail to:

sales.addresses@www.semiconductors.philips.com.

Let's make things better.

**Philips** Semiconductors