# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 4 Port PSE PoE Manager

#### DATASHEET

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | KEY FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

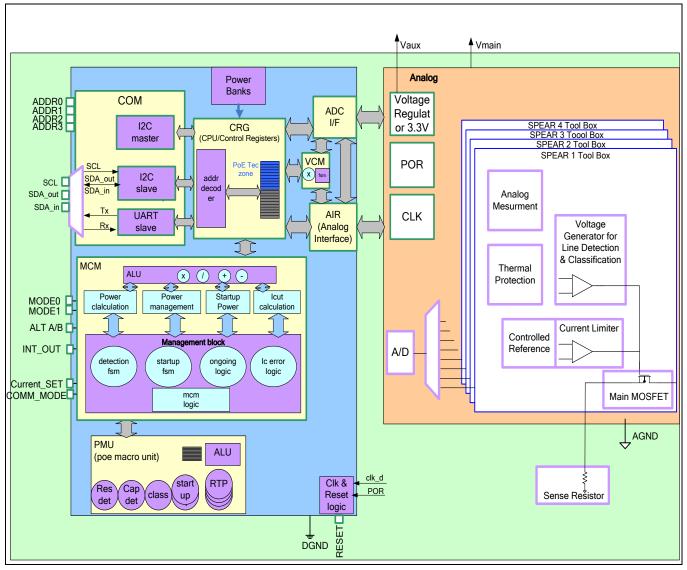

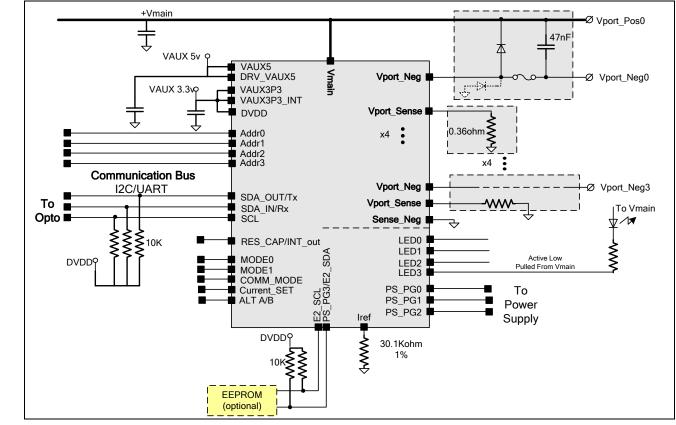

| <b>Microsemi's PD69104B1 Power over Ethernet (PoE) Manager</b><br>enables network devices to share power and data over a single cable.<br>The PD69104B1 PoE Manager chip is employed by both Ethernet<br>switches and Midspans. The device integrates power, analog circuitry<br>and state of the art control logic into a single 48-pin plastic QFN<br>package.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <ul> <li>Supports IEEE802.3af and IEEE802.3at, including two-event classification</li> <li>MSCC Extended Auto, Semi Auto, and Auto modes</li> <li>Supports pre-standard PD detection</li> <li>Supports Cisco devices detection</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <ul> <li>The PD69104B1 device is a 4 port, mixed-signal, high-voltage PoE<br/>Manager. The PD69104B1 supports 2 modes of operation:</li> <li>MSCC Extended Auto mode – this is a stand-alone mode in<br/>which the PD69104B detects IEEE802.3af-2003 compliant<br/>PDs (Powered Devices) and IEEE802.3af-2009 High Power<br/>devices, ensuring safe power feeding and disconnection of<br/>ports based on a power management algorithm while<br/>employing a minimum of external components.</li> <li>Semi Auto mode – allows the host to control which devices are<br/>powered and which are not, as well as to communicate with<br/>the PD69104B1 and to configure it</li> <li>Auto mode – allows turning PDs on and off automatically.<br/>Used for systems with a full power supply.</li> <li>The PD69104B1 executes all real time functions as specified in the<br/>IEEE802.3af-2003 ("AF") and IEEE802.3at High Power ("AT")<br/>standards, including load detection, "AF" and "AT" classifications, and<br/>using Multiple Classification Attempts (MCA).</li> <li>The PD69104B1, supports detect legacy/pre-standard PD devices. It<br/>also provides PD real-time protection through the following<br/>mechanisms: overload, under-load, over-voltage, over-temperature,<br/>and short-circuit. The PD69104B1 supports supply voltages between<br/>44V and 57V with no need for additional power supply sources and<br/>has a built-in thermal protection.</li> </ul> | <ul> <li>Single DC voltage input (44V to 57V)</li> <li>Wide temperature range: -10° to +85°C</li> <li>PD69104B1F version covering -40°C to +85°C</li> <li>Low power dissipation (0.36Ω sense resistor)</li> <li>Drives independent 4/2-pairs power port</li> <li>Supports Extended PoE Protocol and Register Map</li> <li>Includes 2 selectable communication modes (I2C and UART)</li> <li>Includes Reset command pin integrated with an RPD/MRPD mechanism</li> <li>Continuous monitoring port and system data</li> <li>Parameter setting using input pins</li> <li>Parameters setting from external serial EEPROM device</li> <li>Built-in Dynamic Power Management and Emergency Power Management mechanisms with 4 x Power Supply Power Good pins</li> <li>Power soft start mechanism</li> <li>On-chip thermal protection</li> <li>On-chip continual thermal monitoring</li> <li>Voltage/current and temperature monitoring/protection</li> <li>Built-in 3.3V and 5V regulators</li> </ul> |

| The PD69104B1 is a low power device that uses internal MOSFETs and external $0.36\Omega$ sense resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ul><li>Internal power on reset</li><li>MSL1, RoHS compliant</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

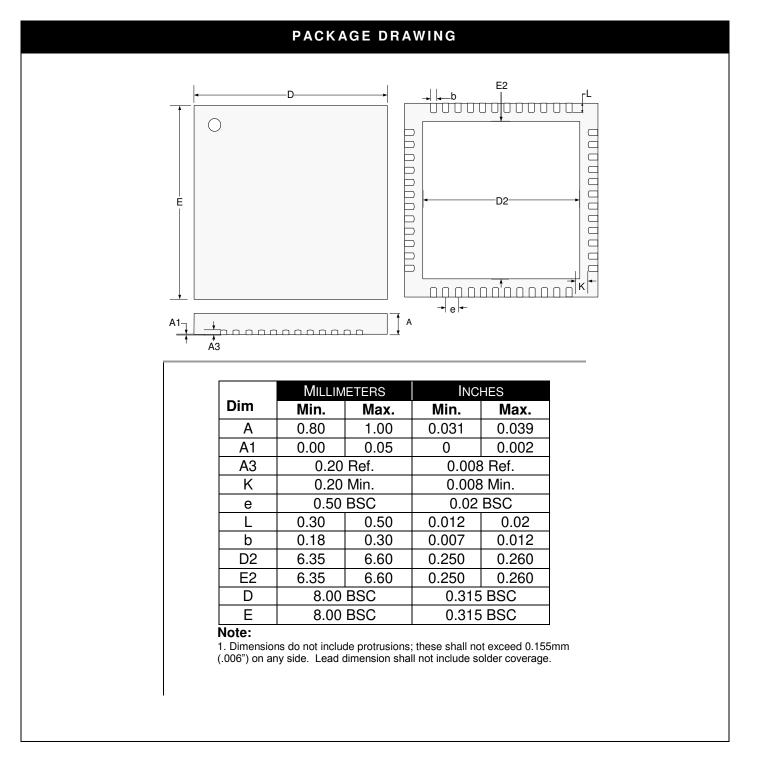

| The PD69104B1 is available in 48 leads, 8 mm x 8 mm QFN package.<br>IMPORTANT: For the most current data, consult MICROSEMI's website: <u>http://www.micro</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | semi.com                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                              | PACKAGE ORDER INFO             | THERMAL DATA                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>A</sub> (°C)                                                                                          | Plastic 48 pin QFN 8x8 mm      | THERMAL RESISTANCE-JUNCTION TO AMBIENT 25° C/W                                                                                                  |

| Γ <sub>Α</sub> (Ο)                                                                                           | RoHS Compliant / Pb-free, MSL1 | THERMAL RESISTANCE-JUNCTION TO CASE $4^{\circ}$ C/W                                                                                             |

| -10 to +85                                                                                                   | PD69104B1ILQ                   | Junction Temperature Calculation: $T_J = T_A + (P_D \times \theta_{JA})$ .                                                                      |

| -40 to +85                                                                                                   | PD69104B1FILQ                  |                                                                                                                                                 |

| <b>Note</b> : Available in Tape and Reel. Append the letters "TR" to the part number. (i.e. PD69104B1ILQ-TR) |                                | The $\theta_{JA}$ numbers are guidelines for the thermal performance of the device/pc-board system. All of the above assume no ambient airflow. |

1

www.Microsemi.com

#### 4 Port PSE PoE Manager

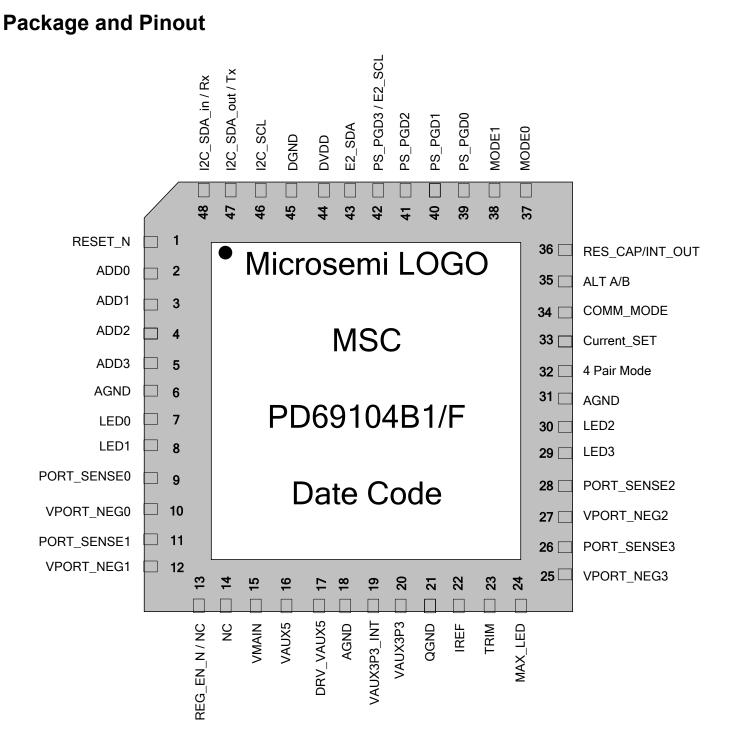

PACKAGE PIN OUT

#### DATASHEET

#### TYPICAL POWER DISSIPATION INFORMATION

$R_{sense}$  Power Dissipation: 0.36 $\Omega \times I_{port}^2$  $R_{ds ON}$  Power Dissipation: 0.3 $\Omega$  x  $I_{port}^{2}$  $P_{\text{port AF}} = 15.4W = >$  Port Power Dissipation @  $R_{\text{sense}} = 37\text{mW}$  (320mA) Port Power Dissipation @  $R_{ds ON} = 31mW$  (320mA) ==> Port Power Dissipation @ R<sub>sense</sub> = 130mW (600mA)  $P_{port AT} = 30W$ Port Power Dissipation @ R<sub>ds ON</sub> = 108mW (600mA) Using Internal 3.3V regulator Typical PD69104B1 self power dissipation (including internal regulations) = 0.5W (50V) Typical PD69104B1 @ 4 x Port AF application power dissipation = 0.5W + 4 x 31mW + 4 x 37mW = 0.77W Typical PD69104B1 @ 4 x Port AT application power dissipation = 0.5W + 4 x 108mW + 4 x 130mW = 1.45W Using External 3.3V regulator Typical PD69104B1 self power dissipation (external 3.3V source) = 0.25W (50V) Typical PD69104B1 @ 4 x Port AF application power dissipation = 0.25W + 4 x 31mW + 4 x 37mW = 0.52W Typical PD69104B1 @ 4 x Port AT application power dissipation = 0.25W + 4 x 108mW + 4 x 130mW = 1.2W

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Input Voltage (V <sub>MAIN</sub> )<br>Port_Neg [07] pins<br>LED pins<br>Port_Sense[07] pins<br>QGND, GND pins<br>VAUX5, DRV_VAUX5<br>All other pins<br>PD69104B1 Operating Ambient<br>Temperature Range<br>PD69104B1F Operating Ambient<br>Temperature Range<br>Maximum Operating Junction<br>Temperature<br>ESD Protection at all I/O pins<br>Storage Temperature Range | $\begin{array}{l} -0.3V_{DC} \text{ to } 74V_{DC} \\ -0.3V_{DC} \text{ to } 74V_{DC} \\ -0.3V_{DC} \text{ to } 74V_{DC} \\ -0.3V_{DC} \text{ to } 3.6V_{DC} \\ -0.3V_{DC} \text{ to } 3.5V_{DC} \\ -0.3V_{DC} \text{ to } 5.5V_{DC} \\ -0.3V_{DC} \text{ to } 3.6V_{DC} \\ -10^{\circ} \text{ to } +85^{\circ}\text{C} \\ -40^{\circ} \text{ to } +85^{\circ}\text{C} \\ +160^{\circ}\text{C} \\ \pm 2\text{KV} \text{ HBM} \\ -65^{\circ} \text{ to } +150^{\circ}\text{C} \end{array}$ | <figure>         Image: displayed bit displ</figure> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Notes:                                                                                                                                                                                                                                                                                                                                                                          | many to the device. All voltages are with                                                                                                                                                                                                                                                                                                                                                                                                                                                | RoHS / Pb-free 100% Matte Tin Finish                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Exceeding these ratings can cause da<br>respect to ground. Currents are mark<br>terminals and marked negative when t                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Copyright © 2013 Rev. 1.3

2

PD69104B1/F

# 4 Port PSE PoE Manager

DATASHEET

### ROHS AND SOLDER REFLOW INFORMATION

RoHS 6/6

Pb-free 100% Matte Tin Finish

Package Peak Temperature for Solder Reflow (40 seconds maximum exposure)

260° C (+0° C, -5° C)

#### Notes:

Exceeding these ratings can cause damage to the device.

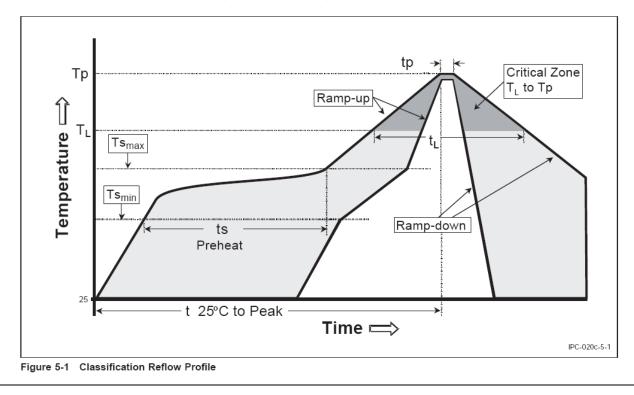

IPC/JEDEC J-STD-020C

July 2004

| Profile Feature                                                                                                                                 | Sn-Pb Eutectic Assembly            | Pb-Free Assembly                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|

| Average Ramp-Up Rate<br>(Ts <sub>max</sub> to Tp)                                                                                               | 3 °C/second max.                   | 3° C/second max.                   |

| Preheat<br>- Temperature Min (Ts <sub>min</sub> )<br>- Temperature Max (Ts <sub>max</sub> )<br>- Time (ts <sub>min</sub> to ts <sub>max</sub> ) | 100 °C<br>150 °C<br>60-120 seconds | 150 °C<br>200 °C<br>60-180 seconds |

| Time maintained above:<br>– Temperature (T <sub>L</sub> )<br>– Time (t <sub>L</sub> )                                                           | 183 °C<br>60-150 seconds           | 217 °C<br>60-150 seconds           |

| Peak/Classification Temperature (Tp)                                                                                                            | See Table 4.1                      | See Table 4.2                      |

| Time within 5 °C of actual Peak<br>Temperature (tp)                                                                                             | 10-30 seconds                      | 20-40 seconds                      |

| Ramp-Down Rate                                                                                                                                  | 6 °C/second max.                   | 6 °C/second max.                   |

| Time 25 °C to Peak Temperature                                                                                                                  | 6 minutes max.                     | 8 minutes max.                     |

Note 1: All temperatures refer to topside of the package, measured on the package body surface.

PD69104B1/F

www.*Microsemi*.com

4 Port PSE PoE Manager

DATASHEET

| Package<br>Thickness | Volume mm³<br><350 | Volume mm <sup>3</sup><br>350 - 2000 | Volume mm <sup>3</sup><br>>2000 |

|----------------------|--------------------|--------------------------------------|---------------------------------|

| <1.6 mm              | 260 +0 °C *        | 260 +0 °C *                          | 260 +0 °C *                     |

| 1.6 mm - 2.5 mm      | 260 +0 °C *        | 250 +0 °C *                          | 245 +0 °C *                     |

| ≥2.5 mm              | 250 +0 °C *        | 245 +0 °C *                          | 245 +0 °C *                     |

# **Electrical Characteristics**

| PARAMETER                                   | SYMBOL TEST CONDITIONS / COMMENT |                                                                          | PD69104B1<br>MANAGER |       |       |                 |

|---------------------------------------------|----------------------------------|--------------------------------------------------------------------------|----------------------|-------|-------|-----------------|

|                                             |                                  |                                                                          | MIN                  | ΤΥΡ   | MAX   |                 |

| POWER SUPPLY                                |                                  |                                                                          |                      |       |       |                 |

| Input Voltage                               | V <sub>MAIN</sub>                | Supports Full IEEE802.3 functionality                                    | 44                   | 55    | 57    | V <sub>DC</sub> |

| Power Supply<br>Current @ Operating<br>Mode | I <sub>MAIN</sub>                | V <sub>MAIN</sub> = 55V                                                  |                      | 10    |       | mA              |

| 5V Output Voltage                           | V <sub>AUX5</sub>                |                                                                          | 4.5                  | 5     | 5.5   | V <sub>DC</sub> |

| 3.3V Output Voltage                         | V <sub>AUX3P3</sub>              |                                                                          | 2.97                 | 3.3   | 3.63  | V <sub>DC</sub> |

|                                             |                                  | Without external NPN                                                     |                      |       | 5     | mA              |

| 3.3V Output Current                         |                                  | With external NPN transistor on VAUX5                                    |                      |       | 30    | mA              |

| 3.3V Input Voltage                          | V <sub>AUX3P3</sub>              | REG_EN_N pin = 3.3V<br>(internal reg. is disabled)<br>VAUX3P3_INT pin=5V | 3                    | 3.3   | 3.6   | V <sub>DC</sub> |

| POWER ON                                    |                                  |                                                                          |                      |       |       |                 |

| RESET (POR)<br>Threshold                    |                                  |                                                                          | 2.575                | 2.775 | 2.975 | V <sub>DC</sub> |

| Hysteresis                                  |                                  |                                                                          | 0.2                  | 0.25  | 0.3   | V <sub>DC</sub> |

| Delay                                       |                                  |                                                                          | 10                   | 50    | 100   | μS              |

4

4 Port PSE PoE Manager

|                               | DATASHEET       |                             |                                    |     |     |                 |  |  |

|-------------------------------|-----------------|-----------------------------|------------------------------------|-----|-----|-----------------|--|--|

| PARAMETER                     | SYMBOL          | TEST CONDITIONS / COMMENT   | P D 6 9 1 0 4 B 1<br>M A N A G E R |     |     | UNITS           |  |  |

|                               |                 |                             | MIN                                | ΤΥΡ | MAX |                 |  |  |

| DIGITAL I/O                   |                 |                             |                                    |     |     |                 |  |  |

| Input Logic High<br>Threshold | V <sub>IH</sub> |                             | 2                                  |     |     | V <sub>DC</sub> |  |  |

| Input Logic Low<br>Threshold  | V <sub>IL</sub> |                             |                                    |     | 0.8 | V <sub>DC</sub> |  |  |

| Input Hysteresis<br>Voltage   |                 |                             | 0.4                                | 0.6 | 0.8 | V <sub>DC</sub> |  |  |

| Input High Current            | I <sub>IH</sub> |                             | -10                                |     | 10  | μA              |  |  |

| Input Low Current             | I <sub>IL</sub> |                             | -10                                |     | 10  | μA              |  |  |

| Output High Voltage           | V <sub>OH</sub> | For I <sub>OH</sub> = -1 mA | 2.4                                |     |     | V <sub>DC</sub> |  |  |

| Output Low Voltage            | V <sub>oL</sub> | I <sub>он</sub> = 1 mA      |                                    |     | 0.4 | V <sub>DC</sub> |  |  |

| POE LOAD<br>CURRENTS        |                 |                                                                                                                                                   |     |     |      |    |

|-----------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|----|

| AT Limit Mode               | AT_LIM_LOW      | Tested With Sense Resistance =<br>$0.366 \Omega$<br>(Rsense+Traces = $0.36 \Omega$ +6m $\Omega$ = $0.366 \Omega$ )<br>connected at port_sense pin | 706 | 722 | 767  | mA |

|                             | AT_LIM_HIGH     |                                                                                                                                                   | 847 | 874 | 919  | mA |

|                             | AT configurable |                                                                                                                                                   | 537 |     | 1200 | mA |

| AF Limit Mode               | AF_LIM          |                                                                                                                                                   | 410 | 425 | 448  | mA |

| PoE Tech High<br>Power Port |                 |                                                                                                                                                   | 808 | 850 | 892  | mA |

| MAIN POWER<br>SWITCHING FET              |                   |                                              |      |     |      |                 |

|------------------------------------------|-------------------|----------------------------------------------|------|-----|------|-----------------|

| On Resistance                            | R <sub>DSON</sub> |                                              |      | 0.3 |      | Ω               |

| Internal Thermal<br>Protection Threshold |                   |                                              |      | 200 |      | °C              |

| LINE DETECTION                           |                   |                                              |      |     |      |                 |

| Range                                    |                   | According to IEEE802.3 standard              | 19   |     | 26.5 | KΩ              |

| CLASSIFICATION                           |                   |                                              |      |     |      |                 |

| Class Event Output<br>Voltage            |                   | Measured between VMAIN and<br>VPORT_NEG pins | 16.5 | 18  | 19.5 | V <sub>DC</sub> |

| Mark Event Output<br>Voltage             |                   | Measured between VMAIN and<br>VPORT_NEG pins | 7.5  | 8.5 | 9.5  | $V_{\text{DC}}$ |

4 Port PSE PoE Manager

|                                                                 |                             | DATASHEET             |       |                            |        |                            |                 |

|-----------------------------------------------------------------|-----------------------------|-----------------------|-------|----------------------------|--------|----------------------------|-----------------|

| PARAMETER                                                       | SYMBOL                      | TEST CONDITIONS / COI | MMENT |                            | D69104 |                            | UNITS           |

|                                                                 |                             |                       |       | MIN                        | ΤΥΡ    | MAX                        |                 |

|                                                                 |                             |                       |       |                            |        |                            |                 |

| LED0 TO 3,<br>MAX_LED<br>DRIVERS                                |                             |                       |       |                            |        |                            |                 |

| Current Sink                                                    | I sink (from VMAIN<br>AGND) | to                    |       |                            | 3      | 5                          | mA              |

|                                                                 |                             |                       |       |                            |        |                            |                 |

| 3 STATES<br>ANALOG INPUT<br>PINS<br>(CURRENT SET,<br>COMM_MODE) |                             |                       |       |                            |        |                            |                 |

| High Level input voltage                                        |                             |                       |       | 80%<br>/ <sub>aux3p3</sub> |        |                            | V <sub>DC</sub> |

| Open                                                            |                             | Not Connected         |       | 40%<br>/ <sub>AUX3P3</sub> |        | 60%<br>V <sub>AUX3P3</sub> | V <sub>DC</sub> |

| Low level input voltage                                         |                             |                       |       |                            |        | 20%<br>V <sub>AUX3P3</sub> | V <sub>DC</sub> |

4 Port PSE PoE Manager

DATASHEET

# **Dynamic Characteristics**

The PD69104B1 utilizes three current level thresholds ( $I_{min}$ ,  $I_{cut}$ ,  $I_{lim}$ ) and three timers ( $T_{min}$ ,  $T_{cut}$ ,  $T_{lim}$ ).

- Loads that consume I<sub>lim</sub> current for more than T<sub>lim</sub> are labeled as 'short circuit state' and are shutdown.

- Loads that dissipate more than I<sub>cut</sub> for longer than T<sub>cut</sub> are labeled as 'overloads' and are shutdown.

- If output power is below  $I_{min}$  for more than  $T_{min}$ , the PD is labeled as 'no-load' and is shutdown.

Automatic recovery from overload and no-load conditions is attempted every  $T_{OVLREC}$  period (typically 1 second). Output power is limited to  $I_{lim}$ , which is the maximum peak current allowed at the port.

#### **Table 1: Operational Mode Parameters**

| PARAMETER                                           |                    | CONDITIONS                                                                                                               | MIN. | TYP. | MAX. | UNIT |

|-----------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Automatic Recovery from<br>No-load Shutdown         |                    | value; measured from port shutdown<br>an be modified through control port)                                               |      | 1    |      | S    |

| Cutoff Timers Accuracy                              | Typical            | accuracy of T <sub>cut</sub>                                                                                             |      | 2    |      | ms   |

| Inrush Current                                      | I <sub>Inrsh</sub> | For t = 50ms, $C_{load}$ = 180µF max.                                                                                    | 400  |      | 450  | mA   |

| Output Current Operating<br>Range                   | I <sub>port</sub>  | Continuous operation after startup period                                                                                | 10   |      | 725  | mA   |

| Output Power Available,<br>Operating Range          | P <sub>port</sub>  | Continuous operation after startup<br>period at port output                                                              | 0.57 |      | 36   | W    |

| Off Mode Current                                    | I <sub>min1</sub>  | Must disconnect where T is greater than $T_{UVL}$                                                                        | 0    |      | 5    | mA   |

|                                                     | I <sub>min2</sub>  | May or may not disconnect where T is greater than T <sub>UVL</sub>                                                       | 5    | 7.5  | 10   | mA   |

| PD Power Maintenance<br>request drop-out time limit | T <sub>PMDO</sub>  | Buffer period to handle transitions                                                                                      | 300  |      | 400  | ms   |

| Overload Time Limit                                 | T <sub>OVL</sub>   |                                                                                                                          | 50   |      | 75   | ms   |

| Turn-on Rise Time                                   | T <sub>rise</sub>  | From 10% to 90% of $V_{port}$<br>(Specified for PD load consisting of 100µF capacitor parallel to 200 $\Omega$ resistor) | 15   |      |      | us   |

| Turn-off Time                                       | T <sub>off</sub>   | From $V_{port}$ to 2.8 $V_{DC}$                                                                                          |      |      | 500  | ms   |

| Time Maintain Power<br>Signature                    | T <sub>MPS</sub>   | DC modulation time for DC<br>disconnect                                                                                  |      | 49   |      | ms   |

4 Port PSE PoE Manager

DATASHEET

#### Table 2: IEEE802.3 AT Mode Parameters

| PARAMETER                                           |                    | CONDITIONS                                                                                                               | MIN. | TYP. | MAX. | UNIT |

|-----------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Automatic Recovery from<br>No-load Shutdown         |                    | value; measured from port shutdown<br>an be modified through control port)                                               |      | 1    |      | S    |

| Cutoff Timers Accuracy                              | Typical            | accuracy of T <sub>cut</sub>                                                                                             |      | 2    |      | ms   |

| Inrush Current                                      | I <sub>Inrsh</sub> | For t = 50ms, $C_{load}$ = 180µF max.                                                                                    | 400  |      | 450  | mA   |

| Output Current Operating range                      | I <sub>port</sub>  | Continuous operation after startup period                                                                                | 10   |      | 725  | mA   |

| Output Power Available,<br>Operating Range          | P <sub>port</sub>  | Continuous operation after startup period at port output                                                                 | 0.57 |      | 36   | w    |

| Off Mode Current                                    | I <sub>min1</sub>  | Must disconnect where T is greater than $T_{UVL}$                                                                        | 0    |      | 5    | mA   |

|                                                     | I <sub>min2</sub>  | May or may not disconnect where T is greater than $T_{UVL}$                                                              | 5    | 7.5  | 10   | mA   |

| PD Power Maintenance<br>request drop-out time limit | T <sub>PMDO</sub>  | Buffer period to handle transitions                                                                                      | 300  |      | 400  | ms   |

| Overload Time Limit                                 | T <sub>OVL</sub>   |                                                                                                                          | 50   |      | 75   | ms   |

| Turn-on Rise Time                                   | T <sub>rise</sub>  | From 10% to 90% of $V_{port}$<br>(Specified for PD load consisting of 100µF capacitor parallel to 200 $\Omega$ resistor) | 15   |      |      | us   |

| Turn-off Time                                       | T <sub>off</sub>   | From V <sub>port</sub> to 2.8V <sub>DC</sub>                                                                             |      |      | 500  | ms   |

| Time Maintain Power<br>Signature                    | T <sub>MPS</sub>   | DC modulation time for DC<br>disconnect                                                                                  |      | 49   |      | ms   |

www.Microsemi.com

4 Port PSE PoE Manager

DATASHEET

PD69104B1 for -10° to +85°C Operating Ambient Temperature Range PD69104B1F for -40° to +85°C Operating Ambient Temperature Range

4 Port PSE PoE Manager

DATASHEET

# **Detailed Pinout Description**

| PIN | PIN NAME    | PIN TYPE             | DESCRIPTION                                                                                                                                                                                                                                                                                                            |  |

|-----|-------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0.  | PAD         | Analog GND           | Exposed PAD: Connect to analog ground (AGND).<br>A decent ground plane should be deployed around this pin whenever<br>possible (refer to PD69104B Layout Design Guidelines)                                                                                                                                            |  |

| 1.  | RESET_N     | Digital Input        | Reset input – active low ('0' = reset)<br>This Pin is also used for RPD / MRPD Function as Described later on<br>this document.<br>Note: This pin should be free of large capacitance in order to prevent<br>RPD & MRPD pulses distortion (please refer to MSCC PD69104B<br>Application Note)                          |  |

| 2.  | ADDR0       | Digital Input        | Address bus for setting the address of the chip. See Table 3.                                                                                                                                                                                                                                                          |  |

| 3.  | ADDR1       | Digital Input        | Address bus for setting the address of the chip. See Table 3.                                                                                                                                                                                                                                                          |  |

| 4.  | ADDR2       | Digital Input        | Address bus for setting the address of the chip. See Table 3.                                                                                                                                                                                                                                                          |  |

| 5.  | ADDR3       | Digital Input        | Address bus for setting the address of the chip. See Table 3.                                                                                                                                                                                                                                                          |  |

| 6.  | AGND        | Power                | Analog ground                                                                                                                                                                                                                                                                                                          |  |

| 7.  | LED 0       | Open Drain<br>Output | Port 0 LED indication – active low ('0' = LED on)<br>See<br>Table 6                                                                                                                                                                                                                                                    |  |

| 8.  | LED 1       | Open Drain<br>Output | Port 1 LED indication – active low ('0' = LED on)<br>See<br>Table 6                                                                                                                                                                                                                                                    |  |

| 9.  | PORT_SENSE0 | Analog Input         | Sense resistor port input (Connected to 0.36 $\Omega$ , 1% resistor to QGN with ~6 m $\Omega$ trace for measurements accuracy).                                                                                                                                                                                        |  |

| 10. | VPORT_NEG0  | Analog I/O           | Negative port output                                                                                                                                                                                                                                                                                                   |  |

| 11. | PORT_SENSE1 | Analog Input         | Sense resistor port input (Connected to 0.36 $\Omega$ , 1% resistor to QGND with ~6 m $\Omega$ trace for measurements accuracy).                                                                                                                                                                                       |  |

| 12. | VPORT_NEG1  | Analog I/O           | Negative port output                                                                                                                                                                                                                                                                                                   |  |

| 13. | REG_EN_N/NC | Analog I/O           | An input pin that enables control of the $3.3V_{DC}$ internal regulator.<br>Disables internal $3.3V_{DC}$ regulator in case external $3.3V_{DC}$ is used to<br>supply the chip.<br>If connected to GND or unconnected – internal regulator is enabled.<br>If connected to $3.3V_{DC}$ – internal regulator is disabled |  |

| 14. | NC          | Analog I/O           | A test pin used only during production.<br>Keep unconnected.                                                                                                                                                                                                                                                           |  |

| 15. | VMAIN       | Power                | Supplies voltage for the internal analog circuitry. A $1\mu$ F (or higher) low ESR bypass capacitor, connected to AGND, should be placed as close as possible to this pin through low resistance traces.                                                                                                               |  |

| 16. | VAUX5       | Power                | Regulated $5V_{DC}$ output voltage source, needs to be connected to a filtering capacitor of $4.7\mu$ F or higher.<br>If an external NPN is used to regulate the voltage, connect this pin to the "Emitter" (the "collector" should be connected to VMAIN).                                                            |  |

4 Port PSE PoE Manager

#### DATASHEET

| PIN | PIN NAME     | PIN TYPE             | DESCRIPTION                                                                                                                                                                                                                          |  |  |  |

|-----|--------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 17. | DRV_VAUX5    | Power                | Driven outputs for $5V_{DC}$ external regulations. In case internal regulation is used, connect to pin 16.<br>In case an external NPN is used to regulate the voltage, connect this pin to the "Base".                               |  |  |  |

| 18. | AGND         | Power                | Analog ground                                                                                                                                                                                                                        |  |  |  |

| 19. | VAUX3P3_INT  | Power                | In case internal 3.3 $V_{DC}$ regulator is used, connected to VAX3P3 (pin 20).<br>In case external $3.3V_{DC}$ regulator is used, connect to VAUX5 (pin 16).                                                                         |  |  |  |

| 20. | VAUX3P3      | Power                | Regulated $3.3V_{DC}$ output voltage source. A $4.7\mu$ F or higher filtering capacitor should be connected between this pin and AGND.<br>When an external $3.3V_{DC}$ regulator is used, connect it to this pin to supply the chip. |  |  |  |

| 21. | QGND         | Power                | Quiet analog ground                                                                                                                                                                                                                  |  |  |  |

| 22. | IREF         | Analog Input         | A reference resistor pin. A 30.1k $\Omega$ , 1% resistor should be connected between this pin and QGND.                                                                                                                              |  |  |  |

| 23. | TRIM         | Test Input           | Trimming input for IC production.<br>Should be connected to VAUX3P3.                                                                                                                                                                 |  |  |  |

| 24. | MAX_LED      | Open Drain<br>Output | MAX LED analog output. Indicates the device has exceeded maximum power budget.<br>See                                                                                                                                                |  |  |  |

| 05  | VEODT NEOD   | A                    | Table 6.                                                                                                                                                                                                                             |  |  |  |

| 25. | VPORT_NEG3   | Analog I/O           | Negative port output                                                                                                                                                                                                                 |  |  |  |

| 26. | PORT_SENSE3  | Analog Input         | Sense resistor port input (Connected to 0.36 $\Omega$ , 1% resistor to QGND with ~6 m $\Omega$ trace for measurements accuracy).                                                                                                     |  |  |  |

| 27. | VPORT_NEG2   | Analog I/O           | Negative port output                                                                                                                                                                                                                 |  |  |  |

| 28. | PORT_SENSE2  | Analog Input         | Sense resistor port input (Connected to 0.36 $\Omega$ , 1% resistor to QGND with ~6 m $\Omega$ trace for measurements accuracy).                                                                                                     |  |  |  |

| 29. | LED 3        | Open Drain<br>Output | Port 3 LED indication – active low ('0' = LED on)<br>See<br>Table 6                                                                                                                                                                  |  |  |  |

| 30. | LED 2        | Open Drain<br>Output | Port 2 LED indication – active low ('0' = LED on)<br>See<br>Table 6                                                                                                                                                                  |  |  |  |

| 31. | AGND         | Power                | Analog ground                                                                                                                                                                                                                        |  |  |  |

| 32. | 4 pairs mode | Analog Input         | <ul> <li>3 state input pin select 4 pairs mode</li> <li>"0" (GND) - 4 ports of 2 pairs.</li> <li>"open" (N.C) - 2 ports of 2 pair &amp; 1 of 4 pair.</li> <li>"1" (VCC) - 2 ports of 4 pair.</li> </ul>                              |  |  |  |

| 33. | Current_SET  | Analog Input         | <ul> <li>3 state input pin, used for selecting output current and AF/AT mode.</li> <li>"0" (AGND) – AF mode</li> <li>"open" (N.C) – Low AT mode 600mA</li> <li>"1" (V<sub>DD</sub>) – High AT mode 720mA</li> </ul>                  |  |  |  |

4 Port PSE PoE Manager

#### DATASHEET

| PIN | PIN NAME         | PIN TYPE                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|-----|------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

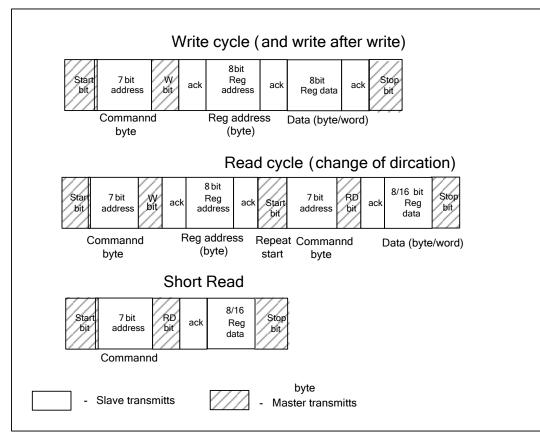

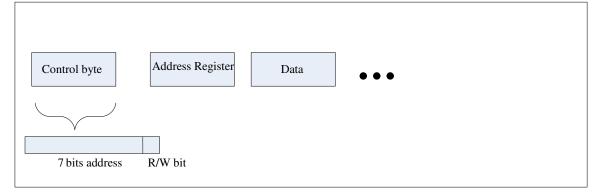

| 34. | COMM_MODE        | Analog Input                | <ul> <li>3 state input pin communication. Following options are available:</li> <li>"0" (AGND) – UART active</li> <li>"open" (N.C) – E2PROM connected</li> <li>"1" (V<sub>DD</sub>) – I2C active</li> </ul>                                                                                                                                                                                                                                                                   |  |  |

| 35. | ALT A/B          | Digital Input               | <ul> <li>User input pin, used for setting the chip working mode.</li> <li>GND – ALT B mode = Midspan mode (midsp [1:4] bits ="1")</li> <li>DVDD – ALT A mode = Endspan mode (midsp [1:4] bits ="0")</li> </ul>                                                                                                                                                                                                                                                                |  |  |

| 36. | INT_OUT          | Digital I/O<br>(open drain) | <ul> <li>In MSCC Extended Auto mode: User input pin. Used for setting the chip legacy detection mode:</li> <li>"1" (V<sub>DD</sub>) – IEEE802.3af compliant resistor detection only</li> <li>"0" (GND) – AF / AT Detection and Legacy (non-standard) line detection</li> <li>In Auto or Semi-Auto modes: Interrupt out pin. Indicates an interruption event has occurred.</li> <li>An external 10K pull-up resistor should be connected between this pin and DVDD.</li> </ul> |  |  |

| 37. | Mode0            | Digital Input               | Used for IC operational mode selection – see<br>Table 4: Mode of Operation                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 38. | Mode1            | Digital Input               | Used for IC operational mode selection – See<br>Table 4: Mode of Operation                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 39. | PS_PGD0          | Digital input               | Power Supply Power Good 0; Power Budget Set pin – for Fast Power Control. (See Table 7)                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 40. | PS_PGD1          | Digital input               | Power Supply Power Good 1; Power Budget Set pin – for Fast Power Control. (See Table 7)                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 41. | PS_PGD2          | Digital input               | Power Supply Power Good 2; Power Budget Set pin – for Fast Power Control. (See Table 7)                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 42. | PS_PGD3 / E2_SCL | Digital I/O<br>(open drain) | <ul> <li>Power Supply Power good 3;</li> <li>Power Budget Set Pin – for initial configuration (See Table 7)</li> <li>Or (refer to COMM MODE PIN)</li> <li>E2_SCL: I2C Clock Out to EEPROM</li> <li>When working with EPROM - An external 10K pull-up resistor should be connected between this pin and DVDD.</li> </ul>                                                                                                                                                       |  |  |

| 43. | E2 SDA           | Digital I/O<br>(open drain) | EEPROM I2C data I/O pin. Used for Power Up configuration in Stand<br>Alone Auto-Mode systems.<br>An external 10K pull-up resistor should be connected between this<br>pin and DVDD.                                                                                                                                                                                                                                                                                           |  |  |

| 44. | DVDD             | Power                       | Digital 3.3V <sub>DC</sub> power input                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 45. | DGND             | Power                       | Digital GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

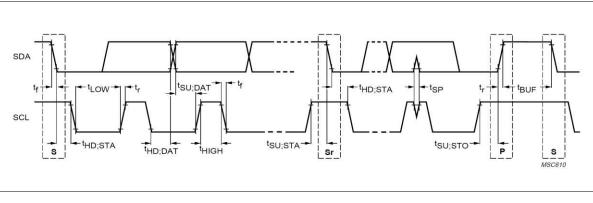

| 46. | I2C SCL          | Digital Input               | I2C bus, serial clock input.<br>An external 10K pull-up resistor should be connected between this<br>pin and DVDD.                                                                                                                                                                                                                                                                                                                                                            |  |  |

# 4 Port PSE PoE Manager

DATASHEET

| PIN | PIN NAME    | PIN TYPE                    | DESCRIPTION                                                                                                                 |  |  |  |

|-----|-------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 47. | I2C_SDA_out | Digital I/O<br>(open drain) | I2C bus, data output / UART Tx output<br>An external 10K pull-up resistor should be connected between this<br>pin and DVDD. |  |  |  |

| 48. | I2C_SDA_in  | Digital I/O<br>(open drain) | I2C bus, data input / UART Rx input<br>An external 10K pull-up resistor should be connected between this<br>pin and DVDD.   |  |  |  |

Note:

- "0" = Connect to DGND

- "1" = Connect to DVDD

4 Port PSE PoE Manager

DATASHEET

| CONST<br>BITS | ADDR3<br>SLAVE<br>1 BIT | ADDR2<br>SLAVE<br>0 BIT | ADDR1<br>ID1<br>BIT | ADDR0<br>ID0<br>BIT | I2C/ UART ADDRESS |  |  |

|---------------|-------------------------|-------------------------|---------------------|---------------------|-------------------|--|--|

| 010           | 0                       | 0                       | 0                   | 0                   | 010000b           |  |  |

| 010           | 0                       | 0                       | 0                   | 1                   | 0100001b          |  |  |

| 010           | 0                       | 0                       | 1                   | 0                   | 0100010b          |  |  |

| 010           | 0                       | 0                       | 1                   | 1                   | 0100011b          |  |  |

| 010           | 0                       | 1                       | 0                   | 0                   | 0100100b          |  |  |

| 010           | 0                       | 1                       | 0                   | 1                   | 0100101b          |  |  |

| 010           | 0                       | 1                       | 1                   | 0                   | 0100110b          |  |  |

| 010           | 0                       | 1                       | 1                   | 1                   | 0100111b          |  |  |

| 010           | 1                       | 0                       | 0                   | 0                   | 0101000b          |  |  |

| 010           | 1                       | 0                       | 0                   | 1                   | 0101001b          |  |  |

| 010           | 1                       | 0                       | 1                   | 0                   | 0101010b          |  |  |

| 010           | 1                       | 0                       | 1                   | 1                   | 0101011b          |  |  |

| 010           | 1                       | 1                       | 0                   | 0                   | 0101100b          |  |  |

| 010           | 1                       | 1                       | 0                   | 1                   | 0101101b          |  |  |

| 010           | 1                       | 1                       | 1                   | 0                   | 0101110b          |  |  |

| 010           | 1                       | 1                       | 1                   | 1                   | 0101111b          |  |  |

#### Table 3: I2C Address Selection Table

#### Notes:

- Address 0000000b is the global address in Extended mode operation I2C (MODE<1:0>='00')

- Address 0110000b is the global address in Auto mode and Semi Auto mode operations (MODE<1:0>='01' or '11')

- All the slaves respond to the global address

- Avoid global read transactions

- Address 0001100b is used for Extended POE address (Alert Response Address) in Auto mode and Semi Auto mode operations

- When reading from this Alert Response address, only slaves that assert the Int\_out pin will send bytes that consist of their own addresses

4 Port PSE PoE Manager

#### DATASHEET

#### Table 4: Mode of Operation

| Mode 1 | Mode 0 | Mode                          | Comm. to the IC                    | Functionality                                                                                                                                                                                                                            | Remarks                                                                                            |  |

|--------|--------|-------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|

| 0      | 0      | MSCC<br>Extended Auto<br>Mode | I2C or UART<br>(see COMM_MODE pin) | Fully autonomous operation<br>without a need for Host<br>Controller (MCU) This Mode<br>Supports Extended Registers<br>Map.<br>Default Operation: With No<br>Interrupt Function (Interrupt can be<br>enabled by communication<br>command) | I2C or UART Protocol to<br>Host with extended register<br>map and PM (Power<br>Management) support |  |

| 0      | 1      | Semi Auto<br>mode             | I2C or UART<br>(see COMM_MODE pin) | Host should manage the ports                                                                                                                                                                                                             | I2C Protocol to Host                                                                               |  |