Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# PE42723

## **Document Category: Product Specification**

## UltraCMOS® SPDT RF Switch, 5-1794 MHz

### **Features**

- Supports DOCSIS 3.0/1 requirements

- · Exceptional harmonics

- 2fo of -121 dBc @ 17 MHz

- 3fo of -140 dBc @ 17 MHz

- · Best in class linearity across frequency band

- Low insertion loss and high isolation performance

- Insertion loss of 0.3 dB @ 1218 MHz

- Isolation of 54 dB @ 204 MHz

- · High ESD performance of 3 kV HBM

- Packaging 12-lead 3 × 3 × 0.75 mm QFN

# **Applications**

- Broadband market (DOCSIS 3.0/1)

- Cable modem

- Set-top box

- Residential gateway

- · Filter bank switching

- Relay replacement between DOCSIS 3.0 and DOCSIS 3.1 configurations

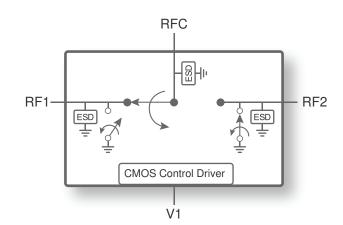

Figure 1 • PE42723 Functional Diagram

## **Product Description**

The PE42723 is a HaRP™ technology-enhanced reflective SPDT RF switch designed for use in cable applications including DOCSIS 3.0/1 cable modem, set-top box and residential gateway. It delivers high linearity and excellent harmonics performance in the 5–1794 MHz band. It also features low insertion loss and high isolation performance making the PE42723 ideal for DOCSIS 3.1 applications.

The PE42723 is manufactured on Peregrine's UltraCMOS® process, a patented variation of silicon-on-insulator (SOI) technology on a sapphire substrate, offering the performance of GaAs with the economy and integration of conventional CMOS.

©2015–2016, Peregrine Semiconductor Corporation. All rights reserved. • Headquarters: 9380 Carroll Park Drive, San Diego, CA, 92121

## **Absolute Maximum Ratings**

Exceeding absolute maximum ratings listed in **Table 1** may cause permanent damage. Operation should be restricted to the limits in **Table 2**. Operation between operating range maximum and absolute maximum for extended periods may reduce reliability.

### **ESD Precautions**

When handling this UltraCMOS device, observe the same precautions as with any other ESD-sensitive devices. Although this device contains circuitry to protect it from damage due to ESD, precautions should be taken to avoid exceeding the rating specified in **Table 1**.

## Latch-up Immunity

Unlike conventional CMOS devices, UltraCMOS devices are immune to latch-up.

Table 1 • Absolute Maximum Ratings for PE42723

| Parameter/Condition                       | Min         | Max  | Unit |

|-------------------------------------------|-------------|------|------|

| Supply voltage, V <sub>DD</sub>           | -0.3        | 5.5  | V    |

| Digital input voltage, V1                 | -0.3        | 3.6  | V    |

| RF input power, 75Ω                       |             | 86   | dBmV |

| Storage temperature range                 | <b>–</b> 65 | +150 | °C   |

| ESD voltage HBM <sup>(1)</sup> , all pins |             | 3000 | V    |

| ESD voltage CDM <sup>(2)</sup> , all pins |             | 500  | V    |

<sup>1)</sup> Human body model (MIL-STD 883 Method 3015).

<sup>2)</sup> Charged device model (JEDEC JESD22-C101).

# **Recommended Operating Conditions**

**Table 2** lists the recommended operating conditions for the PE42723. Devices should not be operated outside the operating conditions listed below.

Table 2 • Recommended Operating Conditions for PE42723

| Parameter                           | Min  | Тур | Max                | Unit |

|-------------------------------------|------|-----|--------------------|------|

| Supply voltage, V <sub>DD</sub>     | 2.3  | 3.3 | 5.5                | V    |

| Supply current, I <sub>DD</sub>     |      | 130 | 200                | μΑ   |

| Digital input high, V1              | 1.17 |     | 3.6 <sup>(1)</sup> | V    |

| Digital input low, V1               | -0.3 |     | 0.6                | V    |

| RF input power, CW <sup>(2)</sup>   |      |     | 80                 | dBmV |

| RF input power, peak <sup>(3)</sup> |      |     | 85                 | dBmV |

| Operating temperature range         | -40  | +25 | +85                | °C   |

<sup>1)</sup> Maximum digital input voltage is limited to  $\ensuremath{V_{DD}}$  and cannot exceed 3.6V.

<sup>2) 100%</sup> duty cycle,  $75\Omega$ .

<sup>3)</sup> OFDMA DOCSIS 3.1, single channel,  $75\Omega$ .

# **Electrical Specifications**

**Table 3** provides the PE42723 key electrical specifications @ +25 °C,  $V_{DD}$  = 3.3V,  $Z_{S}$  =  $Z_{L}$  = 75 $\Omega$ , unless otherwise specified.

Table 3 • PE42723 Electrical Specifications

| Parameter                                    | Path      | Condition                                                                                               | Min            | Тур                  | Max          | Unit                 |

|----------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------|----------------|----------------------|--------------|----------------------|

| Operating frequency                          |           |                                                                                                         | 5              |                      | 1794         | MHz                  |

| Insertion loss <sup>(1)</sup>                | RFC-RFX   | 5–204 MHz<br>204–1218 MHz<br>1218–1794 MHz                                                              |                | 0.10<br>0.30<br>0.40 | 0.20<br>0.45 | dB<br>dB<br>dB       |

| Isolation                                    | All paths | 5–204 MHz<br>204–612 MHz<br>612–1218 MHz<br>1218–1794 MHz                                               | 50<br>40<br>36 | 54<br>44<br>38<br>34 |              | dB<br>dB<br>dB<br>dB |

| Return loss <sup>(1)</sup>                   | RFC-RFX   | 5–204 MHz<br>204–612 MHz<br>612–1218 MHz<br>1218–1794 MHz                                               | 25<br>18       | 30<br>22<br>14<br>13 |              | dB<br>dB<br>dB<br>dB |

| 2nd harmonic, 2fo                            | RFX       | fo = 17 MHz<br>Average $P_{CW}$ = 65 dBmV<br>fo = 170 MHz<br>Average $P_{CW}$ = 65 dBmV<br>fo = 900 MHz |                | -121<br>-121<br>-121 |              | dBc<br>dBc<br>dBc    |

| 3rd harmonic, 3fo                            | RFX       | Average P <sub>CW</sub> = 65 dBmV  fo = 17 MHz  Average P <sub>CW</sub> = 65 dBmV  fo = 170 MHz         |                | -140<br>-132         |              | dBc<br>dBc           |

|                                              |           | Average $P_{CW} = 65 \text{ dBmV}$<br>fo = 900 MHz<br>Average $P_{CW} = 65 \text{ dBmV}$                |                | -135                 |              | dBc                  |

| Input 0.1dB compression point <sup>(2)</sup> | RFC-RFX   | 5–1218 MHz                                                                                              |                | 87                   |              | dBmV                 |

| Switching time                               |           | 50% CTRL to 90% or 10% RF                                                                               |                | 35                   |              | μs                   |

<sup>1)</sup> High frequency performance can be improved by external matching (see Figure 12-Figure 15).

<sup>2)</sup> The input 0.1dB compression point is a linearity figure of merit. Refer to Table 2 for the operating RF input power (75Ω).

## **Switching Frequency**

The PE42723 has a maximum 10 kHz switching frequency. Switching frequency describes the time duration between switching events. Switching time is the time duration between the point the control signal reached 50% of the final value and the point the output signal reaches within 10% or 90% of its target value.

## **Spurious Performance**

The PE42723 spur fundamental occurs around 10 MHz. Its typical performance is -154 dBm/Hz (V1 = H) and -165 dBm/Hz (V1 = L), with 100 kHz bandwidth.

### **Thermal Data**

Psi-JT  $(\Psi_{JT})$ , junction top-of-package, is a thermal metric to estimate junction temperature of a device on the customer application PCB (JEDEC JESD51-2).

$$\Psi_{JT} = (T_J - T_T)/P$$

#### where

$\Psi_{\text{JT}}$  = junction-to-top of package characterization parameter, °C/W

T<sub>.1</sub> = die junction temperature, °C

$T_T$  = package temperature (top surface, in the center), °C

P = power dissipated by device, Watts

Table 4 • Thermal Data for PE42723

| Parameter                                                                                     | Тур | Unit |

|-----------------------------------------------------------------------------------------------|-----|------|

| Maximum junction temperature, T <sub>JMAX</sub> (RF input power, CW = 80 dBmV, +85°C ambient) | 90  | °C   |

| $\Psi_{JT}$                                                                                   | 21  | °C/W |

## **Control Logic**

**Table 5** provides the control logic truth table for the PE42723.

**Table 5 • Truth Table for PE42723**

| State   | V1 |

|---------|----|

| RFC-RF1 | Н  |

| RFC-RF2 | L  |

# **Typical Performance Data**

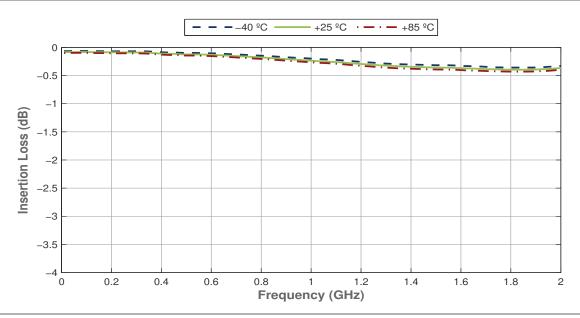

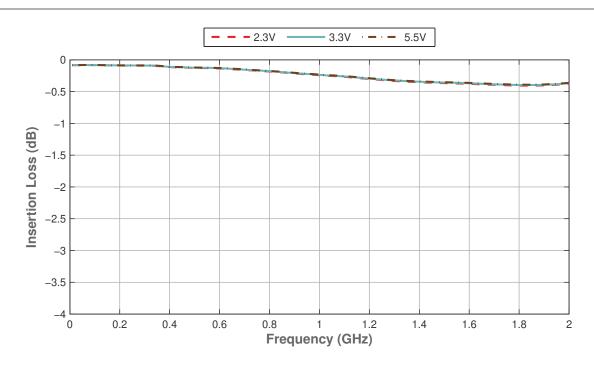

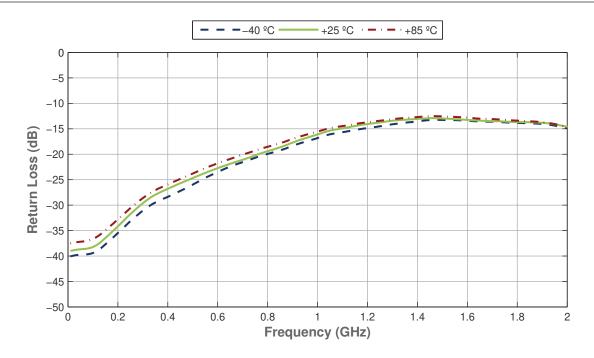

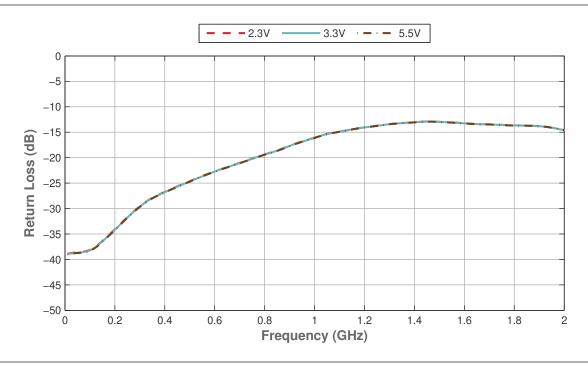

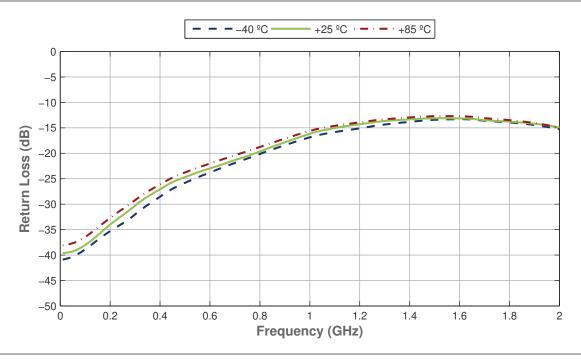

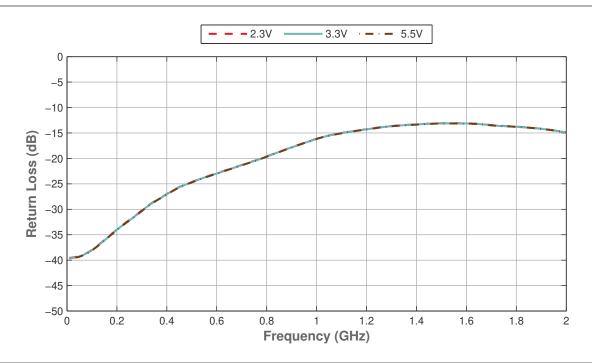

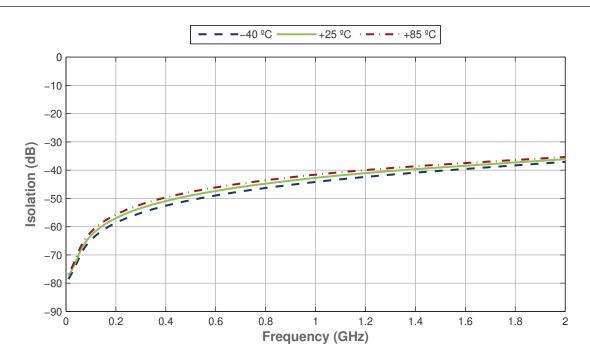

Figure 2–Figure 11 show the typical performance data @ +25 °C,  $V_{DD}$  = 3.3V,  $Z_{S}$  =  $Z_{L}$  = 75 $\Omega$ , unless otherwise specified.

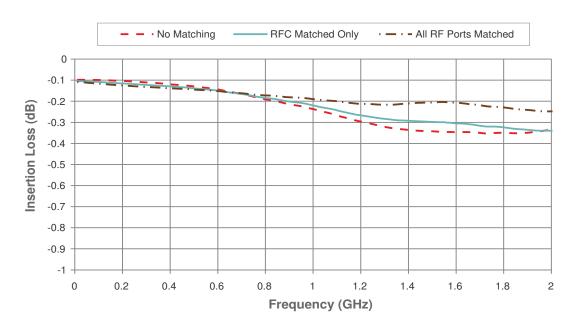

Figure 2 • Insertion Loss vs Temperature (RFC-RFX)(\*)

Note: \* High frequency performance can be improved by external matching (see Figure 12-Figure 15).

Figure 3 • Insertion Loss vs  $V_{DD}$  (RFC-RFX)(\*)

Note: \* High frequency performance can be improved by external matching (see Figure 12-Figure 15).

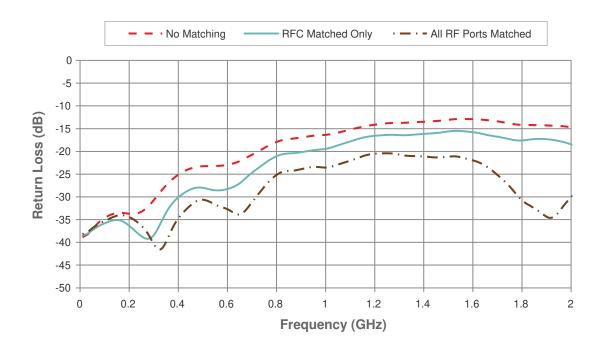

Figure 4 • RFC Port Return Loss vs Temperature(\*)

Note: \* High frequency performance can be improved by external matching (see Figure 12–Figure 15).

Figure 5 • RFC Port Return Loss vs  $V_{DD}^{(*)}$

Note: \* High frequency performance can be improved by external matching (see Figure 12-Figure 15).

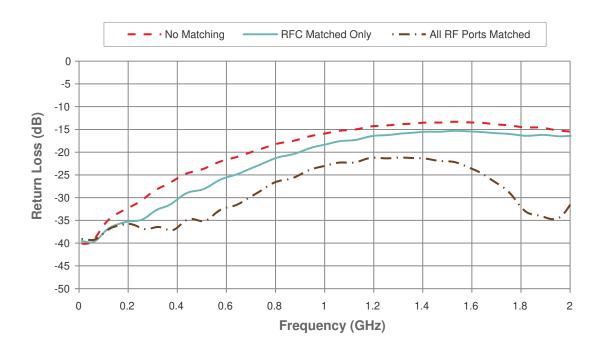

Figure 6 • Active Port Return Loss vs Temperature(\*)

Note: \* High frequency performance can be improved by external matching (see Figure 12–Figure 15).

Figure 7 • Active Port Return Loss vs  $V_{DD}^{(*)}$

Note: \* High frequency performance can be improved by external matching (see Figure 12-Figure 15).

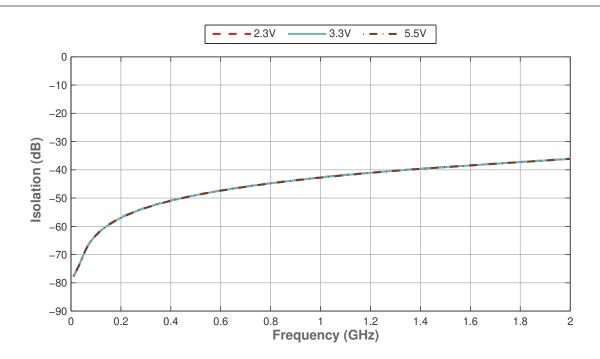

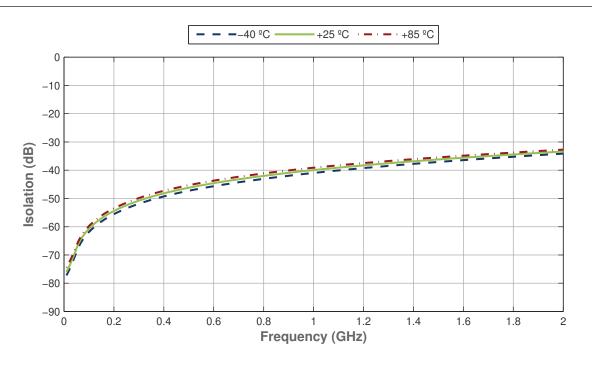

Figure 8 • Isolation vs Temperature (RFX-RFX)

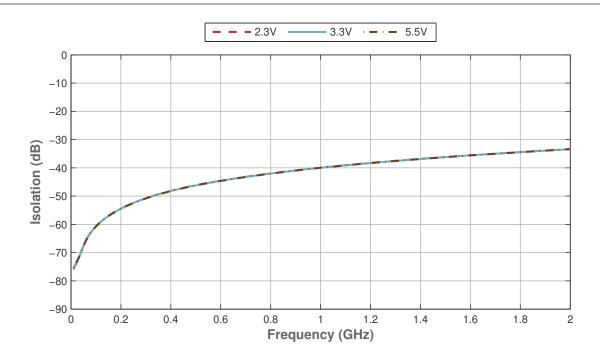

Figure 9 • Isolation vs  $V_{DD}$  (RFX-RFX)

Figure 10 • Isolation vs Temperature (RFC-RFX)

Figure 11 • Isolation vs  $V_{DD}$  (RFC-RFX)

Page 10

# High Frequency Performance with External Matching

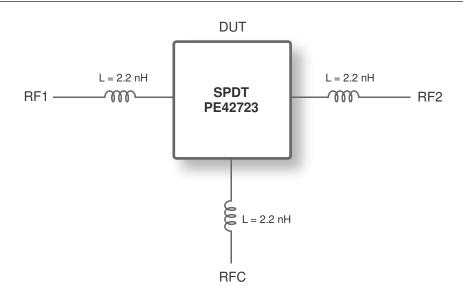

High frequency insertion loss and return loss can be improved by inductive matching on the RF ports in the customer application board layout. **Figure 12** is a matching network using a 2.2 nH inductor on each RF port. The inductor needs to be placed as close to the device under test (DUT) as possible. **Figure 13–Figure 15** show the insertion loss and return loss improvement using a 2.2 nH inductor on RFC port and a 2.2 nH on RF1, RF2 and RFC ports, respectively.

Figure 12 • PE42723 Matching Network

Figure 13 • Insertion Loss (RFC-RFX) With or Without Matching(\*)

Note: \* For reference only.

Figure 14 • RFC Port Return Loss With or Without Matching(\*)

Note: \* For reference only.

Figure 15 • Active Port Return Loss With or Without Matching<sup>(\*)</sup>

Note: \* For reference only.

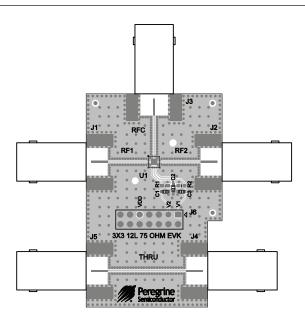

## **Evaluation Kit**

The PE42723 evaluation board was designed to ease customer evaluation of the PE42723 RF switch. The RF common port is connected through a  $75\Omega$  transmission line via the F-Type connector, J3. RF1 and RF2 ports are connected through  $75\Omega$  transmission lines via F-Type connectors J1 and J2, respectively. A  $75\Omega$  through transmission line is available via F-Type connectors J4 (THRU left) and J5 (THRU right), which can be used to deembed the loss of the PCB. J6 provides DC and digital inputs to the device.

Figure 16 • Evaluation Kit Layout for PE42723

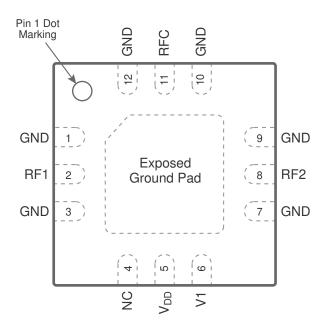

## **Pin Information**

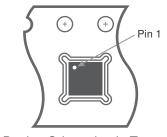

This section provides pinout information for the PE42723. **Figure 17** shows the pin map of this device for the available package. **Table 6** provides a description for each pin.

Figure 17 • Pin Configuration (Top View)

Table 6 • Pin Descriptions for PE42723

| Pin No.               | Pin<br>Name        | Description                              |  |

|-----------------------|--------------------|------------------------------------------|--|

| 1, 3, 7, 9,<br>10, 12 | GND                | Ground                                   |  |

| 2                     | RF1 <sup>(*)</sup> | RF port 1                                |  |

| 4                     | NC                 | Do not connect                           |  |

| 5                     | $V_{DD}$           | Supply voltage (nominal 3.3V)            |  |

| 6                     | V1                 | Digital control logic input 1            |  |

| 8                     | RF2 <sup>(*)</sup> | RF port 2                                |  |

| 11                    | RFC <sup>(*)</sup> | RF common                                |  |

| Pad                   | GND                | Exposed pad: ground for proper operation |  |

Note: \* RF pins 2, 8 and 11 must be at 0 VDC. The RF pins do not require DC blocking capacitors for proper operation if the 0 VDC requirement is met.

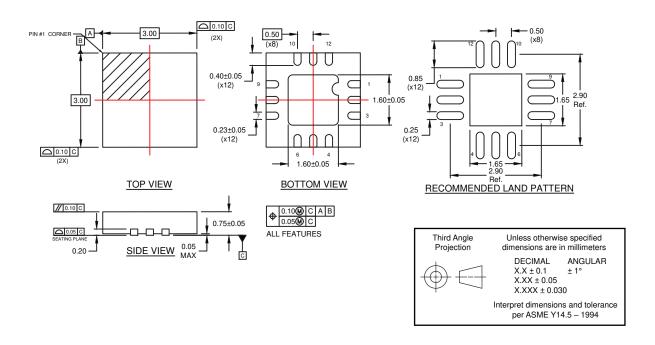

# **Packaging Information**

This section provides packaging data including the moisture sensitivity level, package drawing, package marking and tape-and-reel information.

## **Moisture Sensitivity Level**

The moisture sensitivity level rating for the PE42723 in the 12-lead 3 × 3 × 0.75 mm QFN package is MSL1.

## **Package Drawing**

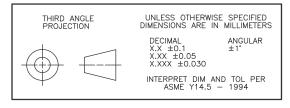

Figure 18 • Package Mechanical Drawing for 12-lead 3 × 3 × 0.75 mm QFN

## **Top-Marking Specification**

Figure 19 • Package Marking Specifications for PE42723

42723 YYWW ZZZZZZ

= Pin 1 indicator

YY = Last two digits of assembly year

WW = Assembly work week

ZZZZZZ = Assembly lot code (maximum six characters)

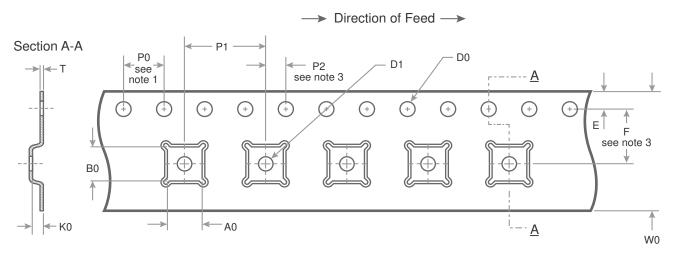

## Tape and Reel Specification

Figure 20 • Tape and Reel Specifications for 12-lead  $3 \times 3 \times 0.75$  mm QFN

| A0 | 3.30             |  |  |

|----|------------------|--|--|

| B0 | 3.30             |  |  |

| K0 | 1.10             |  |  |

| D0 | 1.50 + 0.1/ -0.0 |  |  |

| D1 | 1.5 min          |  |  |

| E  | 1.75 ± 0.10      |  |  |

| F  | 5.50 ± 0.05      |  |  |

| P0 | 4.00             |  |  |

| P1 | 8.00             |  |  |

| P2 | 2.00 ± 0.05      |  |  |

| Т  | 0.30 ± 0.05      |  |  |

| W0 | 12.00 + 0.3      |  |  |

| 1. 1 | 0 | Sprocket | hole | pitch | cumulative | tolerance | ±0.2 |

|------|---|----------|------|-------|------------|-----------|------|

|------|---|----------|------|-------|------------|-----------|------|

- 2. Camber in compliance with EIA 481

- 3. Pocket position relative to sprocket hole measured as true position of pocket, not pocket hole

Device Orientation in Tape

## **Ordering Information**

Table 7 lists the available ordering codes for the PE42723 as well as available shipping methods.

### Table 7 • Order Codes for PE42723

| Order Codes | Description            | Packaging                   | Shipping Method |  |

|-------------|------------------------|-----------------------------|-----------------|--|

| PE42723A-Z  | PE42723 SPDT RF switch | 12-lead 3 × 3 × 0.75 mm QFN | 3000 units/T&R  |  |

| EK42723-01  | PE42723 Evaluation kit | Evaluation kit              | 1/Box           |  |

### **Document Categories**

#### **Advance Information**

The product is in a formative or design stage. The datasheet contains design target specifications for product development. Specifications and features may change in any manner without notice.

### **Preliminary Specification**

The datasheet contains preliminary data. Additional data may be added at a later date. Peregrine reserves the right to change specifications at any time without notice in order to supply the best possible product.

#### **Product Specification**

The datasheet contains final data. In the event Peregrine decides to change the specifications, Peregrine will notify customers of the intended changes by issuing a CNF (Customer Notification Form).

### **Sales Contact**

For additional information, contact Sales at sales@psemi.com.

### **Disclaimers**

The information in this document is believed to be reliable. However, Peregrine assumes no liability for the use of this information. Use shall be entirely at the user's own risk. No patent rights or licenses to any circuits described in this document are implied or granted to any third party. Peregrine's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the Peregrine product could create a situation in which personal injury or death might occur. Peregrine assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

#### **Patent Statement**

Peregrine products are protected under one or more of the following U.S. patents: patents: patents: patents.

## Copyright and Trademark

©2015–2016, Peregrine Semiconductor Corporation. All rights reserved. The Peregrine name, logo, UTSi and UltraCMOS are registered trademarks and HaRP, MultiSwitch and DuNE are trademarks of Peregrine Semiconductor Corp.

#### **Product Brief**

This document contains a shortened version of the datasheet. For the full datasheet, contact sales@psemi.com.

### Not Recommended for New Designs (NRND)

This product is in production but is not recommended for new designs.

### End of Life (EOL)

This product is currently going through the EOL process. It has a specific last-time buy date.

### Obsolete

This product is discontinued. Orders are no longer accepted for this product.