Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Wired Communications

Edition 2001-02-20

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany

© Infineon Technologies AG 2001.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# SICOFI<sup>®</sup>4-µC Four Channel Codec Filter with PCM and Microcontroller Interface

PEB 2466 Version 2.2

PEF 2466 Version 2.2

Wired Communications

**PEB 2466 PEF 2466 Revision History: Current Version 2001-02-20** DS 1 Previous Version: Data Sheet 02.97 DS2 (V 1.2) Delta Sheet 11.98 DS2 (V 1.4) Errata Sheet 05.98 DS1 (V 1.4) Subjects (major changes since last revision)

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

Page

Infineon Technologies AG.

ABM®, AOP®, ARCOFI®, ARCOFI®-BA, ARCOFI®-SP, DigiTape®, EPIC®-1, EPIC®-S, ELIC®, FALC®54, FALC®56, FALC®-E1, FALC®-LH, IDEC®, IOM®, IOM®-1, IOM®-2, IPAT®-2, ISAC®-P, ISAC®-S, ISAC®-S TE, ISAC®-P TE, ITAC®, IWE®, MUSAC®-A, OCTAT®-P, QUAT®-S, SICAT®, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4µC, SLICOFI® are registered trademarks of Infineon Technologies AG. ACE™, ASM™, ASP™, POTSWIRE™, QuadFALC™, SCOUT™ are trademarks of

| Table of                                                                                                                                                                                                                               | f Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|                                                                                                                                                                                                                                        | Preface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                        |

| 1<br>1.1<br>1.2<br>1.3                                                                                                                                                                                                                 | Overview Features Logic Symbol Typical Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3                                                        |

| <b>2</b><br>2.1<br>2.2                                                                                                                                                                                                                 | Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5                                                        |

| <b>3</b><br>3.1<br>3.2                                                                                                                                                                                                                 | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10                                                       |

| 4<br>4.1<br>4.1.1<br>4.1.2<br>4.2.1<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7<br>4.2.8.2<br>4.2.8.1<br>4.2.8.2<br>4.2.9<br>4.2.10<br>4.2.11<br>4.2.12<br>4.2.13<br>4.2.14<br>4.2.15<br>4.2.15<br>4.2.16<br>4.2.17 | Operational Description Operating States Power On Hardware Reset Transmission Characteristics Overload Point 0 dBm0-Levels Compressor Gain Relative to Coding Law Operating Conditions Gain Accuracy Gain Tracking (Receive and Transmit) Frequency Response Group Delay Group Delay, Absolute Values Group Delay Distortion with Frequency Noise Harmonic and Intermodulation Distortion Total Distortion Single Frequency Distortion Overload Compression Crosstalk Out-of-Band Discrimination in Transmit Direction Out-of-Band Discrimination in Receive Direction Out-of-Band Idle Channel Noise at Analog Output | 12 12 14 14 15 16 17 18 18 19 20 20 22 22 22 22 23 24 25 |

| 4.2.18<br><b>5</b>                                                                                                                                                                                                                     | Transhybrid Loss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                          |

| 5.1<br>5.1.1                                                                                                                                                                                                                           | Analog Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 27                                                       |

| Table of                                                                                                    | Contents                                                                                                                                                                                                                                                                                                                                                         | Page                                         |

|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 5.1.2<br>5.2<br>5.2.1<br>5.2.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.4<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4 | Analog Interface Pins  PCM Interface  PCM Interface Pins  PCM Receive and Transmit Example  Signaling Interface  Signaling Interface Pins  Debouncing Functions and Interrupt Generation  Clock Output Signals  Serial Microcontroller Interface  Serial Microcontroller Interface Pins  Write Access  Read Access  Three-Wire Access                            | 30<br>30<br>32<br>34<br>34<br>35<br>36       |

| 6<br>6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.2<br><b>7</b><br>7.1<br>7.1.1<br>7.2                               | Programming Overview Programming Overview Register Model Register Maps CRAM Structure Types of Commands and Data Bytes  Application Hints Support Tools Development Board Guidelines for Board Design Filter Capacitors                                                                                                                                          | 39<br>40<br>41<br>42<br>43<br>43<br>44       |

| 7.3<br>8<br>8.1<br>8.2<br>8.3<br>8.4.1<br>8.5<br>8.4<br>8.6<br>8.6.1<br>8.6.2<br>8.7<br>8.8                 | Proposal for SICOFI®4-µC Board Design  Electrical Characteristics and Timing Diagrams  Absolute Maximum Ratings  Operating Range  Digital Interface  Coupling Capacitors at the Analog Interface  Reset Timing  Analog Interface  PCM-Interface Timing  Single Clocking Mode  Double Clocking Mode  Microcontroller Interface Timing  Signaling Interface Timing | 46<br>47<br>48<br>48<br>48<br>49<br>49<br>50 |

| 8.8.1<br>8.8.2                                                                                              | Timing from the μC Interface to the SO/SB-pins                                                                                                                                                                                                                                                                                                                   | 52                                           |

| Table of Contents |                  |    |  |  |  |

|-------------------|------------------|----|--|--|--|

| 9                 | Test Modes       | 53 |  |  |  |

| 9.1               | Analog Loops     | 53 |  |  |  |

| 9.2               | Digital Loops    |    |  |  |  |

| 9.3               | Cut-Off's        | 55 |  |  |  |

| 10                | Package Outlines | 56 |  |  |  |

| 11                | GlossaryIndex    |    |  |  |  |

| List of Figu | ıres                                                               | Page  |

|--------------|--------------------------------------------------------------------|-------|

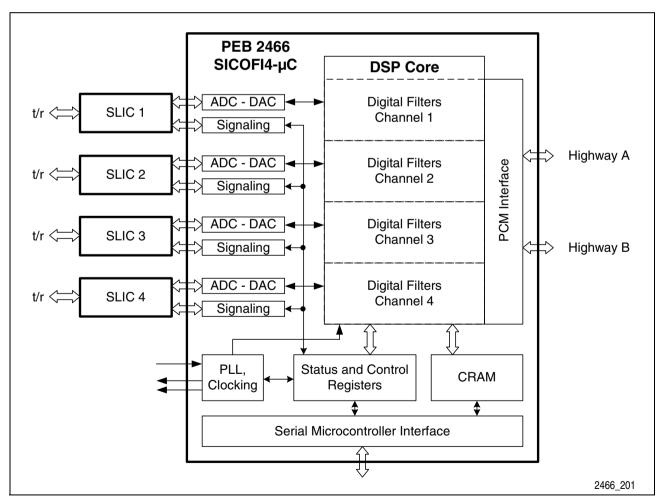

| Figure 1     | SICOFI®4-µC Architecture                                           | 2     |

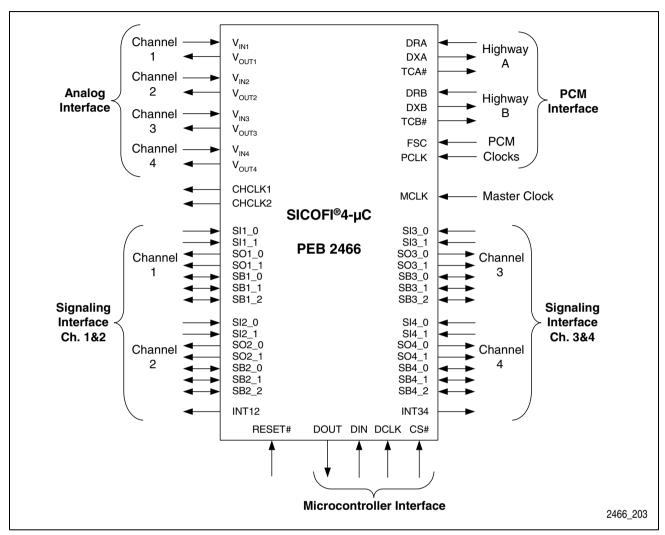

| Figure 2     | SICOFI®4-µC Logic Symbol                                           |       |

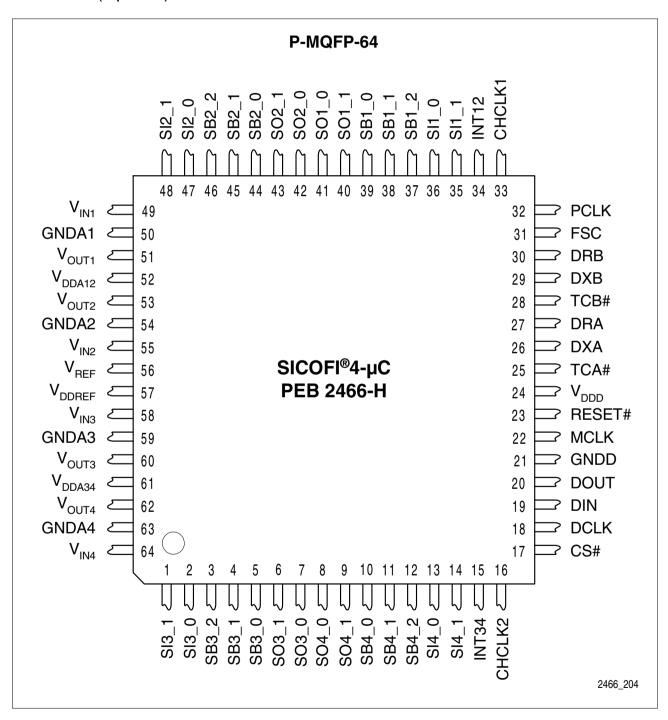

| Figure 3     | Pin Configuration of SICOFI®4-μC                                   | 5     |

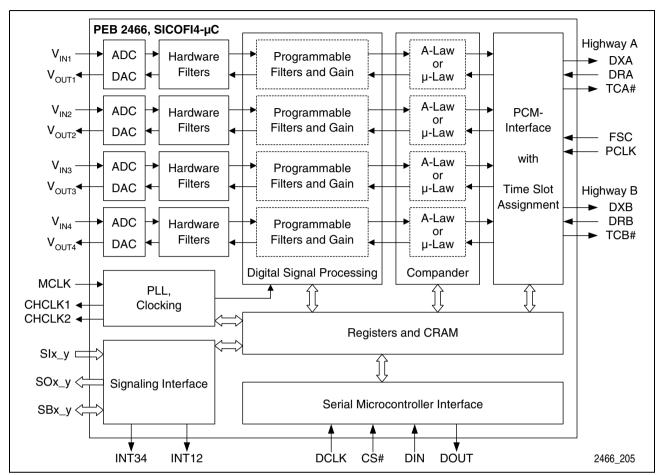

| Figure 4     | SICOFI®4-µC Block Diagram                                          | 11    |

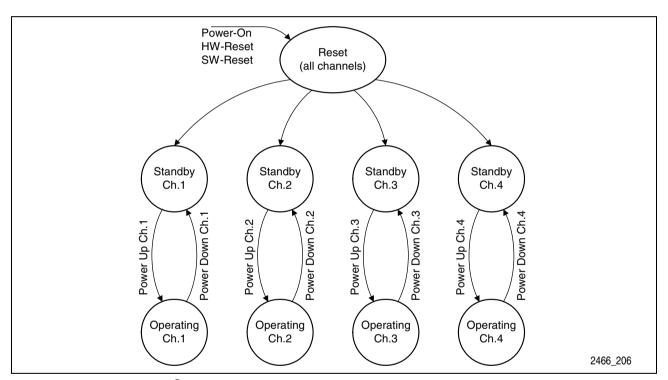

| Figure 5     | SICOFI®4-µC State Diagram                                          | 12    |

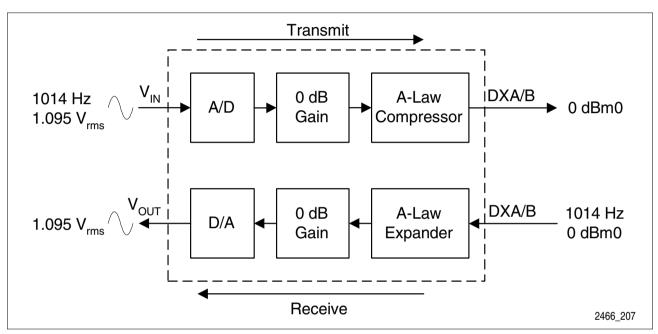

| Figure 6     | Analog and PCM Signal Levels in A-Law Mode                         | 15    |

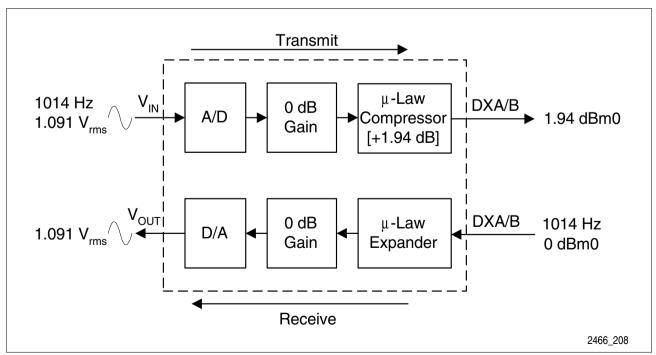

| Figure 7     | Analog and PCM Signal Levels in μ-Law Mode                         | 15    |

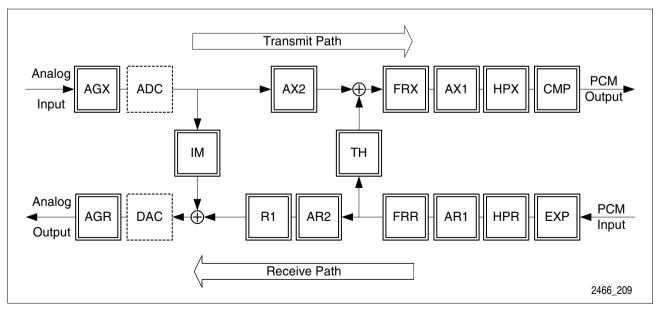

| Figure 8     | Simplified Signal Flow Diagram                                     | 16    |

| Figure 9     | Total Distortion Measured with Sine-Wave, Receive and Transmit     | t 20  |

| Figure 10    | Total Distortion Receive (Noise)                                   | 21    |

| Figure 11    | Total Distortion Transmit (Noise)                                  | 21    |

| Figure 12    | Overload Compression (µ-Law Coding, Transmit Direction)            | 22    |

| Figure 13    | Out-of-Band Discrimination in Transmit Direction                   | 23    |

| Figure 14    | Analog Output: Out-of-Band Signals                                 | 24    |

| Figure 15    | Analog Output: Out-of-Band Idle Channel Noise                      | 25    |

| Figure 16    | Analog Interface to Four Subscriber Line Interface Circuits (SLICs | s) 28 |

| Figure 17    | PCM Interface Example: Location of Time Slots                      |       |

| Figure 18    | PCM Interface Example: Detail A                                    | 32    |

| Figure 19    | Signaling Example: Four Subscriber Lines                           | 33    |

| Figure 20    | Serial Microcontroller Interface                                   | 35    |

| Figure 21    | Example for a Two-Byte Write Access                                | 36    |

| Figure 22    | Example for a One-Byte Read Access                                 |       |

| Figure 23    | Example for a Read Access with Byte-by-Byte Transfer               | 37    |

| Figure 24    | Bi-Directional Data Signal: DIN and DOUT Strapped Together         | 38    |

| Figure 25    | Channel-Specific and Common Coefficients                           |       |

| Figure 26    | Development System with STUT 2466 Evaluation Board                 |       |

| Figure 27    | SICOFI®4-µC Test Circuit Configuration                             | 44    |

| Figure 28    | Proposal for a ground concept                                      |       |

| Figure 29    | PCM Interface Timing in Single Clocking Mode                       |       |

| Figure 30    | PCM Interface Timing in Double Clocking Mode                       |       |

| Figure 31    | Timing of the Microcontroller Interface                            |       |

| Figure 32    | Signaling Output Timing (data downstream)                          |       |

| Figure 33    | Analog Loops                                                       | 53    |

| Figure 34    | Digital Loops                                                      | 54    |

| Figure 35    | Cut-Off's                                                          | 55    |

| List of Tab | oles                                                           | Page |

|-------------|----------------------------------------------------------------|------|

| Table 1     | Pin Definitions and Functions                                  | 6    |

| Table 2     | Register Values and Accessibility                              | 13   |

| Table 3     | Input and Output Pin Behavior                                  | 13   |

| Table 4     | Power Dissipation                                              | 14   |

| Table 5     | Maximum Signal Levels                                          | 14   |

| Table 6     | Analog Voltage Levels Corresponding to 0 dBm0-Level            | 14   |

| Table 7     | Gain Accuracy                                                  | 17   |

| Table 8     | Gain Deviations with Input Level                               | 17   |

| Table 9     | Attenuation with Frequency in Transmit and Receive Direction   | 18   |

| Table 10    | Group Delay, Absolute Values                                   | 18   |

| Table 11    | Group Delay Distortion with Frequency                          | 19   |

| Table 12    | Idle Channel Noise in Transmit Direction                       | 19   |

| Table 13    | Idle Channel Noise in Receive Direction                        | 19   |

| Table 14    | Harmonic and Intermodulation Distortion                        | 20   |

| Table 15    | Signal-to-Total Distortion Ratio Measured with Sine Wave       | 20   |

| Table 16    | Signal-to-Total Distortion Ratio Measured with Noise           | 21   |

| Table 17    | Crosstalk Between Channels                                     | 22   |

| Table 18    | Out-of-Band Signals Applied to the Analog Inputs (VINx)        | 23   |

| Table 19    | Out-of-Band Signals at the Analog Outputs (VOUTx)              | 24   |

| Table 20    | Transhybrid Loss                                               | 26   |

| Table 21    | Analog Interface Pins                                          | 29   |

| Table 22    | PCM Interface Pins                                             | 30   |

| Table 23    | PCM Register Configuration Example                             | 31   |

| Table 24    | Signaling Interface: Pins and Functions for SLIC Interfaces    | 34   |

| Table 25    | Clock Programming                                              | 35   |

| Table 26    | Serial Microcontroller Interface: Pins and Functions           | 36   |

| Table 27    | Register Model                                                 | 39   |

| Table 28    | Read Access to Common Configuration Register (XR) Map          | 40   |

| Table 29    | Write Access to Common Configuration Register (XR) Map         | 40   |

| Table 30    | Channel-Specific Configuration Register (CR) Map (Read & Write | ) 40 |

| Table 31    | Coefficient RAM (CRAM) Structure per Channel                   | 41   |

| Table 32    | Coefficient RAM (CRAM) Structure per Set                       | 42   |

| Table 33    | Types of Commands and Data Bytes                               | 42   |

| Table 34    | Analog Loop Programming in Register CR3, Bits 7 to 4           | 53   |

| Table 35    | Digital Loop Programming in Register CR3, Bits 7 to 4          | 54   |

| Table 36    | Cut-Off Programming in Register CR2, Bits 7 to 5               | 55   |

## **Preface**

This document provides detailed technical information about the SICOFI®4-µC. It is intended for anyone considering or using the device for system design or board layout for a broad range of analog telephony applications. All content applies to both the standard PEB 2466 and the extended temperature version, PEF 2466, unless specified.

### **Organization of this Document**

This Hardware Reference Manual is organized as follows:

- Chapter 1, Overview

Includes a general description of the architecture, feature list, and logic symbol.

- Chapter 2, Pin Descriptions

Illustrates the Pin Configuration and provides detailed functional descriptions.

- Chapter 3, Functional Description

Provides a block diagram and summarizes the major functional blocks.

- Chapter 4, Operational Description

Begins with a state diagram and description of the operating states of all four channels and concludes with detailed transmission characteristics.

- Chapter 5, Interface Descriptions

Describes the Analog, PCM, Signaling, and Serial Microcontroller interfaces.

- Chapter 6, Programming Overview Illustrates the register model and coefficient RAM structure, provides a register map and summary, and identifies the programming command sequences.

- Chapter 7, Application Hints

Describes the development system available for the PEB 2466, and provides guidelines and schematics for board layout.

- Chapter 8, Electrical Characteristics and Timing Diagrams

Provides detailed tables for the electrical characteristics and includes timing diagrams

for the Analog, PCM, Serial Microcontroller, and Signaling interfaces.

- Chapter 9, Test Configuration

Describes the test loops and cut-offs available for functional tests and diagnostics.

- Chapter 10, Package Outlines

Illustrates the P-MQFP-64 package in which the PEB 2466 is manufactured.

- The Appendix Includes a glossary and an index.

#### **Related Documentation**

Other documentation for the PEB 2466 includes a *Product Brief*, a *Product Overview*, a *Programmer's Reference Manual*, and assorted *Application Notes*. Similar documentation is also available for the other members of the SICOFI Codec family including the PSB 2132, PSB 2134, and PEB 2266. Documentation is available by accessing our website: http://www.infineon.com/sicofi

## 1 Overview

The four-channel codec filter PEB 2466 SICOFI<sup>®</sup>4- $\mu$ C is built around a central DSP-core which provides independent filter structures for all channels. Its analog I/O pins are used to connect to external subscriber line interface circuits (SLICs). Their signals are internally routed to the analog-to-digital and digital-to-analog converters (ADC, DAC). The signaling pins carry line status and control information to and from the SLICs. Two programmable clock outputs are available. The SICOFI<sup>®</sup>4- $\mu$ C connects to the digital switching and transmission system through two PCM Highways. The digitized voice band signals are available as A-Law or  $\mu$ -Law codes within selectable 8-bit time slots.

The SICOFI<sup>®</sup>4- $\mu$ C modes, features, and filter characteristics are programmed through a serial interface to a microcontroller. The access mechanism is very simple, and can be implemented with as few as three I/O ports. The PEB 2466 is available for standard temperature range applications (0 °C to +70 °C); the PEF 2466 is available for extended temperature range applications (-40 °C to +85 °C).

Figure 1 SICOFI®4-µC Architecture

# Four Channel Codec Filter with PCM and Microcontroller Interface SICOFI®4-µC

PEB 2466 PEF 2466

Version 2.2 CMOS

### 1.1 Features

- Four-channel single chip codec with digital filters

- High analog driving capability (300  $\Omega$ , 50 pF) for direct driving of transformers

- Digital Signal Processing (DSP) technique

- Programmable digital filters to adapt transmission behavior, especially for:

- AC impedance matching

- Transhybrid balancing

- Frequency response

- Signal levels

- A/µ-Law compression and expansion

- Fulfills international (e.g. ITU-T Q.552, G.712) and country-specific requirements

- High performance ADC and DAC for excellent linearity and dynamic gain

- Programmable Analog Interface to electronic SLICs or transformer solutions

- Seven SLIC-signaling I/O pins per channel with programmable debouncing

- Two PCM Highways accessible by on-chip PCM Interface with Programmable time slot assignment and variable data rates from 128 kbit/s to 8 Mbit/s

- Easy to use 4-pin Serial Microcontroller Interface (SPI compatible) for read/write access

- Single supply voltage (5 V)

- Advanced low-power mixed-signal CMOS technology

- Two programmable tone generators per channel (DTMF possible)

- Level metering function for system tests and for analog input signal testing

- · Advanced on-chip functions for device and system diagnostics and manufacturing test

- Five digital loops

- Four analog loops

- Support tools include:

- Hardware development board STUT 2466

- QSICOS Coefficient Calculation and Register Configuration Software

- Standard P-MQFP-64 package

| Туре                 | Package   |

|----------------------|-----------|

| PEB 2466 Version 2.2 | P-MQFP-64 |

| PEF 2466 Version 2.2 | P-MQFP-64 |

**Overview**

## 1.2 Logic Symbol

Figure 2 SICOFI<sup>®</sup>4-μC Logic Symbol

## 1.3 Typical Applications

Many applications will benefit from the versatility of the SICOFI®4-µC codec and filter. The inherent flexibility enables several products to be developed around one basic architecture, thus affording potentially significant savings in time to market, inventory costs, and support administration.

The following list represents some of the typical applications for which the SICOFI®4-µC codec was designed: Analog linecards for Central Offices and PBXs, Small PBX or Key Systems, Digital Loop Carrier (DLC) Systems, Digital Added Main Lines (DAML) Systems, Fiber-to-the-Curb (FTTC) Systems, Radio-in-the-Loop (RITL) Systems, and any Multi-channel, digital voice processing, storage, or communication applications. Refer to the *Product Overview*, Chapter 5 Application Hints for more information.

# 2 Pin Descriptions

## 2.1 Pin Diagram

(top view)

5

Figure 3 Pin Configuration of SICOFI®4-μC

## 2.2 Pin Definitions and Functions

Table 1 Pin Definitions and Functions

| Pin | Symbol | Туре | Function                                                                                                                                                             |     |

|-----|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1   | SI3_1  | I    | Signaling Input, Channel 3 Pin 1                                                                                                                                     | 3   |

| 2   | SI3_0  | I    | Signaling Input, Channel 3 Pin 0                                                                                                                                     | 3   |

| 3   | SB3_2  | I/O  | Bi-directional Signaling, Channel 3 Pin 2                                                                                                                            | 3   |

| 4   | SB3_1  | I/O  | Bi-directional Signaling, Channel 3 Pin 1                                                                                                                            | 3   |

| 5   | SB3_0  | I/O  | Bi-directional Signaling, Channel 3 Pin 0                                                                                                                            | 3   |

| 6   | SO3_1  | 0    | Signaling Output, Channel 3 Pin 1                                                                                                                                    | 3   |

| 7   | SO3_0  | 0    | Signaling Output, Channel 3 Pin 0                                                                                                                                    | 3   |

| 8   | SO4_0  | 0    | Signaling Output, Channel 4 Pin 0                                                                                                                                    | 4   |

| 9   | SO4_1  | 0    | Signaling Output, Channel 4 Pin 1                                                                                                                                    | 4   |

| 10  | SB4_0  | I/O  | Bi-directional Signaling, Channel 4 Pin 0                                                                                                                            | 4   |

| 11  | SB4_1  | I/O  | Bi-directional Signaling, Channel 4 Pin 1                                                                                                                            | 4   |

| 12  | SB4_2  | I/O  | Bi-directional Signaling, Channel 4 Pin 2                                                                                                                            | 4   |

| 13  | SI4_0  | I    | Signaling Input, Channel 4 Pin 0                                                                                                                                     | 4   |

| 14  | SI4_1  | I    | Signaling Input, Channel 4 Pin 1                                                                                                                                     | 4   |

| 15  | INT34  | 0    | terrupt Output Channels 3 and 4 ctive high.                                                                                                                          |     |

| 16  | CHCLK2 | 0    | Chopper Clock Output 2 Provides 256, 512, or 16384 kHz signal; sync. to MCLK.                                                                                        | all |

| 17  | CS#    | I    | Chip Select Microcontroller Interface chip select, enable to read or write; active low                                                                               | all |

| 18  | DCLK   | I    | Data Clock  Microcontroller Interface data clock, shifts data from or to device; maximum clock rate 8192 kHz.                                                        |     |

| 19  | DIN    | I    | Data Input Microcontroller Interface control data input pin; DCLK determines data rate.                                                                              |     |

| 20  | DOUT   | 0    | Data Output Microcontroller Interface control data output pin; DCLK determines data rate: DOUT is high impedance "Z" if no data is transmitted from the SICOFI®4-µC. | all |

| Pin | Symbol    | Туре | Function                                                                                                                                            |     |  |

|-----|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

| 21  | GNDD      | I    | Digital Ground Ground reference for all digital signals. Internally isolated from GNDA1,2,3,4.                                                      |     |  |

| 22  | MCLK      | I    | Master Clock Input 536, 2048, 4096 or 8192 kHz must be applied for any peration (selected in Register XR5). MCLK, PCLK, FSC must be synchronous.    |     |  |

| 23  | RESET#    | I    | Reset Input Forces the device to default setting mode; active low.                                                                                  | all |  |

| 24  | $V_{DDD}$ | I    | Digital Supply Voltage<br>+5 V supply for digital circuits (use 100 nF blocking cap.).                                                              | all |  |

| 25  | TCA#      | 0    | Transmit Control Output A  PCM Interface: active if data is transmitted via DXA; active low, open drain.                                            | all |  |

| 26  | DXA       | 0    | Data Transmit to PCM-Highway A PCM Interface: PCM data for each channel is transmitted in 8-bit bursts every 125 µs.                                |     |  |

| 27  | DRA       | I    | Data Receive from PCM-Highway A PCM Interface: PCM data for each channel is received in 8-bit bursts every 125 μs.                                  |     |  |

| 28  | TCB#      | 0    | Transmit Control Output B PCM Interface: active if data is transmitted via DXB; active low, open drain.                                             |     |  |

| 29  | DXB       | 0    | Data Transmit to PCM-highway B PCM Interface: data for each channel is transmitted in 8-bit bursts every 125 μs.                                    |     |  |

| 30  | DRB       | I    | Data Receive from PCM-highway B PCM Interface: data for each channel is received in 8-bit bursts every 125 µs.                                      |     |  |

| 31  | FSC       | I    | Frame Synchronization Clock 8 kHz; reference for individual time slots, indicates start of PCM frame; MCLK, PCLK, FSC must be synchronous.          |     |  |

| 32  | PCLK      | I    | PCM Data Clock 128 to 8192 kHz; determines the rate at which PCM data is shifted into or out of the PCM-ports. MCLK, PCLK, FSC must be synchronous. |     |  |

| Pin | Symbol      | Туре | Function                                                                                                                                                                          |      |

|-----|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 33  | CHCLK1      | 0    | Chopper Clock Output 1 Provides programmable (2 28 ms) output signal (synchronous to MCLK).                                                                                       |      |

| 34  | INT12       | 0    | Interrupt Output, Channels 1 and 2 Active high.                                                                                                                                   | 1, 2 |

| 35  | SI1_1       | I    | Signaling Input Channel 1, Pin 1                                                                                                                                                  | 1    |

| 36  | SI1_0       | I    | Signaling Input Channel 1, Pin 0                                                                                                                                                  | 1    |

| 37  | SB1_2       | I/O  | Bi-directional Signaling, Channel 1 Pin 2                                                                                                                                         | 1    |

| 38  | SB1_1       | I/O  | Bi-directional Signaling, Channel 1 Pin 1                                                                                                                                         | 1    |

| 39  | SB1_0       | I/O  | Bi-directional Signaling, Channel 1 Pin 0                                                                                                                                         | 1    |

| 40  | SO1_1       | 0    | Signaling Output, Channel 1, Pin 1                                                                                                                                                | 1    |

| 41  | SO1_0       | 0    | Signaling Output, Channel 1, Pin 0                                                                                                                                                | 1    |

| 42  | SO2_0       | 0    | Signaling Output, Channel 2, Pin 0                                                                                                                                                | 2    |

| 43  | SO2_1       | 0    | Signaling Output, Channel 2, Pin 1                                                                                                                                                | 2    |

| 44  | SB2_0       | I/O  | Bi-directional Signaling, Channel 2 Pin 0                                                                                                                                         | 2    |

| 45  | SB2_1       | I/O  | Bi-directional Signaling, Channel 2 Pin 1                                                                                                                                         |      |

| 46  | SB2_2       | I/O  | Bi-directional Signaling, Channel 2 Pin 2                                                                                                                                         |      |

| 47  | SI2_0       | I    | Signaling Input, Channel 2, Pin 0                                                                                                                                                 |      |

| 48  | SI2_1       | I    | Signaling Input, Channel 2, Pin 1                                                                                                                                                 |      |

| 49  | $V_{IN1}$   | I    | Analog Voice (Voltage) Input, Channel 1 Requires a coupling capacitor >39 nF to the SLIC.                                                                                         |      |

| 50  | GNDA1       | I    | Analog Ground, Channel 1 Not internally connected to GNDD or GNDA2,3,4.                                                                                                           |      |

| 51  | $V_{OUT1}$  | 0    | Analog Voice (Voltage) Output, Channel 1 Requires a coupling capacitor to the SLIC. The capacitor value depends on the SLIC's input impedance. (See Chapter 5.1 Analog Interface) |      |

| 52  | $V_{DDA12}$ | I    | Analog Supply Voltage, Channels 1 and 2<br>+5 V (100 nF blocking capacitor required).                                                                                             |      |

| 53  | $V_{OUT2}$  | 0    | Analog Voice (Voltage) Output, Channel 2 Requires a coupling capacitor to the SLIC. The capacitor value depends on the SLIC's input impedance. (See Chapter 5.1 Analog Interface) |      |

| Pin | Symbol         | Туре | Function                                                                                                                                                                          |     |

|-----|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 54  | GNDA2          | I    | Analog Ground, Channel 2 Not internally connected to GNDD or GNDA 1,3,4.                                                                                                          |     |

| 55  | $V_{IN2}$      | I    | Analog Voice (Voltage) Input, Channel 2 Requires a coupling capacitor >39 nF to the SLIC.                                                                                         | 2   |

| 56  | $V_{REF}$      | I/O  | Reference Voltage Must connect to a 220 nF cap. to ground.                                                                                                                        | all |

| 57  | $V_{ m DDREF}$ | I    | Analog Supply Reference Voltage<br>+5 V (100 nF blocking capacitor required).                                                                                                     | all |

| 58  | $V_{IN3}$      | I    | Analog Voice (Voltage) Input, Channel 3 Requires a coupling capacitor >39 nF to the SLIC.                                                                                         | 3   |

| 59  | GNDA3          | I    | Analog Ground, Channel 3 Not internally connected to GNDD or GNDA1,2,4.                                                                                                           |     |

| 60  | $V_{OUT3}$     | 0    | Analog Voice (Voltage) Output, Channel 3 Requires a coupling capacitor to the SLIC. The capacitor value depends on the SLIC's input impedance. (See Chapter 5.1 Analog Interface) |     |

| 61  | $V_{DDA34}$    | I    | Analog Supply Voltage, Channels 3 and 4<br>+5 V (100 nF blocking capacitor required).                                                                                             |     |

| 62  | $V_{OUT4}$     | 0    | Analog Voice (Voltage) Output, Channel 4 Requires a coupling capacitor to the SLIC. The capacitor value depends on the SLIC's input impedance. (See Chapter 5.1 Analog Interface) |     |

| 63  | GNDA4          | I    | Analog Ground, Channel 4 Not internally connected to GNDD or GNDA1,2,3.                                                                                                           |     |

| 64  | $V_{IN4}$      | I    | Analog Voice (Voltage) Input, Channel 4 Requires a coupling capacitor >39 nF to the SLIC.                                                                                         |     |

## **Functional Description**

# 3 Functional Description

The telephone subscriber loop is a bi-directional two-wire line. The Subscriber Line Interface Circuit (SLIC) on the network side converts the two-wire interface to a four-wire interface with separate receive and transmit signals, which connect to the SICOFI®4- $\mu$ C. The SLIC can be either a transformer or an electronic circuit with operational amplifiers. It must have a defined input impedance towards the subscriber line for maximum signal power transfer and return loss. The requirements for the input impedance vary from country to country and demand impedance matching to the different environments. Country-specific adaptations are also required for the transhybrid loss, which is a loss between the transmit and the receive ports of the two-wire to four-wire hybrid.

#### 3.1 DSP-based Architecture

The impedance matching and transhybrid balancing functions are performed by loop filters between the transmit path (analog to PCM) and the receive path (PCM to analog). The filter characteristics must be adjusted according to the local requirements of each market. In the analog domain, filters must be optimized in hardware; this is generally both tedious and time-consuming. This is not the case with the DSP-based SICOFI®4- µC four-channel codec. Its integrated signal processor implements the impedance matching and transhybrid balancing functions as digital, programmable filters. It also performs frequency response corrections and level adjustments to enable the design of a truly universal and internationally applicable telephone linecard. Transmission characteristics and frequency behavior are enhanced by the accuracy of the digital filters, which do not fluctuate over temperature or with age.

As an additional benefit of its DSP-based architecture, the PEB 2466 also provides two tone generators per channel. An on-chip level-metering unit allows line-characterization without extra hardware; it can also be used to detect specific tones, e.g., modem tones.

# 3.2 Programming and Control

A very simple Microcontroller Interface is used to program the SICOFI  $^{\$}$ 4- $\mu$ C functions. The same port provides access to 28 general purpose I/O pins of the Signaling Interface. This allows efficient and convenient monitoring and control of other linecard functions, such as on-/off-hook detection, ground-key detection, switching of ring signals and test relays. The Serial Microcontroller Interface provides a programming and control interface and is generic and non-proprietary for use with any microcontroller. It can be implemented with as few as three signal lines, since the data receive and data transmit pins may be strapped together.

## **Functional Description**

Figure 4 SICOFI®4-µC Block Diagram

Figure 4 shows the functional blocks and the interface pins of the SICOFI®4-μC:

- Four independent bi-directional voice channels;

- Oversampling sigma-delta A/D and D/A converters with excellent resolution, dynamic range, linearity, accuracy and signal-to-noise performance;

- Hardware filters for decimation and interpolation of the ADC and DAC bit stream, and pre-processing of the voice data to reduce the load of the DSP;

- DSP core with programmable, channel-independent filter structures for impedance matching, transhybrid balancing, frequency correction and level adjustments;

- Configurable A-Law or μ-Law compressor and expander units;

- Two PCM ports with data rates from 128 kbps to 8 Mbps per highway;

- Programmable time slot assignment for each channel;

- twenty-eight signaling input and output pins, accessible through registers;

- On-chip PLL for an internal 16.384 MHz clock;

- Two programmable versatile clock outputs;

- Eight common configuration registers (XR-Registers) affecting all four channels;

- Four sets of six channel-specific registers (CR-Registers); and

- Coefficient RAM (CRAM) for filter coefficients storage for each channel.

# 4 Operational Description

Each channel of the SICOFI<sup>®</sup>4-μC can be in one of two stable states: "Standby" and "Operating". These states can be switched by programming Bit 0 (PU) in the channel-specific configuration register CR1. "Standby" is a power-saving state. Keeping all unused channels in this state reduces the overall system power dissipation. The third state, "Reset", is transient and is reached after applying power to the device (Power On), after asserting a logic low signal to the RESET#-pin (HW-Reset), or after issuing an XOP command with Bit 7 (RST) set to '1' (SW-Reset). All four channels would be affected in any case.

## 4.1 Operating States

Figure 5 SICOFI®4-µC State Diagram

### 4.1.1 Power On

All input pins must be at GND level before applying VDD to the SICOFI<sup>®</sup>4- $\mu$ C. Otherwise, the device may not enter the Reset State. In this case, the SICOFI<sup>®</sup>4- $\mu$ C can be reset by HW- or SW-Reset, or can be initialized by setting all registers to zero.

#### 4.1.2 Hardware Reset

Voltage levels lower than 1.2 V applied to pin 23 (RESET#) for more than 3  $\mu$ s will reset the SICOFI®4- $\mu$ C. Spikes that are shorter than 1  $\mu$ s will be ignored. When RESET# is released the SICOFI®4- $\mu$ C will enter Standby State.

Table 2 Register Values and Accessibility

| Register | SICOFI®4-µC State |                   |                   |  |

|----------|-------------------|-------------------|-------------------|--|

| negistei | Reset             | Standby           | Operating         |  |

| CR0 CR4  | 00 <sub>H</sub>   | user configurable | user configurable |  |

| XR0 XR7  | 00 <sub>H</sub>   | user configurable | user configurable |  |

| CRAM     | unchanged         | user configurable | user configurable |  |

Table 3

Input and Output Pin Behavior

| Din                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     | SICOFI®4-µC Stat                      | te                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------|--------------------------------------|

| Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reset               | Standby                               | Operating                            |

| DIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ignored             | serial input                          | serial input                         |

| DOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | high impedance      | serial output                         | serial output                        |

| DRA, DRB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ignored             | ignored                               | active receive time slot             |

| DXA, DXB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | high impedance      | high impedance                        | active transmit time slot            |

| TCA#, TCB#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | high                | high                                  | low during active transmit time slot |

| $V_{\text{OUT1}}$ , $V_{\text{OUT2}}$ $V_{\text{OUT3}}$ , $V_{\text{OUT4}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | high impedance      | high impedance                        | analog output                        |

| $egin{array}{c} egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}$ | ignored             | ignored                               | analog input                         |

| SBx_y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | configured as input | programmable as input or output       | programmable as input<br>or output   |

| SOx_y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | GNDD                | digital output                        | digital output                       |

| Slx_y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ignored             | digital input                         | digital input                        |

| CHCLK1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | high                | programmable<br>frequency             | programmable<br>frequency            |

| CHCLK2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | high                | programmable freq.<br>(not 16384 kHz) | programmable<br>frequency            |

Table 4 Power Dissipation

| No. of Channels Operating | Typical Power Dissipation |

|---------------------------|---------------------------|

| None                      | 2.5 mW                    |

| 1                         | 70 mW                     |

| 2                         | 90 mW                     |

| 3                         | 110 mW                    |