# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# ICs for Communications

Multichannel Network Interface Controller for HDLC MUNICH32

PEB 20320 Version 3.4

User's Manual 01.2000

| PEB 20320                                                       |  |                                                  |  |  |  |

|-----------------------------------------------------------------|--|--------------------------------------------------|--|--|--|

| Revision History:                                               |  | Current Version: 01.2000                         |  |  |  |

| Previous Version:                                               |  | User's Manual 1998-06-01 DS2 (V3.4)              |  |  |  |

| Page<br>(in previous<br>Version)Page<br>(in current<br>Version) |  | Subjects (major changes since last revision)     |  |  |  |

|                                                                 |  | Package P-TQFP-176-1 removed from User's Manual. |  |  |  |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

ABM®, AOP®, ARCOFI®, ARCOFI®-BA, ARCOFI®-SP, DigiTape®, EPIC®-1, EPIC®-S, ELIC®, FALC®54, FALC®56, FALC®-E1, FALC®-LH, IDEC®, IOM®, IOM®-1, IOM®-2, IPAT®-2, ISAC®-P, ISAC®-S, ISAC®-S TE, ISAC®-P TE, ITAC®, IWE®, MUSAC®-A, OCTAT®-P, QUAT®-S, SICAT®, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4µC, SLICOFI® are registered trademarks of Infineon Technologies AG.

ACE<sup>™</sup>, ASM<sup>™</sup>, ASP<sup>™</sup>, POTSWIRE<sup>™</sup>, QuadFALC<sup>™</sup>, SCOUT<sup>™</sup> are trademarks of Infineon Technologies AG.

Edition 01.2000 Published by Infineon Technologies AG, SC, Balanstraße 73, 81541 München

© Infineon Technologies AG 2000. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Infineon Technologies AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Infineon Technologies AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

# Preface

The Multichannel Network Interface Controller for HDLC (MUNICH32) is a Multichannel Protocol Controller for a wide area of telecommunication and data communication applications.

## **Organization of this Document**

This User's Manual is divided into 9 chapters. It is organized as follows:

- Chapter 1, Introduction Gives a general description of the product and its family, lists the key features, and presents some typical applications.

- Chapter 2, Functional Description This chapter provides a detailed description of the interfaces and the protocol modes.

- Chapter 3, Operational Description Provides a description of MUNICH32 reset procedure and initialization.

- Chapter 4, Detailed Register Description Gives a detailed description of the shared memory organization.

- · Chapter 5, Application Notes

- Chapter 6, Application Hints

- Chapter 7, Electrical Characteristics Gives a detailed description of all electrical DC and AC characteristics and provides timing diagrams and values for all interfaces.

- · Chapter 8, Package Outlines

- Chapter 9, Appendix This chapter provides source code examples.

# Your Comments

We welcome your comments on this document as we are continuously aiming at improving our documentation. Please send your remarks and suggestions by e-mail to

sc.docu\_comments@infineon.com

Please provide in the subject of your e-mail: device name (MUNICH32), device number (PEB 20320), device version (Version 3.4),

and in the body of your e-mail:

document type (User's Manual), issue date (01.2000) and document revision number (DS3).

#### **Table of Contents**

# Page

| <b>1</b><br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6                                                | Introduction.7Features.8Pin Configuration.11Pin Definitions and Functions.12Logic Symbol.22Functional Block Diagram.23System Integration.25                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>2</b><br>2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.3<br>2.4<br>2.5                            | Functional Description.32Serial Interface.32Microprocessor Interface.38Intel Mode.39Motorola Mode.43DMA Priorities.46Basic Functional Principles.47Detailed Protocol Description.76Boundary Scan Unit.126                                                                                                                                                                                  |

| <b>3</b><br>3.1<br>3.2                                                                            | Operational Description   .131     Reset State   .131     Initialization Procedure   .132                                                                                                                                                                                                                                                                                                  |

| <b>4</b><br>4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.3<br>4.4        | Detailed Register Description.134Organization of the Shared Memory.134Control and Configuration Section.136Action Specification (Read Once After Each Action Request Pulse).136Interrupt Queue Specification.140Interrupt Information.141Time Slot Assignment.148Channel Specification.149Current Receive and Transmit Descriptor Address.161Transmit Descriptor.162Receive Descriptor.168 |

| <b>5</b><br>5.1<br>5.1.1<br>5.1.1.1<br>5.1.1.2<br>5.1.1.3<br>5.1.1.4<br>5.1.2<br>5.1.3<br>5.1.3.1 | Application Notes.173Test Loops.173Test Loop Definitions for the MUNICH32.173Internal Complete Test Loop.173Internal Channelwise Test Loop.174External Complete Test Loop.174External Channelwise Test Loop.175Test Loop Activation.176Test Loop Deactivation and Switching.176Software Operations.177                                                                                     |

| Table  | of       | Contents   |

|--------|----------|------------|

| I UNIC | <b>U</b> | 0011101110 |

| Page |

|------|

|------|

| 5.1.3.2<br>5.1.4<br>5.1.4.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.3.1<br>5.2.3.2<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.3.1<br>5.3.2 | Hardware Reset Operations177Test Loop Examples178Internal Channelwise Test Loop178External Channelwise Test Loop180MUNICH32 in a LAN/WAN Router182Introduction182Hardware183Software188Device Driver Module MUNICH32191Application Module MROUTE194Performance Considerations197Final Remarks201Adaption of the 68040 μP Signals203Schematics205Memory Bus Occupancy for a Single MUNICH32214Bus Occupancy for Idle Tx Channels218 |

|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>6</b><br>6.1<br>6.2<br>6.3<br>6.3.1<br>6.3.2                                                                                           | Application Hints .220   Frequency Adaption in an Intel 368 Common Bus System .220   MUNICH32 Memory Space Requirement .223   Serial Interface to different PCM Systems .224   MUNICH32 for SIEMENS Primary Access Interface .224   MUNICH32 in Systems with MITEL ST BUS .227                                                                                                                                                     |

| <b>7</b><br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6                                                                                        | Electrical Characteristics.229Absolute Maximum Ratings.229DC Characteristics.230Capacitances.231AC Characteristics.231Microprocessor Interface Intel Bus Mode.232Microprocessor Interface Motorola Bus Mode.235                                                                                                                                                                                                                    |

| 8                                                                                                                                         | Package Outlines                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <b>9</b><br>9.1<br>9.2                                                                                                                    | Appendix.243Source Code Extract MUNICH32.243Source Code.245                                                                                                                                                                                                                                                                                                                                                                        |

#### 1 Introduction

The Multichannel Network Interface Controller for HDLC (MUNICH32) is a Multichannel Protocol Controller, which handles up to 32 data channels of a full duplex PCM highway. It performs layer 2 HDLC formatting/deformatting or V.110 and X.30 protocols up to a network data rate of 38.4 Kbit/s as well as transparent transmission for the DMI mode 0, 1 and 2. The processed data is passed on to an external memory shared with one or more host processors.

MUNICH32 is compatible with the LAPD ISDN (Integrated Services Digital Network) protocol specified by CCITT as well as with HDLC, SDLC, LAPB DMI protocols. It provides any rate adaption for time slot transmission data rate from 64 Kbit/s down to 8 Kbit/s and the concatenation of any time slots to data channels, supporting the ISDN H0, H11, H12 superchannels.

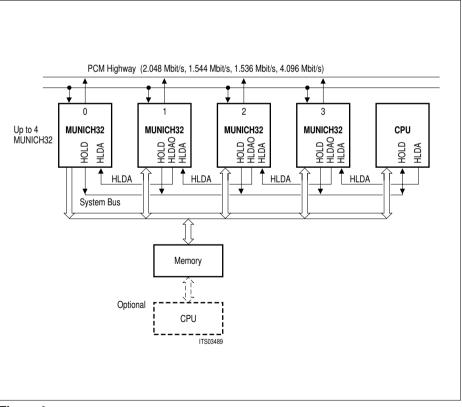

Due to these functions the MUNICH32 can be used in a wide area of telecommunication and data communication applications, e.g. in central office switches, for the connection of a digital PABX to a host computer, as a central D-channel controller to 32 ISDN basic access D-channels or as a multiplexer for terminals and other peripherals. Up to 4 MUNICH32s can be connected to one PCM highway, so a D-channel controller with 128 channels can be achieved.

## Multichannel Network Interface Controller for HDLC PEB 20320 MUNICH32

#### Version 3.4

#### 1.1 Features

- Serial Interface

- Up to 32 independent communication channels.

- Serial multiplexed (full duplex) input/output for 2048-, 4096-, 1544- or 1536-Kbit/s PCM highways.

- Dynamic Programmable Channel Allocation

- Compatible with T1/DS1 24-channel and CEPT 32-channel PCM byte format.

- Concatenation of any, not necessarily consecutive, time slots to superchannels independently for receive and transmit direction.

- Support of H0, H11, H12 ISDN-channels.

- Subchanneling on each time slot possible.

- · Bit Processor Functions (adjustable for each channel)

- HDLC Protocol

- Automatic flag detection and transmission

- Shared opening and closing flag

- Detection of interframe-time-fill change, generation of interframe-time-fill '1's or flags

- Zero bit insertion

- Flag stuffing and flag adjustment for rate adaption

- CRC generation and checking (16 or 32 bits)

- Transparent CRC option per channel and/or per message

- Error detection (abort, long frame, CRC error, 2 categories of short frames, non-octet frame content)

- Special short frame mode to allow reception of 'frames' with a least on byte length

- ABORT/IDLE generation

| Туре      | Package      |

|-----------|--------------|

| PEB 20320 | P-MQFP-160-1 |

# CMOS

8

- V.110/X.30 Protocol

- Automatic synchronization in receive direction, automatic generation of the synchronization pattern in transmit direction

- E / S / X bits freely programmable in transmit direction, van be changed during transmission; changes monitored and reported in receive direction

- Generation/detection of loss of synchronism

- Bit framing with network data rates from 600 bit/s up to 38.4 Kbit/s

- Transparent Mode A

- Slot synchronous transparent transmission/reception without frame structure

- Bit-overwrite with fill/mask bits

- Flag generation, flag stuffing, flag extraction, flag generation in the abort case with programmable flag

- Transparent Mode B

- Transparent transmission/reception in frames delimited by 00<sub>H</sub> flags

- Shared opening and closing flag

- Flag stuffing, flag detection, flag generation in the abort case

- Error detection (non octet frame content, short frame, long frame)

- Transparent Mode R

- Transparent transmission/reception with GSM 08.60 frame structure

- Automatic 0000<sub>H</sub> flag generation/detection

- Support of 40,  $39^{1}/_{2}$ ,  $40^{1}/_{2}$  octet frames

- Error detection (non octet frame content, short frame, long frame)

- Protocol Independent

- Channel inversion (data, flags, IDLE code)

- Format conventions as in CCITT Q.921 § 2.8

- Data over- and underflow detected

- Processor Interface

- ON-CHIP 64-channel DMA controller with buffer chaining capability.

- Compatible with Motorola 68020 processor family and Intel 32-bit processor (80386).

- 32 bit data bus and 32 bit address bus (4 Gbyte RAM addressable, Motorola and Intel non-parity) or 28 bit address bus (256 Mbyte RAM addressable, Intel parity)

- Intel parity mode with data byte parity (4 parity bits)

- Parity check for read accesses

- Parity generation for write accesses

- Interrupt-circular buffer with variable size

- Maskable interrupts for each channel

- $-\mu$ P interface buffer of depth 16 long words for adaptive bus occupation

- General

- Connection of up to four MUNICH32 supporting a 128-channel basic access D-channel controller.

- ON-CHIP receive and transmit data buffer; the buffer size is 256 bytes each.

- HDLC protocol or transparent mode, support of ECMA 102, CCITT I4.63 RA2, V.110, X.30, DMI mode 0, 1, 2 (bit rate adaption), GSM 08.60 TRAU frames.

- LOOP mode, complete loop as well as single channel loop

- JTAG boundary scan test

- Advanced low-power CMOS technology

- TTL-compatible inputs/outputs

- 160 pin P-MQFP package

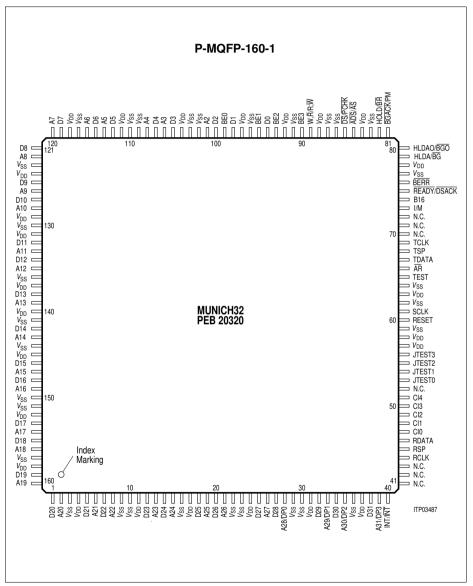

#### 1.2 Pin Configuration

(top view)

Figure 1

#### 1.3 Pin Definitions and Functions

Pin Definitions and Functions

| Pin No.<br>P-MQFP-160-1                                                                                                                                       | Symbol          | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 83, 87, 88, 92,<br>97, 103, 104,<br>110, 111, 117,<br>123, 130, 136,<br>141, 144, 150,<br>151, 157, 3, 9,<br>10, 16, 22, 23,<br>29, 30, 36, 59,<br>62, 64, 77 | V <sub>SS</sub> | 1                       | <b>Ground</b> (0 V)<br>All pins must have the same level.                                                                                                                                                                                                                                                                                          |

| 73                                                                                                                                                            | I/M             | Ι                       | Intel Bus Mode or Motorola Bus Mode<br>By connecting this pin to either $V_{SS}$ or $V_{DD}$<br>the bus interface can be adapted to either<br>Intel or Motorola environment. The data is<br>interpreted either in Intel or Motorola<br>manner; i.e. little or big endian convention.<br>I/M = low: Intel bus mode<br>I/M = high: Motorola bus mode |

| 39                                                                                                                                                            | A31<br>DP3      | 0                       | Address Bit 31<br>(Intel non-parity/Motorola) tristate when<br>unused.<br>Data Parity 3 (Intel parity mode),<br>bidirectional tristate line containing/<br>expecting parity bit of D(31:24).                                                                                                                                                       |

| 35                                                                                                                                                            | A30<br>DP2      | 0<br>I/O                | Address Bit 30<br>(Intel non-parity/Motorola) tristate when<br>unused.<br>Data Parity 2 (Intel parity mode),<br>bidirectional tristate line containing/<br>expecting parity bit of D(23:16).                                                                                                                                                       |

Note: Input pins that are unused in a specific configuration must be strapped to  $V_{ss}$ . I/O or output pins that are unused in a specific configuration must be left open!

| Pin No.<br>P-MQFP-160-1                                                                                                                    | Symbol  | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33                                                                                                                                         | A29     | 0                       | Address Bit 29<br>(Intel non-parity/Motorola) tristate when<br>unused.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                            | DP1     | I/O                     | <b>Data Parity 1</b> (Intel parity mode),<br>bidirectional tristate line containing/<br>expecting parity bit of D(15:8)                                                                                                                                                                                                                                                                                                                                                                     |

| 28                                                                                                                                         | A28     | 0                       | Address Bit 28<br>(Intel non-parity/Motorola) tristate when<br>unused                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                            | DP0     | I/O                     | <b>Data Parity 0</b> (Intel parity mode),<br>bidirectional tristate line containing/<br>expecting parity bit of D(7:0)                                                                                                                                                                                                                                                                                                                                                                      |

| 26, 21, 19, 15,<br>13, 8, 6, 2, 160,<br>156, 154, 149,<br>147, 143, 139,<br>135, 133, 128,<br>126, 122, 120,<br>116, 114, 109,<br>107, 102 | A(27:2) | 0                       | Address Bus<br>tristate when unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 91, 94, 96, 100                                                                                                                            | BE(3:0) | 0                       | Byte Enable (Intel bus mode)<br>The MUNICH32 provides word and long<br>word transfer. The byte enables determine<br>the address offset to the address<br>A31 A2, the actual word has been<br>stored to.<br>Address Offset Size (Motorola mode)<br>Indicates the number of bytes remaining to<br>be transferred for this access. These<br>signals define the active sections of the<br>data bus.<br>In both cases these signals are tristate<br>when unused.<br>See Chapter 2.2 for details. |

| Pin No.<br>P-MQFP-160-1                                                                                                                                          | Symbol          | Input (I)<br>Output (O) | Function                                                                                                                                                                                              |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 38, 34, 32, 27,<br>25, 20, 18, 14,<br>12, 7, 5, 1, 159,<br>153, 148, 146,<br>142, 138, 134,<br>132, 127, 125,<br>121, 119, 115,<br>113, 108, 106,<br>101, 99, 95 | D(31:0)         | I/O                     | <b>Data Bus</b><br>The data bus lines are bidirectional tristate<br>lines which interface with the system's<br>data bus.                                                                              |  |

| 86                                                                                                                                                               | DS              | Ο                       | <b>Data Strobe</b> (Motorola mode)<br>This signal indicates that valid data is to be<br>placed on the data bus (read cycle) or has<br>been placed on the data bus by the<br>MUNICH32 (write cycle).   |  |

|                                                                                                                                                                  | РСНК            | Ο                       | <b>Parity Check</b> (Intel parity mode)<br>This signal indicates, whether the parity<br>bits of a read cycle are valid (PCHK high)<br>or invalid (PCHK low). See <b>Chapter 2.2.1</b><br>for details. |  |

| 84, 93, 89, 98,<br>105, 112, 118,<br>124, 129, 131,<br>137, 140, 145,<br>152, 158, 4, 11,<br>17, 24, 31, 37,<br>57, 58, 63, 78                                   | V <sub>DD</sub> | I                       | Supply voltage 5 V $\pm$ 5% All pins must have the same level.                                                                                                                                        |  |

| 85                                                                                                                                                               | ADS             | 0                       | Address Status (Intel bus mode)<br>This signal indicates that a valid bus cycle<br>definition and address are being driven at<br>the pins.                                                            |  |

|                                                                                                                                                                  | ĀS              | Ο                       | Address Strobe (Motorola bus mode)<br>A valid address is transmitted on the<br>address bus at the falling edge of AS.<br>In both cases this signal is active low and                                  |  |

|                                                                                                                                                                  |                 |                         | tristate when unused.                                                                                                                                                                                 |  |

| Pin No.<br>P-MQFP-160-1 | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------|--------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 90                      | W/R    | 0                       | Write/Read (Intel bus mode)<br>This signal distinguishes write from read<br>operations.                                                                                                                                                                                                                                                                                                                |

|                         | R/W    | 0                       | Read/Write (Motorola bus mode)<br>This signal distinguishes between read<br>and write operations.<br>In both cases this signal is tristate when                                                                                                                                                                                                                                                        |

|                         |        |                         | unused.                                                                                                                                                                                                                                                                                                                                                                                                |

| 75                      | READY  | 1                       | <b>Ready</b> (Intel bus mode)<br>This signal indicates that the current bus<br>cycle is complete. When READY is<br>asserted during a read cycle the<br>MUNICH32 latches the input data and<br>terminates the cycle. When READY is<br>asserted during a write cycle the<br>MUNICH32 terminates the cycle.                                                                                               |

|                         | DSACK  | Ι                       | <b>Data Transfer Acknowledge</b> (Motorola<br>bus mode)<br>This active low input indicates that a data<br>transfer may be performed. During a read<br>cycle data becomes valid at the falling<br>edge of DSACK. The data is latched<br>internally and the bus cycle is terminated.<br>During a write cycle the falling edge of<br>DSACK marks the latching of data and the<br>bus cycle is terminated. |

| Pin No.<br>P-MQFP-160-1 | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------|--------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 76                      | BERR   | 1                       | <b>Bus Error</b> (Intel and Motorola bus mode)<br>This active low signal informs the<br>MUNICH32 that a bus cycle error has<br>occurred. The MUNICH32 terminates the<br>bus cycle.<br>In case of an erroneous read cycle in the<br>control and configuration section an<br>'Action Request Fail' interrupt is generated<br>and the action is suspended. In case of an<br>erroneous read cycle in the transmit data<br>section the corresponding frame is<br>aborted and a FO interrupt is generated. In<br>all other cases of read or write cycles<br>terminated with an error condition no<br>further actions are performed by the<br>MUNICH32. Please see <b>Chapter 2.2</b> ,<br>'Microprocessor Interface', first paragraph<br>and <b>Figure 18</b> .<br>As bus cycles are executed without time<br>limit this signal prevents a hang-up<br>situation of the MUNICH32. |

| 74                      | B16    | 1                       | <b>Word Operation</b><br>Setting this bit to $V_{DD}$ causes the<br>MUNICH32 to perform 32-bit long word<br>accesses to the shared memory, setting it<br>to $V_{SS}$ causes the MUNICH32 to perform<br>16-bit word accesses on the data lines<br>D(15:0) only. In 16-bit word access mode<br>the data lines D(31:16) should be left<br>open.<br>This bit is <b>not</b> dynamic and should be set<br>to $V_{DD}$ in Intel parity mode.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Pin Definitions and F | Functions (cont'd) |

|-----------------------|--------------------|

|-----------------------|--------------------|

| Pin No.<br>P-MQFP-160-1 | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                   |

|-------------------------|--------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 82                      | HOLD   | 0                       | <b>Bus Hold Request</b> (Intel bus mode)<br>This signal is driven high when the<br>MUNICH32 requests the control of the<br>bus.                                                                                                                                            |

|                         | BR     | I/O                     | <b>Bus Request</b> (Motorola bus mode)<br>This signal is driven low when the<br>MUNICH32 requests the control of the bus<br>and is interpreted when another<br>MUNICH32 wants to be the bus master.                                                                        |

| 79                      | HLDA   | I                       | <b>Bus Hold Acknowledge</b> (Intel bus mode)<br>This active high signal indicates that the<br>processor has released the control of the<br>bus. The MUNICH32 starts the bus cycles.                                                                                        |

|                         | BG     | I                       | <b>Bus Grant</b> (Motorola bus mode)<br>This active low signal indicates that the<br>MUNICH32 may assume the bus<br>mastership.                                                                                                                                            |

| 81                      | BGACK  | I/O                     | <b>Bus Grant Acknowledge</b> (Motorola bus<br>mode)<br>This signal is driven low by the device,<br>when it has become the bus master. It also<br>informs the MUNICH32 whether another<br>device is bus master.                                                             |

|                         | РМ     | I                       | <b>Parity Mode</b> (Intel bus mode)<br>This signal has to be strapped to $V_{\rm DD}$<br>before reset to enable the Intel parity<br>mode or to $V_{\rm SS}$ before reset to enable the<br>Intel non-parity mode. It has to be left<br>strapped during reset and operation. |

| Pin No.<br>P-MQFP-160-1 | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------|--------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 80                      | HLDAO  | 0                       | Bus Hold Acknowledge Passing ON<br>(Intel bus mode)<br>If another MUNICH32 has initiated a<br>HOLD REQUEST the HOLD<br>ACKNOWLEDGE is passed on via<br>HLDAO. The MUNICH32 does not give<br>another HOLD REQUEST before the<br>HOLD ACKNOWLEDGE has been<br>deactivated in order to prevent blocking in<br>the case of continuous request by one<br>MUNICH32.          |

|                         | BGO    | Ο                       | <b>Bus Grant Acknowledge</b> (Motorola bus<br>mode)<br>If the MUNICH32 has not requested the<br>bus mastership it passes on the BUS<br>GRANT. The MUNICH32 does not give<br>another BUS REQUEST before the BUS<br>REQUEST and the BUS GRANT<br>ACKNOWLEDGE have been deactivated<br>in order to prevent blocking in the case of<br>continuous request by one MUNICH32. |

| 66                      | ĀR     | 1                       | Action Request<br>AR must be pulsed low to cause an action<br>of the MUNICH32. The AR is activated for<br>updating the mode and channel<br>configurations, setting a test loop, or<br>initializing the interrupt queue. The<br>min. time between Reset and first AR is<br>500 μs.                                                                                      |

| Pin No.<br>P-MQFP-160-1 | Symbol  | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------|---------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40                      | INT/INT | 0                       | Interrupt Request<br>An interrupt is given when a transmission/<br>reception error is detected, frames are<br>received or transmitted, or a host initiated<br>action is performed. The interrupt pulse<br>signal interacts with a write cycle to the<br>shared memory. The data written into the<br>interrupt queue contains the interrupt<br>specification.<br>The interrupt is active high for Intel bus<br>mode and active low for Motorola bus<br>mode. |

| 44                      | RCLK    | I                       | Receive Clock<br>This clock provides the data clock for RDA<br>T1/DS1 24-channel 1.544 MHz<br>24-channel 1.536 MHz<br>CEPT 32-channel 2.048 MHz<br>32-channel 4.096 MHz                                                                                                                                                                                                                                                                                     |

| 45                      | RSP     | I                       | <b>Receive Synchronization Pulse</b><br>This signal provides the reference for the<br>receive PCM frame synchronization. It<br>marks the first bit in the PCM frame.                                                                                                                                                                                                                                                                                        |

| 46                      | RDATA   | I                       | <b>Receive Data</b><br>Serial data is received at this PCM input<br>port. The MUNICH32 supports the T1/<br>DS1 24-channel PCM format, the CEPT<br>32-channel PCM format as well as a 32-<br>channel PCM format with 4.096-Mbit/s bit<br>rate.                                                                                                                                                                                                               |

| 61                      | SCLK    | 1                       | System ClockPCM highway system clock highwayfrequency32-channel16.384 MHz2.048 or4.096 MHz24-channel12.288 MHz1.536 MHz24-channel12.352 MHz1.544 MHz                                                                                                                                                                                                                                                                                                        |

| Pin No.<br>P-MQFP-160-1 | Symbol         | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------|----------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 51 47                   | CI(4:0)        | 1                       | Chip Identification<br>Up to four MUNICH32 can be connected<br>to the PCM highway. These inputs define<br>the start address of the control section<br>pointer in the shared memory.<br>Cl4 is the polarity of A31 A22<br>Cl3 is the polarity of A21 A16<br>Cl2 is the polarity of A15 A4<br>Cl1 is the polarity of A3<br>Cl0 is the polarity of A2<br>A1, A0 are always '00' |

| 56 53                   | JTEST<br>(3:0) | I/O                     | <b>Test Pins</b><br>The MUNICH32 supports the JTAG<br>boundary scan test and the JTAG test<br>standards.                                                                                                                                                                                                                                                                     |

| 65                      | TEST           | I                       | <b>Test</b><br>If this bit is set to $V_{\text{DD}}$ MUNICH32 works in<br>a test mode.<br>For the functional working mode this bit<br>must be set to $V_{\text{SS}}$ .                                                                                                                                                                                                       |

| 67                      | TDATA          | 0                       | <b>Transmit Data</b><br>Serial data is sent by this PCM output port<br>is push-pull for active bits in the PCM<br>frame and tristate for inactive bits.                                                                                                                                                                                                                      |

| 68                      | TSP            | 1                       | <b>Transmit Synchronization Pulse</b><br>This signal provides the reference for the<br>transmit frame synchronization. It marks<br>the last bit in the PCM frame.                                                                                                                                                                                                            |

| 69                      | TCLK           | I                       | Transmit Clock<br>This clock provides the data clock for<br>TDATA<br>T1/DS1 24-channel 1.544 MHz<br>24-channel 1.536 MHz<br>CEPT 32-channel 2.048 MHz<br>32-channel 4.096 MHz                                                                                                                                                                                                |

| Pin No.<br>P-MQFP-160-1       | Symbol | Input (I)<br>Output (O) | Function                                                                    |

|-------------------------------|--------|-------------------------|-----------------------------------------------------------------------------|

| 60                            | RESET  | I                       | Reset                                                                       |

| 41, 42, 43, 52,<br>70, 71, 72 | N.C.   | -                       | <b>No Connect</b><br>These pins are reserved and should not be<br>connected |

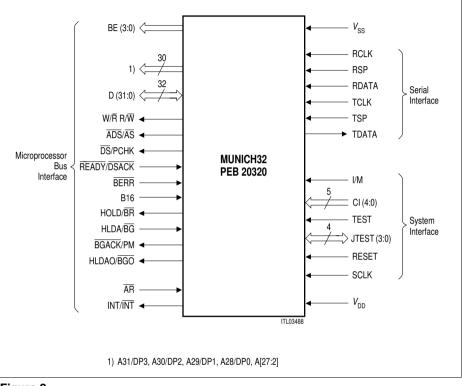

# 1.4 Logic Symbol

#### Figure 2 MUNICH32 Logic Symbol

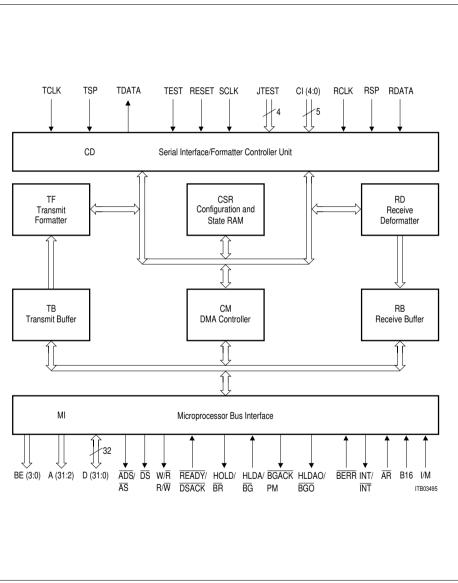

# 1.5 Functional Block Diagram

#### Figure 3 Block Diagram of MUNICH32

The internal functions of MUNICH32 are partitioned into 8 major blocks.

- 1. Serial Interface, Formatter Control Unit CD

- Parallel-Serial conversion, PCM timing, switching of the test loops, controlling of the multiplex procedure.

- 2. Transmit Formatter TF

- HDLC frame, bit stuffing, flag generation, flag stuffing and adjustment,

- CRC generation, transparent mode transmission and V.110, X.30 80 bit framing.

- 3. Transmit Buffer TB

- Buffer size of 64 long words allocated to the channels, i.e. eight PCM frames can be stored before transmission, individual channel capacity programmable.

- 4. Receive Deformatter RD

- HDLC frame, zero-bit deletion, flag detection, CRC checking, transparent mode reception and V.110, X.30 80 bit framing.

- 5. Receive Buffer RB

- Buffer size of 64 long words allocated to the channels, i.e. eight PCM frames can be stored, individual long words are freely accessible by each channel.

- 6. Configuration and State RAM CSR

- Since the Transmit Formatter, Receive Deformatter are used in a multiplex manner, the state and configuration information of each channel has to be stored.

- 7. DMA Controller CM

- Interrupt processing, memory address calculation, chaining list handling, chip configuration.

- 8. µP interface MI

- Motorola/Intel microprocessor interface.

# 1.6 System Integration

The MUNICH32 is designed to handle up to 32 data channels of a PCM highway. It transfers the data between the PCM highway and a memory shared with a host processor via a 32-bit  $\mu$ P interface. At the same time it performs protocol formatting and deformatting as well as rate adaption for each channel independently. The host sets the operating mode, bit rate adaption method and time slot allocation of each channel by writing the information into the shared memory.

Using subchanneling each time slot can be shared between up to four MUNICH32s; so that in one single time slot four different D-channels can be handled by four MUNICH32s.

Figure 4, Figure 5 and Figure 6 give a general overview of system integration of the MUNICH32.

#### Figure 4 General System Integration (Intel Bus Mode)