Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Wired Communications

Edition 2000-11-09

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany

© Infineon Technologies AG 11/8/00. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### **Warnings**

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

Dual Channel Subscriber Line Interface Codec Filter

PEB 3265 Version 1.3

PEB 3264/-2 Version 1.3

**SLICOFI-2/-2S/-2S2 Preliminary Revision History:** 2000-11-09 DS2 Previous Version: Data Sheet DS1 Page Subjects (major changes since last revision) PEB 3264, PEB 3264-2 and PEB 3265 versions changed from 1.2 to 1.3 all Page 7 Pin Definitions: Description for pins IO1B, IO2B, IO1A, IO2A and SELCLK changed. Page 11 Chapter 3.1 "Functional Overview" completely overworked. Table 4 "Operating Modes for SLICOFI-2x and SLIC": modes and Page 18 footnotes added. Table 9 "SLIC-P Interface Code": footnote modified. Page 22 Table 10 "SLIC-P Modes": modes added. Page 24 Chapter 5 "Signal Path and Test Loops": new pictures Page 31 Chapter 6.1.4 "Power Dissipation SLICOFI-2": max. limit values added. Page 32 Chapter 6.1.5 "Power Dissipation SLICOFI-2S/-2S2": max. limit values added. Page 34 Chapter 6.1.7 "Miscellaneous Characteristics": Comparator thresholds description changes Chapter 6.2.2 "Group Delay": description modified. Page 41 Chapter "Input/Output Waveform for AC Tests" on Page 43 added. Page 43 Page 45 PCM interface timings "Single-Clocking Mode" on Page 45 and "Double-Clocking Mode" on Page 46: FSC hold time ( $t_{\text{FSC}-h}$ ) renamed to FSC hold time 1 ( $t_{\text{FSC}-h1}$ ), FSC hold time 2 ( $t_{\text{FSC}}$  h<sub>2</sub>) added, formula of max. value for TCA/B delay

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com.

IOM-2 interface timings "Single-Clocking Mode" on Page 49

FSC hold time ( $t_{\text{FSC}-h}$ ) renamed to FSC hold time 1 ( $t_{\text{FSC}-h1}$ ),

FSC hold time 2 ( $t_{FSC}$  h<sub>2</sub>) added, parameters and timing of pin DU modified

and "Double-Clocking Mode" on Page 50:

Chapter 8.1 "List of Abbreviations" updated.

time off ( $t_{dTCoff}$ ) modified

Page 49

Page 52

| Table of                                                                                                                | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page                       |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 1<br>1.1<br>1.2<br>1.3                                                                                                  | Overview . Features SLICOFI-2 Features SLICOFI-2S/-2S2 Logic Symbol                                                                                                                                                                                                                                                                                                                                                                                                              | 3<br>4                     |

| <b>2</b><br>2.1                                                                                                         | Pin Descriptions     Pin Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |

| 3<br>3.1<br>3.1.1<br>3.1.2<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4                                                   | Functional Description  Functional Overview  Basic Functions available for all SLICOFI-2x Codecs  Additional Functions available for the SLICOFI-2 Codec  Block Diagrams  DTMF Generation  DTMF Detection (SLICOFI-2 only)  Caller ID Generation (SLICOFI-2 only)  Line Echo Cancelling (LEC) (SLICOFI-2 only)                                                                                                                                                                   | 11 12 14 15 15             |

| <b>4</b><br>4.1<br>4.2<br>4.3                                                                                           | Operating Modes for the DuSLIC Chip Set  SLICOFI-2S/-2S2 and SLIC-S/-S2 Interface  SLICOFI-2 and SLIC-E/-E2 Interface  SLICOFI-2 and SLIC-P Interface                                                                                                                                                                                                                                                                                                                            | 20<br>21                   |

| <b>5</b><br>5.1<br>5.2                                                                                                  | Signal Path and Test Loops Test Loops SLICOFI-2 Test Loops SLICOFI-2S/-2S2                                                                                                                                                                                                                                                                                                                                                                                                       | 24                         |

| 6<br>6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.2<br>6.2.1<br>6.2.2<br>6.3<br>6.4<br>6.4.1 | Electrical Characteristics  Electrical Characteristics PEB 3264/PEB 3264-2/PEB 3265  Absolute Maximum Ratings  Power Up Sequence for Supply Voltages  Operating Range  Power Dissipation SLICOFI-2  Power Dissipation SLICOFI-2S/-2S2  Digital Interface  Miscellaneous Characteristics  AC Transmission SLICOFI-2/-2S/-2S2  Gain Tracking (Receive or Transmit)  Group Delay  DC Characteristics  SLICOFI-2/-2S/-2S2 Timing Characteristics  Input/Output Waveform for AC Tests | 29 30 31 32 34 35 41 42 43 |

| 6.4.2<br>6.4.3                                                                                                          | MCLK/FSC Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |

| Table of                             | Table of Contents    |    |  |  |

|--------------------------------------|----------------------|----|--|--|

| 6.4.3.1<br>6.4.3.2<br>6.4.4<br>6.4.5 | Single-Clocking Mode | 46 |  |  |

| 6.4.5.1<br>6.4.5.2                   | Single-Clocking Mode | 49 |  |  |

| 7                                    | Package Outlines     | 51 |  |  |

| <b>8</b><br>8.1                      | Glossary             |    |  |  |

| 9                                    | Index                | 54 |  |  |

| List of Figur | res                                                      | Page |

|---------------|----------------------------------------------------------|------|

| Figure 1      | Logic Symbol SLICOFI-2/-2S/-2S2                          | 5    |

| Figure 2      | Pin Configuration SLICOFI-2/-2S/-2S2 (top view)          | 6    |

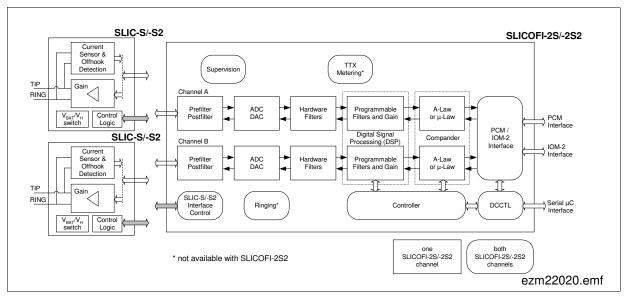

| Figure 3      | Line Circuit Functions included in the SLICOFI-2S/-2S2   | 13   |

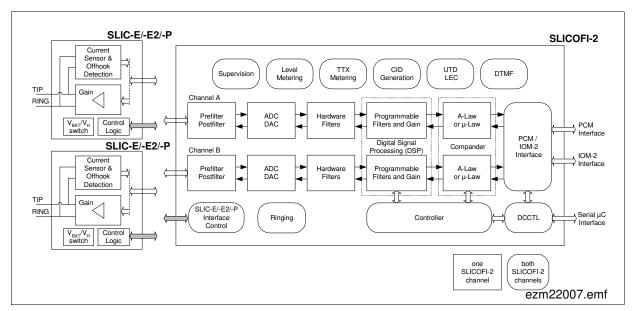

| Figure 4      | Line Circuit Functions included in the SLICOFI-2         | 13   |

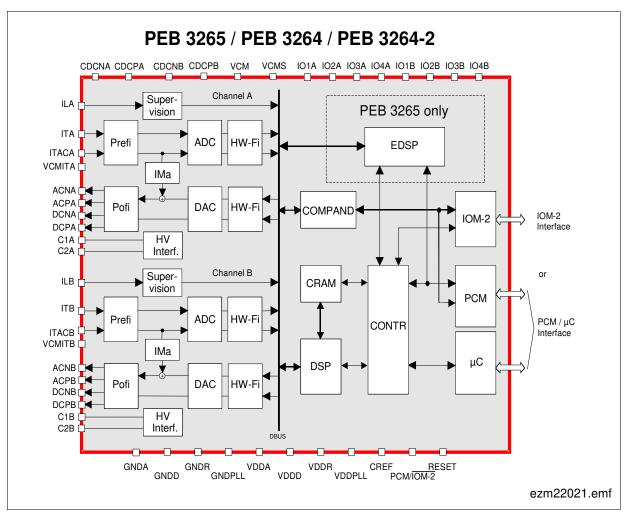

| Figure 5      | Block Diagram SLICOFI-2/-2S/-2S2 (PEB 3265, PEB 3264/-2) | 14   |

| Figure 6      | AC Test Loops SLICOFI-2                                  | 24   |

| Figure 7      | DC Test Loops SLICOFI-2                                  | 25   |

| Figure 8      | AC Test Loops SLICOFI-2S                                 | 26   |

| Figure 9      | AC Test Loops SLICOFI-2S2                                | 27   |

| Figure 10     | DC Test Loops SLICOFI-2S/-2S2                            |      |

| Figure 11     | Hysteresis for Input Pins                                |      |

| Figure 12     | Overload Compression A/D                                 |      |

| Figure 13     | Insertion Loss                                           |      |

| Figure 14     | Gain Tracking Receive                                    |      |

| Figure 15     | Gain Tracking Transmit                                   |      |

| Figure 16     | Group Delay Distortion Receive and Transmit              |      |

| Figure 17     | Insertion Loss                                           |      |

| Figure 18     | Waveform for AC Tests                                    |      |

| Figure 19     | MCLK / FSC-Timing                                        |      |

| Figure 20     | PCM Interface Timing - Single-Clocking Mode              |      |

| Figure 21     | PCM Interface Timing – Double-Clocking Mode              |      |

| Figure 22     | Microcontroller Interface Timing                         |      |

| Figure 23     | IOM-2 Interface Timing – Single-Clocking Mode            |      |

| Figure 24     | IOM-2 Interface Timing – Double-Clocking Mode            |      |

| Figure 25     | PEB 3265, PEB 3264, PEB 3264-2 (SLICOFI-2x)              | 51   |

Data Sheet 2000-11-09

#### **Preface**

#### **Synonyms**

To simplify matters, the following synonyms are used:

SLICOFI-2x Synonym used for all codec versions SLICOFI-2/-2S/-2S2

SLIC: Synonym used for all SLIC versions SLIC-S, SLIC-S2, SLIC-E2

and SLIC-P

#### **Organization of this Document**

This Data Sheet is divided into nine chapters. It is organized as follows:

- Chapter 1, Overview

A general description of the product, a list of its key features.

- · Chapter 2, Pin Descriptions

- Chapter 3, Functional Description

The main functions are presented following a functional block diagram.

- Chapter 4, Operational Description

A brief description of the three operating modes: power down, active and ringing (plus signal monitoring techniques).

- Chapter 5, Interfaces

Connection information.

- Chapter 6, Electrical Characteristics Parameters, symbols and limit values.

- Chapter 7, Package Outlines

Illustrations and dimensions of the package outlines.

- Chapter 8, Glossary

List of abbreviations and description of symbols.

- Chapter 9, Index

Data Sheet 1 2000-11-09

Preliminary Overview

#### 1 Overview

The Subscriber Line Interface Circuit *SLICOFI-2x* is a highly flexible two channel codec solution for analog line circuits. The *SLICOFI-2x* is programmable via software and can be adapted to all different standards worldwide.

#### **DuSLIC Architecture**

The SLICOFI-2 (PEB 3265) and SLICOFI-2S/-2S2 (PEB 3264/-2) chips are part of the DuSLIC chip set and are designed for use with the SLIC-E/-E2/-P (PEB 4265/-2, PEB 4266) and SLIC-S/-S2 (PEB 4264/-2) devices. For an overview about available DuSLIC versions see the DuSLIC Chip Set Selection Guide.

The DuSLIC design splits the traditional SLIC functions to high- and low-voltage functions. The low-voltage functions are handled in the *SLICOFI-2x* device, the high-voltage functions are handled in the SLIC devices.

All *SLICOFI-2x* codec devices are manufactured in an advanced 0.35 μm 3.3 V CMOS process.

For further information see Chapter 3.1.

Data Sheet 2 2000-11-09

# **Dual Channel Subscriber Line Interface Codec Filter** *SLICOFI-2x*

PEB 3265 PEB 3264 PEB 3264-2

Version 1.3 CMOS

# 1.1 Features SLICOFI-2<sup>1)</sup>

- Fully programmable dual-channel codec

- Programmable battery feeding with capability for driving long loops

- Internal balanced/unbalanced ringing capability (up to 85 Vrms balanced / 50 Vrms unbalanced)

- External ringing support

- Ground/loop start signaling

- · Polarity reversal

- On-hook transmission

- Programmable Teletax (TTX) generation

- Integrated DTMF generator

- Integrated DTMF decoder

- Integrated Caller ID (FSK) generator

- Integrated fax/modem detection (Universal Tone Detection UTD)

- Integrated Line Echo Cancellation unit (LEC)

- Optimized filter structure for modem transmission

- Message waiting lamp support (for PBX applications)

- Three-party conferencing (in PCM/μC mode)

- 8 and 16 kHz PCM Transmission

- IOM-2 or PCM/μC-interface selectable

- · Power optimized architecture

- Power management capability (battery switching)

- Integrated test and diagnosis functions

- Specification in accordance with ITU-T Recommendation Q.552 for interface Z, ITU-T Recommendation G.712 and applicable LSSGR

<sup>1)</sup> Features are indicated for the DuSLIC chip set and are partially realized by the SLICOFI-2 codec.

| Туре                           | Package     |

|--------------------------------|-------------|

| PEB 3265, PEB 3264, PEB 3264-2 | P-MQFP-64-1 |

Preliminary Overview

# 1.2 Features SLICOFI-2S/-2S2<sup>1)</sup>

- Fully programmable dual-channel codec

- Programmable battery feed with capability for driving long loops

- Internal balanced ringing capability up to 45 Vrms

- External ringing support

- Ground/loop start signaling

- Polarity reversal

- On-hook transmission

- Programmable Teletax (TTX) generation (not available with SLICOFI-2S2)

- Integrated DTMF generator

- 8 and 16 kHz PCM Transmission

- IOM-2 or PCM/μC-interface selectable

- · Power optimized architecture

- Power management capability (battery switching)

- Specification in accordance with ITU-T Recommendation Q.552 for interface Z, ITU-T Recommendation G.712 and applicable LSSGR

Data Sheet 4 2000-11-09

<sup>1)</sup> Features are indicated for the DuSLIC chip set and are partially realized by the SLICOFI-2S/-2S2 codec.

Preliminary Overview

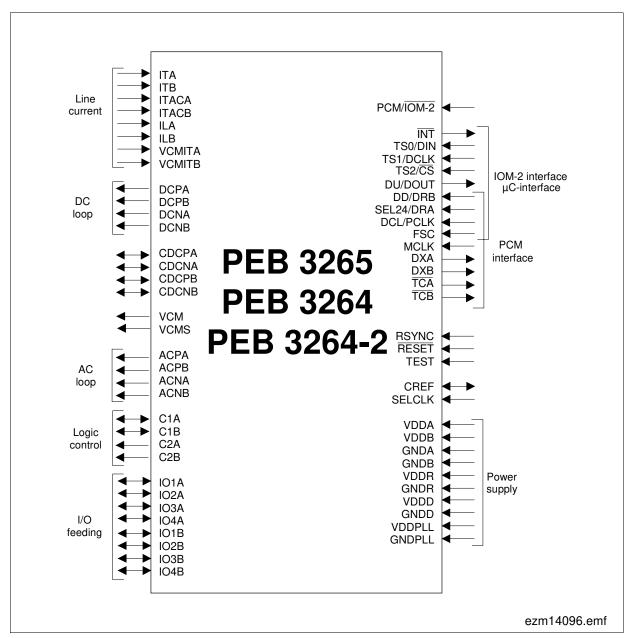

## 1.3 Logic Symbol

Figure 1 Logic Symbol SLICOFI-2/-2S/-2S2

Preliminary Pin Descriptions

# 2 Pin Descriptions

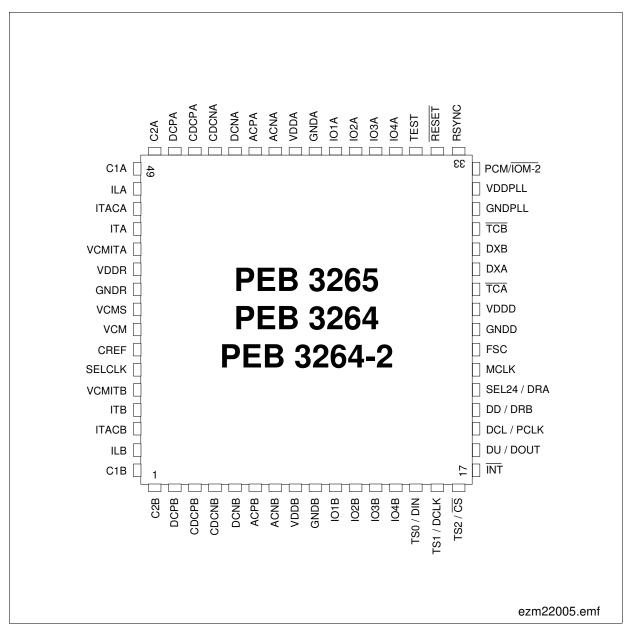

## 2.1 Pin Diagram

Figure 2 Pin Configuration SLICOFI-2/-2S/-2S2 (top view)

# **Pin Descriptions**

| Table 1 | Pin Definitions | and Functions | <b>SLICOFI-2/-2S/-2S2</b> |

|---------|-----------------|---------------|---------------------------|

|---------|-----------------|---------------|---------------------------|

| Pin<br>No. | ,           | Input (I)<br>Output (O) | Function                                                                                                                                                                                                               |  |

|------------|-------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1          | C2B         | 0                       | Ternary logic output for controlling the SLIC operation mode (channel B)                                                                                                                                               |  |

| 2          | DCPB        | 0                       | Two-wire output voltage (DCP) (channel B)                                                                                                                                                                              |  |

| 3          | CDCPB       | I/O                     | External capacitance for filtering (channel B)                                                                                                                                                                         |  |

| 4          | CDCNB       | I/O                     | External capacitance for filtering (channel B)                                                                                                                                                                         |  |

| 5          | DCNB        | 0                       | Two-wire output voltage (DCN) (channel B)                                                                                                                                                                              |  |

| 6          | ACPB        | 0                       | Differential two-wire AC output voltage controlling the RING pin (channel B)                                                                                                                                           |  |

| 7          | ACNB        | 0                       | Differential two-wire AC output voltage controlling the TIP pin (channel B)                                                                                                                                            |  |

| 8          | VDDB        | Power                   | + 3.3 V analog supply voltage (channel B)                                                                                                                                                                              |  |

| 9          | GNDB        | Power                   | Analog ground (channel B)                                                                                                                                                                                              |  |

| 10         | IO1B        | I/O                     | User-programmable I/O pin (channel B) with relay-driving capability. In external ringing mode IO1 is used to automatically control and drive the ring relay.                                                           |  |

| 11         | IO2B        | I/O                     | User-programmable I/O pin (channel B) with relay-driving capability. SLICOFI-2 and SLIC-P: connected to pin C3 of SLIC-P, when two supply voltages for voice transmission and internal ringing are used. <sup>1)</sup> |  |

| 12         | IO3B        | I/O                     | User-programmable I/O pin (channel B) with analog input functionality                                                                                                                                                  |  |

| 13         | IO4B        | I/O                     | User-programmable I/O pin (channel B) with analog input functionality                                                                                                                                                  |  |

| 14         | TS0<br>DIN  | 1                       | PCM/ $\overline{\text{IOM-2}}$ = 0 (IOM-2 interface): Time slot selection pin 0 PCM/ $\overline{\text{IOM-2}}$ = 1 ( $\mu$ C interface): Data in                                                                       |  |

| 15         | TS1<br>DCLK | 1                       | $PCM/\overline{IOM-2} = 0$ (IOM-2 interface): Time slot selection pin 1 $PCM/\overline{IOM-2} = 1$ ( $\mu C$ interface): Data clock                                                                                    |  |

| 16         | TS2<br>CS   | 1                       | PCM/IOM-2 = 0 (IOM-2 interface):<br>Time slot selection Pin 2<br>PCM/IOM-2 = 1 (μC interface): Chip select, low active                                                                                                 |  |

| 17         | ĪNT         | 0                       | $ \begin{array}{l} PCM/\overline{IOM-2} = 0 \; (IOM-2 \; interface); \; not \; connected \\ PCM/\overline{IOM-2} = 1 \; (\mu C \; interface); \; Interrupt \; pin, \; low \; active \\ \end{array} $                   |  |

# **Pin Descriptions**

Table 1 Pin Definitions and Functions SLICOFI-2/-2S/-2S2 (cont'd)

| Pin<br>No. | ,            | Input (I)<br>Output (O) | Function                                                                                                                                                                                            |  |

|------------|--------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 18         | DU<br>DOUT   | 0                       | PCM/IOM-2 = 0 (IOM-2 interface): Data upstream, open drain PCM/IOM-2 = 1 (μC interface): Data out, push/pull                                                                                        |  |

| 19         | DCL<br>PCLK  |                         | CM/IOM-2 = 1 (μο interface): Data out, push/puh<br>CM/IOM-2 = 0 (IOM-2 interface): Data clock<br>CM/IOM-2 = 1 (PCM interface): 128 kHz to 8192 kHz<br>CM clock                                      |  |

| 20         | DD<br>DRB    | <br>                    | PCM/IOM-2 = 0 (IOM-2 interface): Data downstream PCM/IOM-2 = 1 (PCM interface): Receive data input for PCM highway B                                                                                |  |

| 21         | SEL24<br>DRA | I                       | PCM/IOM-2 =0 (IOM-2 interface): SEL24 = 0: DCL = 2048 kHz selected SEL24 = 1: DCL = 4096 kHz selected PCM/IOM-2 =1 (PCM-interface): Receive Data input for PCM-highway A                            |  |

| 22         | MCLK         | I                       | PCM/IOM-2 = 0 (IOM-2 interface): not connected PCM/IOM-2 = 1 (PCM interface): master clock when PCM/μC interface is used, clock rates are 512 kHz, 1536 kHz, 2048 kHz, 4096 kHz, 7168 kHz, 8192 kHz |  |

| 23         | FSC          | I                       | Frame synchronization clock for PCM/µC or IOM-2 interface, 8 kHz, identifies the beginning of the frame, individual time slots are referenced to this input signal.                                 |  |

| 24         | GNDD         | Power                   | Digital ground                                                                                                                                                                                      |  |

| 25         | VDDD         | Power                   | + 3.3 V digital supply voltage                                                                                                                                                                      |  |

| 26         | TCA          | 0                       | Transmit control output for PCM highway A, active low during transmission, open drain                                                                                                               |  |

| 27         | DXA          | 0                       | Transmit data output for PCM highway A (goes tristate when inactive)                                                                                                                                |  |

| 28         | DXB          | 0                       | Transmit data output for PCM highway B (goes tristate when inactive)                                                                                                                                |  |

| 29         | TCB          | 0                       | Transmit control output for PCM highway B, active low during transmission, open drain                                                                                                               |  |

| 30         | GNDPLL       | Power                   | Digital ground PLL                                                                                                                                                                                  |  |

| 31         | VDDPLL       | Power                   | + 3.3 V supply voltage PLL                                                                                                                                                                          |  |

# **Pin Descriptions**

| Table 1 | Pin Definitions and Functions SLICOFI-2/-2S/-2S2 ( | cont'd) |

|---------|----------------------------------------------------|---------|

|---------|----------------------------------------------------|---------|

|            | 0             | 1                       |                                                                                                                                                                                                                        |  |

|------------|---------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin<br>No. | Sym-<br>bol   | Input (I)<br>Output (O) | Function                                                                                                                                                                                                               |  |

| 32         | PCM/<br>IOM-2 | 1                       | PCM/ $\overline{\text{IOM-2}}$ = 1: PCM/ $\mu$ C interface selected PCM/ $\overline{\text{IOM-2}}$ = 0: IOM-2 interface selected                                                                                       |  |

| 33         | RSYNC         | I                       | External ringing synchronization pin                                                                                                                                                                                   |  |

| 34         | RESET         | I                       | Reset pin, low active                                                                                                                                                                                                  |  |

| 35         | TEST          | I                       | Testpin for production test, has to be connected to GNDD                                                                                                                                                               |  |

| 36         | IO4A          | I/O                     | User-programmable I/O Pin (channel A) with analog input functionality                                                                                                                                                  |  |

| 37         | IO3A          | I/O                     | User-programmable I/O Pin (channel A) with analog input functionality                                                                                                                                                  |  |

| 38         | IO2A          | I/O                     | User-programmable I/O Pin (channel A) with relay-driving capability. SLICOFI-2 and SLIC-P: connected to pin C3 of SLIC-P, when two supply voltages for voice transmission and internal ringing are used. <sup>1)</sup> |  |

| 39         | IO1A          | I/O                     | User-programmable I/O Pin (channel A) with relay-driving capability. In external ringing mode IO1 is used to automatically control and drive the ring relay.                                                           |  |

| 40         | GNDA          | Power                   | Analog ground (channel A)                                                                                                                                                                                              |  |

| 41         | VDDA          | Power                   | + 3.3 V analog supply voltage (channel A)                                                                                                                                                                              |  |

| 42         | ACNA          | 0                       | Differential two-wire AC output voltage controlling the TIP pin (channel A)                                                                                                                                            |  |

| 43         | ACPA          | 0                       | Differential two-wire AC output voltage controlling the RING pin (channel A)                                                                                                                                           |  |

| 44         | DCNA          | 0                       | Two-wire output voltage (DCN) (channel A)                                                                                                                                                                              |  |

| 45         | CDCNA         | I/O                     | External capacitance for filtering (channel A)                                                                                                                                                                         |  |

| 46         | CDCPA         | I/O                     | External capacitance for filtering (channel A)                                                                                                                                                                         |  |

| 47         | DCPA          | 0                       | Two-wire output voltage (DCP) (channel A)                                                                                                                                                                              |  |

| 48         | C2A           | 0                       | Ternary logic output for controlling the SLIC operation mode (channel A)                                                                                                                                               |  |

| 49         | C1A           | I/O                     | Ternary logic output, controlling the SLIC operation mode (channel A); indicating thermal overload of SLIC if a current of typically 150 $\mu\text{A}$ is drawn out                                                    |  |

| 50         | ILA           | I                       | Longitudinal current input (channel A)                                                                                                                                                                                 |  |

| 51         | ITACA         | I                       | Transversal current input (AC) (channel A)                                                                                                                                                                             |  |

|            |               |                         |                                                                                                                                                                                                                        |  |

## **Pin Descriptions**

# Table 1 Pin Definitions and Functions SLICOFI-2/-2S/-2S2 (cont'd)

| Pin | ,      | Input (I)  | Function                                                                                                                                                                                                                                                                           |  |

|-----|--------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| No. | bol    | Output (O) |                                                                                                                                                                                                                                                                                    |  |

| 52  | ITA    | I          | Transversal current input (AC + DC) (channel A)                                                                                                                                                                                                                                    |  |

| 53  | VCMITA | I          | Reference pin for trans./long. current sensing (channel A)                                                                                                                                                                                                                         |  |

| 54  | VDDR   | Power      | + 3.3 V analog supply voltage (bias)                                                                                                                                                                                                                                               |  |

| 55  | GNDR   | Power      | Analog ground (bias)                                                                                                                                                                                                                                                               |  |

| 56  | VCMS   | 0          | Reference voltage for differential two-wire interface, typical 1.5 V                                                                                                                                                                                                               |  |

| 57  | VCM    | 0          | Reference voltage for input pins IT, IL, ITAC                                                                                                                                                                                                                                      |  |

| 58  | CREF   | I/O        | An external capacitor of 68 nF has to be connected to GNDR                                                                                                                                                                                                                         |  |

| 59  | SELCLK | I          | Master clock select. Should be set to GND (internal master clock generation). For test purposes, external master clock generation can be selected (SELCLK = 1). In this case a clock of nominal 32.768 Mhz with a jitter time of less than 1 ns has to be applied to the MCLK pin. |  |

| 60  | VCMITB | 1          | Reference pin for transversal/longitudinal current sensing (channel B)                                                                                                                                                                                                             |  |

| 61  | ITB    | I          | Transversal current input (AC + DC) (channel B)                                                                                                                                                                                                                                    |  |

| 62  | ITACB  | I          | Transversal current input (AC) (channel B)                                                                                                                                                                                                                                         |  |

| 63  | ILB    | I          | Longitudinal current input (channel B)                                                                                                                                                                                                                                             |  |

| 64  | C1B    | I/O        | Ternary logic output, controlling the SLIC operation mode (channel B); indicating thermal overload of SLIC if a current of typically 150 $\mu$ A is drawn out                                                                                                                      |  |

<sup>1)</sup> If SLIC-P is selected, IO2 cannot be controlled by the user, but is utilized by the SLICOFI-2 to control the C3 pin of SLIC-P.

#### **Functional Description**

# 3 Functional Description

#### 3.1 Functional Overview

#### 3.1.1 Basic Functions available for all *SLICOFI-2x* Codecs

The functions described in this chapter are integrated in all DuSLIC chip sets (see Figure 3 for SLICOFI-2S/-2S2 and Figure 4 for SLICOFI-2).

All BORSCHT functions are integrated:

- · Battery feed

- Overvoltage protection (realized by the robust high-voltage SLIC technology and additional circuitry)

- Ringing<sup>1)</sup>

- Signaling (supervision)

- Coding

- Hybrid for 2/4-wire conversion

- Testing

An important feature of the DuSLIC design is the fact that all the SLIC and codec functions are programmable via the IOM-2 or PCM/ $\mu$ C-interface of the dual channel *SLICOFI-2x* device:

- DC (battery) feed characteristics

- AC impedance matching

- Transmit gain

- · Receive gain

- Hybrid balance

- Frequency response in transmit and receive direction

- Ring frequency and amplitude<sup>1)</sup>

- · Hook thresholds

- TTX modes<sup>2)</sup>

Because signal processing within the *SLICOFI-2x* is completely digital, it is possible to adapt to the requirements listed above by simply updating the coefficients that control DSP processing of all data. This means, for example, that changing impedance matching or hybrid balance requires no hardware modifications. A single hardware is now capable of meeting the requirements for different markets. The digital nature of the filters and gain stages also assures high reliability, no drifts (over temperature or time) and minimal variations between different lines.

Data Sheet 11 2000-11-09

<sup>1)</sup> With SLICOFI-2S2 only external ringing is supported

<sup>2)</sup> Not available with SLICOFI-2S2 codec

#### **Functional Description**

The characteristics for the two voice channels within *SLICOFI-2x* can be programmed independently of each other. The DuSLICOS software is provided to automate calculation of coefficients to match different requirements. DuSLICOS also verifies the calculated coefficients.

#### 3.1.2 Additional Functions available for the SLICOFI-2 Codec

The following line circuit functions are integrated only in the SLICOFI-2 (see Figure 4):

Teletax metering

For pulse metering, a 12/16 kHz sinusoidal metering burst has to be transmitted. The DuSLIC chip set generates the metering signal internally and has an integrated notch filter.

DTMF

DuSLIC has an integrated DTMF generator comprising two tone generators and a DTMF decoder. The decoder is able to monitor the transmit or receive path for valid tone pairs and outputs the corresponding digital code for each DTMF tone pair.

Caller ID Frequency Shift Keying (FSK) Modulator

DuSLIC has an integrated FSK modulator capable of sending Caller ID information. The Caller ID modulator complies with all requirements of ITU-T recommendation V.23 and Bell 202.

LEC (Line Echo Cancellation)

DuSLIC contains an adaptive line echo cancellation unit for the cancellation of near end echos (up to 8 ms cancelable echo delay time).

UTD (Universal Tone Detection)

DuSLIC has an integrated Universal Tone Detection unit to detect special tones in the receive or transmit path (e.g. fax or modem tones).

#### **Functional Description**

Figure 3 Line Circuit Functions included in the SLICOFI-2S/-2S2

Figure 4 Line Circuit Functions included in the SLICOFI-2

#### **Functional Description**

#### 3.2 Block Diagrams

**Figure 5** shows the internal block structure of all *SLICOFI-2x* codec versions available. The Enhanced Digital Signal Processor (EDSP) realizing the add-on funtions<sup>1)</sup> is only integrated in the SLICOFI-2 (PEB 3265) device.

Figure 5 Block Diagram SLICOFI-2/-2S/-2S2 (PEB 3265, PEB 3264/-2)

Data Sheet 14 2000-11-09

The add-on functions are DTMF detection, Caller ID generation, Message Waiting lamp support, Three-party Conferencing, Universal Tone Detection (UTD), Line Echo Cancellation (LEC) and Sleep Mode.

#### **Functional Description**

## 3.2.1 DTMF Generation

The *SLICOFI-2x* offers programmable DTMF generation for both channels by using the internal tone generators.

## 3.2.2 DTMF Detection (SLICOFI-2 only)

Both channels (A and B) of the SLICOFI-2 device have a powerful built-in DTMF decoder that will meet most national requirements. The receiver algorithm performance meets the quality criteria for central office/exchange applications. It complies among others with the requirements of ITU-T Q.24, Bellcore GR-30-CORE (TR-NWT-000506) and Deutsche Telekom network (BAPT 223 ZV 5, Approval Specification of the Federal Office for Post and Telecommunications, Germany).

The performance of the algorithm can be adapted according to the needs of the application via the digital interface (detection level, twist, bandwidth and center frequency of the notch filter).

Table 2 shows the performance characteristics of the DTMF decoder algorithm:

Table 2 Performance Characteristics of the DTMF Decoder Algorithm

|    | Characteristic                                 | Value                                                  | Notes                                  |

|----|------------------------------------------------|--------------------------------------------------------|----------------------------------------|

| 1  | Valid input signal detection level             | - 48 to 0 dBm0                                         | Programmable                           |

| 2  | Input signal rejection level                   | <ul><li>5 dB of valid signal detection level</li></ul> | _                                      |

| 3  | Positive twist accept                          | < 8 dB                                                 | Programmable                           |

| 4  | Negative twist accept                          | < 8 dB                                                 | Programmable                           |

| 5  | Frequency deviation accept                     | < ± (1.5% + 4 Hz) and<br>< ± 1.8%                      | Related to center frequency            |

| 6  | Frequency deviation reject                     | > ± 3%                                                 | Related to center frequency            |

| 7  | DTMF noise tolerance (could be the same as 14) | – 12 dB                                                | dB referenced to lowest amplitude tone |

| 8  | Minimum tone accept duration                   | 40 ms                                                  | _                                      |

| 9  | Maximum tone reject duration                   | 25 ms                                                  | _                                      |

| 10 | Signaling velocity                             | ≥ 93 ms/digit                                          | _                                      |

| 11 | Minimum inter-digit pause duration             | 40 ms                                                  | _                                      |

| 12 | Maximum tone drop-out duration                 | 20 ms                                                  | _                                      |

#### **Functional Description**

Table 2 Performance Characteristics of the DTMF Decoder Algorithm (cont'd)

|    | Characteristic                                                     | Value                                                                            | Notes                                  |

|----|--------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------|

| 13 | Interference rejection 30 Hz to 480 Hz for valid DTMF recognition  | Level in frequency<br>range 30 Hz 480 Hz<br>≤ level of DTMF<br>frequency + 22 dB | dB referenced to lowest amplitude tone |

| 14 | Gaussian noise influence<br>Signal level – 22 dBm0,<br>SNR = 23 dB | Error rate better than 1 in 10000                                                | _                                      |

| 15 | Pulse noise influence<br>Impulse noise tape 201                    | Error rate better than 14 in 10000                                               | _                                      |

In the event of pauses < 20 ms:

- If the pause is followed by a tone pair with the same frequencies as before, this is interpreted as drop-out.

- If the pause is followed by a tone pair with different frequencies and if all other conditions are valid, this is interpreted as two different numbers.

DTMF decoders can be switched on or off individually to reduce power consumption. In normal operation, the decoder monitors the Tip and Ring wires via the ITAC pins (transmit path). Alternatively the decoder can be switched also in the receive path. On detecting a valid DTMF tone pair, SLICOFI-2 generates an interrupt via the appropriate INT pin and indicates a change of status. The DTMF code information is provided by a register which is read via the digital interface.

The DTMF decoder also has excellent speech-rejection capabilities and complies with Bellcore TR-TSY-000763. The algorithm has been fully tested with the speech sample sequences in the Series-1 Digit Simulation Test Tapes for DTMF decoders from Bellcore.

#### **Functional Description**

## 3.2.3 Caller ID Generation (SLICOFI-2 only)

The SLICOFI-2 contains a FSK generation unit for sending Caller ID information.

#### **SLICOFI-2 FSK Generation**

Different countries use different standards to send Caller ID information. The SLICOFI-2 chip is compatible with the widely used standards Bellcore GR-30-CORE, British Telecom (BT) SIN227, SIN242 or the UK Cable Communications Association (CCA) specification TW/P&E/312. Continuous phase binary frequency shift keying (FSK) modulation is used for coding which is compatible with BELL 202 (see **Table 3**) and ITU-T V.23, the most common standards. The SLICOFI-2 can be easily adapted to these requirements by programming via the microcontroller interface. Coefficient sets are provided for the most common standards.

Table 3 FSK Modulation Characteristics

| Characteristic    | ITU-T V.23  | Bell 202                   |  |  |  |  |  |

|-------------------|-------------|----------------------------|--|--|--|--|--|

| Mark (Logic 1)    | 1300 ± 3 Hz | 1200 ± 3 Hz                |  |  |  |  |  |

| Space (Logic 0)   | 2100 ± 3 Hz | 2200 ± 3 Hz                |  |  |  |  |  |

| Modulation        |             | FSK                        |  |  |  |  |  |

| Transmission rate |             | 1200 ± 6 baud              |  |  |  |  |  |

| Data format       | Serial      | Serial binary asynchronous |  |  |  |  |  |

# 3.2.4 Line Echo Cancelling (LEC) (SLICOFI-2 only)

The SLICOFI-2 line echo canceller is compatible with applicable standards ITU-T G.165 and G.168. An echo cancellation delay time of up to 8 ms can be programmed (for restrictions see chapter "MIPS requirements for EDSP Capabilities" in the DuSLIC Data Sheet).

# **Operating Modes for the DuSLIC Chip Set**

# 4 Operating Modes for the DuSLIC Chip Set

Table 4 Operating Modes for *SLICOFI-2x* and SLICS

| SLICOFI-2x<br>Mode                    | SLIC Type          |                    | CIDD/<br>CIOP <sup>1)</sup> |    |        | Additional Bits used (Note <sup>2)</sup> ) |                                                       |

|---------------------------------------|--------------------|--------------------|-----------------------------|----|--------|--------------------------------------------|-------------------------------------------------------|

|                                       | SLIC-S/<br>SLIC-S2 | SLIC-E/<br>SLIC-E2 | SLIC-P                      | M2 | M1     | МО                                         |                                                       |

| Sleep (SL)                            | _                  | PDRH               | PDRH                        | 1  | 1      | 1                                          | SLEEP-EN = 1                                          |

|                                       |                    |                    | PDRR                        | 1  | 1      | 1                                          | SLEEP-EN = 1, ACTR = 1                                |

| Power Down<br>Resistive (PDR)         | PDRH               | PDRH               | PDRH                        | 1  | 1      | 1                                          | SLEEP-EN = 0                                          |

|                                       |                    |                    | PDRR                        | 1  | 1      | 1                                          | SLEEP-EN = 0, ACTR = 1                                |

| Power Down<br>High Impedance<br>(PDH) | PDH                | PDH                | PDH                         | 0  | 0      | 0                                          | _                                                     |

| Active High (ACTH)                    | ACTH               | ACTH               | ACTH                        | 0  | 1      | 0                                          | _                                                     |

| Active Low<br>(ACTL)                  | ACTL               | ACTL               | ACTL                        | 0  | 1      | 0                                          | ACTL = 1                                              |

| Active Ring (ACTR)                    | ACTR               | ACTR               | ACTR                        | 0  | 1      | 0                                          | ACTR = 1                                              |

| Ringing (Ring)                        | ACTR <sup>3)</sup> | ACTR               | ACTR                        | 1  | 0      | 1                                          | _                                                     |

|                                       | _                  | _                  | ROT                         | 1  | 0      | 1                                          | HIT = 1                                               |

|                                       | _                  | _                  | ROR                         | 1  | 0      | 1                                          | HIR = 1                                               |

| Active with HIT                       | HIT                | HIT                | HIT                         | 0  | 1<br>1 | 0<br>0                                     | HIT = 1<br>HIT = 1, ACTR = 0                          |

| Active with HIR                       | HIR                | HIR                | HIR                         | 0  | 1      | 0                                          | HIR = 0<br>HIR = 0, ACTR = 0                          |

| Active with Ring to Ground            |                    |                    | ROT                         | 0  | 1      | 0                                          | HIT = 1, ACTR = 1                                     |

| Active with Tip to Ground             |                    |                    | ROR                         | 0  | 1      | 0                                          | HIR = 1, ACTR = 1                                     |

| HIRT                                  | _                  | HIRT               | HIRT                        | 0  | 1      | 0                                          | HIR = 1, HIT = 1                                      |

| Active with<br>Metering               | ACTx <sup>3)</sup> | ACTx <sup>4)</sup> | ACTx <sup>4)</sup>          | 1  | 1      | 0                                          | TTX-DIS to select Reverse<br>Polarity or TTX Metering |