Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **ICs for Communications**

**Extended PCM Interface Controller**

EPIC®-1

PEB 2055 / PEF 2055 Versions A3

EPIC®-S

PEB 2054 / PEF 2054 Versions 1.0

User's Manual 02.97

| PEB 2055<br>PEF 2055<br>Revision H | istory:                       | User's Manual 02.97                          |  |

|------------------------------------|-------------------------------|----------------------------------------------|--|

| Previous Release:                  |                               | Technical Manual 02.92 (Editorial Update)    |  |

| Page (in<br>Previous<br>Release)   | Page<br>(in User's<br>Manual) | Subjects (major changes since last revision) |  |

#### Edition 02.97

This edition was realized using the software system FrameMaker®.

Published by Siemens AG, Bereich Halbleiter, Marketing-Kommunikation, Balanstraße 73, 81541 München

© Siemens AG 7/23/97. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

| Table o         | of Contents                                                    | Page |

|-----------------|----------------------------------------------------------------|------|

| <b>1</b><br>1.1 | Overview                                                       |      |

| 1.1<br>1.2      | Pin Configuration                                              |      |

| 1.3             | Pin Definitions and Functions                                  |      |

| 1.4             | Logic Symbols                                                  |      |

| 1.5             | Functional Block Diagram                                       |      |

| 1.6             | Using the EPIC-S                                               |      |

| 1.7             | System Integration and Application                             | 18   |

| 1.7.1           | Digital Line Card                                              |      |

| 1.7.1.1         | Switching, Layer-1 Control                                     |      |

| 1.7.1.2         | Decentralized D-Channel Handling                               |      |

| 1.7.1.3         | Central D-Channel Processing                                   | 20   |

| 1.7.1.4         | Mixed D-Channel Processing, Signaling Decentralized,           |      |

| 4 7 0           | Packet Data Centralized                                        | 21   |

| 1.7.2           | Analog Line Card                                               |      |

| 1.7.3           | Packet Handlers                                                | 24   |

| 2               | Functional Description                                         | 27   |

| 2.1             | Bus Interface                                                  | 27   |

| 2.2             | PCM Interface                                                  |      |

| 2.3             | Configurable Interface                                         |      |

| 2.4             | Memory Structure and Switching                                 |      |

| 2.5             | Pre-processed Channels, Layer-1 Support                        |      |

| 2.6             | Special Functions                                              | 31   |

| 3               | Operational Description                                        | 32   |

| 3.1             | Microprocessor Interface Operation                             | 32   |

| 3.2             | Clocking                                                       |      |

| 3.3             | Reset                                                          |      |

| 3.4             | EPIC® Operation                                                |      |

| 3.4.1           | PCM-Interface                                                  |      |

| 3.4.2           | Configurable Interface                                         |      |

| 3.4.3           | Switching Functions                                            |      |

| 3.4.4           | Special Functions                                              |      |

| 3.5<br>3.5.1    | Initialization Procedure                                       |      |

| 3.5.1<br>3.5.2  | Hardware Reset                                                 |      |

| 3.5.2.1         | Register Initialization                                        |      |

| 3.5.2.1         | Control Memory Reset                                           |      |

| 3.5.2.3         | Initialization of Pre-processed Channels                       |      |

| 3.5.2.4         | Initialization of the Upstream Data Memory (DM) Tristate Field |      |

| 3.5.3           | Activation of the PCM and CFI Interfaces                       |      |

|                 |                                                                |      |

| Table o | of Contents                                                 | Page |

|---------|-------------------------------------------------------------|------|

| 4       | Detailed Register Description                               | 46   |

| 4.1     | Register Address Arrangement                                | 46   |

| 4.2     | Detailed Register Description                               | 48   |

| 4.2.1   | PCM Interface Registers                                     | 48   |

| 4.2.1.1 | PCM-Mode Register (PMOD)                                    |      |

| 4.2.1.2 | Bit Number per PCM-Frame (PBNR)                             | 50   |

| 4.2.1.3 | PCM-Offset Downstream Register (POFD)                       | 50   |

| 4.2.1.4 | PCM-Offset Upstream Register (POFU)                         | 51   |

|         | PCM-Clock Shift Register (PCSR)                             |      |

| 4.2.1.6 | PCM-Input Comparison Mismatch (PICM)                        | 52   |

| 4.2.2   | Configurable Interface Registers                            | 53   |

| 4.2.2.1 | Configurable Interface Mode Register 1 (CMD1)               | 53   |

| 4.2.2.2 | Configurable Interface Mode Register 2 (CMD2)               | 55   |

| 4.2.2.3 | Configurable Interface Bit Number Register (CBNR)           | 58   |

| 4.2.2.4 | Configurable Interface Time Slot Adjustment Register (CTAR) | 58   |

|         | Configurable Interface Bit Shift Register (CBSR)            |      |

| 4.2.2.6 | Configurable Interface Subchannel Register (CSCR)           | 60   |

| 4.2.3   | Memory Access Registers                                     | 61   |

| 4.2.3.1 | Memory Access Control Register (MACR)                       | 61   |

| 4.2.3.2 | Memory Access Address Register (MAAR)                       | 65   |

| 4.2.3.3 | Memory Access Data Register (MADR)                          | 66   |

| 4.2.4   | Synchronous Transfer Registers                              | 67   |

| 4.2.4.1 | Synchronous Transfer Data Register (STDA)                   | 67   |

| 4.2.4.2 | ,                                                           |      |

| 4.2.4.3 | Synchronous Transfer Receive Address Register A (SARA)      | 68   |

| 4.2.4.4 | Synchronous Transfer Receive Address Register B (SARB)      | 69   |

| 4.2.4.5 | Synchronous Transfer Transmit Address Register A (SAXA)     | 69   |

|         | Synchronous Transfer Transmit Address Register B (SAXB)     |      |

| 4.2.4.7 | Synchronous Transfer Control Register (STCR)                | 70   |

| 4.2.5   | Monitor/Feature Control Registers                           |      |

|         | MF-Channel Active Indication Register (MFAIR)               |      |

|         | MF-Channel Subscriber Address Register (MFSAR)              |      |

|         | Monitor/Feature Control Channel FIFO (MFFIFO)               |      |

| 4.2.6   | Status/Control Registers                                    | 73   |

| 4.2.6.1 | Signaling FIFO (CIFIFO)                                     |      |

| 4.2.6.2 | Timer Register (TIMR)                                       | 74   |

|         | Status Register (STAR)                                      |      |

|         | Command Register (CMDR)                                     |      |

|         | Interrupt Status Register (ISTA)                            |      |

|         | Mask Register (MASK)                                        |      |

| 4.2.6.7 | Operation Mode Register (OMDR)                              | 80   |

| Table o | f Contents                                                   | Page |

|---------|--------------------------------------------------------------|------|

| 4.2.6.8 | Version Number Status Register (VNSR)                        | 82   |

| 5       | Application Hints                                            | 83   |

| 5.1     | Introduction                                                 | 83   |

| 5.1.1   | IOM® and SLD Functions                                       | 83   |

| 5.2     | Configuration of Interfaces                                  | 89   |

| 5.2.1   | PCM Interface Configuration                                  | 89   |

| 5.2.1.1 | PCM Interface Signals                                        | 89   |

| 5.2.1.2 | PCM Interface Registers                                      | 89   |

| 5.2.1.3 | PCM Interface Characteristics                                | 91   |

| 5.2.2   | Configurable Interface Configuration                         | 102  |

| 5.2.2.1 | CFI Interface Signals                                        | 102  |

| 5.2.2.2 | CFI Registers                                                | 102  |

| 5.2.2.3 | CFI Characteristics                                          |      |

| 5.3     | Data and Control Memories                                    | 130  |

| 5.3.1   | Memory Structure                                             | 130  |

| 5.3.2   | Indirect Register Access                                     |      |

| 5.3.3   | Memory Access Commands                                       |      |

| 5.3.3.1 | Access to the Data Memory Data Field                         |      |

| 5.3.3.2 | Access to the Data Memory Code (Tristate) Field              |      |

| 5.3.3.3 | Access to the Control Memory Data Field                      |      |

| 5.3.3.4 | Access to the Control Memory Code Field                      | 144  |

| 5.4     | Switched Channels                                            |      |

| 5.4.1   | CFI - PCM Time Slot Assignment                               |      |

| 5.4.2   | Subchannel Switching                                         |      |

| 5.4.3   | Loops                                                        |      |

| 5.4.3.1 | CFI - CFI Loops                                              |      |

|         | PCM - PCM Loops                                              |      |

| 5.4.4   | Switching Delays                                             |      |

| 5.4.4.1 | Internal Procedures at the Serial Interfaces                 |      |

|         | How to Determine the Delay                                   |      |

|         | Example: Switching of Wide Band ISDN Channels with the EPIC® |      |

| 5.5     | Preprocessed Channels                                        |      |

| 5.5.1   | Initialization of Preprocessed Channels                      |      |

| 5.5.2   | Control/Signaling (CS) Handler                               |      |

| 5.5.2.1 | Registers used in Conjunction with the CS Handler            |      |

| 5.5.2.2 | Access to Downstream C/I and SIG Channels                    |      |

| 5.5.2.3 | Access to the Upstream C/I and SIG Channels                  |      |

| 5.5.3   | Monitor/Feature Control (MF) Handler                         |      |

| 5.5.3.1 | Registers used in Conjunction with the MF Handler            |      |

| 5.5.3.2 | •                                                            |      |

| 5.6     | μP Channels                                                  | 208  |

| Table o | of Contents                                                          | Page  |

|---------|----------------------------------------------------------------------|-------|

| 5.7     | Synchronous Transfer Utility                                         | 212   |

| 5.7.1   | Registers Used in Conjunction with the Synchronous Transfer Utility  |       |

| 5.8     | Supervision Functions                                                |       |

| 5.8.1   | Hardware Timer                                                       | 221   |

| 5.8.2   | PCM Input Comparison                                                 | 223   |

| 5.8.3   | PCM Framing Supervision                                              | 226   |

| 5.8.4   | Power and Clock Supply Supervision/Chip Version                      |       |

| 5.9     | Applications                                                         |       |

| 5.9.1   | Analog IOM®-2 Line Card with SICOFI®-4 as Codec/Filter Device        |       |

| 5.9.2   | IOM®-2 Trunk Line Applications                                       |       |

| 5.9.2.1 | PBX With Multiple ISDN Trunk Lines                                   |       |

| 5.9.2.2 | Small PBX                                                            |       |

| 5.9.3   | Miscellaneous                                                        |       |

| 5.9.3.1 | Interfacing the EPIC® to a MUSAC™                                    |       |

| 5.9.3.2 | - P                                                                  | 242   |

| 5.9.3.3 | Interfacing an IOM®-2 Terminal Mode Interface                        | 0.4.4 |

|         | to a 2.048 Mbit/s PCM Backplane                                      | 244   |

| 6       | Electrical Characteristics                                           | 246   |

| 7       | Package Outlines                                                     | 257   |

| 8       | Appendix                                                             | 258   |

| 8.1     | Working Sheets                                                       |       |

| 8.1.1   | Register Summary for EPIC® Initialization                            |       |

| 8.1.2   | Switching of PCM Time Slots to the CFI Interface (data downstream) . |       |

| 8.1.3   | Switching of CFI Time Slots to the PCM Interface (data upstream)     | 263   |

| 8.1.4   | Preparing EPIC®s C/I Channels                                        | 264   |

| 8.1.5   | Receiving and Transmitting IOM®-2 C/I-Codes                          | 265   |

| 8.2     | Development Tools                                                    | 266   |

| 8.2.1   | SIPB 5000 Mainboard                                                  |       |

| 8.2.2   | SIPB 5121 IOM®-2 Line Card (EPIC®/IDEC®)                             | 267   |

| 8.2.3   | EPIC® Configurator                                                   | 268   |

| 9       | Lists                                                                | 269   |

| 9.1     | Glossary                                                             |       |

IOM®, IOM®-1, IOM®-2, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4 $\mu$ C, SLICOFI®, ARCOFI®, ARCOFI®-BA, ARCOFI®-SP, EPIC®-1, EPIC®-S, ELIC®, IPAT®-2, ITAC®, ISAC®-S, ISAC®-S TE, ISAC®-P, ISAC®-P TE, IDEC®, SICAT®, OCTAT®-P, QUAT®-S are registered trademarks of Siemens AG.

MUSAC™-A, FALC™54, IWE™, SARE™, UTPT™, ASM™, ASP™ are trademarks of Siemens AG.

Purchase of Siemens I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C-system provided the system conforms to the I<sup>2</sup>C specifications defined by Philips. Copyright Philips 1983.

#### 1 Overview

The PEB 2055 (Extended PCM Interface Controller) is a highly integrated controller circuit optimized for analog and ISDN line card and central switches applications. The EPIC-1 provides the circuitry necessary to manage up to 32 digital (ISDN or proprietary) or 64 analog subscribers.

The EPIC-1 is dedicated to switch PCM data between two serial interfaces, the system interface (PCM interface) and the configurable interface (CFI). The EPIC-1 performs non-blocking time and space switching for up to 128 channels.

Since the system cost of the EPIC-1 is divided by the number of lines it controls, an highly economical implementation of digital or analog subscriber lines can be performed.

The EPIC-S (PEB 2054) is a pin compatible device offering half the switching capacity of the EPIC-1. Therefore the EPIC-S is capable of handling up to 16 ISDN or 32 analog subscribers. It is programmable according to the EPIC-1 with respect of the pins not available.

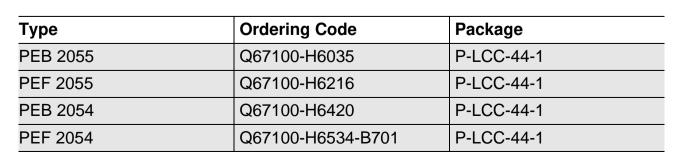

The EPIC is implemented in a Siemens advanced CMOS-technology and manufactured in a P-LCC-44-1 package.

The EPIC is member of a chip family supporting a highly economical implementation of line cards and subscriber terminals.

### **Chip Family**

| ı | ina  | $C_{2}$ | rds. |

|---|------|---------|------|

|   | 1116 | 1.4     | 1115 |

| PEB 2055  | Extended PCM Interface Controller    | (EPIC)     |

|-----------|--------------------------------------|------------|

| PEB 20550 | Extended Line Card Controller        | (ELIC)     |

| PEB 2096  | Octal U <sub>PN</sub> Transceiver    | (OCTAT-P)  |

| PEB 2095  | ISDN Burst Transceiver Circuit       | (IBC)      |

| PEB 2084  | Quadruple S <sub>0</sub> Transceiver | (QUAT-S)   |

| PEB 2465  | Quadruple DSP based Codec Filter     | (SICOFI-4) |

| PEB 2075  | ISDN D-Channel Exchange Controller   | (IDEC)     |

|           |                                      |            |

#### Terminals:

| PSB 2196 | Digital Subscriber Access Controller | (ISAC-P TE) |

|----------|--------------------------------------|-------------|

|          |                                      |             |

for U<sub>PN</sub> Interface

PEB 2081 (V3.2) S/T-Bus Interface Circuit Extended (SBCX)

# Extended PCM Interface Controller EPIC®-1, EPIC®-S

PEB 2055 PEF 2055 PEB 2054 PEF 2054

Versions A3 (PEB 2055), V1.0 (PEB 2054)

**CMOS**

#### 1.1 Features

#### **Switching**

- Board Controller for up to

- 32 ISDN or 64 analog subscribers (PEB 2055)

- 16 ISDN or 32 analog subscribers (PEB 2054)

- Non-blocking switch for

- 128 channels (PEB 2055)

- 64 channels (PEB 2054)

- Switching of 16-, 32-, or 64-kbit/s channels

- Two consecutive 64-kbit/s channels can be switched as a single 128-kbit/s channel

- Freely programmable time slot assignment for all subscribers

- Two serial interfaces (PCM and CFI) programmable over a wide data range (128 -8192 kbit/s)

- Data rates of PCM and configurable interface independent from each other (data rate adaptation)

- PCM-interface

- Tristate control signals for external drivers

- Programmable clock shift

- Single or double data clock

- Configurable interface

- Configurable for IOM-, SLD- and PCM-applications

- High degree of flexibility for datastream adaptation

- Programmable clockshift

- Single or double data clock

- Synchronous μP-access to two selected channels

#### **Handling of Layer-1 Functions**

- Change detection for C/I-channel (IOM-configuration) or feature control (SLD-configuration)

- Double last-look logic for C/I-channel (IOM-2 analog configuration)

- Additional last-look logic for feature control (SLD-configuration)

- Buffered monitor (IOM-configuration) or signaling channel (SLD-configuration)

#### **Bus Interface**

- Siemens/Intel or Motorola type μP-interface

- 8-bit demultiplexed bus interface

- FIFO-access interrupt or DMA controlled

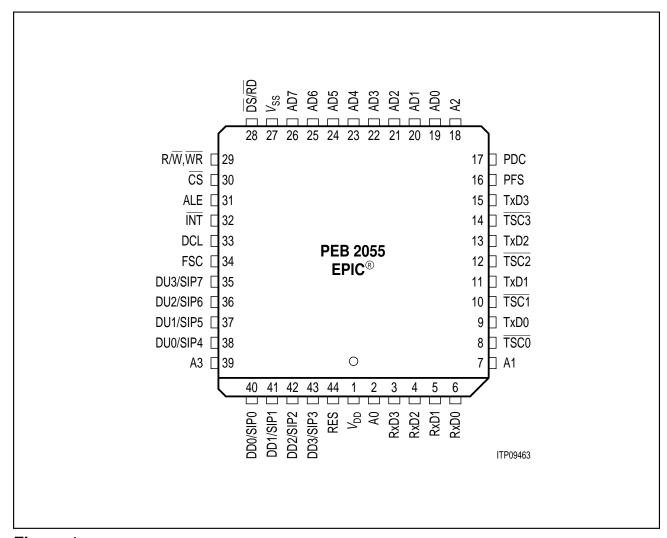

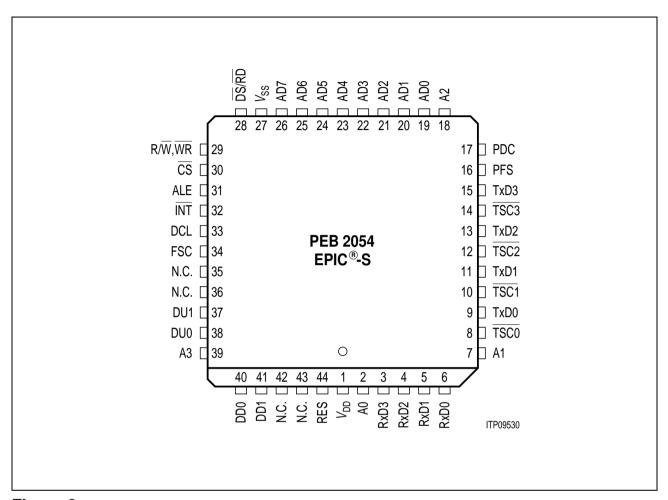

### 1.2 Pin Configuration

(top view)

Figure 1

Pin Configuration EPIC®-1

Figure 2 Pin Configuration EPIC®-S

PEB 2055 PEF 2055

# **SIEMENS**

**Overview**

### 1.3 Pin Definitions and Functions

| Pin<br>EPIC-S                                |                                              | Symbol                                                                               | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30                                           | 30                                           | CS                                                                                   | I                       | Chip Select; active low. A "low" on this line selects the EPIC for read/write operations.                                                                                                                                                                                                                            |

| 29                                           | 29                                           | WR,<br>R/W                                                                           | I                       | Write, active low, Siemens/Intel bus mode. When "low", a write operation is indicated. Read/Write, Motorola bus mode. When "high" a valid μP-access identifies a read operation, when "low" it identifies a write access.                                                                                            |

| 28                                           | 28                                           | RD, DS                                                                               |                         | Read, active low, Siemens/Intel bus mode. When "low" a read operation is indicated. Data Strobe, Motorola bus mode. A rising edge marks the end of a read or write operation.                                                                                                                                        |

| 19<br>20<br>21<br>22<br>23<br>24<br>25<br>26 | 19<br>20<br>21<br>22<br>23<br>24<br>25<br>26 | AD0, D0<br>AD1, D1<br>AD2, D2<br>AD3, D3<br>AD4, D4<br>AD5, D5<br>AD6, D6<br>AD7, D7 | I/O<br>I/O<br>I/O       | Address/Data Bus; multiplexed bus mode. Transfers addresses from the μP-system to the EPIC and data between the μP and the EPIC. Data Bus; demultiplexed bus mode. Transfers data between the μP and the EPIC. When driving data the pins have push pull characteristic, otherwise they are in high impedance state. |

| 31                                           | 31                                           | ALE                                                                                  | I                       | Address Latch Enable ALE controls the on chip address latch in multiplexed bus mode. While ALE is "high", the latch is transparent. The falling edge latches the current address. During the first read/write access following reset ALE is evaluated to select the bus mode.                                        |

| 32                                           | 32                                           | INT                                                                                  | O<br>(OD)               | Interrupt Request, active low. This signal is activated when the EPIC requests an interrupt. Due to the open drain (OD) characteristic of INT multiple interrupt sources can be connected together.                                                                                                                  |

| 44                                           | 44                                           | RES                                                                                  | I                       | Reset A "high" forces the EPIC into reset state.                                                                                                                                                                                                                                                                     |

| 16                                           | 16                                           | PFS                                                                                  | 1                       | PCM Interface Frames Synchronization                                                                                                                                                                                                                                                                                 |

PEB 2055 PEF 2055

# **SIEMENS**

Overview

## 1.3 Pin Definitions and Functions (cont'd)

| Pin<br>EPIC-S       |                          | Symbol                                       | Input (I)<br>Output (O)                          | Function                                                                                                                                                                                                                                                                                            |

|---------------------|--------------------------|----------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17                  | 17                       | PDC                                          | 1                                                | PCM Interface Data Clock Single or double data rate.                                                                                                                                                                                                                                                |

| 6<br>5<br>4<br>3    | 6<br>5<br>4<br>3         | RxD0<br>RxD1<br>RxD2<br>RxD3                 | <br>                                             | Receive PCM Interface Data Time-slot oriented data is received on this pins and forwarded into the downstream data memory of the EPIC.                                                                                                                                                              |

| 9<br>11<br>13<br>15 | 9<br>11<br>13<br>15      | TxD0<br>TxD1<br>TxD2<br>TxD3                 | 0 0 0 0                                          | Transmit PCM Interface Data Time slot oriented data is shifted out of the EPIC's upstream data memory on this lines. For time-slots which are flagged in the tristate data memory or when bit OMDR:PSB is reset the pins are set to high impedance state.                                           |

| 8<br>10<br>12<br>14 | 8<br>10<br>12<br>14      | TSC0<br>TSC1<br>TSC2<br>TSC3                 | 0 0 0 0                                          | Tristate Control Supplies a control signal for an external driver. These lines are "low" when the corresponding TxD outputs are valid. During reset these lines are "high".                                                                                                                         |

| 34                  | 34                       | FSC                                          | I/O                                              | Frame Synchronization Input or output in IOM configuration. Direction indication signal in SLD mode.                                                                                                                                                                                                |

| 33                  | 33                       | DCL                                          | I/O                                              | Data Clock Input or output in IOM, slave clock in SLD configuration. In IOM configuration single or double data rate, single data rate in SLD mode.                                                                                                                                                 |

| 38<br>37<br>-<br>-  | 38<br>37<br>36 *<br>35 * | DU0/SIP4<br>DU1/SIP5<br>DU2/SIP6<br>DU3/SIP7 | I/IO (OD)<br>I/IO (OD)<br>I/IO (OD)<br>I/IO (OD) | Data Upstream Input; IOM or PCM configuration. Serial Interface Port, SLD configuration. Depending on the bit OMDR:COS these lines have push pull or open drain characteristic. For unassigned channels or when bit OMDR:CSB is reset the pins are in the state high impedance. * Note: EPIC-1 only |

PEB 2055 PEF 2055

# **SIEMENS**

Overview

## 1.3 Pin Definitions and Functions (cont'd)

| Pin<br>EPIC-S      | _                        | Symbol                                       | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                               |

|--------------------|--------------------------|----------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40<br>41<br>-<br>- | 40<br>41<br>42 *<br>43 * | DD0/SIP0<br>DD1/SIP1<br>DD2/SIP2<br>DD3/SIP3 | ` ,                     | Data Downstream Output, IOM or PCM configuration. Serial Interface Port, SLD configuration. Depending on the bit OMDR:COS these lines have push pull or open drain characteristic. For unassigned channels or when bit OMDR:CSB is reset the pins are in the high impedance state. * Note: EPIC-1 only |

| 2<br>7<br>18<br>39 | 2<br>7<br>18<br>39       | A0<br>A1<br>A2<br>A3                         | I/O                     | Address bus in the demultiplexed $\mu P$ interface mode.                                                                                                                                                                                                                                               |

| 1 27               | 1<br>27                  | $V_{	extsf{DD}}$ $V_{	extsf{SS}}$            | 1                       | Supply voltage: 5 V ± 5%  Ground: 0 V                                                                                                                                                                                                                                                                  |

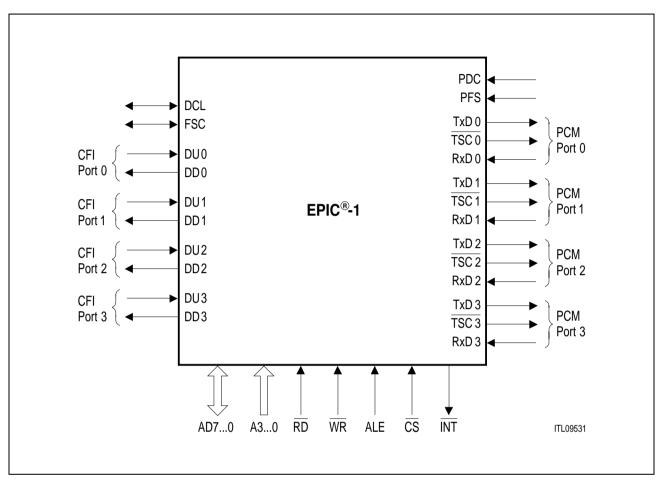

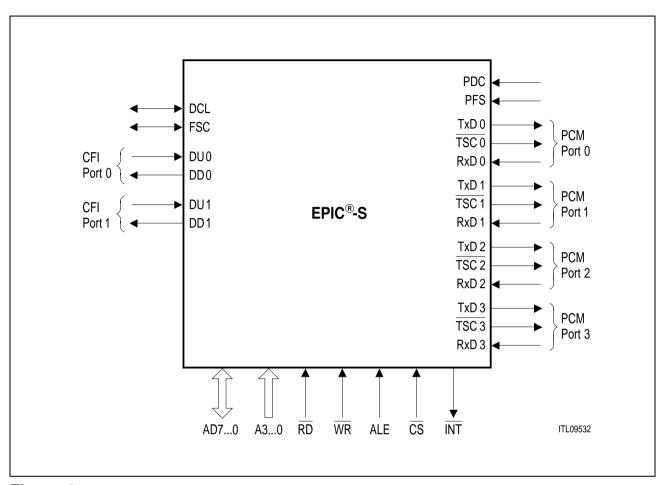

### 1.4 Logic Symbols

Figure 3 Logic Symbol of the EPIC®-1

Figure 4 Logic Symbol of the EPIC®-S

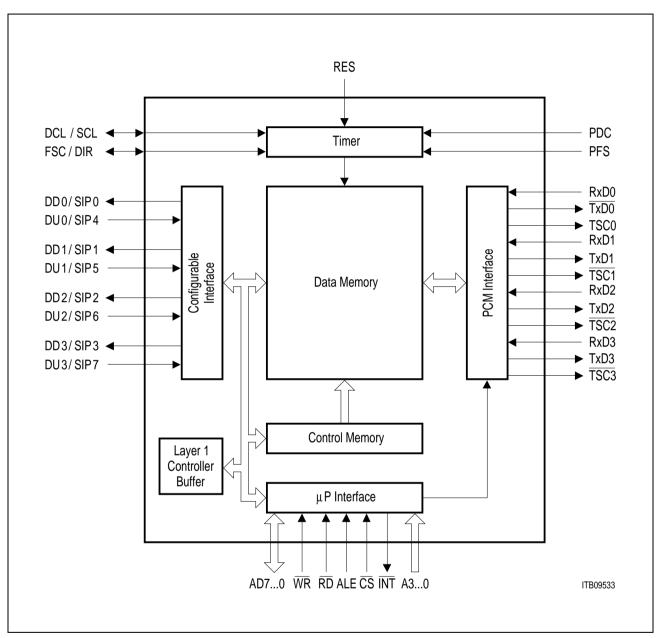

### 1.5 Functional Block Diagram

Figure 5

Functional Block Diagram EPIC®

SIEMENS PEB 2055 PEF 2055

Overview

### 1.6 Using the EPIC-S

The EPIC-S is based on the same technology as the EPIC-1 aside from only providing CFI port 0 and CFI port 1. Therefore this User's Manual applies to both, the EPIC-S and the EPIC-1.

When using the EPIC-S the user has to be aware not to program connections that would imply the not supported CFI ports.

The following points require specific attention:

- 1. During power up the EPIC-S must be supplied with an external Hardware Reset.

- 2. Register bit OMDR:CSB may be programmed to high (switch off standby of CFI interface) only after a Control Memory reset procedure with MACR:CMC3..0 =  $0_H$ .

- 3. The pins not available with respect to the EPIC-1 (PEB 2055) must not be programmed as outputs.

### 1.7 System Integration and Application

The main application fields of the EPIC are:

- Digital line cards with different architectures,

- Central control units of key systems,

- Analog line cards,

- Concentrators.

### 1.7.1 Digital Line Card

#### 1.7.1.1 Switching, Layer-1 Control

The EPIC provides a switching capability for up to 32 digital subscribers between the PCM system highway and the IOM-2 interface (64 B-channels). Typically it switches 64-kbit/s channels between the PCM and the IOM-interfaces. Moreover it is able to handle also 16-, 32- and 128-kbit/s channels.

The signaling handler supports the command/indication (C/I) channel which is used to exchange predefined layer-1 information with the transceiver device.

A monitor handler supports the handshake protocol defined on the IOM-monitor channel. It allows programming of layer-1 devices which do not have a dedicated  $\mu P$  interface.

The EPIC can be operated in tandem, i.e. one device is active, another one is a backup device. The backup device can instantaneously take over from the active device when the active device fails. Due to this tandem operation capability and the high number of ISDN subscribers which can be connected to one EPIC, the use of single line cards is feasible.

Several line card architectures are possible.

### 1.7.1.2 Decentralized D-Channel Handling

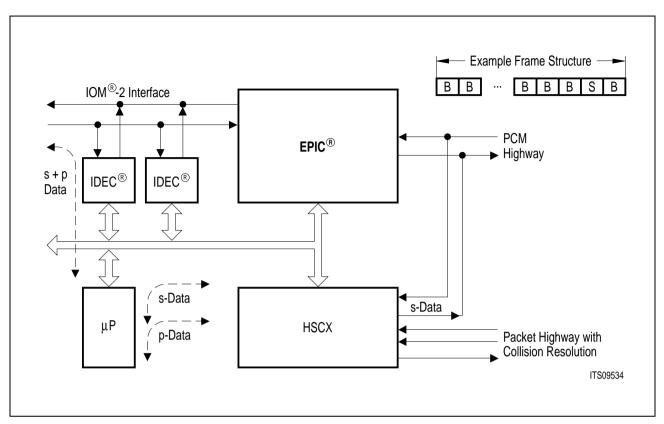

In completely decentral D-channel processing architectures (see **figure 6**), the processing capacity of the line card is usually designed to avoid blocking situations even under maximum conceivable D-channel traffic conditions. In such an architecture the EPIC switches the B-channels and performs C/I and monitor channel control.

The IDECs handle the layer 2 functions for signaling and data packets in the D-channel. They transfer the extracted data via the  $\mu P$  and an HDLC controller, e.g. the HSCX (High Level Serial Controller Extended SAB 82525) to the system. One of the channels of the HSCX may access either a time slot of programmable bandwidth on one of the system highways or a separate signalling highway.

In both cases the highway capacity used for packet traffic can be shared among several line cards due to the statistical multiplexing capabilities of the HSCX.

Figure 6

Line Card Architecture for Completely Decentral D-Channel Processing

### 1.7.1.3 Central D-Channel Processing

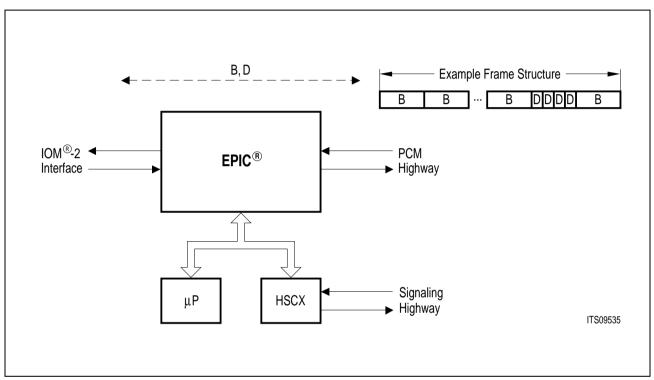

In this application the EPIC not only switches the B-channels and performs the C/I- and monitor channel control function, but switches also the D-channel data onto the system highway. In upstream direction the EPIC can combine up to four 16-kbit/s D-channels into one 64-kbit/s channel. In downstream direction it provides the capability to distribute one 64-kbit/s channel to four 16-kbit/s channels.

Figure 7

Digital Line Card Architecture with a Completely Central D-Channel Handling

# 1.7.1.4 Mixed D-Channel Processing, Signaling Decentralized, Packet Data Centralized

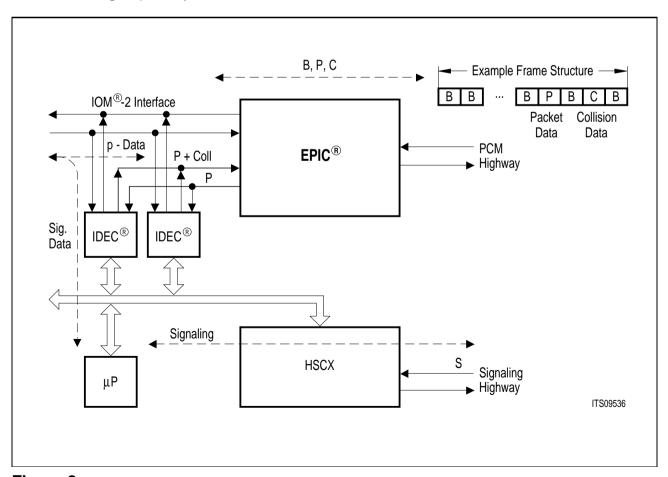

Another possibility is a mixed architecture with centralized packet data and decentralized signaling handling. This is a very flexible architecture which reduces the dynamic load of central processing units by evaluating the signaling information on the line card, but does not require resources for packet data handling. Any increase of packet data traffic does not necessitate a change in the line card architecture, the central packet handling unit can be expanded.

In this application IDECs are employed to handle the data on the D-channel. The IDECs separate signaling information from data packets. The signaling messages are transferred to the  $\mu P$ , which in turn hands them over to the group controller using the HSCX.

The packet data is processed differently. Together with the collision resolution information it is transferred to one IOM-2 port of the EPIC. The EPIC switches the channels to the PCM-highway, optionally combining four D-channels to one 64-kbit/s channel. In this configuration one IOM-2 interface is occupied by IDECs, reducing the total switching capability of the EPIC-1 to 24 ISDN-subscribers.

Figure 8

Line Card Architecture for Mixed D-Channel Processing

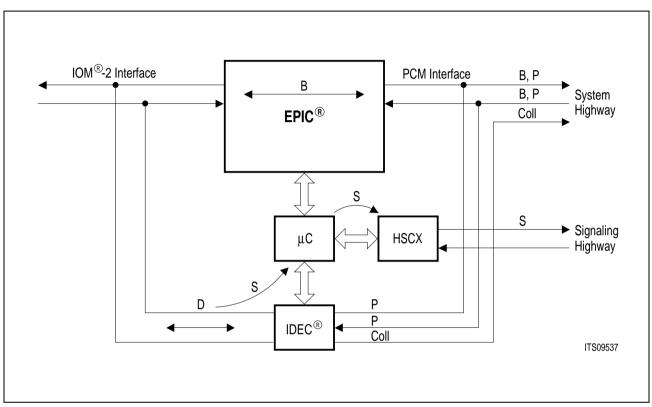

Alternatively, the packet and collision data can be directly exchanged between the IDECs and the PCM-highway. Thus, the full 32 subscriber switching capability of the EPIC is retained.

Figure 9

Line Card Architecture for Mixed D-Channel Processing

### 1.7.2 Analog Line Card

Together with the highly flexible Siemens codec filter circuits SLICOFI, SICOFI, SICOFI-2 or SICOFI-4 the EPIC constitutes an optimized analog subscriber board architecture.

The EPIC-1 handles the signalling and voice data for up to 64 subscriber channels with 64 kbit/s. The HSCX establishes the link to the group controller board.

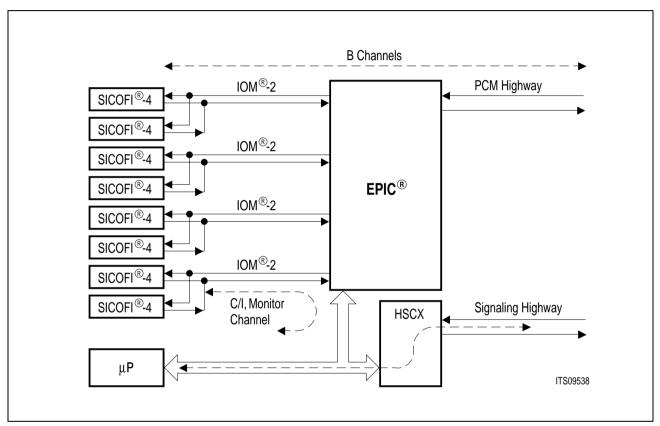

Figure 10

Line Card Architecture for Analog Subscribers

#### 1.7.3 Packet Handlers

The EPIC is an important building block for networks based on either central, decentral or mixed signaling and packet data handling architectures. Its flexibility allows for the modification of the packet handling architecture according to the changing needs.

Thus it may be useful to add central packet handling groups to a network originally based on decentral signaling and packet handling. This may be the case if growing data packet traffic exceeds the initial capacity of the network. The result is a mixed architecture.

On the other hand, increasing packet handling demand on a few dedicated subscriber lines calls for solutions which back up the capacity at these few decentral line cards.

In both of these cases and several other applications, the EPIC is a powerful device for solving the problem of packet handling. In most applications it is used together with the IDEC (ISDN D channel Exchange Controller).

Decentralized and mixed packet handling has already been covered in the line card chapter. In the following, the centralized signaling/packet handlers built up with the EPIC will be described.

Central packet handling is used if many subscribers with a generally low demand for packet switching are to be connected to a system. Concentrating the packet servers for multiple users eliminates the need to provide a packet server channel for every user. The overall number of packet server channels can thus be reduced.

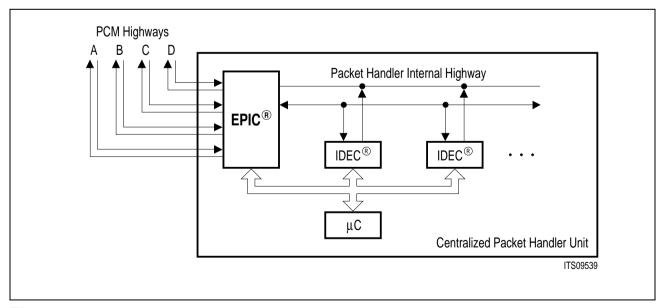

In such a central packet handling group, the EPIC performs the switching and concentrator function. It connects a variable number of PCM highways to the packet handler internal highway. HDLC controllers are also connected to this internal highway as illustrated in **figure 11**.

Figure 11

Centralized Packet Handler with a Single Internal Highway Connected to 4 PCM Highways

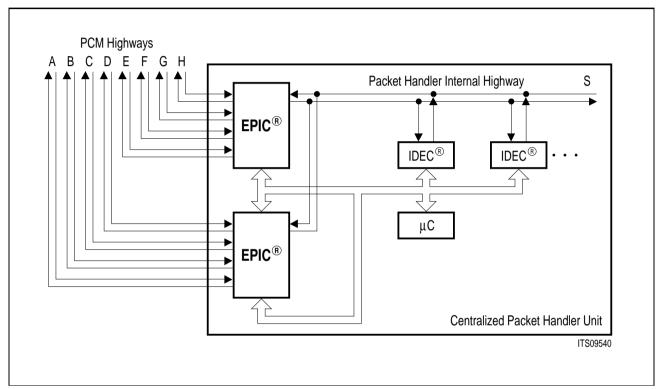

This figure shows one EPIC connecting four PCM highways to one packet handler internal highway. These highways are accessed by the IDECs, which are 4 channel HDLC controller and handle the packets. If more than four PCM highways shall be connected to the centralized packet handler, further EPICs are necessary. Such a configuration is shown in **figure 12**, where 8 highways are switched to one packet handler internal highway. In this case the two EPICs are connected in parallel at the packet handlers internal side.

Figure 12

Centralized Packet Handler with One Internal Highway Connected to 8 PCM Highways

The data rate of the packet handler internal highway can be up to 4.096 Mbit/s. If this capacity is not sufficient, other packet handler internal highways may be added as depicted in **figure 13**.