Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Wired Communications

Edition 2001-11-20

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany

© Infineon Technologies AG 2001.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# SWITI Switching IC

PEF 20450 MTSI

PEF 20470 MTSI-L

PEF 24470 MTSI-XL

Version 1.3

Wired Communications

PEF 20450 / 20470 / 24470

**PRELIMINARY**

Revision History: 2001-11-20 DS 1

**Previous Version:**

# PEF 20450 / 20470 / 24470 V1.2, Preliminary Data Sheet DS1, 2001-04-04

| Page      | Content                                                                             |

|-----------|-------------------------------------------------------------------------------------|

| 12        | Table 5 updated                                                                     |

| 26        | Chapter 3.4.3 updated, added Figure 9                                               |

| 28        | Chapter 3.7.1 and Chapter 3.7.2 updated                                             |

| 30        | Chapter 4.2 reworked                                                                |

| 49        | Description of Configuration Command Register 1 and 2 (CMD1 and CMD2) updated       |

| <b>57</b> | Description of Interrupt Status Register 1 (ISTA1) reworked                         |

| 58        | Description of Interrupt Error Status Register 1 and 2 (IESTA1 and IESTA2) reworked |

| 60        | Description of Interrupt Error Mask Register 1 and 2 (INTEM1 and INTEM2) reworked   |

| 74        | Chapter 6.2 reworked                                                                |

| 82        | Figure 18 updated                                                                   |

| 85        | Chapter 6.7.3 reworked                                                              |

| 101       | Chapter 7.1 and Table 22 updated                                                    |

| 104       | Table 23 updated                                                                    |

| 110       | Table 27 and Figure 39 updated                                                      |

| 112       | Added Chapter, 7.5"Hardware Reset Timing"                                           |

| 115       | Table 32 updated.                                                                   |

|           |                                                                                     |

|           |                                                                                     |

| -         |                                                                                     |

|           |                                                                                     |

|           |                                                                                     |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

| Table of                                                                                                                                                                                                               | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 1<br>1.1<br>1.2<br>1.3<br>1.4                                                                                                                                                                                          | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5<br>6<br>8                                        |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6                                                                                                                                                       | Pin Description Pin Diagrams Pin Definitions and Functions Local Bus Interface (PCM) General Purpose Port Clock Signals JTAG Interface Microprocessor Interface Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11 12 12 12 12 13                                  |

| 3<br>3.1<br>3.2<br>3.3<br>3.3.1<br>3.3.1.2<br>3.3.1.3<br>3.3.1.4<br>3.3.1.5<br>3.3.1.6<br>3.3.2<br>3.3.3<br>3.3.4<br>3.4.2<br>3.4.2.1<br>3.4.2.2<br>3.4.2.1<br>3.4.2.2<br>3.4.3<br>3.4.4<br>3.5<br>3.6<br>3.7<br>3.7.2 | Architectural Description Functional Block Diagram Overview of Functional Blocks Switching Factory Switching Modes Minimum and Constant Delay Subchannel Switching Multipoint Switching Broadcast Switching Bidirectional Switching Bidirectional Switching Message Mode Parallel Mode for Local Bus Switching Block Error Handling Analyze Connection and Data Memory Clock Generator and PLL General Overview Analog PLL (APLL) Functional Description Jitter Transfer Function Phase Alignment PLL Synchronization Loops Read SWITI Configuration with Indirect Register Addressing Power-On and Reset Behavior Hardware Reset Software Reset | 15 16 17 17 17 18 18 19 20 21 21 21 25 25 27 27 28 |

| 4                                                                                                                                                                                                                      | Description of Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                 |

| Table of                                                                                                     | Contents                                                                                                                                                                                                                                                                                                                                                  | Page                                         |

|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2<br>4.4<br>4.5<br>4.5.1<br>4.5.2<br>4.6<br>4.6.1<br>4.6.2<br>4.6.3<br>4.7 | Local Bus Interface (PCM)  Data Rate  Microprocessor Interface  Intel/Siemens or Motorola Mode  De-multiplexed or Multiplexed Mode  General Purpose Port (GPIO)  General Purpose Clocks  Frame Group Outputs  GPCLK as Clock Outputs  JTAG (Boundary Scan)  Boundary Scan  Test-Access-Port (TAP)  TAP Controller  Identification Code via µP Read Access | 30<br>31<br>33<br>33<br>34<br>35<br>35<br>35 |

| <b>5</b> 5.1 5.2 5.3 5.4                                                                                     | Register Description Register Overview For 8-Bit Interface Detailed Register Description For 8-bit Interface Register Overview For 16-Bit Interface Detailed Register Description For 16-Bit Interface                                                                                                                                                    | 40<br>42<br>67                               |

| <b>6</b> 6.1                                                                                                 | Programming the Device                                                                                                                                                                                                                                                                                                                                    | 73                                           |

| 6.2                                                                                                          | Interrupt Handling                                                                                                                                                                                                                                                                                                                                        |                                              |

| 6.3<br>6.4                                                                                                   | Command and Register Overview                                                                                                                                                                                                                                                                                                                             |                                              |

| 6.4<br>6.5                                                                                                   | Indirect Configuration Register Access                                                                                                                                                                                                                                                                                                                    |                                              |

| 6.6                                                                                                          | Clocking Unit                                                                                                                                                                                                                                                                                                                                             |                                              |

| 6.7                                                                                                          | Local Bus (PCM) Line Interface                                                                                                                                                                                                                                                                                                                            |                                              |

| 6.7.1                                                                                                        | Standby Command                                                                                                                                                                                                                                                                                                                                           |                                              |

| 6.7.2                                                                                                        | Determining Clock Rates                                                                                                                                                                                                                                                                                                                                   |                                              |

| 6.7.3                                                                                                        | Performing Bit Shifting                                                                                                                                                                                                                                                                                                                                   |                                              |

| 6.7.3.1                                                                                                      | Input Bit Shifting                                                                                                                                                                                                                                                                                                                                        |                                              |

| 6.7.3.2                                                                                                      | Output Bit Shifting                                                                                                                                                                                                                                                                                                                                       |                                              |

| 6.8                                                                                                          | Global Clock Signals                                                                                                                                                                                                                                                                                                                                      |                                              |

| 6.8.1                                                                                                        | Framing Groups                                                                                                                                                                                                                                                                                                                                            |                                              |

| 6.9                                                                                                          | Read Time-Slot Value                                                                                                                                                                                                                                                                                                                                      | 88                                           |

| 6.10                                                                                                         | Establish Connections                                                                                                                                                                                                                                                                                                                                     | 89                                           |

| 6.10.1                                                                                                       | Establish 8-bit Connections                                                                                                                                                                                                                                                                                                                               | 89                                           |

| 6.10.2                                                                                                       | Subchannel Switching                                                                                                                                                                                                                                                                                                                                      | 90                                           |

| 6.10.2.1                                                                                                     | Establish 4-bit Connections                                                                                                                                                                                                                                                                                                                               | 90                                           |

| 6.10.2.2                                                                                                     | Establish 2-bit Connections                                                                                                                                                                                                                                                                                                                               |                                              |

| 6.10.2.3                                                                                                     | Establish 1-bit Connections                                                                                                                                                                                                                                                                                                                               | 92                                           |

| 6.10.3                                                                                                       | Establish Broadcast Connections                                                                                                                                                                                                                                                                                                                           | 93                                           |

| Table of                                                                                                       | of Contents                                                                                                                                                                                                                                                                                                                       | Page                                               |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 6.10.4<br>6.10.5<br>6.11<br>6.12<br>6.12.1<br>6.12.2<br>6.12.3<br>6.12.4<br>6.12.5<br>6.12.5<br>6.12.7<br>6.13 | Establish Subchannel Broadcast Connection Establish Multipoint Connection Send Messages Release Connections Release 8-bit Connections Release 4-bit Connections Release 2-bit Connections Release 1-bit Connections Release Broadcast Connection Release Broadcast Connection Release Multipoint Connection Stop Sending Messages | 95<br>97<br>97<br>97<br>97<br>97<br>98<br>98<br>99 |

| 7 7.1 7.2 7.3 7.3.1 7.3.2 7.3.3 7.4 7.5                                                                        | Timing Diagrams PCM Interface Timing PCM Parallel Mode Timing Microprocessor Interface Timing Infineon/Intel Timing in De-Multiplexed Mode Infineon/Intel Timing in Multiplexed Mode Motorola Microprocessor Timing JTAG Interface Timing Hardware Reset Timing                                                                   | 101<br>104<br>105<br>105<br>106<br>108             |

| 8<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6                                                                    | Electrical Characteristics Absolute Maximum Ratings Operating Range Crystal Oscillator DC Characteristics Capacitances AC Characteristics                                                                                                                                                                                         | 113<br>113<br>114<br>115<br>116                    |

| 9                                                                                                              | Package Outlines                                                                                                                                                                                                                                                                                                                  | 117                                                |

| List of Figu | ures                                              | Page |

|--------------|---------------------------------------------------|------|

| Figure 1     | Logic Symbol                                      | 9    |

| Figure 2     | Standard PBX or CO Application                    |      |

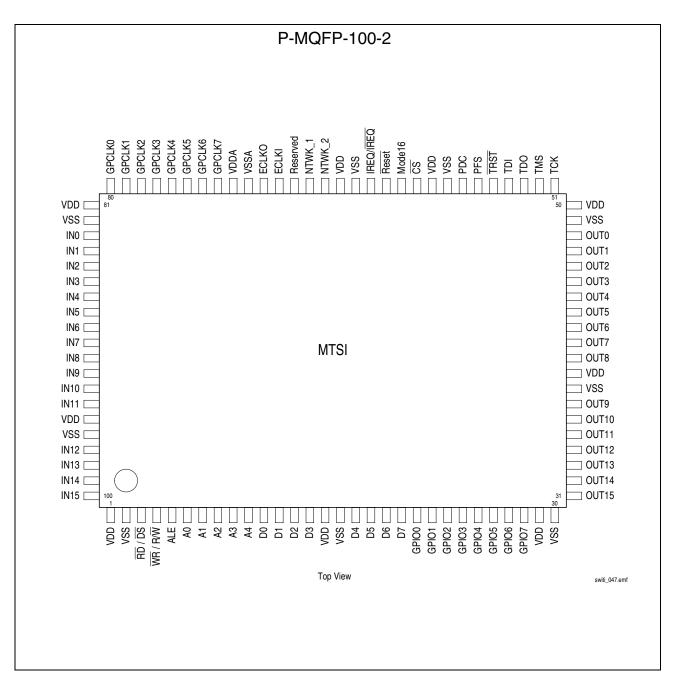

| Figure 3     | Pin Configuration                                 | 11   |

| Figure 4     | Block Diagram                                     | 15   |

| Figure 5     | Bidirectional Mode                                |      |

| Figure 6     | SWITI Clock Generator                             | 21   |

| Figure 7     | Block Diagram of APLL                             | 23   |

| Figure 8     | APLL - Jitter Transfer Function                   | 25   |

| Figure 9     | Example of Phase Alignment                        | 26   |

| Figure 10    | PCM Interface Configurations                      | 29   |

| Figure 11    | PCM Bit Shifting                                  | 30   |

| Figure 12    | Multiplexed and in De-multiplexed Bus Mode        | 32   |

| Figure 13    | GPIO Port Configuration Example                   | 33   |

| Figure 14    | Frame Signal Example                              | 34   |

| Figure 15    | Order of Register Access                          | 72   |

| Figure 16    | 8-bit µP Access Interrupt Structure               | 74   |

| Figure 17    | 16-bit μP Access Interrupt Structure              | 75   |

| Figure 18    | Initialization Procedure after Reset              | 82   |

| Figure 19    | Example: Input Bit Shifting                       | 85   |

| Figure 20    | Example: Output Bit Shifting                      | 86   |

| Figure 21    | Example Framing Groups                            | 87   |

| Figure 22    | Example: 8-bit Connection                         | 89   |

| Figure 23    | Subchannel Address in Time-Slot                   | 90   |

| Figure 24    | Example: 4-bit Connection                         | 90   |

| Figure 25    | Example: 2-bit Connection                         | 91   |

| Figure 26    | Example: 1-bit Connection                         | 92   |

| Figure 27    | Example: Broadcast Connection                     |      |

| Figure 28    | Example: Subchannel Broadcast Connection          | 94   |

| Figure 29    | Example: Multipoint Connection                    | 95   |

| Figure 30    | Example: Send Message                             |      |

| Figure 31    | PCM Timing                                        |      |

| Figure 32    | Parallel Mode Timing                              |      |

| Figure 33    | Infineon/Intel Read Cycle in De-Multiplexed Mode  |      |

| Figure 34    | Infineon/Intel Write Cycle in De-Multiplexed Mode |      |

| Figure 35    | Infineon/Intel Read Cycle in Multiplexed Mode     |      |

| Figure 36    | Infineon/Intel Write Cycle in Multiplexed Mode    |      |

| Figure 37    | Motorola Read Cycle                               |      |

| Figure 38    | Motorola Write Cycle                              |      |

| Figure 39    | Boundary Scan Timing                              |      |

| Figure 40    | Hardware Reset Timing                             |      |

| Figure 41    | External Crystal                                  |      |

| Figure 42    | I/O Wave Form for AC-Test                         |      |

| Figure 43    | Outlines of P-MQFP-100-2                          | 117  |

# PEF 20450 / 20470 / 24470

| List of Table |                                                    | Page  |

|---------------|----------------------------------------------------|-------|

| Table 1       | Who should read what?                              | 2     |

| Table 2       | SWITI Family Tree                                  | 3     |

| Table 3       | Local Bus Interface                                | 12    |

| Table 4       | GPIO                                               | 12    |

| Table 5       | Clock Pins                                         | 12    |

| Table 6       | JTAG Interface                                     | 13    |

| Table 7       | Microprocessor Interface                           | 13    |

| Table 8       | Power Supply Pins                                  | 14    |

| Table 9       | TAP Controller Instructions                        |       |

| Table 10      | Boundary Scan IDCODE                               | 37    |

| Table 11      | IDCODE via µP Read Access                          | 38    |

| Table 12      | Register Overview For 8-Bit Interface              | 40    |

| Table 13      | Value Range for SPA/DPA                            | 41    |

| Table 14      | Value Range for ITSA/OTSA                          | 41    |

| Table 15      | Value Range for SCA                                | 41    |

| Table 16      | Register Overview For 16-Bit Interface             | 67    |

| Table 17      | Affected Registers for Connection Commands         | 76    |

| Table 18      | Affected Registers for Configuration Commands      | 77    |

| Table 19      | Connection Command and Parameter Codes             | 78    |

| Table 20      | Configuration Command 1 and Parameter Codes        | 79    |

| Table 21      | Configuration Command 2 and Parameter Code         | 79    |

| Table 22      | PCM Timing                                         | . 102 |

| Table 23      | PCM Parallel Mode Timing                           | . 104 |

| Table 24      | Infineon/Intel Timing in De-Multiplexed Mode       | . 105 |

| Table 25      | Infineon/Intel Timing in Multiplexed Mode          | . 107 |

| Table 26      | Motorola Timing                                    | . 108 |

| Table 27      | JTAG Interface Timing                              | . 110 |

| Table 28      | Hardware Reset Timing                              | . 112 |

| Table 29      | Absolute Maximum Ratings                           | . 113 |

| Table 30      | Operating Range                                    |       |

| Table 31      | External Capacitances for Crystal (Recommendation) | . 114 |

| Table 32      | DC Characteristics                                 | . 115 |

| Table 33      | Input/Output Capacitances                          | . 115 |

#### **Preface**

The Switching IC (SWITI) is a family of switching devices for a wide area of telecommunication and data communication applications. This document provides complete reference information according to chip interfaces, programming, internal architecture and applications.

#### **Organization of this Document**

This Preliminary Data Sheet is divided into 9 chapters. It is organized as follows:

#### Chapter 1, Overview

Gives a general description of the product and its family, lists the key features, and presents some typical applications.

#### Chapter 2, Pin Description

Lists pin locations with associated signals, categorizes signals according to function, and describes signals.

#### Chapter 3, Description of Interfaces

Rough overview of the internal architecture.

#### Chapter 4, Description of Interfaces

Short introduction of used interfaces.

#### Chapter 5, Register Description

Gives information about all registers accessible via the microprocessor interface according to address, short name, access, reset value and value range.

#### Chapter 6. Programming the Device

Gives a variety of examples how to programm the device, lists all available command and parameter values.

# • Chapter 7, Timing Diagrams

Contains timing diagrams.

#### Chapter 8, Electrical Characteristics

Specification of the electrical parameters.

#### Chapter 9, Package Outlines

Outlines of the available packages (P-MQFP-100-2).

# Table 1 Who should read what?

| Addressed Person | Relevant Chapters |

|------------------|-------------------|

| Programmer       | 3, 5, 6           |

| Board Designer   | 2, 3, 4, 7, 8, 9  |

#### 1 Overview

The new switching family, called SWITI, provides a complete and cost-effective solution for all switching systems. The family is divided in two sub-families, the MTSI family and the HTSI family. The Preliminary Data Sheet describes the functionality and characteristic of the MTSI devices.

The devices can be used in today's switching applications, e.g. conventional PBXs and central offices, as well as in H.100/H.110 applications (only the HTSI family), which are the key to high performing CTI- and Voice-over-IP-applications, one of the most important future technologies in telecommunications.

The main requirements of today's switching applications are met by the following features:

- Constant delay e.g. to support wide band data switching, or channel bundling

- Bit switching/subchannel switching to support applications such as mobile base stations, DECT, computer telephony

In addition, the SWITI family provides new features to ensure a broad range of configurations to make it possible to adapt the device to all switching applications:

- A compliant H.100/H.110 interface (HTSI)

- 8-channel stream-to-stream switching capability (HTSI)

- · Message mode, which allows to assign a preset value to any output time-slot

- GPIO (General Purpose I/O) port, which is controlled from the external μP

**SWITI family.** The SWITI family consists of 6 ICs with different switching capacities. The possible configurations are shown in **Table 2**. The HTSI versions provide an additional H.100 / H.110 interface, while the MTSIs are standard switching devices. All devices can be programmed easily, thus helping the designer/programmer to integrate the device into his application comfortably.

Table 2 SWITI Family Tree

| Name             | Package     | Sales<br>code       | Connec-<br>tions | Local bus IN/OUT | H-Bus IO |

|------------------|-------------|---------------------|------------------|------------------|----------|

| HTSI-XL (H-Mode) | P-BGA-217-1 | PEF24471<br>HTSI-XL | 2048             | 16/16            | 32       |

| HTSI-XL (M-Mode) |             | PEF24471<br>HTSI-XL |                  | 32/32            | -        |

| HTSI-L (H-Mode)  | P-BGA-217-1 | PEF20471<br>HTSI-L  | 1024             | 16/16            | 32       |

| HTSI-L (M-Mode)  |             | PEF20471<br>HTSI-L  |                  | 32/32            | -        |

# Table 2 SWITI Family Tree (cont'd)

| Name          | Package      | Sales<br>code       | Connec-<br>tions | Local bus IN/OUT | H-Bus IO |

|---------------|--------------|---------------------|------------------|------------------|----------|

| HTSI (H-Mode) | P-BGA-217-1  | PEF20451<br>HTSI    | 512              | 16/16            | 32       |

| HTSI (M-Mode) |              | PEF20451<br>HTSI    |                  | 32/32            | -        |

| MTSI-XL       | P-MQFP-100-2 | PEF24470<br>MTSI-XL | 2048             | 16/16            | -        |

| MTSI-L        | P-MQFP-100-2 | PEF20470<br>MTSI-L  | 1024             | 16/16            | -        |

| MTSI          | P-MQFP-100-2 | PEF20450<br>MTSI    | 512              | 16/16            | -        |

# Switching IC SWITI

#### PEF 20450 / 20470 / 24470

Version 1.3 CMOS

#### 1.1 Overview of Features

#### General

- Switching capacity of 512, 1024, or up to 2048 connections of different types between different buses

- Programmable data rates of 2.048 Mbit/s, 4.096 Mbit/s, 8.192 Mbit/s, and 16.384 Mbit/s on per stream basis

- Constant delay or minimum delay programmable on per connection basis

- Subchannel switching ability of 1-bit, 2-bit, 4-bit wide time-slots

- Programmable clock shift for local bus

- Automatic data rate adaption

- Optional 8-bit parallel input and/or 8-bit parallel output for first 8 lines of local bus

- Broadcast capabilities

- Multipoint switching ability

- · Read and write access to all time-slots

- Message mode (time-slot write access)

- Programmable framing group

- GPIO port

- 8-bit µP-interface supports both Intel and Motorola mode

- Optional 16-bit µP interface mode (instead of GPIO port)

- On chip PLL for PCM bus clock operation (master/slave)

- JTAG interface

- Boundary scan according to IEEE 1149.1

- 3.3 V power supply

- 5 V tolerant inputs/outputs

| P-MQFP-100-2 |

|--------------|

| Туре                      | Package      |

|---------------------------|--------------|

| PEF 20450 / 20470 / 24470 | P-MQFP-100-2 |

#### 1.2 Features in Detail

#### **Flexible Data Rates**

Each input and each output line of the local bus is programmable to operate at different data rates. The possible data rates are 2.048 Mbit/s, 4.096 Mbit/s, 8.192 Mbit/s, and 16.384 Mbit/s.

#### **Constant and Minimum Delay**

Each connection independent of the addressed buses can be determined to be a constant delay or minimum delay connection. Constant delay means that any input time-slot or subchannel is available on the programmed output after 2 frames. Minimum delay means that the time-slot or subchannel appears at the output as soon as possible. The minimum delay depends on the chosen connections and the possible range is between 0 and 2 frames.

#### **Subchannel Switching**

Each connection can be a 1-bit, 2-bit, 4-bit, or 8-bit connection. Subchannel switching has a constant delay of 2 frames. Subchannel switching is supported only for data rate of 2.048 Mbit/s, 4.096 Mbit/s and 8.192 Mbit/s.

#### **Programmable Clock Shift**

The position of time-slot 0 of each local bus input line can be programmed within the time-slot before and after the PFS rising edge in half bit steps. Also the position of time-slot 0 of all local bus output lines can be programmed within the first time-slot after the PFS rising edge.

#### **Automatic Data Rate Adaption**

Connections are also possible between lines operating at different data rates. The programmer just specifies input and output line, time-slot, and if necessary, the subchannel.

#### **Parallel Mode**

The first 8 local bus input and output lines can be configured to one parallel input or output port respectively. In serial mode a time-slot is determined by 8 consecutive data clock cycles according to each line. In parallel mode a time-slot is determined by 1 data clock cycle according to the first 8 lines.

#### **Broadcast**

With this feature it is possible to distribute one incoming time-slot to different output time-slots.

#### Multipoint

Multipoint connections can be seen as the opposite of broadcast connections. Here it is possible to generate one output time-slot consisting of several input time-slots. The specified input time-slots are logically AND or OR connected (selectable) and have a constant delay of 2 frames.

#### **Read Access**

The programmer has access to any input time-slot. After issuing an appropriate command the arrival of the time-slot will be reported by interrupt. The value can be read from a dedicated register. For every read request the command has to be issued again.

#### **Message Mode (Write Access)**

This feature allows a constant value to be sent to any given output time-slot.

#### **Framing Group**

It is possible to specify up to 8 different framing signals of 8 kHz. The position of the rising edge and the pulse width can be programmed for each signal. The reference frame is determined by the PFS signal. The pulse parameters are programmed in half step resolution according to a 16.384 MHz clock.

#### **General Purpose Clocks**

All 8 GPCLK lines can be configured as individual clock outputs with 8 kHz, 2.048 MHz, 4.096 MHz, 8.192 MHz, 16.384 MHz and for test purposes with the internal frequency or the input frequency of the analog PLL (APLL).

#### **GPIO Port**

Each line of the general purpose input/output port can be configured to be either input or output. According to an input an edge causes an interrupt. The outputs can be influenced by write access via the microprocessor interface. Thus the user has the possibility to observe and influence additional signals for his application.

#### **Microprocessor Interface**

All devices provide a standard 8-bit microprocessor interface operating in either Intel or Motorola mode. Optionally it is possible to configure the GPIO port as additional data lines to provide a 16-bit microprocessor interface. The use of the 16-bit µP interface

reduces the number of write cycles required to configure a connection from 7 (in case of 8-bit µP interface) to 3 write cycles.

#### **Input/Output Tolerance**

The MTSI can be used in a 5 V environment. Inputs and outputs are 3.3 V and 5 V tolerant. The outputs have TTL level driving capability.

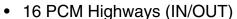

# 1.3 Logic Symbol

The MTSI is a pure PCM switch and provides 16 PCM input lines and 16 PCM output lines.

Figure 1 Logic Symbol

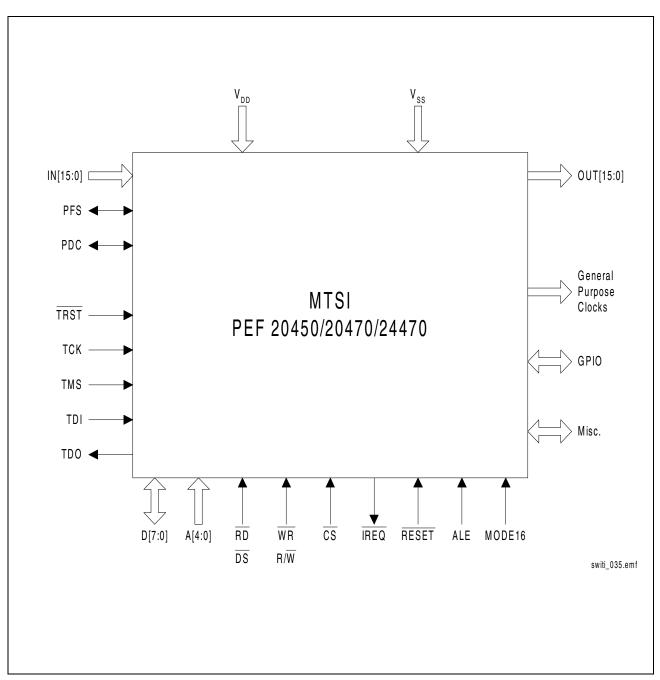

# 1.4 Standard PBX or CO Application

The MTSI or the HTSI in M-Mode can be used, just as the MTSC or MTSL, in standard private branch exchange or central office applications (**Figure 2**), e.g. in the switching network.

Figure 2 Standard PBX or CO Application

#### PRELIMINARY Pin Description

# 2 Pin Description

The pin description gives an overview of the pin numbers, names, direction, position and function ordered by the different interfaces.

Note: All unused input or I/O pins should be connected to  $V_{SS}$  to avoid leakage current.

# 2.1 Pin Diagrams

Figure 3 Pin Configuration

# PRELIMINARY Pin Description

# 2.2 Pin Definitions and Functions

# 2.2.1 Local Bus Interface (PCM)

Table 3 Local Bus Interface

| Pin No.          | Symbol                  | In (I)<br>Out (O) | Function                                                                  | Reset<br>Behavior |

|------------------|-------------------------|-------------------|---------------------------------------------------------------------------|-------------------|

| 56               | PFS                     | I/O               | PCM Frame Synchronization Clock of 8 kHz                                  | High Z            |

| 57               | PDC                     | I/O               | PCM Data Clock of 2.048 Mbit/s, 4.096 Mbit/s, 8.192 Mbit/s, 16.384 Mbit/s | High Z            |

| 100-97,<br>94-83 | IN[15:0] <sup>1)</sup>  | I                 | PCM Receive Data Port 15 to 0                                             |                   |

| 31-37,<br>40-48  | OUT[15:0] <sup>2)</sup> | 0                 | PCM Transmit Data Port 15 to 0                                            | High Z            |

<sup>1) 100</sup> is IN15, 99 is IN14, 98 is IN13..

# 2.2.2 General Purpose Port

#### Table 4 GPIO

| Pin No. | Symbol                  | In (I)<br>Out (O) | Function                                                   | Reset<br>Behavior |

|---------|-------------------------|-------------------|------------------------------------------------------------|-------------------|

| 28-21   | GPIO[7:0] <sup>1)</sup> | I/O               | General Purpose I/O port (only if 8-bit μP interface used) | Input             |

|         | D[15:8]                 |                   | Upper 8 bit of 16-bit µP interface                         |                   |

<sup>1) 28</sup> is GPIO7, 27 is GPIO6, 26 is GPIO5...

# 2.2.3 Clock Signals

Table 5 Clock Pins

| Pin No. | Symbol     | In (I)<br>Out (O) | Function                                                                                                      | Reset<br>Behavior |

|---------|------------|-------------------|---------------------------------------------------------------------------------------------------------------|-------------------|

| 69      | ECLKI      | I                 | External Crystal Input of 16.384 MHz, or 32.768 MHz<br>External Oscillator Input of 16.384 MHz, or 32.768 MHz |                   |

| 70      | ECLKO      | 0                 | External Crystal Output of 16.384 MHz, or 32.768 MHz                                                          |                   |

| 73-80   | GPCLK[7:0] | 0                 | General Purpose Clock Output (Framing Signals)                                                                | High Z            |

<sup>&</sup>lt;sup>2)</sup> 31 is OUT15, 32 is OUT14, 33 is OUT13..

# **Pin Description**

Table 5Clock Pins (cont'd)

| Pin No. | Symbol | In (I)<br>Out (O) | Function                                                                                                                                                         | Reset<br>Behavior |

|---------|--------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 67      | NTWK_1 | I                 | Primary Network Timing Reference Input<br>Optionally the PLL can be synchronized to this input which<br>can be 8 kHz, 512 kHz, 1.536 MHz, 1.544 MHz, 2.048 MHz   |                   |

| 66      | NTWK_2 | I                 | Secondary Network Timing Reference Input<br>Optionally the PLL can be synchronized to this input which<br>can be 8 kHz, 512 kHz, 1.536 MHz, 1.544 MHz, 2.048 MHz |                   |

<sup>1) 73</sup> is GPCLK7, 74 is GPCLK6, 75 is GPCLK5...

#### 2.2.4 JTAG Interface

Table 6 JTAG Interface

| Pin No. | Symbol | In (I)<br>Out (O) | Function                                                                                                           | Reset<br>Behavior |

|---------|--------|-------------------|--------------------------------------------------------------------------------------------------------------------|-------------------|

| 51      | TCK    | I                 | Test Clock<br>Single rate test data clock.                                                                         |                   |

| 52      | TMS    | I                 | Test Mode Select A '0' to '1' transition on this pin is required to step through the TAP controller state machine. |                   |

| 55      | TRST   | I                 | Test Reset Resets the TAP controller state machine (asynchronous reset).                                           |                   |

| 53      | TDO    | 0                 | Test Data Out In the appropriate TAP controller state test data or a instruction is shifted out via this line.     | High Z            |

| 54      | TDI    | I                 | Test Data Input In the appropriate TAP controller state test data or a instruction is shifted in via this line.    |                   |

# 2.2.5 Microprocessor Interface

Table 7

Microprocessor Interface

| Pin No. | Symbol | In (I)<br>Out (O) | Function                                                                                                                                                                             | Reset<br>Behavior |

|---------|--------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 60      | CS     | I                 | Chip Select Active low. A "low" on this line selects all registers for read/write operations.                                                                                        |                   |

| 3       | RD     | I                 | Read (Intel/Infineon Mode) Indicates a read access.                                                                                                                                  |                   |

|         | DS     |                   | Data Strobe (Motorola Mode) During a read cycle, DS indicates that the device should place valid data on the bus. During a write access, DS indicates that valid data is on the bus. |                   |

# **Pin Description**

Table 7

Microprocessor Interface (cont'd)

| Pin No.         | Symbol               | In (I)<br>Out (O) | Function                                                                                                                                                                                                                                                                              | Reset<br>Behavior |

|-----------------|----------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 4               | WR                   | I                 | Write (Intel/Infineon Mode) Indicates a write access.                                                                                                                                                                                                                                 |                   |

|                 | R/W                  |                   | Read/Write (Motorola Mode) Indicates the direction of the data transfer on the bus.                                                                                                                                                                                                   |                   |

| 5               | ALE                  | I                 | Address Latch Enable Controls the on-chip address latch in multiplexed bus mode. While ALE is 'high', the latch is transparent. The falling edge latches the current address. ALE is also evaluated to determine the bus mode (ALE fix 'low' = Motorola, fix 'high' = Intel/Infineon) |                   |

| 61              | MODE16               | I                 | Microprocessor Bus 8/16-Bit Interface Selection ('low' = 8 bit, 'high' = 16 bit)                                                                                                                                                                                                      |                   |

| 63              | IREQ/<br>IREQ        | O<br>OD           | Interrupt Request This pin is programmable to push/pull (active high or low) or open-drain. This signal is activated when SWITI requests an µP interrupt. When operated in open drain mode, multiple interrupt sources may be connected.                                              | High Z            |

| 10-6            | A[4:0] <sup>1)</sup> | I                 | Address Bus<br>When operated in address/data multiplex mode, the<br>address pins are externally connected to the D bus.                                                                                                                                                               |                   |

| 20-17,<br>14-11 | D[7:0] <sup>2)</sup> | I/O               | Data bus II                                                                                                                                                                                                                                                                           |                   |

| 62              | RESET                | I                 | System Reset SWITI is forced to go into reset state.                                                                                                                                                                                                                                  |                   |

<sup>1) 10</sup> is A4, 9 is A3, 8 is A2...

# 2.2.6 Power Supply

**Table 8** Power Supply Pins

| Pin No.                          | Symbol           | In (I)<br>Out (O) | Function                                        |

|----------------------------------|------------------|-------------------|-------------------------------------------------|

| 1,15, 29,39,<br>50,59, 65,81, 95 | V <sub>DD</sub>  | I                 | Power Supply 3.3 V                              |

| 2,16, 30,38,<br>49,58, 64,82, 96 | V <sub>SS</sub>  | I                 | Digital Ground (0 V)                            |

| 72                               | V <sub>DDA</sub> | I                 | Power Supply Analog Logic 3.3 V<br>Used for PLL |

| 71                               | V <sub>SSA</sub> | I                 | Analog Ground (0 V)                             |

| 68                               | R                |                   | Reserved. Must be connected to ground           |

<sup>&</sup>lt;sup>2)</sup> 20 is D7, 19 is D6, 18 is D5..

### **Architectural Description**

# 3 Architectural Description

The following sections give a short overview of the functionality of the SWITI.

# 3.1 Functional Block Diagram

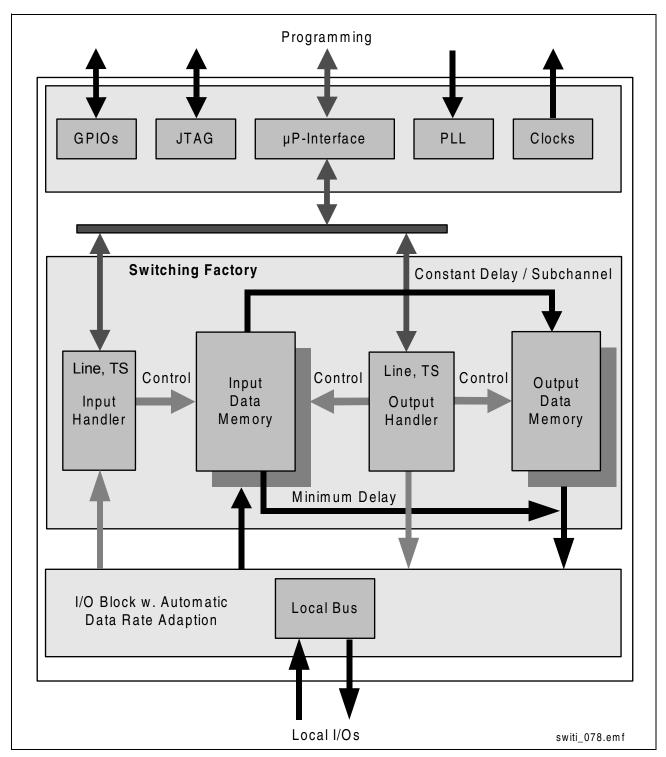

Figure 4 Block Diagram

#### **Architectural Description**

#### 3.2 Overview of Functional Blocks

#### **Switching Factory**

The switching factory is responsible for transferring and handling the incoming data streams to the assigned output channels and time-slots. The block includes a 512, 1024, or 2048 byte input and output data memory as well as an input and output connection memory.

#### Local bus I/O Block

The block is designed to handle the conversion of the data provided via the switching block and the external local bus (PCM) interface. It performs the PCM timing, the data rate selection and the tristate control.

#### **Microprocessor Interface Block**

A standard 8-bit multiplexed or de-multiplexed  $\mu P$  interface is provided, compatible to Intel/Infineon Tech. (e.g. 80386EX, C166) and Motorola (e.g. 68040, 68340, 68360, 801) bus systems. If the GPIO port is not needed it can be used to provide a 16-bit  $\mu P$  interface.

#### **GPIO Block**

This block supports up to 8 external port lines each one configurable as input or output. A change on an input line may cause an interrupt (if not masked). The user has access to the port configuration and information via the appropriate registers of the  $\mu P$  interface.

#### **PLL and Clock Block**

The PLL generates all frequencies supporting the local bus (PCM). The internal phase-locked loop (PLL) generates all bus frequencies synchronized to a selected reference signal. The output frequency tolerance is equal to the input frequency tolerance. The PLL operates from a 16.384 MHz, or 32.768 MHz external crystal, oscillator.