Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Wired Communications

Edition 2001-07-16

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 7/16/01. All Rights Reserved.

### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# DFE-Q V2.1 Quad ISDN 2B1Q Echocanceller Digital Front End

PEF 24911 Version 2.1

Wired Communications

# PEF 24911

| Revision H                     | istory: 2001-07-16                                                                                                                                                                                                                         | DS 3         |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|

| Previous Ve                    | ersion: Data Sheet 11.00                                                                                                                                                                                                                   | DS 2         |  |  |

| Page                           | Subjects (major changes since last revision)                                                                                                                                                                                               |              |  |  |

| Page 13                        | New function: Disable Super Frame Marker introduced on pin 16: DSFM                                                                                                                                                                        |              |  |  |

| Page 13<br>Page 13,<br>Page 39 | Refined description of pin 49: CRCON Especially, CRCON = '1' selects MFILT= 0011 0xxx (erroneously, MFILT= 000010xx was documented in DS2)                                                                                                 |              |  |  |

| Page 28                        | Added note: MON-12 read access is impossible in state 'Deact                                                                                                                                                                               | ivated'      |  |  |

| Page 43                        | Restriction: PACA/PACE must not be used during local loopba                                                                                                                                                                                | ck active    |  |  |

| Page 54                        | C/I-command LTD added (function as in V1.x)                                                                                                                                                                                                | _            |  |  |

| Page 63                        | AR0 and ARX set UOA = '1' (before: AR0 and ARX set UOA to value as the received SAI bit)                                                                                                                                                   | the same     |  |  |

| Page 95<br>Page 130            | Refined description 'Framer / Deframer Loopback': - always transparent - prerequisite is transparent state                                                                                                                                 |              |  |  |

| Page 97                        | Bit Error Rate Counter: refined operational description                                                                                                                                                                                    |              |  |  |

| Page 103                       | Data Through is only test mode, C/I-command = ARL must not when pin DT = '1'                                                                                                                                                               | be applied   |  |  |

| Page 113                       | Refined description of 'Control via MON-2'                                                                                                                                                                                                 |              |  |  |

| Page 119                       | Removed 'Propagation Delay Measurement': function not supp                                                                                                                                                                                 | orted        |  |  |

| Page 120                       | Refined description of mode register evaluation timing                                                                                                                                                                                     |              |  |  |

| <b>Page 121</b>                | Removed description OPMODE.MODE1,0: no settings possible                                                                                                                                                                                   | Э            |  |  |

| Page 125<br>Page 127           | SAI-evaluation / UOA-control: - M4RMASK.bit6: only SAI-reporting via MON-2 is selected - M4WMASK.bit6: in addition to UOA-bit control, also SAI-evaluate state machine is selected; refined description (see also Figure 21 and Figure 22) | ation by the |  |  |

| <b>Page 129</b>                | Changed TEST.bit6 = '1' (not '0')                                                                                                                                                                                                          |              |  |  |

| Page 130                       | Statemachine is put into transparent state by TRANS='0' (not '                                                                                                                                                                             | 1')          |  |  |

| Page 135                       | Refined reset timing description; added 900µs internal delay to                                                                                                                                                                            | figure       |  |  |

| Page 136                       | Refined description of FSC / Superframe-FSC-timing                                                                                                                                                                                         |              |  |  |

| Page 137                       | Table 21: Max. connection resistance specified                                                                                                                                                                                             |              |  |  |

| Page 139                       | Removed input capacitance of pin XIN (pin XIN is not supporte                                                                                                                                                                              | d)           |  |  |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

| Table of                                                                                                                                                                                                           | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>1.1<br>1.2<br>1.3<br>1.4                                                                                                                                                                                      | Introduction Features Logic Symbol System Integration Operational Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2<br>4<br>5                                                                                                                                                                                                                                                                        |

| <b>2</b><br>2.1<br>2.2<br>2.3                                                                                                                                                                                      | Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 11<br>. 12                                                                                                                                                                                                                                                                       |

| 3<br>3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.8.1<br>3.8.2<br>3.8.3<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14<br>3.15<br>3.16<br>3.16<br>3.16.3 | Functional Description Functional Overview IOM®-2 Interface IOM®-2 Interface Frame Structure Superframe Marker Function IOM®-2 Command/ Indicate Channel IOM®-2 Monitor Channel MON-12 Protocol Interface to the Analog Front End General Purpose I/Os Clock Generation U-Transceiver Functions 2B1Q Frame Structure Maintenance Channel M4 Bit Reporting to State Machine M4, M5, M6 Bit Control Mechanisms Start of Maintenance Bit Evaluation Embedded Operations Channel (EOC) EOC Processor Cyclic Redundancy Check Scrambling/ Descrambling Encoding/ Decoding (2B1Q) C/I Codes (2B1Q) State Machine Notation LT Mode State Diagram Inputs to the U-Transceiver in LT-Mode Outputs of the U-Transceiver in LT-Mode | <ul> <li>20</li> <li>21</li> <li>22</li> <li>23</li> <li>24</li> <li>24</li> <li>28</li> <li>30</li> <li>34</li> <li>34</li> <li>43</li> <li>45</li> <li>46</li> <li>47</li> <li>50</li> <li>52</li> <li>53</li> <li>54</li> <li>55</li> <li>57</li> <li>58</li> <li>62</li> </ul> |

| <b>4</b><br>4.1<br>4.2<br>4.3                                                                                                                                                                                      | Operational Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 69<br>. 69                                                                                                                                                                                                                                                                       |

| Table of   | Contents                                                    | Page |

|------------|-------------------------------------------------------------|------|

| 4.3.1      | Complete Activation Initiated by LT                         | 73   |

| 4.3.2      | Activation with ACT-Bit Status Ignored by the Exchange Side | 74   |

| 4.3.3      | Complete Activation Initiated by TE                         |      |

| 4.3.4      | Complete Deactivation                                       |      |

| 4.3.5      | Partial Activation (U Only)                                 |      |

| 4.3.6      | Activation Initiated by LT with U Active                    |      |

| 4.3.7      | Activation Initiated by TE with U Active                    |      |

| 4.3.8      | Deactivating S/T-Interface Only                             |      |

| 4.4        | Maintenance and Test Functions                              |      |

| 4.4.1      | Test Loopbacks                                              | 88   |

| 4.4.1.1    | Analog Loopback (No.1)                                      | 89   |

| 4.4.1.2    | Loopback No.2 - Overview                                    |      |

| 4.4.1.3    | Loopback No.2 - Complete Loopback                           | 91   |

| 4.4.1.4    | Loopback No.2 - Single Channel Loopbacks                    | 93   |

| 4.4.1.5    | Local Loopbacks Featured By Register LOOP                   |      |

| 4.4.2      | Bit Error Rate Counter                                      |      |

| 4.4.3      | Block Error Counters                                        |      |

| 4.4.3.1    | Near-End and Far-End Block Error Counter                    | 97   |

| 4.4.3.2    | Testing Block Error Counters                                | 100  |

| 4.4.4      | System Measurements                                         |      |

| 4.4.4.1    | Single-Pulses Test Mode (SSP)                               | 103  |

| 4.4.4.2    | Data Through Test Mode (DT)                                 |      |

| 4.4.4.3    | Reset Mode                                                  |      |

| 4.4.4.4    | Pulse Mask Measurement                                      |      |

| 4.4.4.5    | Power Spectral-Density Measurement                          | 104  |

| 4.4.4.6    | Total Power Measurement                                     |      |

| 4.4.4.7    | Return-Loss Measurement                                     | 105  |

| 4.4.4.8    | Quiet Mode Measurement                                      | 105  |

| 4.4.4.9    | Insertion Loss Measurement                                  | 105  |

| 4.4.5      | Boundary Scan                                               | 105  |

| 5          | Monitor Commands                                            | 110  |

| 5.1        | MON-0 - Exchanging EOC Information                          |      |

| 5.1        | <b>5 5</b>                                                  | _    |

| 5.2<br>5.3 | MON-2 - Exchanging Overhead Bits                            |      |

| 5.3        | MON-6 - Local Functions                                     | 114  |

| 6          | Register Description                                        | 117  |

| 6.1        | Register Summary                                            |      |

|            | 118                                                         |      |

| 6.2        | Reset of U-Transceiver Functions in State 'Deactivated'     | 120  |

| 6.3        | Mode Register Evaluation Timing                             | 120  |

| 6.4        | Detailed Register Description                               |      |

| 6.4.1      | LP_SEL - Line Port Selection Register                       | 121  |

Data Sheet 2001-07-16

# **PEF 24911**

| Table of                         | f Contents                                   | Page |

|----------------------------------|----------------------------------------------|------|

| 6.4.2<br>6.4.3<br>6.4.4<br>6.4.5 | OPMODE - Operation Mode Register             | 122  |

| 6.4.6                            | TEST - Test Register                         |      |

| 6.4.7                            | LOOP - Loop Back Register                    |      |

| 6.4.8                            | FEBE - Far End Block Error Counter Register  |      |

| 6.4.9                            | NEBE - Near End Block Error Counter Register |      |

| 6.4.10                           | BERC - Bit Error Rate Counter Register       | 132  |

| 7                                | Electrical Characteristics                   | 133  |

| 7.1                              | Absolute Maximum Ratings                     | 133  |

| 7.2                              | Operating Range                              | 133  |

| 7.3                              | DC Characteristics                           |      |

| 7.4                              | AC Characteristics                           |      |

| 7.4.1                            | Reset Timing                                 |      |

| 7.4.2                            | IOM®-2 Interface Timing                      |      |

| 7.4.3                            | Interface to the Analog Front End            |      |

| 7.4.4                            | Boundary Scan Timing                         |      |

| 7.5                              | Capacitances                                 |      |

| 7.6                              | Power Supply                                 |      |

| 7.6.1                            | Supply Voltage                               |      |

| 7.6.2                            | Power Consumption                            | 139  |

| 8                                | Package Outlines                             | 140  |

| 9                                | Appendix A: Standards and Specifications     | 141  |

| 10                               | Glossary                                     | 142  |

| List of Figu | ıres                                                         | Page   |

|--------------|--------------------------------------------------------------|--------|

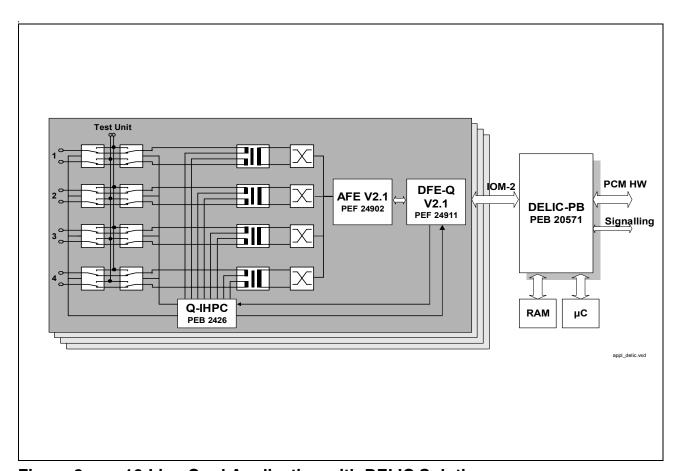

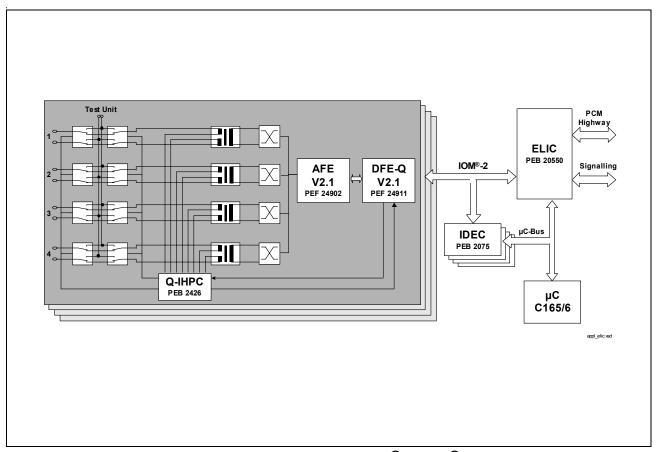

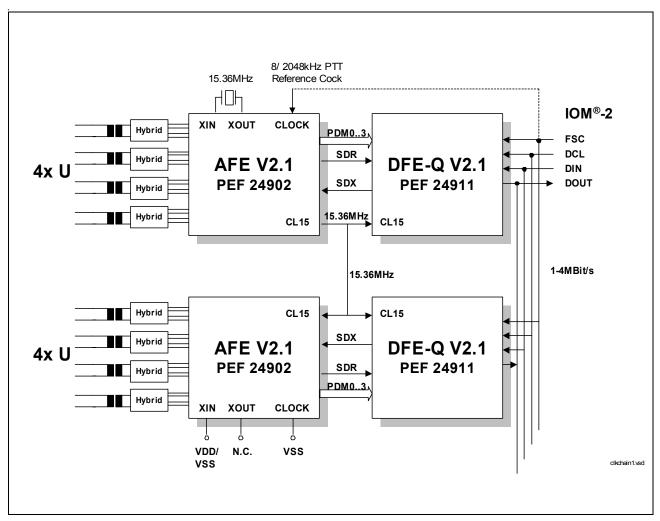

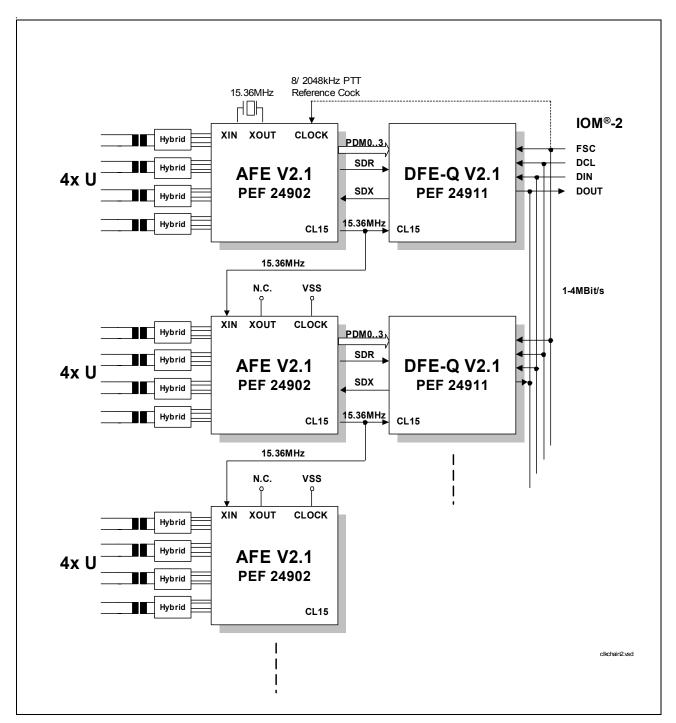

| Figure 1     | DFE-Q/ AFE 2nd Generation Chip Set                           | 1      |

| Figure 2     | Logic Symbol                                                 |        |

| Figure 3     | 16-Line Card Application with DELIC Solution                 | 5      |

| Figure 4     | 16-Line Card Application with ELIC®/ IDEC® Solution          |        |

| Figure 5     | Connecting Two AFE/DFE-Q Chip Sets                           |        |

| Figure 6     | Recommended Clocking Scheme for More Than Two DFE-Q/AFE      | E Chip |

| ,            | Sets 8                                                       |        |

| Figure 7     | Pin Configuration (63 of 64 used)                            |        |

| Figure 8     | Block Diagram and Data Flow (DFE-Q V2.1 + AFE V2.1)          |        |

| Figure 9     | Clock Supply and Data Exchange between Master and Slave      |        |

| Figure 10    | Multiplexed Frame Structure of the IOM®-2 Interface          |        |

| Figure 11    | Superframe Marker                                            |        |

| Figure 12    | Handshake Protocol with a 2-Byte Monitor Message/Response    |        |

| Figure 13    | Abortion of Monitor Channel Transmission                     |        |

| Figure 14    | Interface to the Analog Front End                            |        |

| Figure 15    | Frame Structure on SDX/SDR                                   |        |

| Figure 16    | U-Superframe Structure                                       |        |

| Figure 17    | U-Basic Frame Structure                                      |        |

| Figure 18    | MON-0/2 - M-Bit Correspondence                               |        |

| Figure 19    | Maintenance Channel Filtering Options                        |        |

| Figure 20    | M4 Bit Report Timing                                         |        |

| Figure 21    | M4, M5, M6 Bit Control in Transmit Direction                 |        |

| Figure 22    | M4, M5, M6 Bit Control in Receive Direction                  |        |

| Figure 23    | EOC-Procedure in Auto- and Transparent Mode                  |        |

| Figure 24    | CRC-Process                                                  |        |

| Figure 25    | Scrambler/ Descrambler Algorithms                            |        |

| Figure 26    | Explanation of the State Diagram                             |        |

| Figure 27    | State Transition Diagram in LT-Mode                          |        |

| Figure 28    | Complete Activation Initiated by LT                          |        |

| Figure 29    | Activation with ACT-Bit Status Ignored by the Exchange       |        |

| Figure 30    | Complete Activation Initiated by TE                          |        |

| Figure 31    | Complete Deactivation                                        |        |

| Figure 32    | U Only Activation                                            |        |

| Figure 33    | LT Initiated Activation with U-Interface Active              |        |

| Figure 34    | TE-Activation with U Active and Exchange Control (case 1)    |        |

| Figure 35    | TE-Activation with U Active and no Exchange Control (case 2) |        |

| Figure 36    | Deactivation of S/T Only                                     |        |

| Figure 37    | Test Loopbacks                                               |        |

| Figure 38    | Complete Loopback Options in the NT                          |        |

| Figure 39    | Loopbacks Featured by Register LOOP                          |        |

| Figure 40    | Block Error Counter Test                                     |        |

| Figure 41    | Total Power Measurement Set-Up                               | 104    |

Data Sheet 2001-07-16

# **PEF 24911**

| List of Figures |                                    |     |

|-----------------|------------------------------------|-----|

| Figure 42       | DFE-Q V2.1 Register Map            | 117 |

| Figure 43       | Input/Output Waveform for AC Tests | 135 |

| Figure 44       | Reset Timing                       | 135 |

| Figure 45       | IOM®-2 Interface Timing            | 136 |

| Figure 46       | Boundary Scan Timing               | 138 |

Data Sheet 2001-07-16

# **PEF 24911**

| List of Tab | les                                                   | Page           |

|-------------|-------------------------------------------------------|----------------|

| Table 1     | Pin Definitions and Functions                         | 12             |

| Table 2     | Pinning Changes                                       | 19             |

| Table 3     | IOM®-2 Data Rates                                     | 22             |

| Table 4     | Assignments of IOM® Channels to Time-Slots No. on SDX | K/SDR and Line |

|             | Ports No. 30                                          |                |

| Table 5     | 2B1Q Coding Table                                     | 32             |

| Table 6     | 2B1Q U-Frame Structure                                | 35             |

| Table 7     | Overhead Bits Filter Setting by CRCON Pin             | 40             |

| Table 8     | Supported EOC-Commands                                | 46             |

| Table 9     | 2B1Q Coding Table                                     | 53             |

| Table 10    | Command / Indicate Codes (2B1Q)                       | 54             |

| Table 11    | Timers Used in LT-Modes                               | 61             |

| Table 12    | U-Interface Signals                                   | 71             |

| Table 13    | Boundary Scan Cells                                   | 106            |

| Table 14    | TAP Controller Instructions:                          | 108            |

| Table 15    | MON-0 Functions                                       |                |

| Table 16    | MON-2 and Overhead Bits                               | 113            |

| Table 17    | MON-8-Local Function Commands                         | 115            |

| Table 18    | Register Map Reference Table                          | 118            |

| Table 19    | IOM®-2 Dynamic Input Characteristics                  | 136            |

| Table 20    | IOM®-2 Dynamic Output Characteristics                 | 137            |

| Table 21    | Interface Signals of AFE and DFE-Q                    | 137            |

| Table 22    | Boundary Scan Dynamic Timing Requirements             | 138            |

| Table 23    | Power Consumption                                     | 139            |

# 1 Introduction

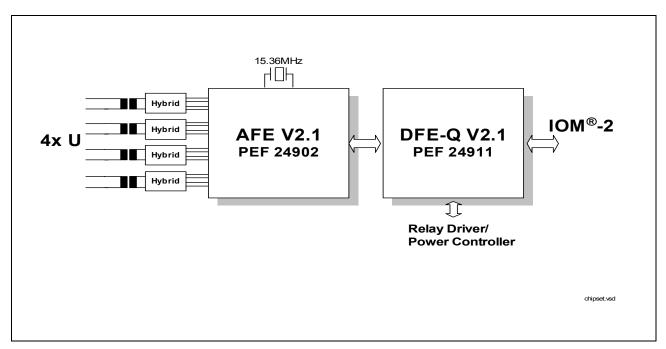

The Quad ISDN 2B1Q Echocanceller Digital Front End (DFE-Q) is the digital part of an optimized two-chip solution featuring 4x ISDN basic rate access and IDSL access at 144 kbit/s. The PEF 24911 is designed to provide in conjunction with the Quad ISDN Echocanceller Analog Front End (PEF 24902 V2.1) full duplex data transmission at the U-reference point according to ANSI T1.601 (1998), ETSI TS 102 080 (1998) and ITU-T G.961 standards.

The DFE-Q 2nd generation has been completely reengineered to guarantee the availability of the well proved DFE-Q/AFE solution over the year 2000. The PEF 24911 V2.1 is downwards pin compatible and functionally equivalent to the DFE-Q V1.x. Thus, line card manufacturers can make use of the most advanced process technology without the need to change their current design (besides the changeover to 3.3 V power supply).

No software changes are required if the DFE-Q V2.1 is deployed in existing DFE-Q V1.x solutions. Some new features are provided such as free programmable filtering options for the maintenance bits (M1-6) and enhanced monitoring and test functions. The data rate is programmable from 1 Mbit/s to 4 Mbit/s.

Figure 1 DFE-Q/ AFE 2nd Generation Chip Set

The output and input pins are throughout 5 V TTL compatible although the PEF 24911 is processed in advanced 3.3 V CMOS technology. A power down state with very low power consumption is featured.

The PEF 24911 comes in a P-MQFP-64 package.

# Quad ISDN 2B1Q Echocanceller Digital Front End DFE-Q V2.1

**PEF 24911**

### Version 2.1

### 1.1 Features

### **U-Interface**

- Digital part of a two-chip solution featuring full duplex data transmission and reception over two-wire metallic subscriber loops providing 4x ISDN basic rate access or IDSL access at 144 kbit/s

- · Conforms to:

- ANSI T1.601-1998

- ETSI TS 102 080 (1998)

- Recommendation ITU-T G.961

- 2B1Q-block code (2 binary, 1 quaternary) at 80-kHz symbol rate

- LT mode

- Data rate of the system interface programmable

- Activation/ deactivation controller

- 15 s start-up guard timer (T1) can be disabled for use in repeater applications

- Adaptive echo cancellation and equalization

- Automatic gain control and polarity adaptation

- Clock recovery (frame and bit synchronization) in all applications

- Built-in wake-up unit for activation from power-down state.

### **System Interface**

- IOM®-2 interface with programmable data rates (1 Mbit/s to 4 Mbit/s)

- SW controlled I/O ports for relay driver and power feeder control

- 4 relay driver pins per port

- 2 status pins per port

| Туре      | Package   |

|-----------|-----------|

| PEF 24911 | P-MQFP-64 |

### **Others**

- Software compatible to PEF 24911 V1.3 (Quad IEC DFE-Q)

- Inputs and outputs 5 V TTL compatible

- DOUT (open drain) accepts pull-up to 3.3 V or 5 V

- +3.3 V ±0.3 V Power Supply

- Advanced low power CMOS technology

- Extended temperature range (– 40...to 85 °C)

- Boundary-Scan, JTAG IEEE 1149.1

# Add-On Features and Differences with Respect to DFE-Q V1.3/V1.2/V1.1

- Max. IOM<sup>®</sup>-2 data rate 4 Mbit/s (DCL= 8 MHz)

- +3.3 V instead of +5 V power supply

- Dedicated pins for SSP and DT test modes

- DOUT configurable either as open drain or push-pull (tristate) output

- New MON-12 class features internal register access

- Coefficients retrievable by MON-12 commands instead of MON-8 commands

- Advanced filter options for MON-0 and MON-2 messages

- Bit Error Rate measurement per port

- Additional digital local loops

- C/I codes 'LTD' and 'HI' are no more supported

- Optimized LT-state machine

- JTAG Boundary-Scan with dedicated reset line TRST (replaces power-on reset functionality)

### **Addressed Applications**

- ISDN Line Cards for Central Office

- ISDN Line Cards for Access Networks

- ISDN Line Cards in PBX Systems

- IDSL Line Cards

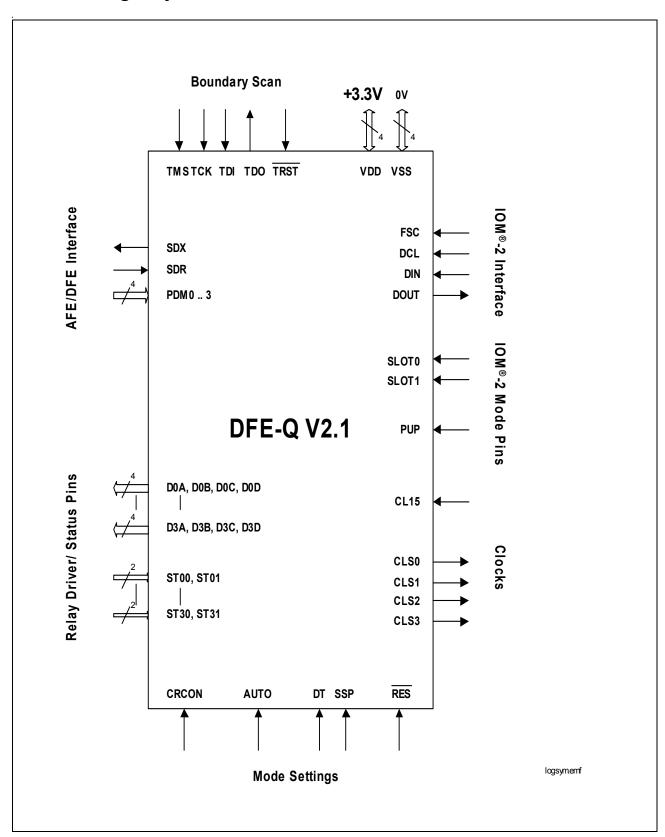

# 1.2 Logic Symbol

Figure 2 Logic Symbol

# 1.3 System Integration

This paragraph shows how the DFE-Q V2.1 may be integrated in systems using other Infineon ISDN devices. The PEF 24911 DFE-Q is optimized for use in the following applications:

- Digital Line Cards for Central Office

- Digital Line Cards for Access Networks (LT mode only)

- PBX applications (LT mode only)

Figure 3 and Figure 4 illustrate line card solutions with various Infineon line card controllers. The DELIC-PB (PEB 20571) supersedes the ELIC<sup>®</sup> (PEB 20550) and will feature up to 32 HDLC controllers on-chip. The DELIC controls up to 4 devices of DFE-Q V2.1 on a single IOM<sup>®</sup>-2 interface. In this application an additional clock doubler is necessary to generate the 8.192 MHz DCL clock for the DFE-Q derived from the 4.096 MHz BCL clock of the DELIC.

Figure 3 16-Line Card Application with DELIC Solution

Figure 4 16-Line Card Application with ELIC®/ IDEC® Solution

Figure 5 shows how an 8 channel line card application is realized by use of two AFE/DFE-Q chip sets:

One AFE-PLL generates the synchronized 15.36 MHz clock and provides the master clock at pin CL15 for the other 3 devices. The internal PLL of the first AFE synchronizes the 15.36 MHz master clock onto a PTT reference clock of either 8 kHz or 2048 kHz. Infineon recommends to feed the FSC clock input of the DFE-Q V2.1 and the PLL reference clock input (pin CLOCK) of the AFE from the same clock source.

The PLL of the second AFE is deactivated. The 15.36 MHz master clock is applied at pin CL15. CL15 is configured as input if XIN is clamped either to VDD or to VSS. Pin XOUT has to be left open and CLOCK shall be tied to GND.

Figure 5 Connecting Two AFE/DFE-Q Chip Sets

The DFE-Q devices are supplied by the first AFE at pin CL15 with the synchronized 15.36 MHz clock. The IOM<sup>®</sup>-2 channels the DFE-Q devices are assigned to can be programmed by the two slot pins. Starting from channel no. 0/4/8/12 always four subsequent channels are occupied.

Alternatively the clocking scheme as shown in **Figure 6** may be applied if more than 3 devices are to be clocked (e.g. in a 16-channel line card application). Instead to supply the 2nd AFE with the master clock at pin CL15, here the 15.36 MHz master clock is input at pin XIN. Thereby pin CL15 is configured as output and passes the 15.36 MHz clock on to the attached DFE-Q. If the clock chain is extended in the same way by another two AFE/DFE-Q chip sets a 16-channel line card application can be realized with just one single crystal. Note that the 15.36 MHz clock is inverted once by the AFE if it is input at XIN and output at CL15. This way the duty cycle is recovered again.

Figure 6 Recommended Clocking Scheme for More Than Two DFE-Q/AFE Chip Sets

# 1.4 Operational Overview

The DFE-Q V2.1 operates always in LT mode. Other operating modes known from former versions of the DFE-Q are not further supported.

# **System Interface Configurations**

The following parameters of the system interface are configurable:

- Open Drain/ Push-Pull Mode

Configured as open drain the output pin DOUT is floating and a pull-up resistor is required. In push-pull mode the output pin is high impedance outside the active time slots.

- IOM®-2 Channel Assignment

- IOM®-2 channels are always assigned in blocks of four.

| SLOT1 | SLOT0 | Assigned IOM <sup>®</sup> -2 Channels |

|-------|-------|---------------------------------------|

| 0     | 0     | 03                                    |

| 0     | 1     | 47                                    |

| 1     | 0     | 8 11                                  |

| 1     | 1     | 12 15                                 |

IOM<sup>®</sup>-2 Data Rates

| DCL Frequency [kHz] | Data Rate<br>[kBit/s] | IOM <sup>®</sup> -2 Channels |  |

|---------------------|-----------------------|------------------------------|--|

| 2048                | 1024                  | 4                            |  |

| 3072                | 1536                  | 6                            |  |

| 4096 2048           |                       | 8                            |  |

| 6144                | 3072                  | 12                           |  |

| 8192 4096           |                       | 16                           |  |

## **Send Single Pulses Test Mode**

In test mode 'Send Single Pulses' +/-3 pulses spaced by 1.5 ms are transmitted on all U lines. The test mode is activated by pin SSP= set to '1'. The SSP test function can be as well stimulated by C/I= SSP besides the fact that the HW selection impacts all line ports while the SW selection impacts only the chosen line.

# **Data Through Mode**

In test mode 'Data Through' the U-transceiver is forced to enter the 'Transparent' state and to issue SL3T (see **Table 12**) independently of the wake-up protocol. The DT test mode is activated by pin DT= set to '1'. The DT test function can be as well stimulated by C/I= DT besides the fact that the HW selection impacts all line ports while the SW selection impacts only the chosen line.

# 2 Pin Descriptions

# 2.1 Pin Diagram

(top view)

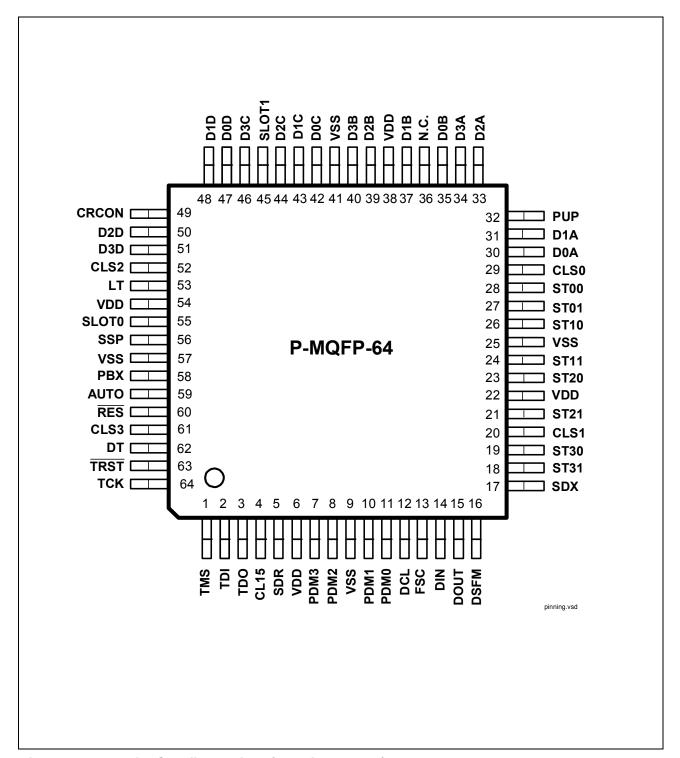

Figure 7 Pin Configuration (63 of 64 used)

# **Pin Descriptions**

### **Pin Definitions and Functions** 2.2

| Table 1 Pin Definitions and Functions |             |                         | nctions                                                                                                                                                                                                  |

|---------------------------------------|-------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.                               | Symbol      | Input (I)<br>Output (O) | Function                                                                                                                                                                                                 |

| IOM <sup>®</sup> -2 Int               | erface      |                         |                                                                                                                                                                                                          |

| 13                                    | FSC         | I                       | Frame Synchronization Clock (8kHz) the start of the first B1-channel in time-slot 0 is marked, FSC is expected to be '1' for at least two DCL periods.                                                   |

| 12                                    | DCL         | I                       | Data Clock<br>clock rate ranges from 2048 to 8192 kHz<br>(1024 to 4096 kBit/s)                                                                                                                           |

| 14                                    | DIN         | I                       | Data In input of IOM <sup>®</sup> -2 data synchronous to DCL clock                                                                                                                                       |

| 15                                    | DOUT        | O<br>(OD/<br>PuP)       | Data Out output of IOM®-2 data synchronous to DCL clock                                                                                                                                                  |

| Mode Sele                             | ection Pins |                         |                                                                                                                                                                                                          |

| 60                                    | RES         |                         | Reset triggers asynchronous HW reset, Schmitt trigger input '1'= inactive '0'= active                                                                                                                    |

| 55                                    | SLOT0       |                         | IOM®-2 Channel Slot Selection 0 assigns IOM®-2 channels in blocks of 4  SLOT1, 0: '00'= IOM®-2 channels 0 to 3 '01'= IOM®-2 channels 4 to 7 '10'= IOM®-2 channels 8 to 11 '11'= IOM®-2 channels 12 to 15 |

| 45                                    | SLOT1       | I<br>(PD)               | IOM®-2 Channel Slot Selection 1<br>assigns IOM®-2 channels in blocks of 4                                                                                                                                |

Table 1

Pin Definitions and Functions (cont'd)

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|--------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16      | DSFM   | I<br>(PD)               | Disable Super Frame Marker '1' = Inhibits the evaluation of the super frame marker on FSC. I.e the transmitted super- frame is not affected by an FSC pulse shorter than 2 DCL clock periods. '0' = The position of the transmitted superframe is synchronized to short FSC pulses.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 32      | PUP    | I<br>(PD)               | Push Pull Mode in push pull mode '0' and '1' is actively driven during an occupied time slot, outside the active time slots DOUT is high impedance (tristate) '1'= configures DOUT as push/pull output '0'= configures DOUT as open drain output                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 49      | CRCON  | I<br>(PD)               | CRC Check On/Off defines the condition on which MON-2 messages and M4 bit will be passed on, the setting has effect on all ports (see Table 7). Pin CRCON is evaluated only after hardware reset. '1'= CRC Check On MON-2 messages are not issued and M4-bit are not forwarded to the statemachine if the CRC-check of the U-superframe containing M4-bit changes is not ok. (MFILT= 0011 0xxx) '0'= CRC Check Off MON-2 messages are issued every time a change in at least one of the overhead bits (M4,5,6) of the U-interface is detected, regardless of the CRC checksum status. M4-bit are forwarded to the statemachine with triple-last-look filtering (TLL). (MFILT= 0000 0xxx) |

| 53      | LT     | I                       | reserved, clamp to high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Table 1

Pin Definitions and Functions (cont'd)

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                      |

|---------|--------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 58      | PBX    | 1                       | reserved, clamp to low                                                                                                                                                                                                                                                                                                                                                        |

| 59      | AUTO   | I                       | EOC Auto Mode selects auto or transparent mode for EOC channel processing, the setting has effect on all ports '1'= EOC auto mode (MFILT= xxxx x100) '0'= EOC transparent mode (MFILT= xxxx x001)                                                                                                                                                                             |

| 56      | SSP    | I                       | Send Single Pulses (SSP) Test Mode '1'= alternating +/-3 pulses are issued at all line ports in 1.5 ms intervals '0'= deactivated, clamp to GND if not used This pin function corresponds to the SW selection by C/I= SSP besides the fact that the HW selection impacts all line ports while the SW selection impacts only the chosen line                                   |

| 62      | DT     |                         | Data Through (DT) Test Mode enables/disables DT test mode '1'= DT test mode enabled, the U-transceiver is forced on all line ports to enter the 'Transparent' state '0'= DT test mode disabled This pin function corresponds to the SW selection by C/I= DT besides the fact that the HW selection impacts all line ports while the SW selection impacts only the chosen line |

# Interface to the Analog Front End

| 4  | CL15 | I | 15.36 MHz Master Clock Input                                                                                                                                                        |

|----|------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11 | PDM0 |   | Pulse Density Modulated Receive Data of Line<br>Port 0<br>pulse density modulated bit stream from the<br>PEF 24902 Quad AFE that is output from the<br>second-order sigma-delta ADC |

Table 1

Pin Definitions and Functions (cont'd)

| Pin No. | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                 |

|---------|--------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10      | PDM1   | I                       | Pulse Density Modulated Receive Data of Line<br>Port 1<br>pulse density modulated bit stream from the<br>PEF 24902 Quad AFE that is output from the<br>second-order sigma-delta ADC                                                                                                                                                      |

| 8       | PDM2   | I                       | Pulse Density Modulated Receive Data of Line<br>Port 2<br>pulse density modulated bit stream from the<br>PEF 24902 Quad AFE that is output from the<br>second-order sigma-delta ADC                                                                                                                                                      |

| 7       | PDM3   | I                       | Pulse Density Modulated Receive Data of Line<br>Port 3<br>pulse density modulated bit stream from the<br>PEF 24902 Quad AFE that is output from the<br>second-order sigma-delta ADC                                                                                                                                                      |

| 5       | SDR    | I                       | Serial Data Receive Line interface signal from the PEF 24902 Quad AFE that transports level detect information for the wake-up recognition of all 4 lines by use of TDM                                                                                                                                                                  |

| 17      | SDX    | 0                       | Serial Data Transmit Line interface to the PEF 24902 Quad AFE for the transmit and control data. Transmission is based on clock CL15 (15.36 Mbit/s). For each line port the following bits are exchanged: TD0, TD1: Transmit data RANGE: Range select LOOP: Analog loopback switch PDOW: Power down/power up Synchronization information |