# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **Universal Active ORing Controller IC**

# Description

The PI2001 *Cool-ORing*<sup>™</sup> solution is a universal high-speed Active ORing controller IC designed for use with N-channel MOSFETs in redundant power system architectures. The PI2001 *Cool-ORing* controller enables an extremely low power loss solution with fast dynamic response to fault conditions, critical for high availability systems. The PI2001 controls single or parallel MOSFETs to address Active ORing applications protecting against power source failures. The PI2001 can be used in either high-side or low-side Active ORing applications and a master/slave feature allows the paralleling of IC/MOSFET chipsets for high current Active ORing.

The gate drive output turns the MOSFET on in normal steady state operation, while achieving highspeed turn-off during input power source fault conditions, that cause reverse current flow, with auto-reset once the fault clears. The MOSFET drain-to-source voltage is monitored to detect normal forward, excessive forward, light load and reverse current flow. The PI2001 provides an active low fault flag output to the system during excessive forward current, reverse current, light load, overvoltage, under-voltage and over-temperature fault conditions. There is an internal shunt regulator at the VC input for high voltage applications and the under-voltage and over-voltage thresholds are programmable via external resistor dividers.

### Features

- Fast Dynamic Response to Power Source failures, with 160ns reverse current turn-off delay time

- 4A gate discharge current

- Accurate MOSFET drain-to-source voltage sensing to indicate system level fault conditions

- Programmable under & over-voltage detection

- Over temperature fault detection

- Adjustable reverse current blanking timer

- 100V for 100ms operation in low side applications

- Master/Slave I/O for paralleling (TDFN only)

- Active low fault flag output

# **Applications**

- N+1 Redundant Power Systems

- Servers & High End Computing

- Telecom Systems

- Low & High-side Active ORing

- High current Active ORing

# **Package Information**

The PI2001 is offered in the following packages:

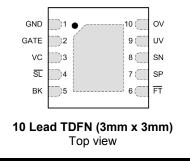

- 10 Lead 3mm x 3mm TDFN package

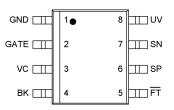

- 8 Lead SOIC package

# Typical Applications:

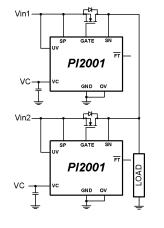

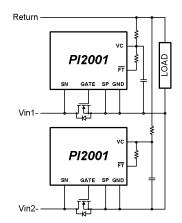

Figure 1a: PI2001 High Side Active ORing

Figure 1b: Pl2001 Low Side Active ORing

### Pin Description

| Pin                                                               | Pin Nu                                                                                                                                                                                                                                             | umber          |                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Name                                                              | 10 Lead<br>TDFN                                                                                                                                                                                                                                    | 8 Lead<br>SOIC | Description                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| GND                                                               | 1                                                                                                                                                                                                                                                  | 1              | Ground: This pin is ground for the gate driver and control circuitry.                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| GATE                                                              | 2                                                                                                                                                                                                                                                  | 2              | <b>Gate Drive Output:</b> This pin drives the gate of the external N-channel MOSFET.<br>Under normal operating conditions, the GATE pin pulls high to 9.5V (typ) with respect<br>to the SP pin. The controller turns the gate off during a reverse current fault that<br>exceeds the reverse voltage threshold.                                                                            |  |  |  |  |  |

| VC                                                                | 3                                                                                                                                                                                                                                                  | 3              | <b>Controller Input Supply:</b> This pin is the supply pin for the control circuitry and gate driver. Connect a 1µF capacitor between VC pin and the GND pin. Voltage on this pin is limited to 15.5V by an internal shunt regulator. For high voltage auxiliary supply applications connect a shunt resistor between VC and the auxiliary supply.                                         |  |  |  |  |  |

| SL                                                                | 4                                                                                                                                                                                                                                                  | n/a            | <b>Slave Input-Output:</b> This pin is used for paralleling multiple PI2001 solutions in high power applications. When the PI2001 is configured as the Master, this pin functions as an output capable of driving up to $10 \ \overline{SL}$ pins of slaved PI2001 devices. It serves as an input when the PI2001 is configured in slave mode.                                             |  |  |  |  |  |

| BK                                                                | 5                                                                                                                                                                                                                                                  | 4              | <b>Blanking Timer Input-Output:</b> Connect a resistor from BK to GND to set the blanking time for the Reverse Comparator function. To configure the controller in slave mode, connect BK to VC. To configure the controller in master mode with the fastest turn-off response, connect BK directly to GND.                                                                                |  |  |  |  |  |

| $\overline{FT}$                                                   | FT65inputs are VC Under-Voltage<br>Current, light load, reverse                                                                                                                                                                                    |                | <b>Fault State Output:</b> This open collector pin pulls low when a fault occurs. Fault logic inputs are VC Under-Voltage, Input Under-Voltage, Input Over-Voltage, Forward Over-Current, light load, reverse current, and Over-Temperature. Leave this pin open if unused.                                                                                                                |  |  |  |  |  |

| SP                                                                | 7                                                                                                                                                                                                                                                  | 6              | <b>Positive Sense Input &amp; Clamp:</b> Connect SP pin to the Source pin of the external N-<br>channel MOSFET. The polarity of the voltage difference between SP and SN provides<br>an indication of current flow direction through the MOSFET.                                                                                                                                           |  |  |  |  |  |

| SN                                                                | SN 8 7 Negative Sense Input & Clamp: Connect SN to the Drai channel MOSFET. The polarity of the voltage difference an indication of current flow direction through the MOSFE   UV 9 8 Provide the sense of the |                | <b>Negative Sense Input &amp; Clamp:</b> Connect SN to the Drain pin of the external N-<br>channel MOSFET. The polarity of the voltage difference between SP and SN provides<br>an indication of current flow direction through the MOSFET.                                                                                                                                                |  |  |  |  |  |

| UV                                                                |                                                                                                                                                                                                                                                    |                |                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| OV10Input Over-<br>condition in<br>threshold, the<br>threshold is |                                                                                                                                                                                                                                                    | n/a            | <b>Input Over-Voltage Input:</b> The OV pin is used to detect an input source over-voltage condition in ground referenced applications. When the OV pin voltage crosses the OV threshold, the $\overline{FT}$ pin pulls low indicating a fault condition. The input voltage OV threshold is programmable through an external resistor divider. Connect OV to GND to disable this function. |  |  |  |  |  |

# Package Pin-Outs

8 Lead SOIC (5mm x 6mm) Top view

# **Absolute Maximum Ratings**

| -0.3V to 17.3V / 40mA                           |

|-------------------------------------------------|

| -0.3V to 8.0V / 10mA                            |

| -0.3V to 17.3V / 10mA                           |

| -0.3V to 17.3V / 5A                             |

| -0.3V to 80V / 10mA                             |

| 100V / 10mA                                     |

| -0.3V / 5A peak                                 |

| -65°C to 150°C                                  |

| -40°C to Over Temperature Fault (T $_{\rm FT})$ |

| 250°C                                           |

| 2kV HBM                                         |

|                                                 |

# **Electrical Specifications**

Unless otherwise specified: -40°C < T\_J < 125°C, VC =12V,  $C_{Vc}$  = 1uF,  $C_{GATE}$  = 4nF,  $C_{SL}$  = 10pF

| Parameter                             | Symbol               | Min | Тур  | Мах  | Units | Conditions                               |

|---------------------------------------|----------------------|-----|------|------|-------|------------------------------------------|

| VC Supply                             |                      |     | •    |      | •     |                                          |

| Operating Supply Range <sup>(3)</sup> | V <sub>VC-GND</sub>  | 4.5 |      | 13.2 | V     | No VC limiting Resistors                 |

| Quiescent Current                     | I <sub>VC</sub>      |     | 3.7  | 4.2  | mA    | Normal Operating Condition,<br>No Faults |

| VC Clamp Voltage                      | V <sub>VC-CLM</sub>  | 15  | 15.5 | 16   | V     | I <sub>VC</sub> =10mA                    |

| VC Clamp Shunt Resistance             | R <sub>VC</sub>      |     |      | 7.5  | Ω     | Delta I <sub>vc</sub> =10mA              |

| VC Under-Voltage Rising Threshold     | V <sub>VCUVR</sub>   |     | 4.3  | 4.5  | V     |                                          |

| VC Under-Voltage Falling Threshold    | V <sub>VCUVF</sub>   | 4.0 | 4.15 |      | V     |                                          |

| VC Under-Voltage Hysteresis           | V <sub>VCUV-HS</sub> |     | 150  |      | mV    |                                          |

| FAULT                                 |                      |     |      |      |       |                                          |

| Under-Voltage Rising Threshold        | V <sub>UVR</sub>     |     | 500  | 540  | mV    |                                          |

| Under-Voltage Falling Threshold       | V <sub>UVF</sub>     | 440 | 475  |      | mV    |                                          |

| Under-Voltage Threshold Hysteresis    | V <sub>UV-HS</sub>   |     | 25   |      | mV    |                                          |

| Under-Voltage Bias Current            | I <sub>UV</sub>      | -1  |      | 1    | μA    |                                          |

| Over-Voltage Rising Threshold         | V <sub>OVR</sub>     |     | 500  | 540  | mV    |                                          |

| Over-Voltage Falling Threshold        | V <sub>OVF</sub>     | 440 | 475  |      | mV    |                                          |

| Over-Voltage Threshold Hysteresis     | V <sub>OV-HS</sub>   |     | 25   |      | mV    |                                          |

| Over-Voltage Bias Current             | I <sub>OV</sub>      | -1  |      | 1    | μA    |                                          |

| Fault Output Low Voltage              | V <sub>FTL</sub>     |     | 0.2  | 0.5  | V     | I <sub>FT</sub> =2mA, VC>3.5V            |

| Fault Output High Leakage Current     | I <sub>FT-LC</sub>   |     |      | 10   | μA    | V <sub>FT</sub> =14V                     |

| Fault Delay Time                      | t <sub>FT-DEL</sub>  | 20  | 40   | 60   | μs    | Includes output glitch filter            |

**Electrical Specifications** Unless otherwise specified: -40°C < T<sub>J</sub> < 125°C, VC =12V, C<sub>Vc</sub> = 1uF, C<sub>GATE</sub> = 4nF, C<sub>SL</sub> = 10pF

| Parameter                                        | Symbol              | Min         | Тур          | Мах  | Units | Conditions                                                                            |

|--------------------------------------------------|---------------------|-------------|--------------|------|-------|---------------------------------------------------------------------------------------|

| FAULT (Continued)                                |                     |             |              |      |       |                                                                                       |

| Over Temperature Fault <sup>(1)</sup>            | T <sub>FT</sub>     |             | 160          |      | °C    |                                                                                       |

| Over Temperature Fault Hysteresis <sup>(1)</sup> | T <sub>FT-HS</sub>  |             | -10          |      | °C    |                                                                                       |

| DIFFERENTIAL AMPLIFIER AND CO                    | MPARATO             | ORS         |              |      | •     |                                                                                       |

| Common Mode Input Voltage                        | V <sub>CM</sub>     | -0.1        |              | 5.5  | V     | SP to GND & SN to GND                                                                 |

| Differential Operating Input Voltage             | V <sub>SP-SN</sub>  | -50         |              | 125  | mV    | SP-SN                                                                                 |

| SP Input Bias Current                            | I <sub>SP</sub>     | -50         | -37          |      | μA    | SP=SN=1.25V                                                                           |

| SN Input Bias Current                            | I <sub>SN</sub>     |             | 3.5          | 8    | μA    | SP=SN=1.25V                                                                           |

| SN Voltage                                       | V <sub>SN</sub>     |             |              | 80   | V     | $I_{SN} \le 7mA, SP=0V, I_{VC} = 10mA$                                                |

| Reverse Comparator Off Threshold                 | V <sub>RVS-TH</sub> | -10         | -6           | -2   | mV    | V <sub>CM</sub> = 3.3V                                                                |

| Reverse Comparator Hysteresis                    | V <sub>RVS-HS</sub> | 2           |              | 5    | mV    | V <sub>CM</sub> = 3.3V                                                                |

| Reverse Fault to Gate Turn-off<br>Delay Time     | t <sub>RVS-MS</sub> |             | 160          | 220  | ns    | $V_{SP-SN}$ = ± 50mV step to 90% of $V_{G}$ max, $V_{BK}$ =0 (minimum blanking)       |

| Reverse Fault to Gate Turn-off<br>Delay Time     | t <sub>RVS-SL</sub> |             | 430          | 600  | ns    | $V_{SP-SN} = \pm 50mV$ step to 90% of $V_G$ max, $V_{BK} = V_{VC}$ (maximum blanking) |

| Forward Comparator On Threshold                  | $V_{\text{FWD-TH}}$ | 2           | 6            | 9    | mV    | V <sub>CM</sub> = 3.3V                                                                |

| Forward Comparator Hysteresis                    | $V_{FWD-HS}$        | -5          |              | -2   | mV    | V <sub>CM</sub> = 3.3V                                                                |

| Forward Over-Current Comparator<br>Threshold     | V <sub>OC-TH</sub>  | 60          | 66           | 70   | mV    | V <sub>CM</sub> = 3.3V                                                                |

| Forward Over-Current Comparator<br>Hysteresis    | $V_{\text{OC-HS}}$  | -8          |              | -4   | mV    | V <sub>CM</sub> = 3.3V                                                                |

| GATE DRIVER                                      |                     |             |              |      |       |                                                                                       |

| Gate Source Current                              | I <sub>G-SC</sub>   |             | -1.0         | -0.4 | mA    | V <sub>G</sub> = 1V, Normal Operating<br>Conditions, No Faults                        |

| Pull Down Peak Current <sup>(1)</sup>            | I <sub>G-PD</sub>   | 1.5         | 4.0          |      | A     |                                                                                       |

| Pull-down Gate Resistance <sup>(1)</sup>         | R <sub>G-PD</sub>   |             | 0.3          |      | Ω     | V <sub>G</sub> = 1.5V @ 25°C                                                          |

| AC Gate Pull-down Voltage <sup>(1)</sup>         | $V_{G-PD}$          |             |              | 0.2  | V     |                                                                                       |

| DC Gate Pull-down Voltage to SP(1)               | $V_{G-PD}$          |             | 1.1          |      | V     | I <sub>G</sub> =100mA, in reverse fault                                               |

| Gate Voltage @ VC UVLO                           | $V_{G-UVLO}$        |             | 0.7          | 1    | V     | I <sub>G</sub> =10μA,1.5V <vc<3.5v< td=""></vc<3.5v<>                                 |

| Gate to SP Clamp Voltage                         | $V_{G-CLMP}$        | 8.5         | 9.5          | 10.5 | V     | Ι <sub>G</sub> = 100μΑ                                                                |

| Gate Voltage High                                | V <sub>G</sub>      | VC-<br>0.5V | VC-<br>0.25V |      | V     | VC- V <sub>SP</sub> < V <sub>G-CLMP</sub>                                             |

| Gate Fault Condition Clear <sup>(1)</sup>        | $V_{G-CL}$          |             | 77           |      | %     |                                                                                       |

| Gate Fall Time                                   | t <sub>G-F</sub>    |             | 10           | 15   | ns    | 90% to 10% of $V_{G}$ max.                                                            |

#### **Electrical Specifications**

Unless otherwise specified:  $-40^{\circ}C < T_J < 125^{\circ}C$ , VC =12V,  $C_{Vc}$  = 1uF,  $C_{GATE} = 4nF$ ,  $C_{SL} = 10pF$

| Parameter                                                                     | Symbol             | Min | Тур  | Max | Units | Conditions                                                                    |

|-------------------------------------------------------------------------------|--------------------|-----|------|-----|-------|-------------------------------------------------------------------------------|

| SLAVE                                                                         |                    |     |      |     |       |                                                                               |

| Slave Source Current                                                          | I <sub>SL</sub>    |     | -60  | -25 | μA    | V <sub>SL</sub> = 1V, Normal Operating<br>Conditions, No Faults               |

| Slave Output Voltage High                                                     | $V_{\text{SL-Hi}}$ |     | 4.3  | 5.5 | V     | Normal Operating Conditions,<br>No Faults                                     |

| Slave Output Voltage Low                                                      | $V_{\text{SL-Lo}}$ |     | 0.2  | 0.5 | V     | I <sub>SL</sub> =4mA                                                          |

| Slave Hold-off Voltage at VC UVLO                                             | $V_{\text{SL-UV}}$ |     | 0.7  | 1   | V     | I <sub>SL</sub> =5µA,1.5V <vc<3.5v< td=""></vc<3.5v<>                         |

| Slave Threshold                                                               | V <sub>SL-TH</sub> |     | 1.75 | 2   | V     |                                                                               |

| Slave Fall Time                                                               | t <sub>SL-FL</sub> |     | 15   | 25  | ns    | 90% to 50% of $V_{SL}$ max $V_{BK}$ =0                                        |

| Slave to Gate Delay Time<br>After Reverse Current Fault<br><i>Master Mode</i> | t <sub>sL-G</sub>  |     | 20   | 30  | ns    | 50%<br>of V <sub>SL</sub> to 90% of V <sub>G</sub> max;<br>V <sub>BK</sub> =0 |

| Slave to Gate Delay Time<br><i>Slave Mode</i>                                 | t <sub>SL-G</sub>  |     | 100  | 130 | ns    | 50% of $V_{SL}$ to 90% of $V_{G}$ max; $V_{BK}$ =VC                           |

| BLANK                                                                         |                    |     |      |     |       |                                                                               |

| Blank Source Current                                                          | I <sub>ВК</sub>    | -60 | -45  | -30 | μA    | V <sub>BK</sub> =0V                                                           |

| Blank Output Voltage                                                          | V <sub>BK</sub>    |     | 0.77 | 0.9 | V     | I <sub>BK</sub> =5µA Connected to GND                                         |

| Blank Slave Mode Threshold                                                    | V <sub>BK-TH</sub> | 1.2 | 1.45 | 1.7 | V     |                                                                               |

**Note 1**: These parameters are not production tested but are guaranteed by design, characterization and correlation with statistical process control.

**Note 2:** Current sourced by a pin is reported with a negative sign.

**Note 3:** Refer to the *Auxiliary Power Supply* section in the *Application Information* for details on the VC requirement to meet the MOSFET Vgs requirement.

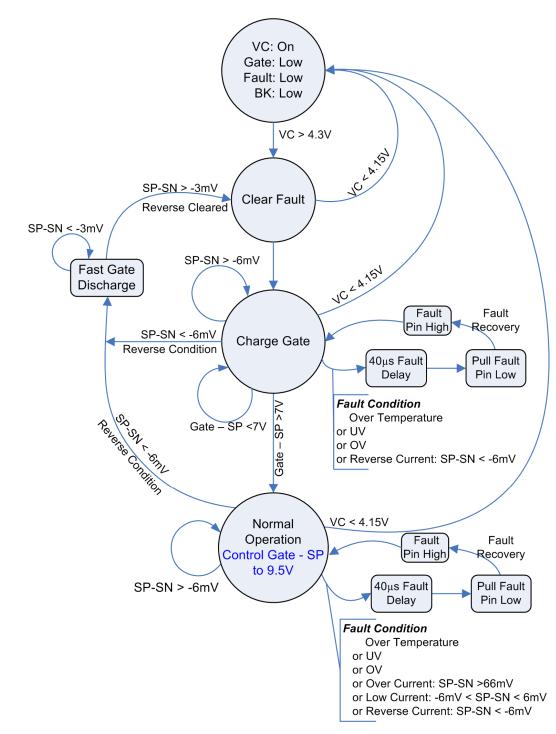

### Functional Description:

The PI2001 *Cool-ORing* controller IC is designed to drive single or paralleled N-channel MOSFETs in Active ORing applications. The PI2001 used with an external MOSFET can function as an ideal ORing diode in the high or low side of a redundant power system, significantly reducing power dissipation and eliminating the need for heatsinking.

An N-channel MOSFET in the conduction path offers extremely low on-resistance resulting in a dramatic reduction of power dissipation versus the performance of a diode used in conventional ORing applications due to its high forward voltage drop. This can allow for the elimination of complex heat other thermal management sinking and requirements. Due to the inherent characteristics of the MOSFET, while the gate remains enhanced above the gate threshold voltage it will allow current to flow in the forward and reverse direction. Ideal ORing applications do not allow for reverse current flow, so the controller has to be capable of very fast and accurate detection of reverse current caused by input power source failures, and turn off the gate of the MOSFET as guickly as possible. Once the gate voltage falls below the gate threshold, the MOSFET is off and the body diode will be reverse biased preventing reverse current flow and subsequent excessive voltage droop on the redundant bus. During forward over-current conditions caused by load faults, the controller maintains gate drive to the MOSFET to keep power dissipation as low as possible, otherwise the inherent body diode of the MOSFET would conduct, which has higher effective forward drop. Conventional ORing solutions using diodes offer no protection against forward overcurrent conditions. During the forward over-current condition, the PI2001 will provide an active-low fault flag to the system via the  $\overline{FT}$  pin. The fault flag is also issued during the reverse current condition, light load conditions, VC Under-Voltage, Input Under-Voltage and Over-Voltage and Over-Temperature conditions.

#### **Differential Amplifier:**

The PI2001 integrates a high-speed low offset voltage differential amplifier to sense the difference between the Sense Positive (SP) pin voltage and Sense Negative (SN) pin voltage with high accuracy. The amplifier output is connected to three comparators: Reverse comparator, Forward comparator, and Forward over-current comparator.

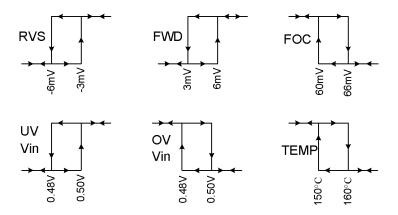

#### **Reverse Comparator: RVS**

The reverse comparator is the most critical comparator. It looks for negative voltage caused by

reverse current. When the SN pin is 6mV higher than the SP pin, the reverse comparator will enable the BK current source to charge an internal 2pF capacitor. The blanking timer provides noise filtering for typical switching power conversion that might cause premature reverse current detection. Once the voltage across the capacitor reaches the timer threshold voltage (1.25V) the gate will be discharged by a 4Apk current. The shortest blanking time is 50ns when BK is connected to ground. The Blanking time programmed by the BK pin will be added to the controller delay time. The Electrical Specifications in the DIFFERENTIAL AMPLIFIER AND COMPARATOR section for Reverse Fault to Slave Low Delay Time "t<sub>RVS-MS</sub> or t<sub>RVS-SL</sub>" is the controller delay time plus the blanking time.

#### **Reverse Blanking Timer: BK**

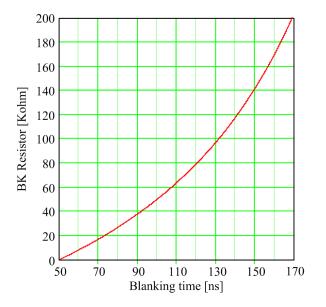

Connecting an external resistor ( $R_{BK}$ ) between the BK pin and ground will increase the blanking time as shown in Figure 2.

Where:

$$R_{RK} \leq 200 K \Omega$$

If BK is connected to VC for slave mode operation, then the blanking time will be about 320ns typically, and total delay time will be 430ns.

The reverse comparator has 3mV of hysteresis referenced to SP-SN.

If the conditions are met for a reverse current fault, then the active-low fault flag output will also indicate a fault to the system after the  $40\mu$ s fault delay time.

Figure 2: Blanking time vs. BK resistor value

#### Forward Voltage Comparator: FWD

The FWD comparator detects when a forward current condition exists and SP is 6mV(typical) positive with respect to SN. When SP-SN is less than 6mV, the FWD comparator will assert the Fault flag to report a fault condition indicative of a light load or "load not present" condition or possible shorted MOSFET.

#### Forward Over Current Comparator: FOC

The FOC comparator indicates an excessive forward current condition when SP is 66mV(typical) higher than SN. When the GATE output voltage is greater than 77% of the regulated gate voltage and SP-SN is higher than 66mV, the PI2001 will initiate a fault condition via the  $\overline{FT}$  pin.

#### Slave:

In high current applications multiple parallel MOSFETs may be needed for a single ORing function. Driving multiple MOSFETs with one controller will increase the loading on the GATE pin and the gate connection parasitic thereby impacting the reverse turn-off response.

The Slave function synchronizes multiple controllers so that one, or more, of the paralleled MOSFETs will have its own local driving source. In this configuration, one controller will be designated as the master and it will control the response of the slaved controllers.

When the controller is configured in "Master Mode", by connecting the BK to ground, the  $\overline{SL}$  will be an output having the same signal characteristics as the GATE signal. In this configuration, the  $\overline{SL}$  output is capable of driving up to ten controllers, configured in "Slave Mode", through their corresponding  $\overline{SL}$  pins. Logic high for the  $\overline{SL}$  pin is limited to 5.5V (max).

When the BK pin is tied to VC, the controller is configured in "Slave Mode" and the  $\overline{SL}$  pin becomes an input. The Gate driver section and reverse current section are the only active circuits in the slave controller while the master performs the diagnostics and gate drive control.

#### VC and Internal Voltage Regulator:

The PI2001 has a separate input (VC) that provides power to the control circuitry and the gate driver. An internal regulator clamps the VC voltage to 15.5V.

For high side applications, the VC input should be high enough above the bus voltage to properly enhance the external N-channel MOSFET. In a low side drive application VC may be tied to the bus voltage through a resistor.

The internal regulator circuit has a comparator to monitor VC voltage and initiates a FAULT condition when VC is lower than the VC Under-Voltage Threshold.

#### UV:

The Under-Voltage (UV) input trip point can be programmed through an external resistor divider to monitor the input voltage. The UV comparator initiates a fault condition and pulls the  $\overline{FT}$  pin low when UV falls below the Under-Voltage Falling Threshold. The GATE pin does not respond to a UV fault. If the PI2001 is configured in a floating application, where the GND pin is connected to the input voltage, the UV pin cannot detect the input voltage. In this case, the UV pin should be disabled by connecting it to the VC pin.

#### OV:

The Over Voltage (OV) input trip point can be programmed through an external resistor divider to monitor the input voltage. The OV comparator initiates a fault condition and pulls the  $\overline{FT}$  pin low when OV rises above the Over-Voltage Rising Threshold. The GATE pin does not respond to an OV fault. If the PI2001 is configured in a floating application, where the GND pin is connected to the input voltage, the OV pin cannot detect the input voltage. In this case, the OV pin should be disabled by connecting it to the GND pin.

#### **Over-Temperature Detection:**

The internal Over-Temperature block monitors the junction temperature of the controller. The Over-Temperature threshold is set to 160°C with -10°C of hysteresis. When the controller temperature exceeds this threshold, the Over-Temperature circuit

initiates a fault condition and pulls the FT pin low. By maintaining proper thermal matching between the controller and the power MOSFET, this function can be used to protect the ORing device from thermal runaway conditions. The GATE pin does not respond to an Over-Temperature fault.

#### Gate Driver:

The gate driver (GATE) output is configured to drive an external N-channel MOSFET. In the high state, the gate driver applies a 1mA current source to the MOSFET gate and regulates the voltage to 9.5V typical ( $V_{G-CLMP}$ ) above the SP pin voltage ( $V_{SP}$ ) when the VC input voltage is higher than  $V_{SP}$  plus  $V_{G-CLMP}$ . Otherwise the gate voltage ( $V_G$ ) to  $V_{SP}$  will

Picor Corporation • picorpower.com

be { $V_{G-SP}$  = VC -  $V_{SP}$  – 0.5V}. Note that VC is the controller internal regulated voltage.

When a reverse current fault is initiated, the gate driver pulls the GATE pin low and discharges the FET gate with 4Apeak capability.

When the input source voltage is applied and before the MOSFET is fully enhanced, a voltage greater than the Forward Over Current (FOC) Threshold will be present across the MOSFET. To avoid an erroneous FOC detection, a VGS detector blanks the FOC and FWD comparators from initiating a fault, until the GATE pin reaches 77% of  $V_{G-CLMP}$ . If VC is too low to establish the Gate Clamp condition the reference for detection is 77% of {VC-V(SP) - 0.25V}.

#### Fault:

The fault circuit output is an open collector with 40µs delay to prevent any false triggering. The  $\overline{FT}$  pin

will be pulled low when any of the following faults occur:

- Reverse current

- Forward Over-Current

- Forward Low Current

- Over-Temperature

- Input Under-Voltage

- Input Over-Voltage

- VC pin Under-Voltage

The only fault condition that initiates gate turn-off of the MOSFET (as well as a fault flag signal) is when the reverse current fault conditions are met. All other fault conditions issue only a fault flag signal via the

$\overline{FT}$  pin, but do not affect the gate of the MOSFET. The  $\overline{FT}$  pin serves as an indicator that a fault condition may be present. This information can be reported to a Host to signal that some system level maintenance may be required.

Figure 3: PI2001 Controller Internal Block Diagram (10 Lead TDFN package pin out shown)

Figure 4: Comparator hysteresis, values are for reference only, please refer to the electrical specifications

**Figure 5:** PI2001 State Diagram (Configured in Master Mode)

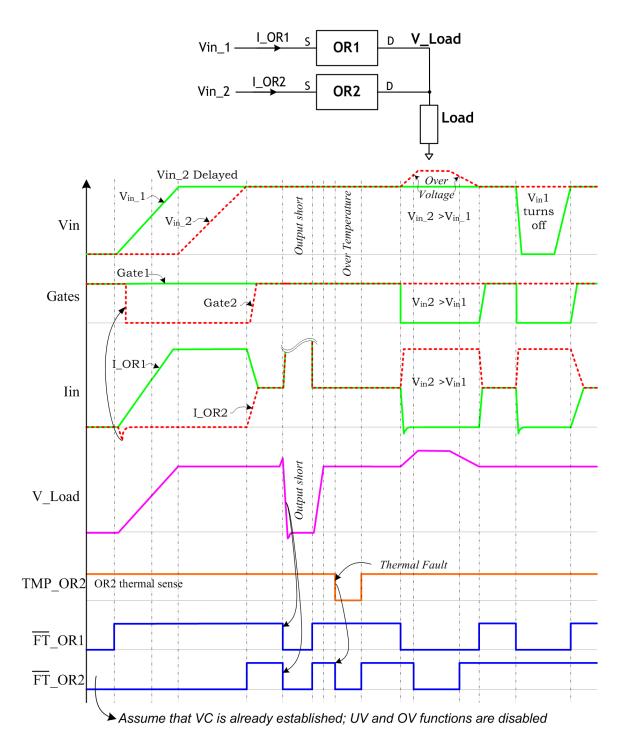

Figure 6: Timing diagram for two PI2001 controllers in an Active ORing application

## **Typical Characteristics:**

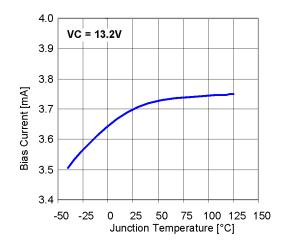

Figure 7: Controller bias current vs. temperature

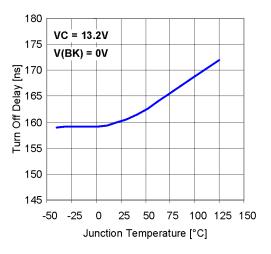

Figure 9: Reverse condition gate turn-off delay time vs. temperature.

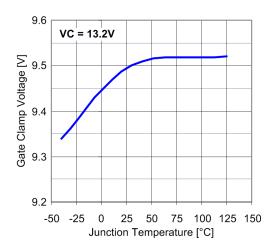

Figure 11: Gate to SP clamp voltage vs. temperature.

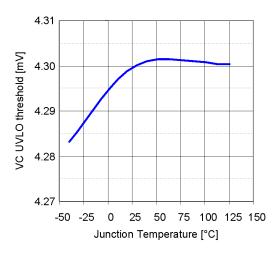

Figure 8: VC UVLO threshold vs. temperature

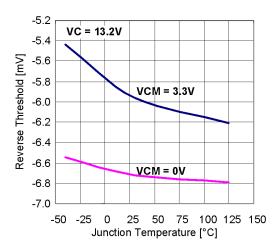

Figure 10: Reverse comparator threshold vs. temperature. VCM: Common Mode Voltage.

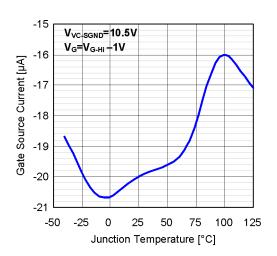

Figure 12: Gate source current vs. temperature

### **Application Information:**

The Pl2001 is designed to replace ORing diodes in high current redundant power architectures. Replacing a traditional diode with a Pl2001 controller IC and a low on-state resistance N-channel MOSFET will result in significant power dissipation reduction as well as board space reduction, efficiency improvement and additional protection features. This section describes in detail the procedure to follow when designing with the Pl2001 Active ORing controller and N-Channel MOSFETs. Three different Active ORing design examples are presented.

#### Fault Indication:

$\overline{FT}$  output pin is an open collector and should be pulled up to the logic voltage or to the controller VC via a resistor (10K $\Omega$ )

#### Blanking Timer:

Connect the blanking timer pin (BK) to GND to program the device for the fastest reverse comparator response time of 160ns typical. To increase the blanking time, connect the BK pin to GND via a resistor to avoid the fault response to short reverse current pulses. Refer to Figure 2 in the reverse comparator functional description for resistor values versus the reverse blanking time.

#### Auxiliary Power Supply (Vaux):

Vaux is an independent power source required to supply power to the PI2001 VC input. The Vaux voltage should be higher than Vin (redundant power source output voltage) by the required gate-to-source voltage (Vgs) to fully enhance the MOSFET, plus 0.5V maximum gate to VC headroom (VHD<sub>VC-G</sub>)

Vaux = Vin + Vgs + VHD<sub>VC-G</sub>

Where,  $VHD_{VC-G}$  is defined as the 0.5V maximum drop from VC in the *Gate Voltage High* (V<sub>G</sub>) specification in the Gate Driver section of the Electrical Specification.

For example, if the bus voltage is 3.3V and the MOSFET requires 5.0V of Vgs to fully enhance the MOSFET, then Vaux should be at least 3.3V + 5.0V + 0.5V = 8.8V.

If Vaux is higher than 15V then a bias resistor (Rbias) is required, and should be connected between the PI2001 VC pin and Vaux. The resistor is selected based on the input voltage range.

Minimize the resistor value for low Vaux voltage levels to avoid a voltage drop that may reduce the VC voltage lower than required to drive the gate of the MOSFET. Select the value of Rbias using the following equations:

$$Rbias = \frac{Vaux_{\min} - VC_{clamp}}{IC_{\max}}$$

Rbias maximum power dissipation:

$$Pd_{Rbias} = \frac{(Vaux_{max} - VC_{clamp})}{Rbias}$$

*Rbias* maximum power dissipation is at maximum input voltage and minimum clamp voltage (15V).

Where:

*Vaux*<sub>min</sub>: Vaux minimum voltage

*Vaux*<sub>max</sub>: Vaux maximum voltage

VC<sub>Clamp</sub>: Controller clamp voltage, 15.5V

*IC*<sub>max</sub> : Controller maximum bias current (4.2mA)

#### Slave:

For a high current application where one MOSFET can not handle the total load current, multiple MOSFETs can be paralleled and driven by a single PI2001 controller. Special care has to be taken when multiple MOSFET gates are driven from one gate driver output. The gate driver output capability will be divided by the number of MOSFET gates connected to it and will slow the MOSFET response to a reverse fault. To avoid MOSFET slow response the PI2001 can be configured in a master / slave configuration providing localized gate drive to each paralleled MOSFET.

The Pl2001 slave feature allows the user to parallel multiple Pl2001s and configure one unit as the master and the rest in slave mode. The slave  $(\overline{SL})$  pin of the master unit will act as an output driving the units configured in slave mode. The  $\overline{SL}$  pins of the slaved units will act as inputs under the control of the master. In this configuration each MOSFET will have its own localized gate driver which is synchronized by the master controller, thereby improving the response to a reverse current condition. One master controller is capable of driving up to 10 slave inputs.

#### N-Channel MOSFET Selection:

There are several factors that affect the MOSFET selection including cost, on-state resistance (Rds(on)), current rating, power dissipation, thermal conductivity, drain-to-source breakdown voltage (BVdss), gate-to-source voltage rating (Vgs), and gate threshold voltage (Vgs<sub>(TH)</sub>).

The first step is to select suitable MOSFETs based on the BVdss requirement for the application. The BVdss voltage rating should be higher than the applied Vin voltage plus expected transient voltages. Stray parasitic inductance in the circuit can also contribute to significant transient voltage conditions, particularly

during MOSFET turn-off after a reverse current fault has been detected. In Active ORing applications when one of the input power sources is shorted, a large reverse current is sourced from the circuit output through the MOSFET. Depending on the output impedance of the system, the reverse current may reach over 60A in some conditions before the MOSFET is turned off. Such high current conditions will store energy even in a small parasitic element. For example, a 1nH parasitic inductance with 60A reverse current will store 1.8µJ (1/2Li2). When the MOSFET is turned off, the stored energy will be released and will produce high negative voltage ringing at the MOSFET source. This event will create a high voltage difference across the drain and source of the MOSFET.

The MOSFET current rating and maximum power dissipation are closely related. Generally the lower the MOSFET Rds(on), the higher the current capability and the lower the resultant power dissipation. This leads to reduced thermal management overhead, but will ultimately be higher cost compared to higher Rds(on) parts. It is important to understand the primary design goal objectives for the application in order to effectively trade off the performance of one MOSFET versus another.

Power dissipation in active ORing circuits is derived from the total source current and the on-state resistance of the selected MOSFET.

MOSFET power dissipation:

$$Pd_{MOSFET} = Is^2 * Rds(on)$$

Where :

*Is* : Source Current *Rds(on)* : MOSFET on-state resistance

#### Note:

In the calculation use Rds(on) at maximum MOSFET temperature because Rds(on) is temperature dependent. Refer to the normalized Rds(on) curves in the MOSFET manufacturers datasheet. Some MOSFET Rds(on) values may increase by 50% at 125°C compared to values at 25°C.

The Junction Temperature rise is a function of power dissipation and thermal resistance.

$$Trise_{MOSFET} = Rth_{IA} * Pd_{MOSFET} = Rth_{IA} * Is^2 * Rds(on),$$

Where:

$Rth_{I4}$ : Junction-to-Ambient thermal resistance

#### Rds(on) and PI2001 sensing:

The PI2001 senses the MOSFET source-to-drain voltage drop via the SP and SN pins to determine the status of the current through the MOSFET. When the MOSFET is fully enhanced, its source-to-drain voltage is equal to the MOSFET on-state resistance multiplied by the source current, VSD = Rds(on)\*Is. The reverse current threshold is set for -6mV and when the differential voltage between the SP & SN pins is less than -6mV, i.e. SP-SN≤-6mV, the PI2001 detects a reverse current fault condition and pulls the MOSFET gate pin low, thus turning off the MOSFET and preventing further reverse current. The reverse current fault protection disconnects the power source fault condition from the redundant bus, and allows the system to keep running.

The GATE pin output voltage is clamped to 10.5V maximum with respect to the SP pin, which should be tied to the MOSFET source pin, to support any MOSFET with a Vgs rating of  $\pm 12V$  or greater. A Vgs rating  $\geq 12V$  is very common for industry standard N-Channel MOSFETs.

#### OV/UV resistor selection:

The UV and OV comparator inputs are used to monitor the input voltage and will indicate a fault condition when this voltage is out of range. The UV and OV pins can be configured in two different ways, either with a divider on each pin, or with a threeresistor divider to the same node, enabling the elimination of one resistor. Under-Voltage is monitored by the UV pin input and Over-Voltage is monitored with the OV pin input.

The Fault pin ( $\overline{FT}$ ) will indicate a fault (active low) when the UV pin is below the threshold or when the OV pin is above the threshold. The UV and OV thresholds are 0.50V typ with 25mV hysteresis and their input current is less than  $\pm 1\mu$ A. It is important to consider the maximum current that will flow in the resistor divider and maximum error due to UV and OV input current. Set the resistor current to 100µA or higher to maintain 1% accuracy for UV and OV due to the bias current.

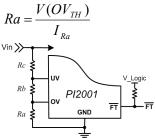

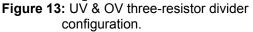

The three-resistor voltage divider configuration for both UV and OV to monitor the same voltage node is shown in figure 13:

| Picor Corporation | n • picorpower.com |  |

|-------------------|--------------------|--|

|-------------------|--------------------|--|

$$Ra = \frac{V(OV_{TH})}{I_{Ra}}$$

Set Ra value based on system allowable current  $I = \frac{1}{Ra} \frac{V(OV_{TH})}{V(OV_{TH})}$

$$Rb = Ra\left(\frac{V(OV)}{V(UV)} - 1\right)$$

$Rc = \left(Ra + Rb\right) \left(\frac{V(UV)}{V_{TH}} - 1\right)$

Where:

$V(UV_{TH})$ : UV threshold voltage $V(OV_{TH})$ : OV threshold voltageV(UV): UV voltage $I_{Ra}$ : Ra current.

Alternatively, a two-resistor voltage divider configuration can be used and is shown in (Figure 14).

Figure 14: Two-resistor divider configuration

The UV resistor voltage divider can be obtained from the following equations:

$$R1_{UV} = \frac{V(UV_{TH})}{I_{RUV}}$$

Set  $R1_{\rm UV}$  value based on system allowable current  $I_{\rm RUV} \ge 100\,\mu A$

$$R2_{UV} = R1_{UV} \left( \frac{V(UV)}{V(UV_{TH})} - 1 \right)$$

Where:

$V(UV_{TH})$  : UV threshold voltage  $I_{RUV}$  :  $R1_{UV}$  current

$$R1_{UV} = \frac{V(UV_{TH})}{I_{RUV}}$$

Set  $R1_{OV}$  value based on system allowable current  $I_{RUV} \ge 100 \,\mu A$

$$R2_{OV} = R1_{OV} \left( \frac{V(OV)}{V(OV_{TH})} - 1 \right)$$

Where:

$V(OV_{TH})$  : OV threshold voltage

$I_{ROV}$  :  $R1_{OV}$  current

#### **Typical application Example 1:**

#### **Requirement:**

Redundant Bus Voltage = 3.3V Load Current = 15A (assume through each redundant path) Maximum Ambient Temperature = 75°C Auxiliary Voltage = 12V (11V to 13V)

#### Solution:

- 1. A single PI2001 with suitable external MOSFET for each redundant 3.3V power source should be used, configured as shown in the circuit schematic in figure 15

- Select a suitable N-Channel MOSFET: Most industry standard MOSFETs have a Vgs rating of +/-12V or higher. Select an N-Channel MOSFET with a low Rds(on) which is capable of supporting the full load current with some margin, so a MOSFET capable of at least 18A in steady state is reasonable. An exemplary MOSFET having these characteristic is FDS6162N7 from Fairchild.

#### From FDS6162N7 datasheet:

- N-Channel MOSFET

- V<sub>DS</sub>= 20V

- I<sub>D</sub> = 23A continuous drain current

- VGS(MAX)= ± 12V

- R<sub>θJA</sub>= 40°C/W

- $R_{DS(on)}=2.9m\Omega$  typical at I<sub>D</sub>=23A, V<sub>GS</sub>≥4.5V, T<sub>J</sub>=25°C

#### Reverse current threshold is:

$$Is.reverse = \frac{Vth.reverse}{Rds(on)} = \frac{-6mV}{2.9m\Omega} = -2.07A$$

#### **Power dissipation:**

Rds(on) is  $3.5m\Omega$  maximum at  $25^{\circ}C \& 4.5Vgs$  and will increase as the temperature increases. Add  $25^{\circ}C$  to maximum ambient temperature to compensate for the temperature rise due to power dissipation. At  $100^{\circ}C$ ( $75^{\circ}C + 25^{\circ}C$ ) Rds(on) will increase by 28%.

$Rds(on) = 3.5m\Omega * 1.28 = 4.48m\Omega$  maximum at 100°C

$Trise = Rth_{IA} * Is^2 * Rds(on)$

Maximum Junction temperature

$$T_{J_{\text{max}}} = T_A + Trise$$

$$T_{J_{\text{max}}} = 75^{\circ}C + \left(\frac{40^{\circ}C}{W} * (15A)^2 * 4.48m\Omega\right) = 115^{\circ}C$$

Recalculate based on calculated Junction temperature, 115°C.

At 115°C Rds(on) will increase by 32%.

$$Rds(on) = 3.5m\Omega * 1.32 = 4.62m\Omega$$

$T_{J_{\text{max}}} = 75^{\circ}C + \left(\frac{40^{\circ}C}{W} * (15A)^2 * 4.62m\Omega\right) = 1165^{\circ}C$

- Vaux: Make sure Vaux voltage is higher than Vin (power source output) by the voltage required to fully enhance the MOSFET. Minimum required Vaux = Vin + Vgs + 0.5V = 3.3V + 4.5V + 0.5V = 8.3V. Since 8.3V is less than the 11V minimum Aux supply voltage, there is sufficient voltage available to drive the gate of the MOSFET.

- 4. **SP and SN pins:** Connect the SP pin to the MOSFET source pin and the SN pin to the MOSFET drain pin.

- 5. **BK pin:** Connect the BK pin to the GND pin to achieve the minimum reverse current response time.

- 6. *SL* **pin:** Not required, so leave floating.

- 7.  $\overline{FT}$  **pin**: Connect to the logic input and to the logic power supply via a 10K $\Omega$  resistor.

- 8. **Program UV and OV to monitor input voltage:** Program UV at 3.0V and OV at 3.6V

Use the three-resistor divider configuration:  $I_{Ra} = 200 \,\mu A$

**Figure 15:** PI2001 in high side Active ORing configuration

#### Typical application Example 2:

#### **Requirement:**

Redundant Bus Voltage =  $12V (\pm 10\%, 10.8V to 13.2V)$

Load Current = 10A (assume through each redundant path)

Maximum Ambient Temperature = 75°C

Auxiliary Voltage =  $24V\pm10\%$  (21.6V to 26.4V) referenced to GND

#### Solution:

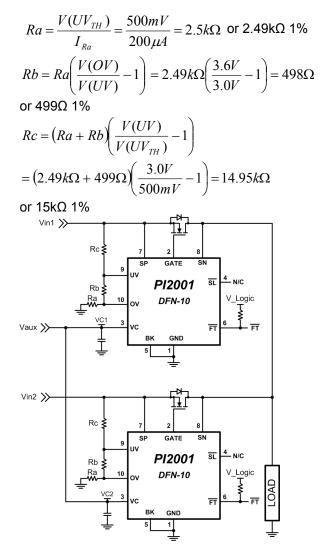

- 1. A single PI2001 with suitable external MOSFET for each redundant 12V power source should be used, configured in a high-side floating configuration as shown in the circuit schematic in Figure 16. The controller is floated on Vin by connecting the controller ground pin to the input voltage Vin.

- 2. Select a suitable N-Channel MOSFET: Select an N-Channel MOSFET with a voltage rating higher than the 12V input plus any expected transient voltages, with a low Rds(on) that is capable of supporting full load current with margin. For instance, a 30V rated MOSFET with 20A current capability is suitable. An exemplary MOSFET having these characteristic is FDS8812NZ from Fairchild.

#### From FDS8812NZ datasheet:

- N-Channel MOSFET

- V<sub>DS</sub>= 30V

- I<sub>D</sub> = 20A continuous drain current

- VGS(MAX)= ± 20V

- R<sub>θJA</sub>= 50°C/W

- $R_{DS(on)}$ =3.2m $\Omega$  typical at I<sub>D</sub>=10A, V<sub>GS</sub>=8V, T<sub>J</sub>=25°C

#### Reverse current threshold is:

$$Is.reverse = \frac{Vth.reverse}{Rds(on)} = \frac{-6mV}{3.2m\Omega} = -1.87A$$

#### Power dissipation:

Rds(on) is  $4.2m\Omega$  maximum at 25°C & 8Vgs and will increase as the temperature increases. Add 25°C to maximum ambient temperature to compensate for the temperature rise due to power dissipation. At 100°C (75°C + 25°C) Rds(on) will increase by 28%.

$Rds(on) = 4.2m\Omega * 1.28 = 5.37m\Omega$  maximum at 100°C

$$Trise = Rth_{I4} * Is^2 * Rds(on)$$

Maximum Junction temperature

$$T_{I_{\text{max}}} = T_A + Trise$$

$$T_{J_{\text{max}}} = 75^{\circ}C + \left(\frac{50^{\circ}C}{W} * (10A)^2 * 5.37m\Omega\right) = 102^{\circ}C$$

3. **Vaux:** Make sure Vaux voltage is higher than Vin (power source output) by the voltage required to fully enhance the MOSFET. In this case there is sufficient headroom on the Vaux supply to increase the Vgs level for a reduction in power dissipation due to lower Rds(on). If the MOSFET requires 8.0V to achieve lower power dissipation, then

Vaux = Vin + Vgs + 0.5V = 12V + 8.0V + 0.5V = 20.5V.

When Vin is off (0V), Pl2001 GND pin is at 0V and Vaux is higher than the VC clamp voltage. A bias resistor (Rbias) is needed in series with the VC pin.

Rbias value:

$$Rbias = \frac{Vaux_{\min} - VC_{clamp}}{IC_{\max}} = \frac{21.6V - 15.5V}{4.2mA} = 1.45K\Omega$$

or 1.30KΩ

Rbias resistor power dissipation rating:

Note: Use minimum value for VC<sub>Clamp</sub> voltage to calculate worst condition power dissipation.

$$Pd_{Rbias} = \frac{(Vaux_{max} - VC_{clamp})^2}{Rbias} = \frac{(26.4V - 15.0V)^2}{1.30K\Omega} = 100mW$$

Figure 16: PI2001 in floating application: example 2

- 4. **SP and SN pins:** Since the PI2001 controller GND pin is connected to the input (Vin) which is also the MOSFET source, connect the SP pin directly to the PI2001 GND pin to reduce the parasitic between the SP pin and the GND pin to avoid negative voltages on the SP pin with respect to GND pin. Connect the SN pin to the MOSFET drain pin.

- 5. **BK pin:** Connect the BK pin to the GND pin to achieve the minimum reverse current response time.

- 6. *SL* **pin:** Not required, so leave floating.

- 7.  $\overline{FT}$  **pin**: The  $\overline{FT}$  pin output is referenced to the Pl2001 GND pin which is connected to Vin. A level shift circuit can be added to make the  $\overline{FT}$  pin output referenced to the system ground. The recommended level shift circuit is shown in Figure 16, The level shift circuit uses a Dual Bias Resistor Transistor circuit which is available as a small device that contains two transistors and their bias resistors, part number NSBC114EPDXV6T1.

- 8. **UV and OV inputs:** In floating applications these pins can not be used to monitor Vin. Connect UV to the VC pin and OV to the GND pin to disable their function.

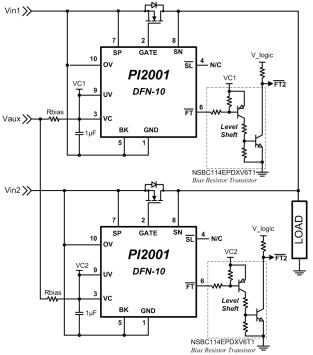

#### Typical application Example 3: Requirement: Redundant Bus Voltage = -48V (-36V to -60V, 100V for 100ms transient)

Load Current = 5A load (assume through each redundant path)

Maximum Ambient Temperature = 60°C

#### Solution:

- 1. A single PI2001 with a suitable MOSFET for each redundant -48V power source should be used and configured as shown in figure 17. The VC is biased from the return line through a bias resistor.

- 2. Select a suitable N-Channel MOSFET: Select the N-Channel MOSFET with voltage rating higher than the input voltage, Vin, plus any expected transient voltages, with a low Rds(on) that is capable of supporting the full load current with margin. For instance, a 100V rated MOSFET with 10A current capability is suitable. An exemplary MOSFET having these characteristic is Si4486EY from Vishay Siliconix.

#### From Si4486EY datasheet:

- N-Channel MOSFET

- V<sub>DS</sub>= 100V

- I<sub>D</sub> = 23A continuous drain current at 125°C

- VGS(MAX) = ± 20V

- $R_{\theta JA} = 50^{\circ} C/W$

- $R_{DS(on)}$ =20m $\Omega$  typical at V<sub>GS</sub>=10V, T<sub>J</sub>=25°C

#### Reverse current threshold is:

$$Is.reverse = \frac{Vth.reverse}{Rds(on)} = \frac{-6mV}{20m\Omega} = -300mA$$

#### Power dissipation:

Rds(on) is  $25m\Omega$  maximum at  $25^{\circ}$ C & 10Vgs and will increase as the temperature increases. Add 40°C to maximum ambient temperature to compensate for the temperature rise due to power dissipation. At 100°C (60°C + 40°C) Rds(on) will increase by 63%.

$Rds(on) = 25m\Omega * 1.63 = 41m\Omega$  maximum at 100°C

Maximum Junction temperature

$$T_{J_{\text{max}}} = 60^{\circ}C + \left(\frac{50^{\circ}C}{W} * (5.0A)^2 * 41m\Omega\right) = 111^{\circ}C$$

Recalculate based on calculated Junction temperature, 115°C.

At 115°C Rds(on) will increase by 72%.

$Rds(on) = 25m\Omega * 1.72 = 43m\Omega$  maximum at 115°C

$$T_{J_{\text{max}}} = 60^{\circ}C + \left(\frac{50^{\circ}C}{W} * (5.0A)^2 * 43m\Omega\right) = 113^{\circ}C$$

**Vaux:** Connect each controller to the return path with a separate bias resistor, Rbias.

To reduce *Rbias* power dissipation,  $VC_{clamp}$  is

selected at 13V which is less than the actual PI2001 clamp voltage (15V typical). 13V is higher than PI2001 maximum gate clamp voltage (10.5V).

$$Rbias = \frac{Vaux_{\min} - VC_{clamp}}{IC_{\max}} = \frac{36V - 13V}{4.2mA} = 5.48K\Omega$$

or 5.49KΩ

*Rbias* maximum power dissipation is at maximum input voltage and minimum clamp voltage

$$Pd_{Rbias} = \frac{(Vaux_{max} - VC_{clampMIN})^{2}}{Rbias} = \frac{(60V - 15V)^{2}}{5.49K\Omega} = 369mW$$

- 3. **SP and SN pins:** Connect the SP pin to the MOSFET source and controller GND pin, and connect the SN pin to Vin- and the drain of the MOSFET.

- 4. **BK pin:** Connect the BK pin to the GND pin to achieve the minimum reverse current response time.

- 5.  $\overline{SL}$  pin: Not required, so leave floating.

- 6.  $\overline{FT}$  **pin**: Connect the  $\overline{FT}$  pin to logic input and to the logic power supply or to the VC pin via a resistor.

- 7. UV and OV inputs: sensing input voltages Vin1and Vin2- separately in this application the resistor divider has to be connected between Vin1-/Vin2- and return. The PI2001 controller GND pins are referenced to the load side, if the resistor dividers are connected between Return and Vin1-/Vin2- it will produce an error due the voltage drop across the MOSFET and will expose the OV and UV controller inputs to a high current in case of an input short circuit and will damage the controller.

The voltage across the load can be monitored by one controller or both. The following shows the resistor voltage divider configuration using the three-resistor divider configuration:

Set I<sub>Ra</sub>=100µA

$$Ra = \frac{V(UV_{TH})}{I_{Ra}} = \frac{500mV}{100\mu A} = 5k\Omega \text{ or } 4.99k\Omega \ 1\%$$

$$Rb = Ra\left(\frac{V(OV)}{V(UV)} - 1\right) = 4.99k\Omega\left(\frac{65V}{34V} - 1\right) = 4.55K\Omega$$

Or Rb=4.53KΩ

$$Rc = \left(Ra + Rb\right)\left(\frac{V(UV)}{V(UV_{TH})} - 1\right)$$

$$Rc = \left(4.99k\Omega + 4.53K\Omega\right)\left(\frac{34V}{500mV} - 1\right) = 638k\Omega$$

or 634kΩ 1%

Figure 17: PI2001 in low side -48V application

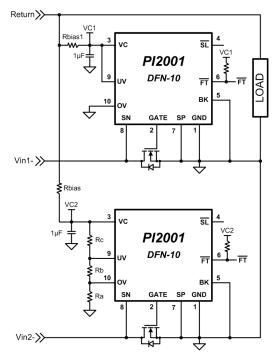

#### Layout Recommendation:

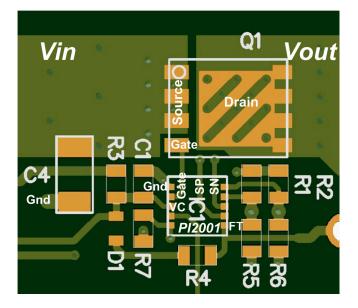

Use the following general guidelines when designing printed circuit boards. An example of the typical land pattern for a TDFN PI2001 and SO-8/PowerPak MOSFET is shown in Figure 18:

- It is best to connect the gate of the MOSFET to the GATE pin of the controller with a short and wide trace.

- The GND pin of the controller carries high peak current and it should be returned to the ground plane through a low impedance path.

- Connections from the SP and SN pins to the MOSFET source and drain pins respectively should be as short as possible

- The VC bypass capacitor should be located as close as possible to the VC and GND pins. Place the Pl2001 and VC bypass capacitor on the same layer of the board. The VC pin and  $C_{VC}$  PCB trace should not contain any vias.

- Connect all MOSFET source pins together with a wide trace to reduce trace parasitics and to accommodate the high current input. Similarly, connect all MOSFET Drain pins together with a wide trace to accommodate the high current output.

Connect the power source very close to the MOSFET source connection to reduce the effects of stray parasitics. If a short trace is not possible, connect C4 (typically 1µF) as shown in figure 18.

Figure 18: PI2001 and MOSFET layout recommendation

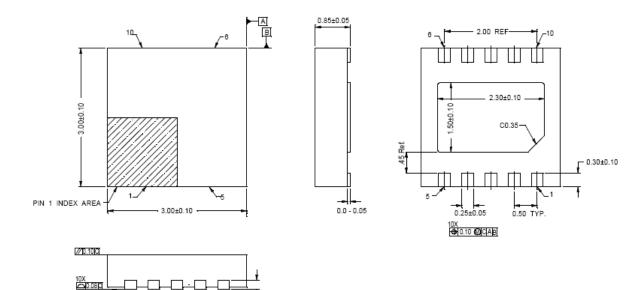

# Package Drawing: 10 Lead TDFN

#### NOTES :

1. All dimensions are in millimeters, angles in degrees.

0.20 REF

2. Coplanarity does not exceed .05mm

c

- 3. Package is variation of JEDEC MO-229

- 4. Warpage does not exceed .05mm

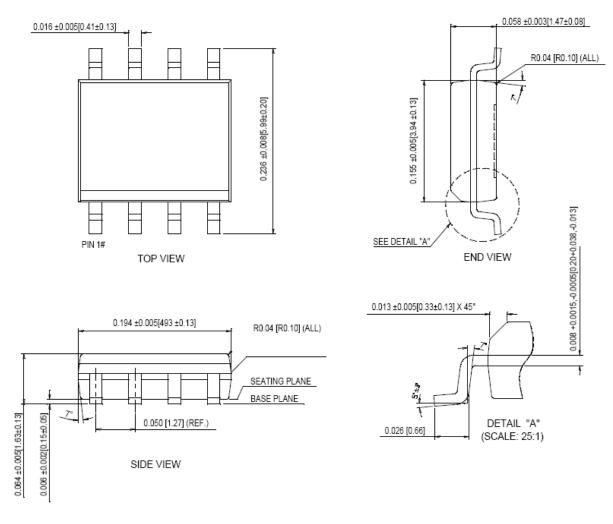

# Package Drawing: 8 Lead SOIC

#### NOTES:

1. ALL DIMENSIONS ARE SHOWN IN INCHES [MM] 2. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006 [0.15] PER SIDE 3. FORMED LEADS SHALL BE PLANAR WITH REPECT TO ONE ANOTHER WITHIN 0.003 [0.08] AT SEATING PLANE 4. GENERAL ANGLE TOLERANCES TO BE +/-2" 5. GENERAL TOLERANCES TO BE +/-0.005 [0.13] 6. THIS POD COMPLIES TO MS-012 ISSUE C

#### **Ordering Information**

| Part Number    | Package                | Transport Media |  |  |

|----------------|------------------------|-----------------|--|--|

| PI2001-00-QEIG | 3mm x 3mm 10 Lead TDFN | Tape & Reel     |  |  |

| PI2001-00-SOIG | 8 Lead SOIC            | Tape & Reel     |  |  |

Picor Corporation • picorpower.com

# Warranty

Vicor products are guaranteed for two years from date of shipment against defects in material or workmanship when in normal use and service. This warranty does not extend to products subjected to misuse, accident, or improper application or maintenance. Vicor shall not be liable for collateral or consequential damage. This warranty is extended to the original purchaser only.

EXCEPT FOR THE FOREGOING EXPRESS WARRANTY, VICOR MAKES NO WARRANTY, EXPRESS OR LIMITED, INCLUDING, BUT NOT LIMITED TO, THE WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE.

Vicor will repair or replace defective products in accordance with its own best judgment. For service under this warranty, the buyer must contact Vicor to obtain a Return Material Authorization (RMA) number and shipping instructions. Products returned without prior authorization will be returned to the buyer. The buyer will pay all charges incurred in returning the product to the factory. Vicor will pay all reshipment charges if the product was defective within the terms of this warranty.

Information published by Vicor has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies. Vicor reserves the right to make changes to any products without further notice to improve reliability, function, or design. Vicor does not assume any liability arising out of the application or use of any product or circuit; neither does it convey any license under its patent rights nor the rights of others. Vicor general policy does not recommend the use of its components in life support applications wherein a failure or malfunction may directly threaten life or injury. Per Vicor Terms and Conditions of Sale, the user of Vicor components in life support applications assumes all risks of such use and indemnifies Vicor against all damages.

# Vicor's comprehensive line of power solutions includes high density AC-DC and DC-DC modules and accessory components, fully configurable AC-DC and DC-DC power supplies, and complete custom power systems.

Information furnished by Vicor is believed to be accurate and reliable. However, no responsibility is assumed by Vicor for its use. Vicor components are not designed to be used in applications, such as life support systems, wherein a failure or malfunction could result in injury or death. All sales are subject to Vicor's Terms and Conditions of Sale, which are available upon request.

#### Specifications are subject to change without notice.

Vicor Corporation 25 Frontage Road Andover, MA 01810 USA Picor Corporation 51 Industrial Drive North Smithfield, RI 02896 USA

Customer Service: custserv@vicorpower.com Technical Support: apps@vicorpower.com Tel: 800-735-6200 Fax: 978-475-6715