Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 3.3V, SOTiny<sup>TM</sup> 0.4 $\Omega$ Dual SPDT Analog Switch

#### **Features**

• CMOS Technology for Bus and Analog Applications

• Low On-Resistance:  $0.4\Omega$  (+2.7V Supply)

• Wide V<sub>DD</sub> Range: +1.5V to +4.2V

• Low Power Consumption : 5μW

• Rail-to-Rail switching throughout Signal Range

• Fast Switching Speed: 20ns max. at 3.3V

• High Off Isolation: -27dB at 100 kHz

–41dB (100 kHz) Crosstalk Rejection Reduces Signal Distortion

• Extended Industrial Temperature Range: -40°C to 85°C

· Packaging:

- Pb-free & Green, 12-pin TDFN (ZE)

#### **Applications**

- · Cell Phones

- PDAs

- Portable Instrumentation

- Battery Powered Communications

- Computer Peripherals

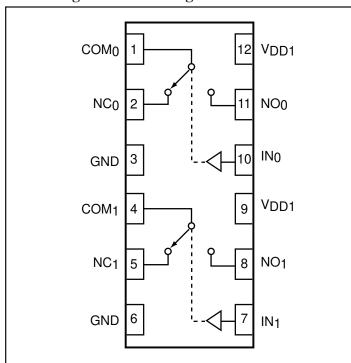

## **Pin Description**

| Pin Number | Name      | Description                         |

|------------|-----------|-------------------------------------|

| 8, 11      | NOx       | Data Port (Normally Open)           |

| 3, 6       | GND       | Ground                              |

| 2, 5       | NCx       | Data Port (Normally Closed)         |

| 1, 4       | COMx      | Common Output/Data Port             |

| 9, 12      | $V_{DDX}$ | Postive Power Supply <sup>(2)</sup> |

| 7, 10      | INx       | Logic Control                       |

#### **Notes:**

- 1. x = 0 or 1

- 2.  $V_{DD0}$  ad  $V_{DD1}$  are not internally connected. Each must be powered seperately.

#### **Description**

The PI3A3160 is a fast Dual single-pole double-throw (SPDT) CMOS switch. It can be used as an analog switch or as a low-delay bus switch. Specified over a wide operating power supply voltage range, +1.5V to +4.2V, the switch has an On-Resistance of  $0.4\Omega$  at 3.0V.

Control inputs, IN, tolerates input drive signals up to 3.3V, independent of supply voltage.

PI3A3160 is a lower voltage and On-Resistance replacement for the PI5A3158.

#### **Block Diagram / Pin Configuration**

#### **Function Table**

| <b>Logic Input</b> | Function              |

|--------------------|-----------------------|

| 0                  | NCx Connected to COMx |

| 1                  | NOx Connected to COMx |

09-0003 PS8711G 10/13/09

#### **Absolute Maximum Ratings**

| Voltages Referenced to GND                                                                                            |                                 |

|-----------------------------------------------------------------------------------------------------------------------|---------------------------------|

| V <sub>DD</sub>                                                                                                       | –0.5V to +4.4V                  |

| V <sub>IN</sub> , V <sub>COM</sub> , V <sub>NC</sub> , V <sub>NO</sub> <sup>(1)</sup> or 30mA, whichever occurs first | $0.5V \text{ to } V_{+} + 0.3V$ |

| Current (any terminal)                                                                                                | ±200mA                          |

| Peak Current, COM, NO, NC (Pulsed at 1ms, 10% duty cycle)                                                             | ±400mA                          |

#### **Thermal Information**

| Continuous Power Dissipation        |                |

|-------------------------------------|----------------|

| SOT23 (derate 7.1mW/°C above +70°C) | 0.5W           |

| Storage Temperature                 | 65°C to +150°C |

| Lead Temperature (soldering, 10s)   | +300°C         |

|                                     |                |

Note 1: Signals on NC, NO, COM, or IN exceeding V<sub>DD</sub> or GND are clamped by internal diodes. Limit forward diode current to 30mA.

Caution: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied.

### **Electrical Specifications - Single +4.2V Supply**

$(V_{DD} = +4.2V \pm 5\%, GND = 0V, V_{IH} = 1.6V, V_{IL} = 0.7V)$

| Parameter                                   | Symbol                  | Conditions                                                   | Temp. (°C) | Min. <sup>(1)</sup> | Typ. (2) | Max. (1)          | Units |  |  |

|---------------------------------------------|-------------------------|--------------------------------------------------------------|------------|---------------------|----------|-------------------|-------|--|--|

| Analog Switch                               |                         |                                                              |            |                     |          |                   |       |  |  |

| Analog Signal Range (3)                     | V <sub>ANALOG</sub>     |                                                              | Full       | 0                   |          | $V_{\mathrm{DD}}$ | V     |  |  |

| On Resistance                               | D                       |                                                              | 25         |                     | 0.4      | 0.45              |       |  |  |

| On Resistance                               | R <sub>ON</sub>         | $V_{DD} = 4.0V,$                                             | Full       |                     |          | 0.6               |       |  |  |

| On-Resistance Match                         | AD                      | $I_{COM} = 99 \text{mA},$<br>$V_{IN} = 0 \text{V to V}_{DD}$ | 25         |                     |          | 0.08              | Ω     |  |  |

| Between Channels <sup>(4)</sup>             | $\Delta R_{ON}$         |                                                              | Full       |                     |          | 0.09              |       |  |  |

| On-Resistance Flatness <sup>(5)</sup>       | R <sub>FLAT(ON)</sub>   | $V_{DD} = 4.0V,$<br>$I_{COM} = 100 \text{mA}$                | 25         |                     |          | 0.1               |       |  |  |

| Oli-Resistance Flatness                     |                         |                                                              | Full       |                     |          | 0.1               |       |  |  |

| NO or NC Off Leakage                        | I <sub>NO(OFF)</sub> or | V <sub>DD</sub> =4.2V                                        | 25         | -100                |          | 100               |       |  |  |

| Current <sup>(6)</sup> I <sub>NC(OFF)</sub> |                         | VDD =4.2 V                                                   | Full       | -400                |          | 400               | ]     |  |  |

| COM On Leakage Cur-                         | I <sub>COM(ON)</sub>    | $V_{DD} = 4.2V$                                              | 25         | -200                |          | 200               | nA    |  |  |

| rent <sup>(6)</sup>                         |                         |                                                              | Full       | -400                |          | 400               |       |  |  |

#### **Notes:**

- 1. The algebraic convention, where most negative value is a minimum and most positive is a maximum, is used in this data sheet.

- 2. Typical values are for DESIGN AID ONLY, not guaranteed or subject to production testing.

- 3. Guaranteed by design.

- 4.  $\Delta R_{ON} = R_{ON} \text{ max.} R_{ON} \text{ min.}$

- 5. Flatness is defined as the difference between the maximum and minimum value of On-Resistance measured.

- 6. Leakage parameters are 100% tested at maximum rated hot temperature and guaranteed by correlation at +25°C.

- 7. Off Isolation =  $20\log_{10} [V_{COM} / (V_{NO} \text{ or } V_{NC})]$ . See Figure 4.

- 8. Between any two switches. See Figure 5.

09-0003 PS8711G 10/13/09

## **Electrical Specifications - Single +3.3V Supply**

$(V_{DD} = +3.3V \pm 10\%, GND = 0V, V_{IH} = 1.4V, V_{IL} = 0.5V)$

| Parameter                             | Symbol                         | Conditions                                                                                 | Temp. (°C) | Min. <sup>(1)</sup> | Typ. (2) | Max. (1)          | Units |  |  |

|---------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------|------------|---------------------|----------|-------------------|-------|--|--|

| Analog Switch                         |                                |                                                                                            |            |                     |          |                   |       |  |  |

| Analog Signal Range (3)               | V <sub>ANALOG</sub>            |                                                                                            | Full       | 0                   |          | $V_{\mathrm{DD}}$ | V     |  |  |

| On Designation                        | l D                            |                                                                                            | 25         |                     | 0.4      | 0.45              |       |  |  |

| On Resistance                         | R <sub>ON</sub>                | $V_{DD} = 2.7V,$                                                                           | Full       |                     |          | 0.6               | ]     |  |  |

| On-Resistance Match                   | A.D.                           | $I_{COM} = 100 \text{mA},$<br>$V_{NO} \text{ or } V_{NC} = +1.5 \text{V}$                  | 25         |                     |          | 0.08              | Ω     |  |  |

| Between Channels <sup>(4)</sup>       | $\Delta R_{ON}$                | THO OF THE TEST                                                                            | Full       |                     |          | 0.09              |       |  |  |

|                                       | R <sub>FLAT(ON)</sub>          | $V_{DD} = 2.7V,$<br>$I_{COM} = 100 \text{mA},$<br>$V_{NO} \text{ or } V_{NC} = 0.8V, 2.0V$ | 25         |                     |          | 0.1               |       |  |  |

| On-Resistance Flatness <sup>(5)</sup> |                                |                                                                                            | Full       |                     |          | 0.1               |       |  |  |

| NO or NC Off Leakage                  | INOVOEEN OF                    | $V_{DD} = 3.3V,$<br>$V_{COM} = 0V,$<br>$V_{NO}$ or $V_{NC} = +2.0V$                        | 25         | -100                |          | 100               |       |  |  |

| Current <sup>(6)</sup>                | $I_{NO(OFF)}$ or $I_{NC(OFF)}$ |                                                                                            | Full       | -400                |          | 400               |       |  |  |

| COM On Leakage Cur-                   | I <sub>COM(ON)</sub>           | $V_{DD} = 3.3V,$<br>$V_{COM} = +2.0V,$<br>$V_{NO}$ or $V_{NC} = +2.0V$                     | 25         | -200                |          | 200               | nA    |  |  |

| rent <sup>(6)</sup>                   |                                |                                                                                            | Full       | -400                |          | 400               |       |  |  |

- 1. The algebraic convention, where most negative value is a minimum and most positive is a maximum, is used in this data sheet.

- 2. Typical values are for DESIGN AID ONLY, not guaranteed or subject to production testing.

- 3. Guaranteed by design.

- 4.  $\Delta R_{ON} = R_{ON} \text{ max.} R_{ON} \text{ min.}$

- 5. Flatness is defined as the difference between the maximum and minimum value of On-Resistance measured.

- 6. Leakage parameters are 100% tested at maximum rated hot temperature and guaranteed by correlation at +25°C.

- 7. Off Isolation =  $20\log_{10} [V_{COM}/(V_{NO} \text{ or } V_{NC})]$ . See Figure 4.

- 8. Between any two switches. See Figure 5.

## **Electrical Specifications - Single +4.2V Supply**

$(V_{DD} = +4.2V \pm 5\%, GND = 0V, V_{IH} = 1.6V, V_{IL} = 0.7V)$

| Description Parameters             |                       | <b>Test Conditions</b>                                                              | Temp (°C) | Min. <sup>(1)</sup> | Typ.(2) | Max. <sup>(1)</sup> | Units          |

|------------------------------------|-----------------------|-------------------------------------------------------------------------------------|-----------|---------------------|---------|---------------------|----------------|

| Logic Input                        |                       |                                                                                     |           |                     |         |                     |                |

| Input High Voltage V <sub>IH</sub> |                       | Guaranteed logic High Level                                                         | Full      | 1.6                 |         |                     | V              |

| Input Low Voltage                  | $V_{\rm IL}$          | Guaranteed logic Low Level                                                          |           |                     |         | 0.7                 | ] <sup>v</sup> |

| Input Current with Voltage<br>High | I <sub>INH</sub>      | $V_{IN} = 1.4V$ , all others = 0.5V                                                 |           | -1                  |         | 1                   |                |

| Input Current with Voltage<br>Low  | I <sub>INL</sub>      | $V_{IN} = 0.5V$ , all other = 1.4V                                                  |           | -1                  |         | 1                   | μA             |

| Dynamic                            |                       |                                                                                     |           |                     |         |                     |                |

| T. O. T.                           |                       |                                                                                     | 25        |                     |         | 20                  |                |

| Turn-On Time                       | t <sub>ON</sub>       | $V_{DD} = 4.2V$ , $V_{NO}$ or                                                       | Full      |                     |         | 25                  | ns             |

| Turn Off Time                      | t <sub>OFF</sub>      | $V_{NC} = 2.0V$ , Figure 1                                                          | 25        |                     |         | 12                  |                |

| Turn-Off Time                      |                       |                                                                                     | Full      |                     |         | 15                  |                |

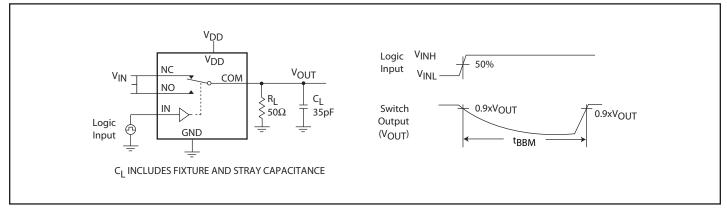

|                                    | t <sub>BBM</sub>      | $V_{NO}$ or $V_{NC}$ = 1.5V,<br>$R_L$ = 50 $\Omega$ ,<br>$C_L$ = 35pF, See Figure 8 | 25        | 1                   | 12      |                     |                |

| Break-Before-Make                  |                       |                                                                                     | Full      | 1                   |         |                     |                |

| Charge Injection <sup>(3)</sup>    | Q                     | $C_L = 1$ nF, $V_{GEN} = 0$ V,<br>$R_{GEN} = 0$ Ω, Figure 2                         | 25        |                     | 100     |                     | pC             |

| Off Isolation <sup>(7)</sup>       | O <sub>IRR</sub>      | $R_L = 50\Omega$ , $f = 100$ kHz, Figure                                            | 3         |                     | -27     |                     | JD.            |

| Cross Talk <sup>(8)</sup>          | X <sub>TALK</sub>     | $R_L = 50\Omega$ , $f = 100$ kHz, Figure                                            | 4         |                     | -41     |                     | dB             |

| NC or NO Capacitance               | C <sub>(OFF)</sub>    | f = 1MHz, Figure 5                                                                  |           |                     | 56      |                     |                |

| COM Off Capacitance                | C <sub>COM(OFF)</sub> | T = TMHz, Figure 3                                                                  |           |                     | 56      |                     | pF             |

| COM On Capacitance                 | C <sub>COM(ON)</sub>  | f = 1MHz, Figure 6                                                                  |           |                     | 160     |                     |                |

| Supply                             |                       |                                                                                     |           |                     |         |                     |                |

| Power-Supply Range                 | $V_{DD}$              |                                                                                     | Full      | 1.5                 |         | 3.6                 | V              |

| Positve Supply Current             | $I_{CC}$              | $V_{DD} = 3.6V$ , $V_{IN} = 0V$ or $V_{DD}$                                         | 25        |                     |         | 0.3                 | μА             |

- 1. The algebraic convention, where most negative value is a minimum and most positive is a maximum, is used in this data sheet.

- 2. Typical values are for DESIGN AID ONLY, not guaranteed or subject to production testing.

- 3. Guaranteed by design.

- 4.  $\Delta R_{ON} = R_{ON} \text{ max.} R_{ON} \text{ min.}$

- 5. Flatness is defined as the difference between the maximum and minimum value of On-Resistance measured.

- 6. Leakage parameters are 100% tested at maximum rated hot temperature and guaranteed by correlation at +25°C.

- 7. Off Isolation =  $20\log_{10} [V_{COM}/(V_{NO} \text{ or } V_{NC})]$ . See Figure 4.

- 8. Between any two switches. See Figure 5.

## **Electrical Specifications - Single +3.3V Supply**

$(V_{DD} = +3.3V \pm 10\%, GND = 0V, V_{IH} = 1.4V, V_{IL} = 0.5V)$

| Description                        | Param-<br>eters       | <b>Test Conditions</b>                                                              | Temp (°C) | Min. <sup>(1)</sup> | Typ. (2) | Max. <sup>(1)</sup> | Units |

|------------------------------------|-----------------------|-------------------------------------------------------------------------------------|-----------|---------------------|----------|---------------------|-------|

| Logic Input                        |                       |                                                                                     |           |                     |          |                     |       |

| Input High Voltage V <sub>IH</sub> |                       | Guaranteed logic High Level                                                         | Full      | 1.4                 |          |                     | V     |

| Input Low Voltage                  | $V_{IL}$              | Guaranteed logic Low Level                                                          |           |                     |          | 0.5                 | ]     |

| Input Current with Voltage<br>High | I <sub>INH</sub>      | $V_{IN} = 1.4V$ , all others = 0.5V                                                 |           | -1                  |          | 1                   |       |

| Input Current with Voltage<br>Low  | I <sub>INL</sub>      | $V_{IN} = 0.5V$ , all other = 1.4V                                                  |           | -1                  |          | 1                   | μA    |

| Dynamic                            |                       |                                                                                     |           |                     |          |                     |       |

| T. O. T.                           | [.                    |                                                                                     | 25        |                     |          | 20                  |       |

| Turn-On Time                       | t <sub>ON</sub>       | $V_{DD} = 3.3V$ , $V_{NO}$ or                                                       | Full      |                     |          | 25                  | ns    |

| T Off T'                           | t <sub>OFF</sub>      | $V_{NC} = 2.0V$ , Figure 1                                                          | 25        |                     |          | 12                  |       |

| Turn-Off Time                      |                       |                                                                                     | Full      |                     |          | 15                  |       |

|                                    | t <sub>BBM</sub>      | $V_{NO}$ or $V_{NC}$ = 1.5V,<br>$R_L$ = 50 $\Omega$ ,<br>$C_L$ = 35pF, See Figure 8 | 25        | 1                   | 12       |                     |       |

| Break-Before-Make                  |                       |                                                                                     | Full      | 1                   |          |                     |       |

| Charge Injection <sup>(3)</sup>    | Q                     | $C_L = 1$ nF, $V_{GEN} = 0$ V,<br>$R_{GEN} = 0$ Ω, Figure 2                         | 25        |                     | 100      |                     | pC    |

| Off Isolation <sup>(7)</sup>       | O <sub>IRR</sub>      | $R_L = 50\Omega$ , $f = 100$ kHz, Figure                                            | 3         |                     | -27      |                     | JD.   |

| Cross Talk <sup>(8)</sup>          | X <sub>TALK</sub>     | $R_L = 50\Omega$ , $f = 100$ kHz, Figure                                            | 4         |                     | -41      |                     | dB    |

| NC or NO Capacitance               | C <sub>(OFF)</sub>    | f = 1MHz, Figure 5                                                                  | '         |                     | 56       |                     |       |

| COM Off Capacitance                | C <sub>COM(OFF)</sub> | 1 – IIVIIIZ, Figure 3                                                               |           |                     | 56       |                     | pF    |

| COM On Capacitance                 | C <sub>COM(ON)</sub>  | f = 1MHz, Figure 6                                                                  |           |                     | 160      |                     |       |

| Supply                             |                       |                                                                                     |           |                     |          |                     |       |

| Power-Supply Range                 | $V_{\mathrm{DD}}$     |                                                                                     | Full      | 1.5                 |          | 3.6                 | V     |

| Positve Supply Current             | I <sub>CC</sub>       | $V_{DD} = 3.6V$ , $V_{IN} = 0V$ or $V_{DD}$                                         | 25        |                     |          | 0.3                 | μΑ    |

- 1. The algebraic convention, where most negative value is a minimum and most positive is a maximum, is used in this data sheet.

- 2. Typical values are for DESIGN AID ONLY, not guaranteed or subject to production testing.

- 3. Guaranteed by design.

- 4.  $\Delta R_{ON} = R_{ON} \text{ max.} R_{ON} \text{ min.}$

- 5. Flatness is defined as the difference between the maximum and minimum value of On-Resistance measured.

- 6. Leakage parameters are 100% tested at maximum rated hot temperature and guaranteed by correlation at +25°C.

- 7. Off Isolation =  $20\log_{10} [V_{COM} / (V_{NO} \text{ or } V_{NC})]$ . See Figure 4.

- 8. Between any two switches. See Figure 5.

## **Electrical Specifications - Single +2.5V Supply**

$(V_{DD} = +2.5V \pm 10\%, GND = 0V, V_{IH} = 1.4V, V_{IL} = 0.5V)$

| Description                           | Parameters            | <b>Test Conditions</b>                                                              | Temp.(°C) | Min. <sup>(1)</sup> | Typ.(2) | Max.(1)           | Units      |

|---------------------------------------|-----------------------|-------------------------------------------------------------------------------------|-----------|---------------------|---------|-------------------|------------|

| Analog Switch                         |                       |                                                                                     |           |                     |         |                   | •          |

| Analog Signal Range <sup>(3)</sup>    | V <sub>ANALOG</sub>   |                                                                                     |           | 0                   |         | $V_{\mathrm{DD}}$ | V          |

| On Resistance                         | Dan                   |                                                                                     | 25        |                     |         | 0.5               |            |

| On Resistance                         | R <sub>ON</sub>       | $V_{DD} = 2.5V, I_{COM} = 80mA,$                                                    | Full      |                     |         | 0.55              | ]          |

| On-Resistance Match                   | $\Delta R_{ m ON}$    | $V_{NO}$ or $V_{NC} = 1.8V$                                                         | 25        |                     |         | 0.09              | $\Omega$   |

| Between Channels (4)                  | ΔKON                  |                                                                                     | Full      |                     |         | 0.09              | ] \( \( \) |

| On-Resistance Flatness <sup>(5)</sup> | Dry (mon)             | $V_{DD} = 2.5V, I_{COM} = 80mA,$                                                    | 25        |                     |         | 0.1               |            |

| Oil-Resistance Platness               | R <sub>FLAT(ON)</sub> | $V_{NO} \text{ or } V_{NC} = 0.8V \ 1.8V$                                           | Full      |                     |         | 0.1               |            |

| Dynamic                               |                       |                                                                                     |           |                     |         |                   |            |

| Turn-On Time                          | t <sub>ON</sub>       | $V_{DD}$ = 2.5V, $V_{NO}$ or $V_{NC}$ = 1.8V, Figure 1                              | 25        |                     |         | 20                |            |

| Turn-On Time                          |                       |                                                                                     | Full      |                     |         | 30                |            |

| Turn-Off Time                         |                       |                                                                                     | 25        |                     |         | 12                |            |

| Turn-On Time                          | t <sub>OFF</sub>      |                                                                                     | Full      |                     |         | 15                | ns         |

| Break-Before-Make                     | $t_{ m BBM}$          | $V_{NO}$ or $V_{NC}$ = 1.5V,<br>$R_L$ = 50 $\Omega$ ,<br>$C_L$ = 35pF, See Figure 8 | 25        | 1                   | 15      |                   |            |

| Charge Injection <sup>(3)</sup>       | Q                     | $C_L = 1$ nF, $V_{GEN} = 0$ V,<br>$R_{GEN} = 0$ V, Figure 2                         | 25        |                     | 60      |                   | рC         |

| Logic Input                           |                       |                                                                                     |           |                     |         |                   |            |

| Input HIGH Voltage                    | V <sub>IH</sub>       | Guaranteed logic high level                                                         | Full      | 1.4                 |         |                   | V          |

| Input LOW Voltage                     | $V_{\rm IL}$          | Guaranteed logic Low level                                                          | Full      |                     |         | 0.5               | <u>l</u>   |

| Input HIGH Current                    | I <sub>INH</sub>      | $V_{IN} = 1.4V$ , all others = $0.5V$                                               | Full      | -1                  |         | 1                 |            |

| Input HIGH Current                    | I <sub>INL</sub>      | $V_{IN} = 0.5V$ , all others = 1.4V                                                 | Full      | -1                  |         | 1                 | μΑ         |

- 1. The algebraic convention, where most negative value is a minimum and most positive is a maximum, is used in this data sheet.

- 2. Typical values are for DESIGN AID ONLY, not guaranteed or subject to production testing.

- 3. Guaranteed by design.

- 4.  $\Delta R_{ON} = R_{ON} \text{ max.} R_{ON} \text{ min.}$

- 5. Flatness is defined as the difference between the maximum and minimum value of On-Resistance measured.

## **Electrical Specifications - Single +1.8V Supply**

$(V_{DD} = +1.8V \pm 10\%, GND = 0V, V_{INH} = 1.4V, V_{INL} = 0.5V)$

| Description                           | Parameters            | <b>Test Conditions</b>                                                              | Temp.(°C) | Min. <sup>(1)</sup> | <b>Typ.</b> <sup>(2)</sup> | Max. <sup>(1)</sup> | Units |

|---------------------------------------|-----------------------|-------------------------------------------------------------------------------------|-----------|---------------------|----------------------------|---------------------|-------|

| Analog Switch                         |                       |                                                                                     |           |                     |                            |                     |       |

| Analog Signal<br>Range <sup>(3)</sup> | V <sub>ANALOG</sub>   |                                                                                     |           | 0                   |                            | V <sub>DD</sub>     | V     |

| On-Resistance                         | R <sub>ON</sub>       |                                                                                     | 25        |                     |                            | 0.55                |       |

| OII-Resistance                        | KON                   | $V_{DD} = 1.8V, I_{COM} = 60mA,$                                                    | Full      |                     |                            | 0.7                 |       |

| On-Resistance Match                   | $\Delta R_{ m ON}$    | $V_{NO}$ or $V_{NC} = 1.5V$                                                         | 25        |                     |                            | 0.03                | Ω     |

| Between Channels (4)                  | ΔKON                  |                                                                                     | Full      |                     |                            | 0.03                |       |

| On-Resistance Flat-                   | Pri ATI(ON)           | $V_{DD} = 1.8V, I_{COM} = 60mA,$                                                    | 25        |                     |                            | 0.9                 |       |

| ness <sup>(5)</sup>                   | R <sub>FLAT(ON)</sub> | $V_{NO}$ or $V_{NC} = 0.8V$ , 1.5V                                                  | Full      |                     |                            | 1.1                 |       |

| Dynamic                               |                       |                                                                                     |           |                     |                            |                     |       |

| Turn-On Time                          | t <sub>ON</sub>       | $V_{DD} = 1.8V, V_{NO} \text{ or } V_{NC} = 1.5V,$                                  | 25        |                     |                            | 40                  |       |

| Turn-On Time                          |                       |                                                                                     | Full      |                     |                            | 50                  |       |

| Turn-Off Time                         |                       | Figure 1                                                                            | 25        |                     |                            | 12                  |       |

| Turn-OII Time                         | t <sub>OFF</sub>      |                                                                                     | Full      |                     |                            | 15                  | ns    |

| Break-Before-Make                     | t <sub>BBM</sub>      | $V_{NO}$ or $V_{NC}$ = 1.5V,<br>$R_L$ = 50 $\Omega$ ,<br>$C_L$ = 35pF, See Figure 8 | 25        | 1                   | 30                         |                     |       |

| Charge Injection <sup>(3)</sup>       | Q                     | $C_L = 1$ nF, $V_{GEN} = 0$ V,<br>$R_{GEN} = 0$ V, Figure 2                         | 25        |                     | 40                         |                     | pC    |

| <b>Logic Input</b>                    |                       |                                                                                     |           |                     |                            |                     |       |

| Input HIGH Voltage                    | V <sub>IH</sub>       | Guaranteed logic high level                                                         | Full      | 1.4                 |                            |                     | W     |

| Input LOW Voltage                     | V <sub>IL</sub>       | Guaranteed logic Low level                                                          | Full      |                     |                            | 0.5                 | V     |

| Input HIGH Current                    | I <sub>INH</sub>      | $V_{\rm IN} = 1.4 \text{V}$ , all others = 0.5 V                                    | Full      | -1                  |                            | 1                   | 4     |

| Input HIGH Current                    | I <sub>INL</sub>      | $V_{\rm IN} = 0.5 \text{V}$ , all others = 1.4 V                                    | Full      | -1                  |                            | 1                   | μΑ    |

- 1. The algebraic convention, where most negative value is a minimum and most positive is a maximum, is used in this data sheet.

- 2. Typical values are for DESIGN AID ONLY, not guaranteed or subject to production testing.

- 3. Guaranteed by design.

- 4.  $\Delta R_{ON} = R_{ON} \text{ max.} R_{ON} \text{ min.}$

- 5. Flatness is defined as the difference between the maximum and minimum value of On-Resistance measured.

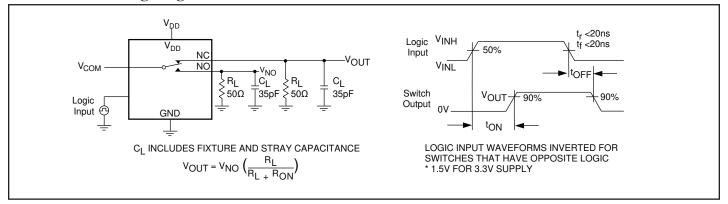

## **Test Circuits/Timing Diagrams**

Figure 1. Switching Time

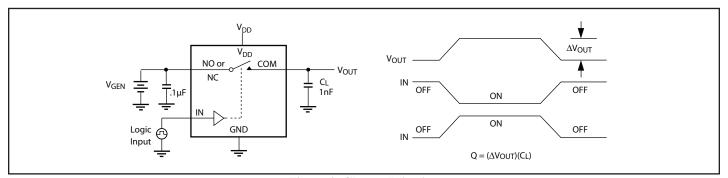

Figure 2. Charge Injection

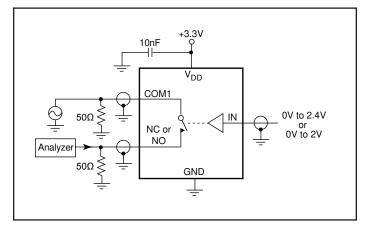

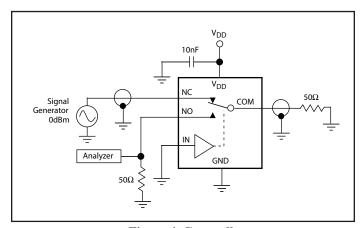

Figure 3. Off Isolation

Figure 4. Crosstalk

## Test Circuits/Timing Diagrams (continued)

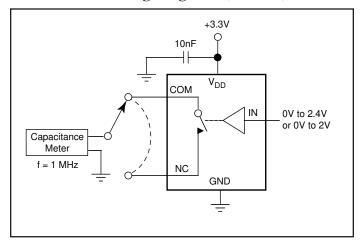

Figure 5. Channel-Off Capacitance

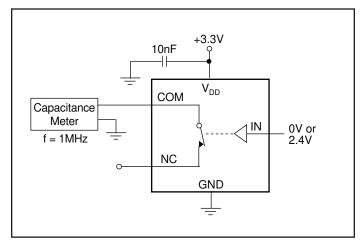

Figure 6. Channel-On Capacitance

Figure 8. Break Before Make Diagram

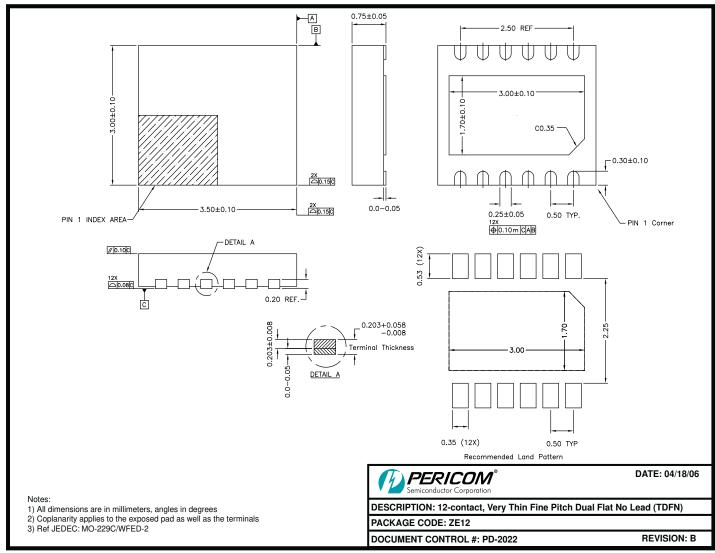

#### Packaging Mechanical: 12-Contact TDFN (ZE)

06-0360

#### Note:

• For latest package info, please check: http://www.pericom.com/products/packaging/mechanicals.php

## **Ordering Information**

| Ordering Code Package Code |    | Package Description              | Top Mark |  |

|----------------------------|----|----------------------------------|----------|--|

| PI3A3160ZEEX               | ZE | Pb-free & Green, 12-contact TDFN | YI       |  |

#### **Notes:**

- 1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- 2. X = Tape/Reel

- 3. Number of transistors = TBD

Pericom Semiconductor Corporation • 1-800-435-2336 • www.pericom.com