# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

A product Line of Diodes Incorporated

### PI3EQX1204-C

### 12.5Gbps 4-channel, SAS3 ReDriver with Linear Equalization

### Features

- → 1-12.5Gbps serial link with linear equalizer

- → Support SATA Gen1/Gen2/Gen3, SAS2/3, and XAUI protocol

- → Supporting 4 differential channels

- ➔ Handle up to 34dB channel loss (42" FR4 trace or 10 meters or SAS3 cable)

- ➔ Independent channel configuration of receiver equalization, output swing and flat gain

- → Rate and Coding Agnostic

- → Transparent to link training, OOB, Idle

- → 260mW per channel power dissipation with 700 mVpp output swing

- → Pin strap and I<sup>2</sup>C selectable device programming

- → 4-bit selectable address bit for  $I^2C$

- → Supply Voltage: 3.3V±0.3V

- → Industrial Temperature Range: -40°C to 85°C

- → Packaging (Pb-free & Green):

- 42-contact TQFN (9mm x3.5mm)

### Description

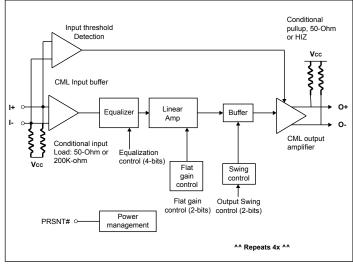

The PI3EQX1204-C is a SAS3, 4 differential channels ReDriver. The device provides programmable linear equalization, output swing and flat gain, by either pin strapping option or I<sup>2</sup>C Control, to optimize performance over a variety of physical mediums by reducing Inter-symbol interference.

PI3EQX1204-C supports four 100-Ohm Differential CML data I/O's and extends the signals across other distant data pathways on the user's platform.

The integrated equalization circuitry provides flexibility with signal integrity of the signal before the ReDriver, whereas the integrated linear amplifier/buffer circuitry provides flexibility with signal integrity of the signal after the ReDriver.

### Application

Rack Server, JBOD storage

### Block Diagram

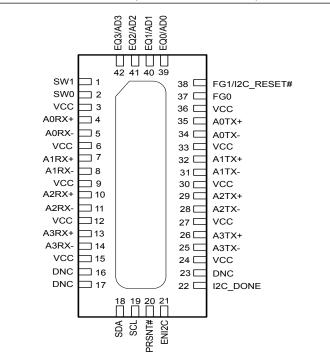

### Pin Configuration (Top-Side View)

### **Pin Description**

| Pin #           | Pin Name                | Туре | Description                                                                                                                                                                                                                                                                                                |  |  |  |

|-----------------|-------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Data Signals    |                         |      |                                                                                                                                                                                                                                                                                                            |  |  |  |

| 4               | A0RX+                   | Ι    | CML inputs for Channel A0, with internal 50-Ohm pull-up and ~200K-Ohm                                                                                                                                                                                                                                      |  |  |  |

| 5               | A0RX-                   | Ι    | pull-up otherwise.                                                                                                                                                                                                                                                                                         |  |  |  |

| 35              | A0TX+                   | 0    | CML outputs for Channel A0, with internal 50-Ohm pull-up and high                                                                                                                                                                                                                                          |  |  |  |

| 34              | A0TX-                   | 0    | impedance otherwise.                                                                                                                                                                                                                                                                                       |  |  |  |

| 7               | A1RX+                   | Ι    | CML inputs for Channel A1, with internal 50-Ohm pull-up and ~200K-Ohm                                                                                                                                                                                                                                      |  |  |  |

| 8               | A1RX-                   | Ι    | otherwise.                                                                                                                                                                                                                                                                                                 |  |  |  |

| 32              | A1TX+                   | 0    | CML outputs for Channel A1, with internal 50-Ohm pull-up and high                                                                                                                                                                                                                                          |  |  |  |

| 31              | A1TX-                   | 0    | impedance otherwise.                                                                                                                                                                                                                                                                                       |  |  |  |

| 10              | A2RX+                   | Ι    | CML inputs for Channel A2, with internal 50-Ohm pull-up and ~200K-Ohm                                                                                                                                                                                                                                      |  |  |  |

| 11              | A2RX-                   | Ι    | otherwise.                                                                                                                                                                                                                                                                                                 |  |  |  |

| 29              | A2TX+                   | 0    | CML outputs for Channel A2, with internal 50-Ohm pull-up and high                                                                                                                                                                                                                                          |  |  |  |

| 28              | A2TX-                   | 0    | impedance otherwise.                                                                                                                                                                                                                                                                                       |  |  |  |

| 13              | A3RX+                   | Ι    | CML inputs for Channel A3, with internal 50-Ohm pull-up and ~200K-Ohm                                                                                                                                                                                                                                      |  |  |  |

| 14              | A3RX-                   | Ι    | otherwise.                                                                                                                                                                                                                                                                                                 |  |  |  |

| 26              | A3TX+                   | 0    | CML outputs for Channel A3, with internal 50-Ohm pull-up and high                                                                                                                                                                                                                                          |  |  |  |

| 25              | A3TX-                   | 0    | impedance otherwise.                                                                                                                                                                                                                                                                                       |  |  |  |

| Control Signals |                         |      |                                                                                                                                                                                                                                                                                                            |  |  |  |

| 19              | SCL                     | I/O  | I <sup>2</sup> C SCL Clock. In Master mode (ENI2C floating), SCL is an output. Otherwise it is an input.                                                                                                                                                                                                   |  |  |  |

| 18              | SDA                     | I/O  | I <sup>2</sup> C SDA data input/output.                                                                                                                                                                                                                                                                    |  |  |  |

| 42, 41, 40, 39  | AD[3:0]                 | Ι    | I <sup>2</sup> C programmable address bits, with internal 100k-Ohm pull-up.                                                                                                                                                                                                                                |  |  |  |

| 20              | PRSNT#                  | I    | This pin is active in both PIN mode(ENI2C=LOW) and I <sup>2</sup> C mode<br>(ENI2C=HIGH). Cable present detect input. This pin has internal 100K-ohm<br>pull-up. When High, a cable is not present, and the device is put in lower power<br>mode. When LOW, the device is enabled and in normal operation. |  |  |  |

| 21              | ENI2C                   | Ι    | When LOW, each channel is programmed by the external pin voltage.<br>When HIGH, each channel is programmed by the data stored in the I <sup>2</sup> C bus.<br>When floating, master mode (Read External EEPROM)                                                                                            |  |  |  |

| 42, 41, 40, 39  | EQ[3:0]                 | Ι    | Inputs with internal 100k-Ohm pull-up. This pins set the amount of Equalizer<br>Boost in all channel when ENI2C is LOW.                                                                                                                                                                                    |  |  |  |

| 1, 2            | SW[1:0]                 | Ι    | Inputs with internal 100k-Ohm pull-up. This pin sets the output Voltage Level in all channel when ENI2C is LOW.                                                                                                                                                                                            |  |  |  |

| 38, 37          | FG[1:0]                 | Ι    | Inputs with internal $100K\Omega$ pull up resistor. Sets the output flat gain level on all channels when ENI2C is low.                                                                                                                                                                                     |  |  |  |

| 38              | I <sup>2</sup> C_RESET# | Ι    | Inputs with internal 100K $\Omega$ pull up resistor. Reset pin for I <sup>2</sup> C. When set low will reset the registers to default state.                                                                                                                                                               |  |  |  |

| Pin #                                  | Pin Name              | Туре | Description                                                                                                                              |

|----------------------------------------|-----------------------|------|------------------------------------------------------------------------------------------------------------------------------------------|

| 22                                     | I <sup>2</sup> C_DONE | 0    | Valid register load status output, use for daisy chain master<br>LOW = External EEPROM load failed<br>HIGH = External EEPROM load passed |

| 16, 17, 23                             | DNC                   |      | Do Not Connect                                                                                                                           |

| Power Pins                             |                       |      |                                                                                                                                          |

| 3, 6, 9, 12, 15, 24,<br>27, 30, 33, 36 | V <sub>CC</sub>       | PWR  | 3.3V Supply Voltage                                                                                                                      |

| ЕР                                     | GND                   | PWR  | Exposed pad. Supply Ground                                                                                                               |

### **Description of Operation**

### **Power Enable function:**

One pin control or I<sup>2</sup>C control, when PRSNT# is set to HIGH, the IC goes into power down mode, both input and output termination set to 200K and High impedance respectively. Individual Channel Enabling is done through the I<sup>2</sup>C register programming.

### **Equalization Setting:**

EQ[3:0] are the selection pins for the equalization selection for each channel.

### **Table 1. Equalization Setting**

|     | Equalizer setting |     |     |        |        |        |        |  |  |

|-----|-------------------|-----|-----|--------|--------|--------|--------|--|--|

| EQ3 | EQ2               | EQ1 | EQ0 | @ 3GHz | @ 4GHz | @ 5GHz | @ 6GHz |  |  |

| 0   | 0                 | 0   | 0   | 3.6    | 4.5    | 5.5    | 6.8    |  |  |

| 0   | 0                 | 0   | 1   | 4      | 5.1    | 6.2    | 7.6    |  |  |

| 0   | 0                 | 1   | 0   | 4.4    | 5.6    | 6.9    | 8.4    |  |  |

| 0   | 0                 | 1   | 1   | 4.7    | 6.1    | 7.5    | 9.1    |  |  |

| 0   | 1                 | 0   | 0   | 5.1    | 6.6    | 8.1    | 9.8    |  |  |

| 0   | 1                 | 0   | 1   | 5.5    | 7.1    | 8.7    | 10.4   |  |  |

| 0   | 1                 | 1   | 0   | 5.9    | 7.6    | 9.2    | 11     |  |  |

| 0   | 1                 | 1   | 1   | 6.2    | 8      | 9.7    | 11.5   |  |  |

| 1   | 0                 | 0   | 0   | 6.6    | 8.5    | 10.2   | 12     |  |  |

| 1   | 0                 | 0   | 1   | 6.9    | 8.9    | 10.7   | 12.5   |  |  |

| 1   | 0                 | 1   | 0   | 7.3    | 9.3    | 11.1   | 12.9   |  |  |

| 1   | 0                 | 1   | 1   | 7.6    | 9.7    | 11.5   | 13.3   |  |  |

| 1   | 1                 | 0   | 0   | 8      | 10.1   | 11.9   | 13.7   |  |  |

| 1   | 1                 | 0   | 1   | 8.2    | 10.5   | 12.3   | 14.1   |  |  |

| 1   | 1                 | 1   | 0   | 8.6    | 10.8   | 12.7   | 14.4   |  |  |

| 1   | 1                 | 1   | 1   | 8.9    | 11.1   | 13     | 14.7   |  |  |

A product Line of Diodes Incorporated

**PI3EQX1204-C**

### Flat Gain Setting:

FG[1:0] are the selection bits for the DC value.

### Table 2. Flat Gain Setting

| Flat Gain Setting |     |      |  |  |  |

|-------------------|-----|------|--|--|--|

| FG1               | FG0 | dB   |  |  |  |

| 0                 | 0   | -3.5 |  |  |  |

| 0                 | 1   | -1.5 |  |  |  |

| 1                 | 0   | 0.5  |  |  |  |

| 1                 | 1   | 2.5  |  |  |  |

### Swing Setting:

Swing Setting: SW[1:0] are the selection bits for the output swing value.

### Table 3. Swing Setting

| SW1 | SW0 | mVp-p |

|-----|-----|-------|

| 0   | 0   | 700   |

| 0   | 1   | 800   |

| 1   | 0   | 900   |

| 1   | 1   | 1000  |

### I<sup>2</sup>C Programming

| Address | assignmen | t        |             |     |                     |     |                 |                 |  |

|---------|-----------|----------|-------------|-----|---------------------|-----|-----------------|-----------------|--|

| A6      | A5        | A        | 4           | A3  | A2                  | A1  | A0              | R/W             |  |

| 1       | 1         | 1        |             | AD3 | AD2                 | AD1 | AD0             | 1=R, 0=W        |  |

| BYTE 0  | Reserved  |          |             |     |                     |     |                 |                 |  |

| BYTE 1  | Reserved  |          |             |     |                     |     |                 |                 |  |

| BYTE 2  |           |          |             |     |                     |     |                 |                 |  |

| Bit     | Туре      | Power up | condition   |     |                     | С   | ontrol affected | Comment         |  |

| 7       | R/W       | 0        |             |     |                     | A   | 3 Power down    |                 |  |

| 6       | R/W       | 0        |             |     |                     | A   | 2 Power down    |                 |  |

| 5       | R/W       | 0        |             |     |                     | A   | 1 Power down    |                 |  |

| 4       | R/W       | 0        |             |     |                     | A   | ) Power down    | 1 Dergen der    |  |

| 3       | R/W       | 0        |             |     |                     |     |                 | -1 = Power down |  |

| 2       | R/W       | 0        |             |     |                     |     |                 |                 |  |

| 1       | R/W       | 0        |             |     |                     |     |                 |                 |  |

| 0       | R/W       | 0        |             |     |                     |     |                 |                 |  |

| BYTE 3  |           |          |             | ·   |                     |     |                 | ·               |  |

| Bit     | Туре      | Power up | condition   |     |                     | C   | ontrol affected | Comment         |  |

| 7       | R/W       | 0        |             |     |                     | E   | Q3              |                 |  |

| 6       | R/W       | 0        |             |     |                     | E   | Q2              | – Equalizer     |  |

| 5       | R/W       | 0        |             |     |                     | E   | Q1              |                 |  |

| 4       | R/W       | 0        |             | C   | annal A0 configur   | E   | Q0              |                 |  |

| 3       | R/W       | 0        |             |     | nannel A0 configura | F   | G1              |                 |  |

| 2       | R/W       | 0        |             |     |                     | F   | G0              | — Flat gain     |  |

| 1       | R/W       | 0        |             |     |                     | SV  | W1              | Suring          |  |

| 0       | R/W       | 0        |             |     |                     | SV  | W0              | — Swing         |  |

| BYTE 4  |           |          |             | i   |                     |     |                 |                 |  |

| Bit     | Туре      | Power up | o condition |     |                     | C   | ontrol affected | Comment         |  |

| 7       | R/W       | 0        |             |     |                     | E   | Q3              |                 |  |

| 6       | R/W       | 0        |             |     |                     | E   | Q2              | Equalizer       |  |

| 5       | R/W       | 0        |             |     |                     | E   | Q1              | Equanzer        |  |

| 4       | R/W       | 0        |             |     | annal Al conferm    | E   | Q0              |                 |  |

| 3       | R/W       | 0        |             |     | nannel A1 configura | F   | G1              | Elat asi:       |  |

| 2       | R/W       | 0        |             |     |                     | F   | G0              | — Flat gain     |  |

| 1       | R/W       | 0        |             |     |                     | SV  | W1              | Servin -        |  |

|         |           |          |             |     |                     |     |                 | Swing           |  |

### I<sup>2</sup>C Programming cont.

| Bit              | Туре                                                        | Power up condition |                                                                      | Control affected         | Comment                    |

|------------------|-------------------------------------------------------------|--------------------|----------------------------------------------------------------------|--------------------------|----------------------------|

| 7                | R/W                                                         | 0                  |                                                                      | EQ3                      |                            |

| 6                | R/W                                                         | 0                  | n Channel A2 configuration<br>FG FG | EQ2                      |                            |

| 5                | R/W                                                         | 0                  |                                                                      | EQ1                      | – Equalizer                |

| 4                | R/W                                                         | 0                  |                                                                      | EQ0                      |                            |

| 3                | R/W                                                         | 0                  |                                                                      | FG1                      |                            |

| 2                | R/W                                                         | 0                  |                                                                      | FG0                      | – Flat gain                |

| 1                | R/W                                                         | 0                  |                                                                      | SW1                      | Continue                   |

| 0                | R/W                                                         | 0                  |                                                                      | SW0                      | - Swing                    |

| BYTE             | 5                                                           |                    |                                                                      |                          |                            |

| Bit              | Туре                                                        | Power up condition |                                                                      | Control affected         | Comment                    |

| 7                | R/W                                                         | 0                  |                                                                      | EQ3                      |                            |

| /                | 10/ 11                                                      | -                  |                                                                      | LQJ                      |                            |

| 6                | R/W                                                         | 0                  |                                                                      | EQ2                      | -<br>-                     |

|                  |                                                             |                    |                                                                      |                          | –<br>– Equalizer           |

| 6                | R/W                                                         | 0                  |                                                                      | EQ2                      | –<br>– Equalizer<br>–      |

| 6<br>5           | R/W<br>R/W                                                  | 0 0                | Channel A3 configuration                                             | EQ2<br>EQ1               | _                          |

| 6<br>5<br>4<br>3 | R/W<br>R/W<br>R/W                                           | 0<br>0<br>0        | Channel A3 configuration                                             | EQ2<br>EQ1<br>EQ0        | – Equalizer<br>– Flat gain |

| 6<br>5<br>4      | R/W           R/W           R/W           R/W           R/W | 0<br>0<br>0<br>0   | Channel A3 configuration                                             | EQ2<br>EQ1<br>EQ0<br>FG1 | _                          |

A product Line of Diodes Incorporated

PI3EQX1204-C

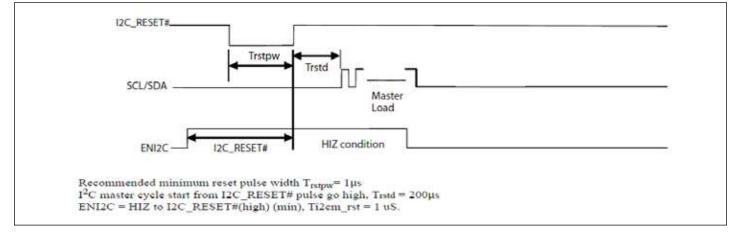

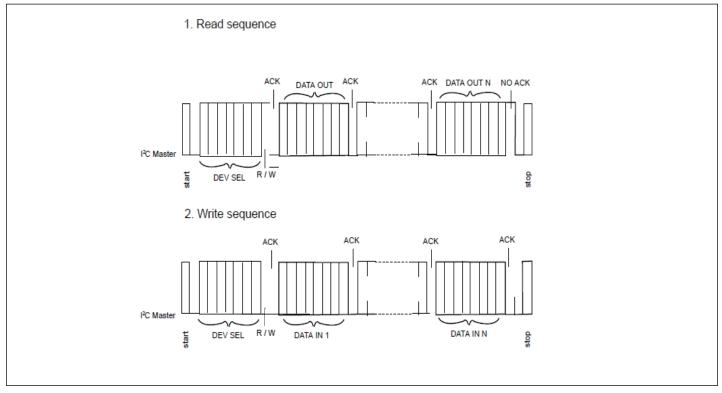

### **Reset and I<sup>2</sup>CM Timing Diagram**

### I<sup>2</sup>C Operation

The integrated I<sup>2</sup>C interface operates as a master or slave device depending on the pin ENI2C being HIZ or HIGH respectively. Standard mode (100Kbps) is supported with 7-bit addressing. The data byte format is 8-bit bytes, and supports the format of indexing to be compatible with other bus devices. In the Slave mode (ENI2C = HIGH), the device supports Read/Write. The bytes must be accessed in sequential order from the lowest to the highest byte with the ability to stop after any complete byte has been transferred. Address bits A3 to A0 are programmable to support multiple chips environment. The Data is loaded until a Stop sequence is issued.

In the master mode (ENI2C = HIZ), PI3EQX1204-C supports up to 16 masters connected in daisy chain through connecting  $I^2C_DONE$  pin to  $I^2C_RESET\#$  pin of the next part.

| I <sup>2</sup> C address: |                        |

|---------------------------|------------------------|

| AD3, AD2, AD1, AD0        | Data starting location |

| 0000                      | 00H                    |

| 0001                      | 10H                    |

| 0010                      | 20H                    |

| 0011                      | 30H                    |

| 0100                      | 40H                    |

| 0101                      | 50H                    |

| 0110                      | 60H                    |

| 0111                      | 70H                    |

| 1000                      | 80H                    |

| 1001                      | 90H                    |

| 1010                      | A0H                    |

| 1011                      | B0H                    |

| 1100                      | С0Н                    |

| 1101                      | D0H                    |

| 1110                      | E0H                    |

| 1111                      | F0H                    |

Master EEPROM data starting address for device address:

Transferring Data

Every byte put on the SDA line must be 8-bits long. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit (MSB) first (see the I<sup>2</sup>C Data Transfer diagram). The PI3EQX1204-C will never hold the clock line SCL LOW to force the master into a wait state.

### Acknowledge

Data transfer with acknowledge is required from the master. When the master releases the SDA line (HIGH) during the acknowledge clock pulse, the PI3EQX1204-C will pull down the SDA line during the acknowledge clock pulse so that it remains stable LOW during the HIGH period of this clock pulse as indicated in the I2C Data Transfer diagram. The PI3EQX1204-C will generate an acknowledge after each byte has been received.

### Data Transfer

A data transfer cycle begins with the master issuing a start bit. After recognizing a start bit, the PI3EQX1204-C will watch the next byte of information for a match with its address setting. When a match is found it will respond with a read or write of data on the following clocks. Each byte must be followed by an acknowledge bit, except for the last byte of a read cycle which ends with a stop bit. For a write cycle, the first data byte following the address byte is an index byte that is used by the PI3EQX1204-C. Data is transferred with the most significant bit (MSB) first.

### **12C Data Transfer**

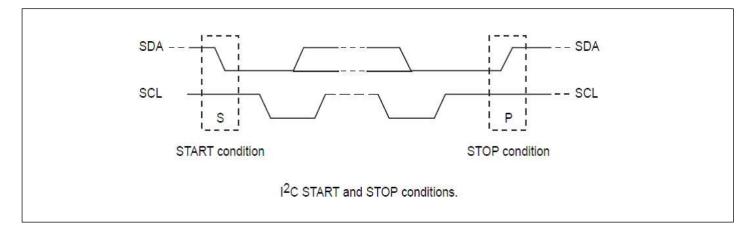

### Start & Stop Conditions

A HIGH to LOW transition on the SDA line while SCL is HIGH indicates a START condition. A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition, as shown in the figure below

### I<sup>2</sup>C Data Transfer

### Maximum Ratings

(Above which useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature65°C to +150°C                                                 |

|-----------------------------------------------------------------------------------|

| Supply Voltage to Ground Potential0.5V to +4.6V                                   |

| DC SIG Voltage $\ldots \ldots \ldots \ldots \ldots -0.5V$ to $V_{CC}\text{+}0.5V$ |

| Output Current25mA to +25mA                                                       |

| Power Dissipation Continuous2.1W                                                  |

| Junction Temperature Tj 125°C                                                     |

| ESD, HBM2kV to +2kV                                                               |

Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Electrical characteristics:**

### LVCMOS I/O DC Specifications ( $V_{CC} = 3.3 \pm 0.3 V$ , $T_A = -40$ to $85^{\circ}$ C)

| Symbol           | Parameter                           | Conditions | Min.               | Тур. | Max                      | Units |

|------------------|-------------------------------------|------------|--------------------|------|--------------------------|-------|

| V <sub>IH</sub>  | DC input logic high                 |            | $V_{\rm CC}/2+0.7$ |      | $V_{\rm C}C + 0.3$       | V     |

| V <sub>IL</sub>  | DC input logic low                  |            | -0.3               |      | V <sub>CC</sub> /2 - 0.7 | v     |

| V <sub>OH</sub>  | At IOH = -200μA                     |            | $V_{CC} + 0.2$     |      |                          | V     |

| V <sub>OL</sub>  | At IOL = $-200\mu$ A                |            |                    |      | 0.2                      | v     |

| V <sub>hys</sub> | Hysteresis of Schmitt trigger input |            | 0.8                |      |                          | v     |

### SDA and SCL I/O for I2C-bus (V\_{CC} = 3.3 $\pm$ 0.3V, T\_A = -40 to 85°C)

| Symbol            | Parameter                                                     | Conditions     | Min.             | Тур. | Max.                     | Units |

|-------------------|---------------------------------------------------------------|----------------|------------------|------|--------------------------|-------|

| V <sub>IH</sub>   | DC input logic high                                           |                | $V_{CC}/2 + 0.7$ |      | V <sub>CC</sub> + 0.3    | V     |

| V <sub>IL</sub>   | DC input logic low                                            |                | -0.3             |      | V <sub>CC</sub> /2 - 0.7 | V     |

| V <sub>OL</sub>   | DC output logic low                                           | $I_{OL} = 3mA$ |                  |      | 0.4                      | V     |

| V <sub>hys</sub>  | Hysteresis of Schmitt trigger input                           |                | 0.8              |      |                          | V     |

| t <sub>of</sub>   | Output fall time from VIHmin to VILmax with bus cap. 10-400pF |                |                  |      | 250                      | ns    |

| f <sub>SCLK</sub> | SCLK clock frequency                                          |                |                  |      | 100                      | kHz   |

### High speed I/O AC/DC Specifications ( $V_{CC} = 3.3 \pm 0.3 V$ , $T_A = -40$ to $85^{\circ}$ C)

| Symbol          | Parameter                       | Conditions                                                                                                                                                                        | Min. | Тур. | Max. | Units |  |

|-----------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|--|

| C <sub>RX</sub> | RX AC coupling capacitance      |                                                                                                                                                                                   |      | 220  |      | nF    |  |

| 0               | T                               | 10MHz to 6GHz differential                                                                                                                                                        |      | 11.0 |      | 10    |  |

| S <sub>11</sub> | Input return loss               | 100 Hz to 6GHz differential       11.0         100 Hz to 6GHz common mode       5.0         100 Hz to 6GHz differential       11.5         110 Hz to 6GHz differential       11.5 |      | dB   |      |       |  |

| 0               |                                 | 10MHz to 6GHz differential                                                                                                                                                        |      | 11.5 |      | 10    |  |

| S <sub>22</sub> | Output return loss              | 1GHz to 6GHz common mode                                                                                                                                                          |      | 4.8  | 0    | dB    |  |

| D               | DC single-ended input impedance |                                                                                                                                                                                   |      | 50   |      | 0     |  |

| R <sub>IN</sub> | DC Differential Input Impedance |                                                                                                                                                                                   |      | 100  |      | Ω     |  |

### High speed I/O AC/DC Specifications cont.

| Symbol                                | Parameter                                                                               | Conditions                             | Min. | Тур. | Max. | Units |  |  |

|---------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------|------|------|------|-------|--|--|

| R <sub>OUT</sub>                      | DC single-ended output impedance                                                        |                                        | 50   |      |      |       |  |  |

|                                       | DC Differential output Impedance                                                        |                                        |      | 100  |      | Ω     |  |  |

| Z <sub>RX-HIZ</sub>                   | DC input CM input impedance during reset or power down                                  |                                        |      | 200  |      | kΩ    |  |  |

| V <sub>RX-DIFF-PP</sub>               | Differential Input Peak-to-peak Volt-<br>age                                            | Operational                            |      |      | 1.2  | Vppd  |  |  |

|                                       | Input source common-mode noise                                                          | DC – 200MHz                            |      |      | 150  | mVpp  |  |  |

| T <sub>TX-IDLE-SET-TO-</sub><br>IDLE  | Max time to electrical idle after send-<br>ing an EIOS                                  |                                        |      | 4    | 8    | ns    |  |  |

| T <sub>TX-IDLE-TO-DIFF-</sub><br>DATA | Max time to valid diff signal after leav-<br>ing electrical idle                        |                                        |      | 4    | 8    | ns    |  |  |

| Vcc                                   | Power supply voltage                                                                    |                                        | 3    | 3.3  | 3.6  | V     |  |  |

| P <sub>max</sub>                      | Max Supply power                                                                        | PRSNT#=0                               |      |      | 1.3  | W     |  |  |

| I <sub>max</sub>                      | Max Supply current                                                                      |                                        |      |      | 360  | mA    |  |  |

| P <sub>idle</sub>                     | Supply power                                                                            | PRSNT#=1                               |      |      | 14.4 | mW    |  |  |

| t <sub>pd</sub>                       | Latency                                                                                 | From input to output                   |      | 0.5  |      | ns    |  |  |

| Gp                                    | Peaking gain (Compensation at 6GHz,<br>relative to 100MHz, 100mVp-p sine<br>wave input) | EQ<3:0> = 1111                         |      | 15.4 |      | dB    |  |  |

|                                       |                                                                                         | EQ<3:0> = 1000                         |      | 12.5 |      |       |  |  |

|                                       |                                                                                         | EQ<3:0> = 0000                         |      | 7.1  |      |       |  |  |

|                                       |                                                                                         | Variation around typical               | -3   |      | +3   | dB    |  |  |

|                                       | Flat gain (100MHz, EQ<3:0> = 1000,<br>SW<1:0> = 10)                                     | FG<1:0> = 11                           |      | 2    |      |       |  |  |

|                                       |                                                                                         | FG<1:0> = 10                           |      | 0    |      | dB    |  |  |

| G <sub>F</sub>                        |                                                                                         | FG<1:0> = 01                           |      | -2   |      |       |  |  |

|                                       |                                                                                         | FG<1:0> = 00                           |      | -4   |      |       |  |  |

|                                       |                                                                                         | Variation around typical               | -3   |      | +3   | dB    |  |  |

| V1dB_100M                             | -1dB compression point of output<br>swing (at 100MHz)                                   | SW<1:0> = 11                           |      | 1370 |      |       |  |  |

|                                       |                                                                                         | SW<1:0> = 10                           |      | 1280 |      | mVppd |  |  |

|                                       |                                                                                         | SW<1:0> = 01                           |      | 1040 |      |       |  |  |

|                                       |                                                                                         | SW<1:0> = 00                           |      | 920  |      |       |  |  |

| V <sub>1dB_6G</sub>                   | -1dB compression point of output<br>swing (at 6GHz)                                     | SW<1:0> = 11                           |      | 1000 |      |       |  |  |

|                                       |                                                                                         | SW<1:0> = 10                           |      | 940  |      |       |  |  |

|                                       |                                                                                         | SW<1:0> = 01                           |      | 700  |      | mVppd |  |  |

|                                       |                                                                                         | SW<1:0> = 00                           |      | 600  |      |       |  |  |

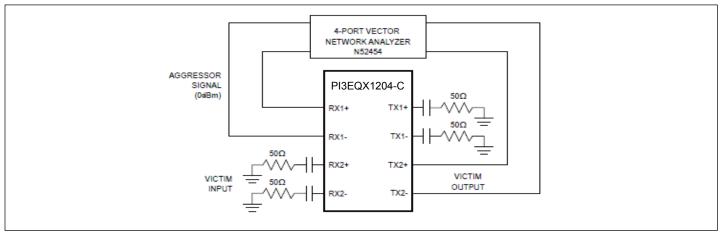

| V <sub>Coup</sub>                     | Channel isolation                                                                       | 100MHz to 6GHz, Figure 1<br>(Note 1)25 |      |      | dB   |       |  |  |

### High speed I/O AC/DC Specifications cont.

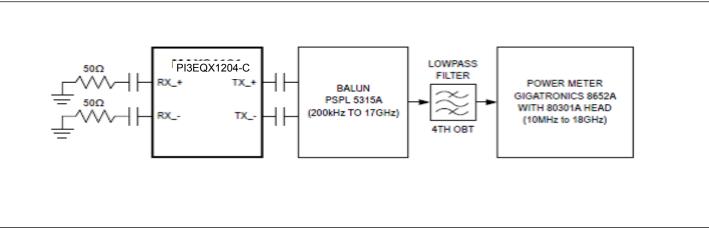

| Symbol        | Parameter                      | Conditions                                                | Min. | Тур. | Max.    | Units             |

|---------------|--------------------------------|-----------------------------------------------------------|------|------|---------|-------------------|

| Vnoise_input  | Input-referred noise           | 100MHz to 6GHz, FG<1:0> =<br>11, EQ<3:0> = 0000, Figure 2 |      | 0.5  |         | mV <sub>RMS</sub> |

|               |                                | 100MHz to 6GHz, FG<1:0> =<br>11, EQ<3:0> = 1010, Figure 2 |      | 0.4  |         |                   |

| Vnoise_output |                                | 100MHz to 6GHz, FG<1:0> =<br>11, EQ<3:0> = 0000, Figure 2 |      | 0.7  |         |                   |

|               | Output-referred noise (Note 2) | 100MHz to 6GHz, FG<1:0> =<br>11, EQ<3:0> = 1010, Figure 2 |      | 0.8  | 0.8 1.6 | mV <sub>RMS</sub> |

Note: (1) Measured using a vector-network analyzer (VNA) with -15dBm power level applied to the adjacent input. The VNA detects the signal at the output of the victim channel. All other inputs and outputs are terminated with  $50\Omega$ .

(2) Guaranteed by design and characterization.

Figure 1. Channel-isolation test configuration

A product Line of Diodes Incorporated

PI3EQX1204-C

### **ESD Specification**

- 2000V HBM

- 500V CDM

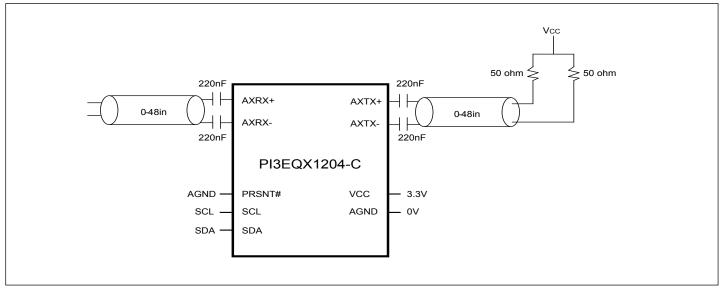

### **Application Diagram**

### AC/DC Specifications - SCL/SDA for I<sup>2</sup>C BUS

| Symbol          | Parameter                                                                                       | Conditions               | Min.                     | Тур. | Max                      | Units |

|-----------------|-------------------------------------------------------------------------------------------------|--------------------------|--------------------------|------|--------------------------|-------|

| V <sub>IH</sub> | DC input logic high                                                                             |                          | V <sub>CC</sub> /2 + 0.7 |      | V <sub>CC</sub> + 0.3    | V     |

| V <sub>IL</sub> | DC input logic low                                                                              |                          | -0.3                     |      | V <sub>CC</sub> /2 - 0.7 | V     |

| V <sub>OL</sub> | DC output logic low                                                                             | $I_{OL} = 3mA$           |                          |      | 0.4                      | V     |

| Ipullup         | Current Through Pull-Up Resistor<br>or Current Source                                           | High Power specification | 3.0                      |      | 3.6                      | mA    |

| VDD             | Nominal Bus Voltage                                                                             |                          | 3.0                      |      | 3.6                      | V     |

| Ileak-bus       | Input leakage per bus segment                                                                   |                          | -200                     |      | 200                      | uA    |

| Ileak-pin       | Input leakage per device pin                                                                    |                          |                          | -15  |                          | uA    |

| CI              | Capacitance for SDA/SCL                                                                         |                          |                          |      | 10                       | pF    |

| Freq            | Bus Operation Frequency                                                                         |                          |                          |      | 100k                     | Hz    |

| TBUF            | "Bus Free Time<br>Between Stop and Start condition"                                             |                          | 1.3                      |      |                          | us    |

| THD:STA         | Hold time after (Repeated) Start condition.<br>After this period, the first clock is generated. | At Ipull-up, Max         | 0.6                      |      |                          | us    |

| TSU:STA         | Repeated start conidtion setup time                                                             |                          | 0.6                      |      |                          | us    |

| TSU:STO         | Stop condition setup time                                                                       |                          | 0.6                      |      |                          | us    |

| THD:DAT         | Data hold time                                                                                  |                          | 0                        |      |                          | ns    |

| TSU:DAT         | Data setup time                                                                                 |                          | 100                      |      |                          | ns    |

| Tlow            | Clock low period                                                                                |                          | 1.3                      |      |                          | us    |

| Thigh           | Clock high period                                                                               |                          | 0.6                      |      | 50                       | us    |

| tF              | Clock/Data fall time                                                                            |                          |                          |      | 300                      | ns    |

| tR              | Clock/Data rise time                                                                            |                          |                          |      | 300                      | ns    |

| tpor            | "Time in which a device must be operation after power-on reset"                                 |                          |                          |      | 500                      | ms    |

Note: (1) Recommended value.

(2) Recommended maximum capacitance load per bus segment is 400pF.

(3) Compliant to I2C physical layer specification.

(4) Ensured by Design. Parameter not tested in production.

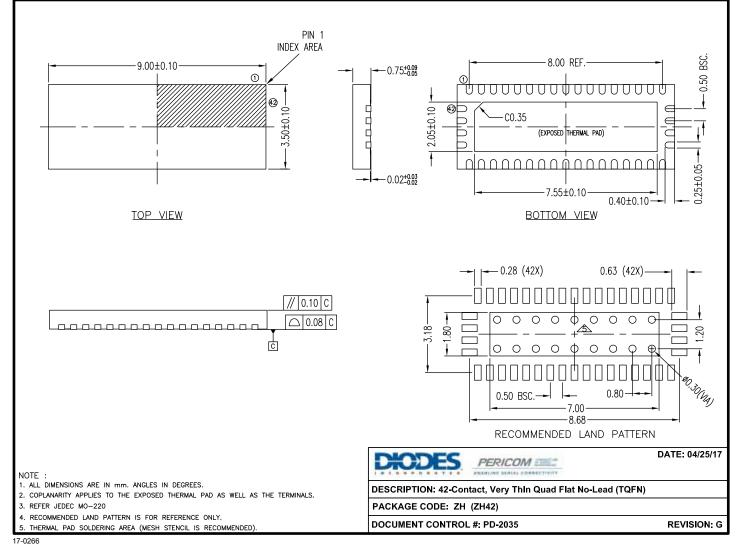

### Package Mechanical: 42-Contact TQFN (ZH)

Note: For latest package info, please check: https://www.diodes.com/design/support/packaging/pericom-packaging/

### **Ordering Information**

| Ordering Number  | Package Code | Package Description                                               |

|------------------|--------------|-------------------------------------------------------------------|

| PI3EQX1204-CZHE  | ZH           | 42-Contact, Thin Fine Pitch Quad Flat No-Lead (TQFN)              |

| PI3EQX1204-CZHEX | ZH           | 42-Contact, Thin Fine Pitch Quad Flat No-Lead (TQFN), Tape & Reel |

Notes:

• Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

• E = Pb-free and Green

• X suffix = Tape/Reel

### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND. EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application. Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

A. Life support devices or systems are devices or systems which:

1. are intended to implant into the body, or

2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the

failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated www.diodes.com