# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### 8-channel PCI Express Gen 3, 10GbE, SATA3 ReDriver™ with Linear Equalization

#### **Features**

- → High-speed serial link with linear equalizer

- → Support PCIe Gen 1/2/3 protocol, 10GbE, SATA3, SAS3

- → Supporting 8 differential channels

- → Independent channel configuration of receiver equalization, output swing and flat gain

- → Per Channel Activity Detector with selectable input termination between 50 $\Omega$  to V<sub>DD</sub> and 200K $\Omega$  to V<sub>DD</sub>

- → Per Channel Output Termination Detector on power up with selectable output termination between 50 $\Omega$  to V<sub>DD</sub> and High impedance

- → Very linear transfer function

- → Fully compliant to PCISIG Link Training

- → Single-ended mode receiver detection for PCIe

- → Input Threshold detection

- $\rightarrow$  Pin strap and I<sup>2</sup>C master/slave selectable device programming with external EEPROM

- $\rightarrow$  4-bit selectable address bit for I<sup>2</sup>C

- → Supply Voltage: 3.3V±0.3V

- → Industrial Temperature Range: -40°C to 85°C

- → Packaging (Pb-free & Green):

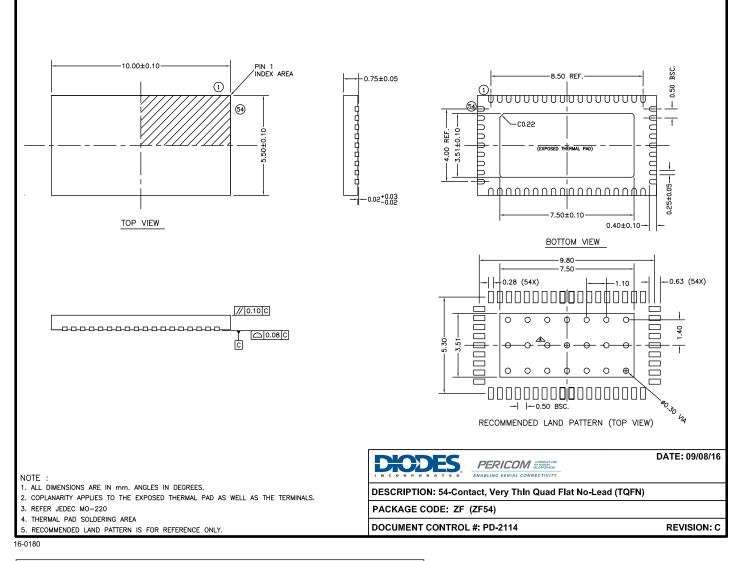

- <sup>o</sup> 54-contact TQFN (10mm x 5.5mm x 0.5mm pitch) flowthrough pinout

#### Description

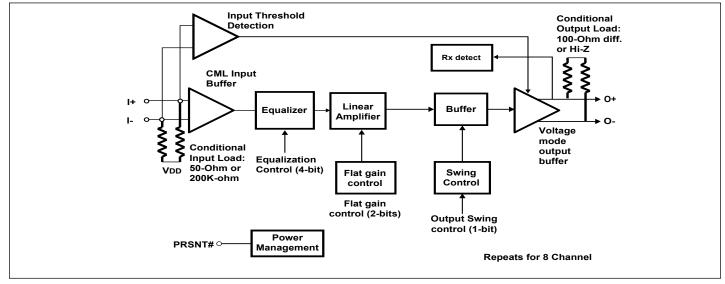

The PI3EQX12908A2 is an 8-channel PCIe Gen 2, 10GbE, SATA3, ReDriver<sup>™</sup>. The device provides programmable linear equalization, output swing and gain, by either pin strapping option or I<sup>2</sup>C Control, to optimize performance over a variety of physical mediums by reducing Inter-symbol interference.

The PI3EQX12908A2 supports eight 100-Ohm Differential CML data I/O's and extends the signals across other distant data pathways on the user's platform.

The programmable settings can be applied easily via pins, software (I<sup>2</sup>C) or loaded via an external EEPROM. When operating in the EEPROM mode, the configuration information is automatically loaded on power up, which eliminates the need for an external microprocessor or software driver.

The PI3EQX12908A2 offers fully Linear Transfer function to fully comply with all PCIe 3 Link Training signals.

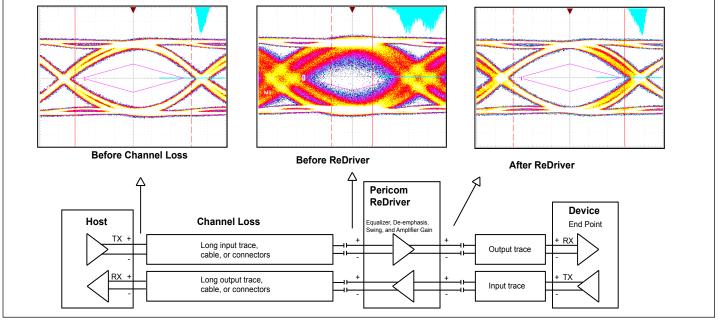

## Eye Diagram

#### **Block Diagram**

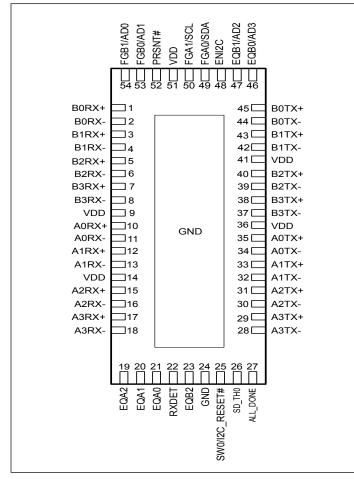

#### Pin Configuration - Top View (54-TQFN)

#### **Pin Description**

(Flow-Thru Pinout)

| Pin # (54-TQFN) | Pin Name | Туре     | Description                                                                    |

|-----------------|----------|----------|--------------------------------------------------------------------------------|

| Data Signals    | ,        | <u>.</u> |                                                                                |

| 10              | A0RX+    | Ι        | Differential inputs for Channel A0, with internal 50-Ohm pull-up and >200K-Ohm |

| 11              | A0RX-    | Ι        | otherwise.                                                                     |

| 35              | A0TX+,   | 0        |                                                                                |

| 34              | A0TX-    | 0        | Differential outputs for Channel A0                                            |

| 12              | A1RX+,   | Ι        | Differential inputs for Channel A1, with internal 50-Ohm pull-up and >200K-Ohm |

| 13              | A1RX-    | Ι        | otherwise.                                                                     |

| 33              | A1TX+,   | 0        | Differential outputs for Channel A1                                            |

| 32              | A1TX-    | 0        | Differential outputs for Channel A1                                            |

| 15              | A2RX+,   | Ι        | Differential inputs for Channel A2, with internal 50-Ohm pull-up and >200K-Ohm |

| 16              | A2RX-    | Ι        | otherwise.                                                                     |

| 31              | A2TX+,   | 0        | Differential entruits for Channel A2                                           |

| 30              | A2TX-    | 0        | Differential outputs for Channel A2                                            |

| 17              | A3RX+,   | Ι        | Differential inputs for Channel A3, with internal 50-Ohm pull-up and >200K-Ohm |

| 18              | A3RX-    | Ι        | otherwise.                                                                     |

| 29              | A3TX+,   | 0        | Differential outputs for Channel A2                                            |

| 28              | A3TX-    | 0        | Differential outputs for Channel A3                                            |

| 1               | B0RX+,   | Ι        | Differential inputs for Channel B0, with internal 50-Ohm pullup and >200KOhm   |

| 2               | BORX-    | Ι        | otherwise.                                                                     |

| 45              | В0ТХ+,   | 0        | Differential outputs for Channel B0                                            |

| 44              | B0TX-    | 0        | Differential outputs for Channel Bo                                            |

| 3               | B1RX+,   | Ι        | Differential inputs for Channel B1, with internal 50-Ohm pullup and >200KOhm   |

| 4               | B1RX-    | Ι        | otherwise.                                                                     |

| 43              | B1TX+,   | 0        | Differential outputs for Channel B1                                            |

| 42              | B1TX-    | 0        |                                                                                |

| 5               | B2RX+,   | Ι        | Differential inputs for Channel B2, with internal 50-Ohm pullup and >200KOhm   |

| 6               | B2RX-    | Ι        | otherwise.                                                                     |

| 40              | B2TX+,   | 0        | Differential outputs for Channel B2                                            |

| 39              | B2TX-    | 0        |                                                                                |

| 7               | B3RX+,   | Ι        | Differential inputs for Channel B3, with internal 50-Ohm pullup and >200KOhm   |

| 8               | B3RX-    | Ι        | otherwise.                                                                     |

| 38              | B3TX+,   | 0        | Differential outputs for Channel B3                                            |

| 37              | B3TX-    | 0        |                                                                                |

## **Pin Description Cont.**

| Pin # (54-TQFN)     | Pin Name             | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------|----------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control Signals     |                      |      |                                                                                                                                                                                                                                                                                                                                                                                                           |

| 48                  | ENI2C                | I    | I <sup>2</sup> C Enable Pin. When tied to Low, each channel is programmed by the external pin voltage (Pin Mode). When tied to High, each channel is programmed by the data stored in the I <sup>2</sup> C bus (Slave Mode). When FLOAT, data is accesses from external EEPROM (Master Mode). ENI2C has pull-up / pull-down 90k-Ohm resistance (Default = $V_{DD}$ / 2).                                  |

| When ENI2C = 1 (I   | <sup>2</sup> C Mode) |      | ·                                                                                                                                                                                                                                                                                                                                                                                                         |

| 50                  | SCL                  | I/O  | $I^2C$ SCL clock input in $I^2C$ Slave Mode (ENI2C = High). This pin becomes clock output when loading from EEPROM in $I^2C$ Master Mode (ENI2C = FLOAT).                                                                                                                                                                                                                                                 |

| 49                  | SDA                  | I/O  | I <sup>2</sup> C SDA data input/output in I <sup>2</sup> C Master or Slave Mode.                                                                                                                                                                                                                                                                                                                          |

| 54, 53, 47, 46      | AD[0:3]              | I    | $I^2C$ programmable address bits in $I^2C$ Master or Slave Mode. AD[0:2] have pull-<br>up 90k-Ohm resistance. AD[3] have pull-up / pull-down 90k-Ohm resistance.<br>(Default = $V_{DD}/2$ )                                                                                                                                                                                                               |

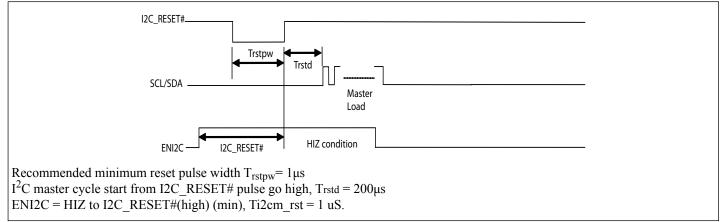

| 25                  | I2C_RESET#           | I    | Reset Pin for I <sup>2</sup> C. When Low, the registers are reset to default value. $I^{2}C_{RESET\#}$ has pull-up 90k-Ohm resistance                                                                                                                                                                                                                                                                     |

| When $ENI2C = 0$ (P | Pin mode)            |      | ·                                                                                                                                                                                                                                                                                                                                                                                                         |

| 21, 20, 19          | EQA[0:2]             | I    | These pins set the level of Equalizer in Bank A channels when ENI2C is Low.<br>When ENI2C is High, the I2C registers provide independent control of each channel. See Table 1: Equalizer Settings. EQA[1] has pull-up 90k-Ohm resistance.<br>EQA[0] and EQA[2] have pull-up / pull-down 90k-Ohm resistance (Default = $V_{DD}$ / 2).                                                                      |

| 46, 47, 23          | EQB[0:2]             | I    | These pins set the level of Equalizer in Bank B channels when ENI2C is Low.<br>When ENI2C is High, the I2C registers provide independent control of each channel, and the EQB[1:0] pins are converted to I <sup>2</sup> C AD[2:3] inputs. See Table 1: Equalizer Settings. EQB[1] has pull-up 90k-Ohm resistance. EQB[0] and EQB[2] have pull-up / pull-down 90k-Ohm resistance (Default = $V_{DD}$ / 2). |

| 49, 50              | FGA[0:1]             | I    | These pins control the level of Flat Gain in Bank A channels when ENI2C is Low. When ENI2C is High, the I <sup>2</sup> C registers provide independent control of each channel, and the FGA[1:0] pins are converted to I <sup>2</sup> C SCL/SDA. See Table 2: Flat Gain Settings.                                                                                                                         |

| 53, 54              | FGB[0:1]             | Ι    | These pins control the level of Flat Gain in Bank B channels when ENI2C is Low.<br>When ENI2C is High, the I <sup>2</sup> C registers provide independent control of each<br>channel, and FGB[1:0] pins are converted to AD[0:1] inputs. See Table 2: Flat Gain<br>Settings. FGB[0] and FGB[1] have pull-up 90k-Ohm resistance.                                                                           |

| 25                  | SW0                  | Ι    | This pins sets the Output Voltage Swing level in all channels when ENI <sup>2</sup> C is Low. SW0 has pull-up 90k-Ohm resistance.                                                                                                                                                                                                                                                                         |

| 26                  | SD_TH0               | I    | Internal Signal Detect Threshold. This pin should be tied to $V_{DD}$ for normal operation. Refer to Table 4 for more options. SD_TH0 has pull-up 90k-Ohm resistance.                                                                                                                                                                                                                                     |

| In both I2C and Pin | n modes              |      |                                                                                                                                                                                                                                                                                                                                                                                                           |

| 22                  | RXDET                | I    | Receiver Detection Control Pin. When High, receiver detection is enabled to support PCIe Mode. When Low, receiver detection is disabled to support 10GbE and SATA3 Modes and input is 50-Ohm to V <sub>DD</sub> . RXDET has pull-up 90k-Ohm resistance.                                                                                                                                                   |

## Pin Description Cont.

| Pin # (54-TQFN)   | Pin Name        | Туре | Description                                                                                                                                                                                                                                  |  |

|-------------------|-----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 52                | PRSNT#          | I    | Cable Present Detect Input. When High, a cable is not present per PCIe Cabling Specification 1.0, and the device is put in lower power mode. When Low, the device is enabled and in normal operation. PRSNT# has pull-up 90k-Ohm resistance. |  |

| Output            |                 |      |                                                                                                                                                                                                                                              |  |

| 27                | ALL_DONE        | 0    | Valid Register Load Status Output. When LOW, the external EEPROM load has failed. When HIGH, the external EEPROM load is successful.                                                                                                         |  |

| Power Pins        |                 |      |                                                                                                                                                                                                                                              |  |

| 9, 14, 36, 41, 51 | V <sub>DD</sub> | PWR  | VR $3.3V \pm 10\%$ Supply Voltage                                                                                                                                                                                                            |  |

| Center Pad, 24    | GND             | PWR  | Supply GND                                                                                                                                                                                                                                   |  |

## **Description of Operation**

#### Output Receiver Detector:

On power up or when PRSNT# becomes low, the output resistance is set to high impedance, and the input resistance is set to 200K ohms. The device continually looks to detect an external 50 ohm termination resistor on a per channel basis. If no 50 ohms is detected in the first 40us of time, the channel is continually polled with 40us detection cycle until detection occurs. This operation can only be reinitiated when PRSNT# or I2C\_RESET# are toggled again.

#### Input Activity Detector:

When the input voltage on individual channel basis falls below Vth-, the output is driven to the common mode voltage so as to eliminate output chatter. When the input voltage is higher than Vth+, the channel is resumed immediately.

#### **Power Enable function:**

One pin control or I2C control, when PRSNT# is set to high, the IC goes into power down mode, both input and output termination set to 200K and high impedance respectively. Individual channel enabling is done through the I2C register programming.

#### **Equalization Setting:**

EQA[2:0] and EQB[2:0] are the selection pins for the equalization selection for each of the channels of A and B respectively.

|     | Equalizer setting (dB) |     |           |           |          |        |        |        |        |

|-----|------------------------|-----|-----------|-----------|----------|--------|--------|--------|--------|

| EQ2 | EQ1                    | EQ0 | EQ 4 Bits | @ 1.25GHz | @ 2.5GHz | @ 3GHz | @ 4GHz | @ 5GHz | @ 6GHz |

| 0   | 0                      | 0   | 0000      | 0         | 0.6      | 1.0    | 1.5    | 2.4    | 2.8    |

| 0   | 0                      | 1   | 0001      | 0.15      | 1.2      | 1.7    | 2.4    | 3.5    | 4      |

| 0   | 1                      | 0   | 0010      | 0.4       | 1.9      | 2.5    | 3.3    | 4.5    | 5      |

| 0   | 1                      | 1   | 0011      | 0.6       | 2.5      | 3.2    | 4.2    | 5.3    | 5.8    |

| 1   | 0                      | 0   | 0100      | 1.8       | 3.4      | 4.1    | 4.9    | 6.0    | 6.4    |

| 1   | 0                      | 1   | 0101      | 2.1       | 3.9      | 4.7    | 5.6    | 6.7    | 7.1    |

| 1   | 1                      | 0   | 0110      | 2.3       | 4.4      | 5.2    | 6.2    | 7.3    | 7.7    |

| 1   | 1                      | 1   | 0111      | 2.5       | 4.9      | 5.7    | 6.8    | 7.9    | 8.2    |

| HIZ | 0                      | 0   | 1000      | 3.4       | 5.6      | 6.4    | 7.3    | 8.4    | 8.7    |

| HIZ | 0                      | 1   | 1001      | 3.6       | 6.0      | 6.9    | 7.8    | 8.9    | 9.1    |

| HIZ | 1                      | 0   | 1010      | 3.8       | 6.4      | 7.3    | 8.3    | 9.3    | 9.5    |

| HIZ | 1                      | 1   | 1011      | 4.1       | 6.8      | 7.7    | 8.7    | 9.7    | 9.9    |

| 0   | 0                      | HIZ | 1100      | 5.1       | 7.5      | 8.3    | 9.2    | 10.1   | 10.2   |

| 0   | 1                      | HIZ | 1101      | 5.3       | 7.8      | 8.6    | 9.5    | 10.4   | 10.5   |

| 1   | 0                      | HIZ | 1110      | 5.4       | 8.1      | 8.9    | 9.8    | 10.7   | 10.8   |

| 1   | 1                      | HIZ | 1111      | 5.6       | 8.4      | 9.2    | 10.1   | 11     | 11.1   |

#### Table 1. Equalization Setting

#### **Flat Gain Setting:**

Flat Gain settings: FGA[0:1] and FGB[0:1] are the selection bits for Flat Gain value for A and B channels.

#### Table 2. Flat Gain Setting

| FGA1<br>FGB1 | FGA0<br>FGB0 | (dB) |

|--------------|--------------|------|

| 0            | 0            | -4   |

| 0            | 1            | -2   |

| 1            | 0            | 0    |

| 1            | 1            | 2    |

#### **Output Swing Setting:**

SW0 is the selection bit for output swing for A and B channels.

#### Table 3. Output Swing Setting

| SWO | mVp-p |

|-----|-------|

| 0   | 900   |

| 1   | 1,000 |

#### **Signal Detect Threshold Level:**

#### Table 4. Signal Detect Threshold Level Setting via I<sup>2</sup>C Bus Mode

| SD_TH1 <i<sup>2C bit&gt;</i<sup> | SD_TH0 | Threshold ON (mVppd) | Threshold OFF (mVppd) |

|----------------------------------|--------|----------------------|-----------------------|

| 0                                | 0      | 130                  | 30                    |

| 0                                | 1      | 150                  | 50                    |

| 1                                | 0      | 170                  | 70                    |

| 1                                | 1      | 210                  | 110                   |

## I<sup>2</sup>C Programming

| Address | assignment |              |          |                                          |                  |     |                                 |

|---------|------------|--------------|----------|------------------------------------------|------------------|-----|---------------------------------|

| A6      | A5         | A4           | A3       | A2                                       | A1               | A0  | R/W                             |

| 1       | 1          | 1            | AD3      | AD2                                      | AD1              | AD0 | 1=R, 0=W                        |

| BYTE 0  |            |              |          |                                          |                  |     |                                 |

| Bit     | Туре       | Power up con | ndition  | Control a                                | affected         |     | Comment                         |

| 7       | R          |              |          | A3 Signal                                | l Detector Outpu | ıt  |                                 |

| 6       | R          |              |          | A2 Signal                                | l Detector Outpu | ıt  |                                 |

| 5       | R          |              |          | A1 Signal                                | l Detector Outpu | ıt  |                                 |

| 4       | R          |              |          | A0 Signal                                | l Detector Outpu | ıt  | 1= Activity 0=no                |

| 3       | R          |              |          | B3 Signal                                | Detector Outpu   | ıt  | activity                        |

| 2       | R          |              |          | B2 Signal                                | Detector Outpu   | ıt  |                                 |

| 1       | R          |              |          | B1 Signal                                | Detector Outpu   | ıt  |                                 |

| 0       | R          |              |          | B0 Signal                                | Detector Outpu   |     |                                 |

| BYTE 1  |            | L            |          | L. L |                  |     |                                 |

| Bit     | Туре       | Power up con | ndition  | Control a                                | affected         |     | Comment                         |

| 7       | R          |              |          | A3 RX D                                  | etector Output   |     |                                 |

| 6       | R          |              |          | A2 RX D                                  | etector Output   |     |                                 |

| 5       | R          |              |          | A1 RX D                                  | etector Output   |     |                                 |

| 4       | R          |              |          | A0 RX D                                  | etector Output   |     | 1 = Far-end 50<br>-ohm detected |

| 3       | R          |              |          | B3 RX De                                 | etector Output   |     | 0 = Not detected                |

| 2       | R          |              |          | B2 RX De                                 | etector Output   |     |                                 |

| 1       | R          |              |          | B1 RX De                                 | etector Output   |     |                                 |

| 0       | R          |              |          | B0 RX De                                 | etector Output   |     |                                 |

| BYTE 2  |            |              |          |                                          |                  |     |                                 |

| Bit     | Туре       | Power up co  | ondition | Control                                  | affected         |     | Comment                         |

| 7       | R/W        | 0            |          | A3 Power                                 | r down           |     |                                 |

| 6       | R/W        | 0            |          | A2 Power                                 | r down           |     |                                 |

| 5       | R/W        | 0            |          | A1 Power                                 | r down           |     |                                 |

| 4       | R/W        | 0            |          | A0 Power                                 | r down           |     | 1 D 1                           |

| 3       | R/W        | 0            |          | B3 Power                                 | down             |     | 1 = Power down                  |

| 2       | R/W        | 0            |          | B2 Power                                 | down             |     |                                 |

| 1       | R/W        | 0            |          | B1 Power                                 | down             |     |                                 |

| 0       | R/W        | 0            |          | B0 Power                                 | down             |     |                                 |

| BYTE 3 |      |                    |                 |                  |             |

|--------|------|--------------------|-----------------|------------------|-------------|

| Bit    | Туре | Power up condition |                 | Control affected | Comment     |

| 7      | R/W  | 0                  |                 | EQ3              |             |

| 6      | R/W  | 0                  | -               | EQ2              | Equalizer   |

| 5      | R/W  | 0                  |                 | EQ1              | See Table 1 |

| 4      | R/W  | 0                  | Channel A0 con- | EQ0              |             |

| 3      | R/W  | 0                  | figuration      | FG1              | Flat Gain   |

| 2      | R/W  | 0                  |                 | FG0              | See Table 2 |

| 1      | R/W  | 0                  |                 | Reserved         | Swing       |

| 0      | R/W  | 0                  |                 | SW0              | See Table 3 |

| BYTE 4 | :    |                    |                 |                  |             |

| Bit    | Туре | Power up conditio  | n               | Control affected | Comment     |

| 7      | R/W  | 0                  |                 | EQ3              |             |

| 6      | R/W  | 0                  |                 | EQ2              | Equalizer   |

| 5      | R/W  | 0                  |                 | EQ1              | See Table 1 |

| 4      | R/W  | 0                  | Channel A1 con- | EQ0              |             |

| 3      | R/W  | 0                  | figuration      | FG1              | Flat Gain   |

| 2      | R/W  | 0                  |                 | FG0              | See Table 2 |

| 1      | R/W  | 0                  |                 | Reserved         | Swing       |

| 0      | R/W  | 0                  |                 | SW0              | See Table 3 |

| BYTE 5 |      |                    |                 |                  |             |

| Bit    | Туре | Power up condition |                 | Control affected | Comment     |

| 7      | R/W  | 0                  |                 | EQ3              |             |

| 6      | R/W  | 0                  | Channel A2 con- | EQ2              | Equalizer   |

| 5      | R/W  | 0                  | figuration      | EQ1              | See Table 1 |

| 4      | R/W  | 0                  |                 | EQ0              |             |

| 3      | R/W  | 0                  |                 | FG1              | Flat Gain   |

| 2      | R/W  | 0                  |                 | FG0              | See Table 2 |

| 1      | R/W  | 0                  |                 | Reserved         | Swing       |

| 0      | R/W  | 0                  |                 | SW0              | See Table 3 |

| BYTE 6 | 5    |                    |                               |                  |             |

|--------|------|--------------------|-------------------------------|------------------|-------------|

| Bit    | Туре | Power up condition |                               | Control affected | Comment     |

| 7      | R/W  | 0                  |                               | EQ3              |             |

| 6      | R/W  | 0                  |                               | EQ2              | Equalizer   |

| 5      | R/W  | 0                  |                               | EQ1              | See Table 1 |

| 4      | R/W  | 0 (                | Channel A3 con-               | EQ0              |             |

| 3      | R/W  | 0 f                | figuration                    | FG1              | Flat Gain   |

| 2      | R/W  | 0                  |                               | FG0              | See Table 2 |

| 1      | R/W  | 0                  |                               | Reserved         | Swing       |

| 0      | R/W  | 0                  |                               | SW0              | See Table 3 |

| BYTE 7 | 7    |                    |                               |                  |             |

| Bit    | Туре | Power up condition |                               | Control affected | Comment     |

| 7      | R/W  | 0                  |                               | EQ3              |             |

| 6      | R/W  | 0                  |                               | EQ2              | Equalizer   |

| 5      | R/W  | 0                  |                               | EQ1              | See Table 1 |

| 4      | R/W  | 0                  | Channel B0 con-               | EQ0              |             |

| 3      | R/W  | 0 f                | figuration                    | FG1              | Flat Gain   |

| 2      | R/W  | 0                  |                               | FG0              | See Table 2 |

| 1      | R/W  | 0                  |                               | Reserved         | Swing       |

| 0      | R/W  | 0                  |                               | SW0              | See Table 3 |

| BYTE 8 | 3    |                    |                               |                  |             |

| Bit    | Туре | Power up condition |                               | Control affected | Comment     |

| 7      | R/W  | 0                  |                               | EQ3              |             |

| 6      | R/W  | 0                  |                               | EQ2              | Equalizer   |

| 5      | R/W  | 0                  |                               | EQ1              | See Table 1 |

| 4      | R/W  | 0                  | Channel B1 con-<br>figuration | EQ0              |             |

| 3      | R/W  | 0 f                |                               | FG1              | Flat Gain   |

| 2      | R/W  | 0                  |                               | FG0              | See Table 2 |

| 1      | R/W  | 0                  |                               | Reserved         | Swing       |

| 0      | R/W  | 0                  |                               | SW0              | See Table 3 |

| BYTE 9 | )    |                    |                 |                    |              |

|--------|------|--------------------|-----------------|--------------------|--------------|

| Bit    | Туре | Power up condition |                 | Control affected   | Comment      |

| 7      | R/W  | 0                  |                 | EQ3                |              |

| 6      | R/W  | 0                  |                 | EQ2                | Equalizer    |

| 5      | R/W  | 0                  |                 | EQ1                | See Table 1  |

| 4      | R/W  | 0 0                | Channel B2 con- | EQ0                |              |

| 3      | R/W  | 0 f                | iguration       | FG1                | Flat Gain    |

| 2      | R/W  | 0                  |                 | FG0                | See Table 2  |

| 1      | R/W  | 0                  |                 | Reserved           | Swing        |

| 0      | R/W  | 0                  |                 | SW0                | See Table 3  |

| BYTE 1 | 10   |                    |                 |                    |              |

| Bit    | Туре | Power up condition |                 | Control affected   | Comment      |

| 7      | R/W  | 0                  |                 | EQ3                |              |

| 6      | R/W  | 0                  |                 | EQ2                | Equalizer    |

| 5      | R/W  | 0                  |                 | EQ1                | See Table 1  |

| 4      | R/W  | 0 0                | Channel B3 con- | EQ0                |              |

| 3      | R/W  | 0 f                | iguration       | FG1                | Flat Gain    |

| 2      | R/W  | 0                  |                 | FG0                | See Table 2  |

| 1      | R/W  | 0                  |                 | Reserved           | Swing        |

| 0      | R/W  | 0                  |                 | SW0                | See Table 3  |

| BYTE 1 | 1    |                    |                 |                    |              |

| Bit    | Туре | Power up condition |                 | Control affected   | Comment      |

| 7      | R/W  | 0                  |                 | A3 Signal Detector |              |

| 6      | R/W  | 0                  |                 | A2 Signal Detector |              |

| 5      | R/W  | 0                  |                 | A1 Signal Detector |              |

| 4      | R/W  | 0                  |                 | A0 Signal Detector | 1=Power Down |

| 3      | R/W  | 0                  |                 | B3 Signal Detector | 1=Power Down |

| 2      | R/W  | 0                  |                 | B2 Signal Detector |              |

| 1      | R/W  | 0                  |                 | B1 Signal Detector |              |

| 0      | R/W  | 0                  |                 | B0 Signal Detector |              |

| BYTE 1 | 12           |                             |                  |                 |

|--------|--------------|-----------------------------|------------------|-----------------|

| Bit    | Туре         | Power up condition          | Control affected | Comment         |

| 7      | R/W          | 0                           | A3 RX Detector   |                 |

| 6      | R/W          | 0                           | A2 RX Detector   |                 |

| 5      | R/W          | 0                           | A1 RX Detector   | 1=Power Down    |

| 4      | R/W          | 0                           | A0 RX Detector   |                 |

| 3      | R/W          | 0                           | B3 RX Detector   |                 |

| 2      | R/W          | 0                           | B2 RX Detector   |                 |

| 1      | R/W          | 0                           | B1 RX Detector   | 1=disable       |

| 0      | R/W          | 0                           | B0 RX Detector   |                 |

| BYTE 1 | 13           |                             |                  |                 |

| Bit    | Туре         | Power up condition          | Control affected | Comment         |

| 7      | R/W          | 0                           |                  |                 |

| 6      | R/W          | 0                           |                  |                 |

| 5      | R/W          | 0                           |                  |                 |

| 4      | R/W          | 0                           | Reserved         |                 |

| 3      | R/W          | 0                           |                  |                 |

| 2      | R/W          | 0                           |                  |                 |

| 1      | R/W          | 0                           | SD_TH1           | Signal Detector |

| 0      | R/W          | 0                           | SD_TH0           | Threshold       |

| BYTE 1 | 4 to 15 have | e '0' as Power-up condition |                  |                 |

## Reset and I<sup>2</sup>C Master Timing Diagram

## I<sup>2</sup>C Operation

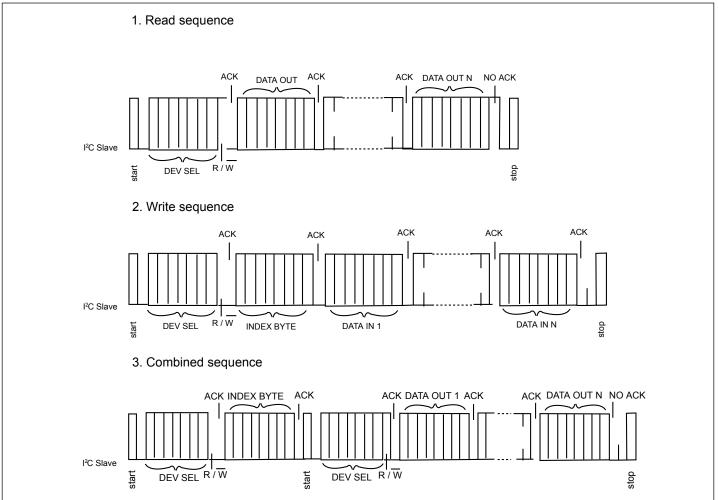

The integrated I2C interface operates as a master or slave device depending on the pin ENI2C being HIZ or HIGH respectively. Standard mode (100Kbps) is supported with 7-bit addressing. The data byte format is 8-bit bytes, and supports the format of indexing to be compatible with other bus devices. In the Slave mode (ENI2C = HIGH), the device supports Read/Write. The bytes must be accessed in sequential order from the lowest to the highest byte with the ability to stop after any complete byte has been transferred. Address bits A3 to A0 are programmable to support multiple chips environment. The Data is loaded until a Stop sequence is issued.

In the master mode (ENI2C = HIZ), PI3EQX12908A2 supports up to 16 masters connected in daisy chain through connecting I2C\_ DONE pin to I2C\_RESET# pin of the next part.

Master EEPROM data starting address of the device address is indicated in the table below:

| AD3, AD2, AD1, AD0 | <b>EEPROM Data Starting Location</b> |

|--------------------|--------------------------------------|

| 0000               | 00h                                  |

| 0001               | 10h                                  |

| 0010               | 20h                                  |

| 0011               | 30h                                  |

| 0100               | 40h                                  |

| 0101               | 50h                                  |

| 0110               | 60h                                  |

| 0111               | 70h                                  |

| 1000               | 80h                                  |

| 1001               | 90h                                  |

| 1010               | A0h                                  |

| 1011               | B0h                                  |

| 1100               | C0h                                  |

| 1101               | D0h                                  |

| 1110               | E0h                                  |

| 1111               | F0h                                  |

When tying multiple PI3EQX12908A2 devices to the SDA and SCL bus, use the guidelines below to configure the devices. The user also can refer the application notes for detail information.

• Use AD[3:0] address bits so that each device can loaded it's configuration from the EEPROM.

Example below is for 4 devices. The first device in the sequence must be address 0x00h;

subsequent devices must follow the address order listed below.

- U1: AD[3:0] = 0000 = 0x00h,

- U2: AD[3:0] = 0001 = 0x10h,

- U3: AD[3:0] = 0010 = 0x20h,

- U4: AD[3:0] = 0011 = 0x30h

• For I2C Slave Mode operation, use a 2Kohms pull-up resistor on SDA and SCL pins. For I2C Master Mode operation, use a 1Kohm pull-up resistor on SDA and SCL pins.

• Daisy-chain I2C\_RESET# and ALL\_DONE from one device to the next device in the sequence so that they do not compete for the EEPROM at the same time.

1. Tie ALL DONE of U1 to I2C RESET# of U2

2. Tie ALL DONE of U2 to I2C RESET# of U3

3. Tie ALL\_DONE of U3 to I2C\_RESET# of U4

4. Optional: Tie ALL\_DONE output of U4 to a LED to show the devices has been loaded successfully

Below is an example of a 2 kbits (256 x 8-bit) EEPROM in hex format for 4pcs PI3EQX12908A2 device. Bold fonts in yellow are register setting from Byte0 to Byte15 for each device in each line. Bold fonts in red is the EEPROM data location.

| :1000 <mark>00</mark> 00 <mark>000000FF00000FFFFFFFFFF60000FF6201</mark> 94 |  |

|-----------------------------------------------------------------------------|--|

| :1000 <mark>10</mark> 00 <mark>000000FFFF00000FFFFFFFF0000FF6201</mark> 84  |  |

| :1000 <mark>20</mark> 00 <mark>000000FFFFFF0000FFFFFF0000FF6201</mark> 74   |  |

| :1000 <mark>30</mark> 00 <mark>000000FFFFFFF60000FFFF0000FF6201</mark> 64   |  |

| :10004000000000000000000000000000000000                                     |  |

| :10005000000000000000000000000000000000                                     |  |

| :10006000000000000000000000000000000000                                     |  |

| :10007000000000000000000000000000000000                                     |  |

| : 10008000000000000000000000000000000000                                    |  |

| :10009000000000000000000000000000000000                                     |  |

| :1000A000000000000000000000000000000000                                     |  |

| :1000B000000000000000000000000000000000                                     |  |

| :1000C000000000000000000000000000000000                                     |  |

| :1000D000000000000000000000000000000000                                     |  |

| :1000E000000000000000000000000000000000                                     |  |

| :1000F000000000000000000000000000000000                                     |  |

| :00000001FF                                                                 |  |

2k bits (256 x 8-bit) EEPROM Date Example

Below is the sample of the I2C master reading waveform based on the setup above.

| 16 | K Prevu                                           |                                                      | M 4.00ms                                          |                       | i rig?                  |

|----|---------------------------------------------------|------------------------------------------------------|---------------------------------------------------|-----------------------|-------------------------|

|    |                                                   | U [ ]                                                |                                                   | 1                     |                         |

| -  |                                                   |                                                      |                                                   |                       |                         |

| 2  |                                                   |                                                      | يداخرها وتعاديك بمناقح والمتكان المتكاف المتعادية |                       |                         |

|    |                                                   |                                                      |                                                   |                       |                         |

|    |                                                   |                                                      |                                                   |                       |                         |

|    | Zoom Factor: 4 X                                  | L                                                    |                                                   |                       |                         |

|    |                                                   |                                                      |                                                   |                       |                         |

|    |                                                   |                                                      |                                                   |                       |                         |

|    |                                                   |                                                      |                                                   |                       |                         |

|    |                                                   |                                                      |                                                   |                       |                         |

|    | U1 Read Process                                   | U2 Read Process                                      | U3 Read Process                                   | U4 Re                 | ad Process              |

|    |                                                   |                                                      |                                                   |                       |                         |

|    | SCL                                               |                                                      |                                                   |                       | i in the second second  |

|    |                                                   |                                                      |                                                   |                       |                         |

| 2  |                                                   |                                                      |                                                   |                       |                         |

|    | and the second second second second second second | and that I is maked a providence of the P Providence | Annual I al I - presentant - provident - prese    |                       |                         |

|    |                                                   |                                                      |                                                   |                       |                         |

|    | SDA                                               |                                                      |                                                   |                       | كند الديد وزوار         |

| 1  | ومورود ومرشور والرار ومرجع محتجم والمرجع والمرجع  |                                                      |                                                   |                       |                         |

| -  | EEPROM<br>Data location: 0x00                     | 0x10                                                 | 0x20                                              |                       | 0x30                    |

|    | Data location: 0x00                               | 010                                                  | 0x20                                              |                       | 0x50                    |

|    |                                                   |                                                      |                                                   |                       |                         |

|    |                                                   |                                                      |                                                   |                       |                         |

|    |                                                   |                                                      |                                                   |                       |                         |

|    |                                                   |                                                      |                                                   |                       |                         |

|    |                                                   |                                                      |                                                   |                       |                         |

|    |                                                   |                                                      |                                                   |                       |                         |

|    |                                                   |                                                      |                                                   |                       |                         |

|    | (1) 2.00 V 🦠 (2) 2.00 V 🗞                         |                                                      | Z 1.00ms<br>■→▼2.12000ms                          | 25.0MS/s<br>1M points | 1.60 V                  |

|    |                                                   |                                                      | 2. 120001113                                      |                       |                         |

|    |                                                   |                                                      |                                                   |                       | 19 Feb 2014<br>15:47:45 |

|    |                                                   |                                                      |                                                   |                       | 15:47:45                |

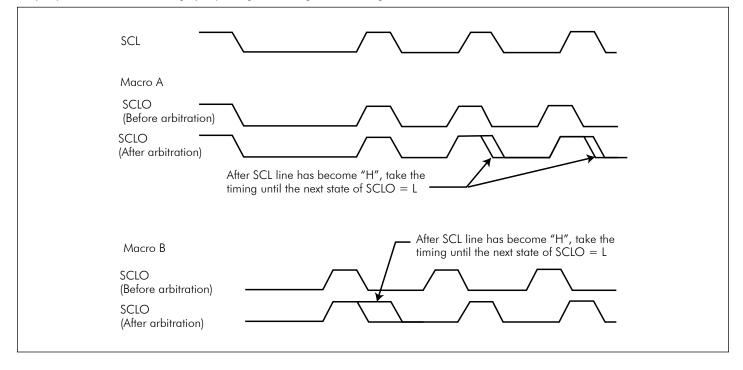

#### **SCL Synchronization**

When more than one I2C device becomes a master device and drives the SCL line, each device senses the state of SCL line and automatically adjust the the drive timing by adjusting the timing to the timing to the slowest one.

#### **Transferring Data**

Every byte put on the SDA line must be 8-bits long. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit (MSB) first (see the I2C Data Transfer diagram). The PI3EQX12908A2 will never hold the clock line SCL LOW to force the master into a wait state.

## Acknowledge

Data transfer with acknowledge is required from the master. When the master releases the SDA line (HIGH) during the acknowledge clock pulse, the PI3EQX12908A2 will pull down the SDA line during the acknowledge clock pulse so that it remains stable LOW during the HIGH period of this clock pulse as indicated in the I2C Data Transfer diagram. The PI3EQX12908A2 will generate an acknowledge after each byte has been received.

#### **Data Transfer**

A data transfer cycle begins with the master issuing a start bit. After recognizing a start bit, the PI3EQX12908A2 will watch the next byte of information for a match with its address setting. When a match is found it will respond with a read or write of data on the following clocks. Each byte must be followed by an acknowledge bit, except for the last byte of a read cycle which ends with a stop bit. For a write cycle, the first data byte following the address byte is an index byte that is used by the PI3EQX12908A2. Data is transferred with the most significant bit (MSB) first.

## I<sup>2</sup>C Data Transfer

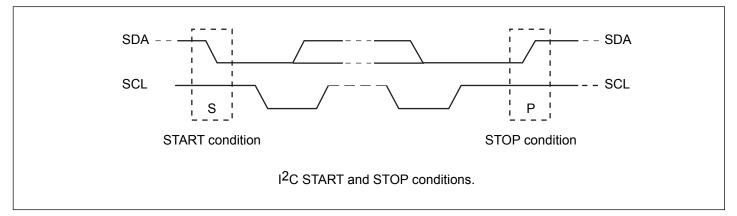

#### **Start & Stop Conditions**

A HIGH to LOW transition on the SDA line while SCL is HIGH indicates a START condition. A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition, as shown in the figure below. When a STOP condition is detected, index byte value will be reset to 0.

## I<sup>2</sup>C Data Transfer Sequence

Note:

**PI3EQX12908A2**

#### **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.)

| Supply Voltage              | 0.5V to +4.0V                            |

|-----------------------------|------------------------------------------|

| LVCMOS Input/Output Voltage | 0.5V to +4.0V                            |

| CML Input Voltage           | $\ldots$ -0.5V to (V <sub>DD</sub> +0.5) |

| CML Input Current           | 30 to +30 mA                             |

| I <sup>2</sup> C pins       | V <sub>DD</sub> +0.3 V                   |

| Storage Temperature         | 65°C to +150°C                           |

| Max. Junction Temperature   | 125 °C                                   |

| ESD HBM                     |                                          |

|                             |                                          |

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## LVCMOS I/O DC Specifications (V<sub>DD</sub> = $3.3 \pm 10\%$ , T<sub>A</sub> = -40 to $85^{\circ}$ C)

| Symbol           | Parameter                           | Conditions                  | Min.                     | Тур. | Max.                     | Units |

|------------------|-------------------------------------|-----------------------------|--------------------------|------|--------------------------|-------|

| V <sub>IH</sub>  | DC input logic high                 |                             | V <sub>DD</sub> /2 + 0.7 |      | V <sub>DD</sub> + 0.3    | V     |

| V <sub>IL</sub>  | DC input logic low                  |                             | -0.3                     |      | V <sub>DD</sub> /2 - 0.7 | V     |

| V <sub>OH</sub>  | DC output logic high                | At I <sub>OH</sub> = -200μA | V <sub>DD</sub> - 0.2    |      |                          | V     |

| V <sub>OL</sub>  | DC output logic low                 | At $I_{OL} = +200 \mu A$    |                          |      | 0.2                      | V     |

| V <sub>hys</sub> | Hysteresis of Schmitt trigger input |                             | 0.8                      |      |                          | V     |

## **SDA and SCL I/O for I<sup>2</sup>C-bus** ( $V_{DD} = 3.3 \pm 10\%$ , $T_A = -40$ to $85^{\circ}$ C)

| Symbol            | Parameter                                        | Conditions                    | Min.                     | Тур. | Max.                     | Units |

|-------------------|--------------------------------------------------|-------------------------------|--------------------------|------|--------------------------|-------|

| V <sub>IH</sub>   | DC input logic high                              |                               | V <sub>DD</sub> /2 + 0.7 |      | V <sub>DD</sub> + 0.3    | V     |

| V <sub>IL</sub>   | DC input logic low                               |                               | -0.3                     |      | V <sub>DD</sub> /2 - 0.7 | V     |

| V <sub>OL</sub>   | DC output logic low                              | $I_{OL} = 3mA$                |                          |      | 0.4                      | V     |

| V <sub>hys</sub>  | Hysteresis of Schmitt trigger input              |                               | 0.8                      |      |                          | V     |

| t <sub>of</sub>   | Output fall time from $V_{IHmin}$ to $V_{ILmax}$ | Bus capacity = 10 to<br>400pF |                          | 250  |                          | ns    |

| f <sub>SCLK</sub> | SCLK clock frequency                             |                               |                          | 100  |                          | kHz   |

## High Speed I/O AC/DC Specifications (V<sub>DD</sub> = $3.3 \pm 10\%$ , T<sub>A</sub> = -40 to $85^{\circ}$ C)

| Receiver Input (100Ω differential) |                                 |                          |      |      |      |       |

|------------------------------------|---------------------------------|--------------------------|------|------|------|-------|

| Symbol                             | Parameter                       | Conditions               | Min. | Тур. | Max. | Units |

| C <sub>RX</sub>                    | RX AC coupling capacitance      |                          |      | 220  |      | nF    |

| S <sub>11</sub> Input return loss  | 10MHz to 4GHz dif-<br>ferential |                          | 13   |      | ar   |       |

|                                    |                                 | 1GHz to 4GHz common mode |      | 4    |      | dB    |

## High Speed I/O AC/DC Specifications Cont.

| Symbol                                | Parameter                                                                                                        | Conditions                      | Min. | Тур.       | Max. | Units             |  |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------|------|------------|------|-------------------|--|

| S <sub>22</sub>                       | Output noture loss                                                                                               | 10MHz to 4GHz differ-<br>ential |      | 21         |      | db                |  |

| 522                                   | Output return loss                                                                                               | 1GHz to 4GHz common<br>mode     |      | 4          |      | dB                |  |

| D                                     | DC single-ended input impedance                                                                                  |                                 |      | 50         |      | 0                 |  |

| R <sub>IN</sub>                       | DC differential input impedance                                                                                  |                                 |      | 100        |      | Ω                 |  |

| D                                     | DC single-ended output impedance                                                                                 |                                 |      | 50         |      | 0                 |  |

| R <sub>OUT</sub>                      | DC differential output impedance                                                                                 |                                 |      | 100        |      | Ω                 |  |

| Z <sub>RX-HIZ</sub>                   | DC input CM input impedance during reset<br>or power down                                                        |                                 |      | 200        |      | kΩ                |  |

| V <sub>RX-DIFF-PP</sub>               | Differential Input Peak-to-peak Voltage                                                                          | Operational                     |      |            | 1.2  | V <sub>ppd</sub>  |  |

|                                       | Input source common-mode noise                                                                                   | DC – 200MHz                     |      |            | 150  | mV <sub>ppd</sub> |  |

| T <sub>TX-IDLE-SET-TO-</sub><br>IDLE  | Max time to electrical idle after sending an EIOS                                                                |                                 |      | 4          | 8    | ns                |  |

| T <sub>TX-IDLE-TO-DIFF-</sub><br>data | Max time to valid diff signal after leaving electrical idle                                                      |                                 |      | 4          | 8    | ns                |  |

| V <sub>th +</sub>                     | On threshold of signal detector                                                                                  | Signal swing @ 4GHz             | 130  |            | 210  | mV <sub>ppd</sub> |  |

| V <sub>th -</sub>                     | Off threshold of signal detector                                                                                 | Signal swing @ 100MHz           | 30   |            | 110  | mV <sub>ppd</sub> |  |

| V <sub>DD</sub>                       | Power supply voltage                                                                                             |                                 | 3    | 3.3        | 3.6  | V                 |  |

| P <sub>max</sub>                      | Max Supply power                                                                                                 | PRSNT#=0                        |      |            | 1    | W                 |  |

| I <sub>max</sub>                      | Max Supply current                                                                                               |                                 |      |            | 330  | mA                |  |

| P <sub>idle</sub>                     | Supply power                                                                                                     | PRSNT#=1                        |      |            | 36   | mW                |  |

|                                       |                                                                                                                  | EQ<3:0> = 1111                  |      | 16.1       |      |                   |  |

| 0                                     | Peaking gain (Compensation at 5GHz, rela-<br>tive to 100MHz, 100mVp-p sine wave input)<br>SW<1:0>=01, FG<1:0>=10 | EQ<3:0> = 1000                  |      | 13.5       |      | ID                |  |

| G <sub>P5GHZ</sub>                    |                                                                                                                  | EQ<3:0> = 0000                  |      | 8.0        |      | dB                |  |

|                                       | 5                                                                                                                | Variation around typical        | -3   |            | +3   |                   |  |

|                                       |                                                                                                                  | EQ<3:0> = 1111                  |      | 17.2       |      |                   |  |

|                                       | Peaking gain (Compensation at 6GHz, rela-                                                                        | EQ<3:0> = 1000                  |      | 14.8       |      |                   |  |

| G <sub>P6GHZ</sub>                    | tive to 100MHz, 100mVp-p sine wave input)                                                                        | EQ<3:0> = 0000                  |      | 9.0        |      | dB                |  |

|                                       | SW<1:0>=01, FG<1:0>=10                                                                                           | Variation around typical        | -3   |            | +3   |                   |  |

|                                       |                                                                                                                  |                                 |      | +2.0       |      |                   |  |

|                                       |                                                                                                                  | FG<1:0> = 11<br>FG<1:0> = 10    |      | -0.5       |      |                   |  |

| G <sub>F</sub>                        | Flat gain (100MHz, EQ<3:0> = 1000,                                                                               | FG<1:0> = 01                    |      | -2.0       |      | dB                |  |

| S.                                    | SW<1:0> = 01)                                                                                                    | FG<1:0> = 00                    |      | -4.0       |      | uD                |  |

|                                       |                                                                                                                  | Variation around typical        | -3   | 1.0        | +3   |                   |  |

|                                       | -1dB compression point of output swing (at                                                                       | SW0=1                           | -    | 1000       |      |                   |  |

| V <sub>1dB_100M</sub>                 | 100MHz)                                                                                                          | SW0=0                           |      | 900        |      | mV <sub>ppd</sub> |  |

| V <sub>1dB_6G</sub>                   | -1dB compression point of output swing (at<br>6GHz) FG= 0dB, EQ = 0000 or 0(h)                                   | SW0=1<br>SW0=0                  |      | 600<br>540 |      | mV <sub>ppd</sub> |  |

## High Speed I/O AC/DC Specifications Cont.

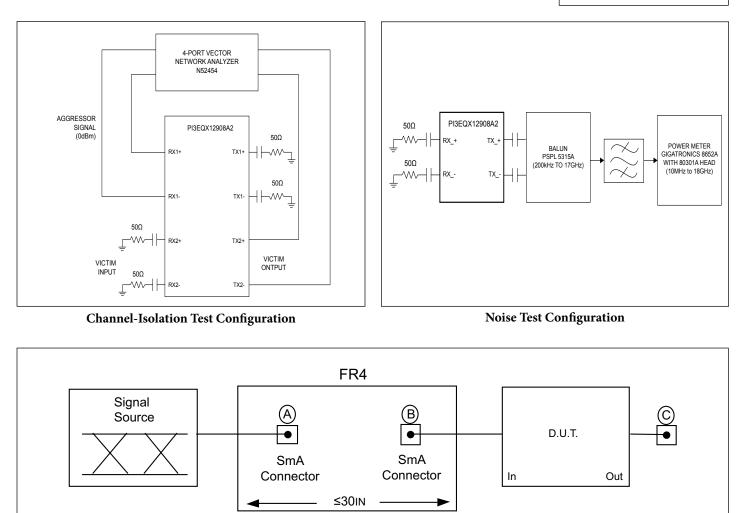

| Symbol                                        | Parameter                                                    | Conditions                                                   | Min. | Typ.   | Max.              | Units             |

|-----------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|------|--------|-------------------|-------------------|

| V <sub>Coup</sub>                             | Channel isolation                                            | 100MHz to 5GHz, Fig-<br>ure 1 (Note 1)                       |      | 28     |                   | dB                |

| V <sub>noise_input</sub> Input-referred noise | Lund of and a size                                           | 100MHz to 5GHz,<br>FG<1:0> = 11, EQ<3:0><br>= 0000, Figure 2 |      | 0.5    |                   |                   |

|                                               | 100MHz to 5GHz,<br>FG<1:0> = 11, EQ<3:0><br>= 1010, Figure 2 |                                                              | 0.4  |        | mV <sub>RMS</sub> |                   |

| V                                             |                                                              | 100MHz to 5GHz,<br>FG<1:0> = 11, EQ<3:0><br>= 0000, Figure 2 |      | 0.7    |                   | V                 |

| V <sub>noise_output</sub> Output-             | Output-referred noise (Note 2)                               | 100MHz to 5GHz,<br>FG<1:0> = 11, EQ<3:0><br>= 1010, Figure 2 |      | 0.8    | 1.6               | mV <sub>RMS</sub> |

| Latency                                       |                                                              |                                                              |      | 1      |                   |                   |

| t <sub>pd</sub>                               | Latency                                                      | From input to output                                         |      | 0.2    |                   | ns                |

| Jitter                                        |                                                              |                                                              |      |        |                   |                   |

| D                                             | Additive Random Jitter at 8Gb/s (worst                       | PRBS31@24hrs<br>36" 5mils FR4<br>VID = 0.8mVp-p              |      | 0.0259 |                   |                   |

| R <sub>j</sub>                                | case)                                                        | DE = 0 dB $EQ = 0100$                                        |      | 0.0258 |                   | UI                |

Note 1: Measured using a vector-network analyzer (VNA) with -15dBm power level applied to the adjacent input. The VNA detects the signal at the output of the victim channel. All other inputs and outputs are terminated with  $50\Omega$ .

Note 2: Guaranteed by design and characterization.

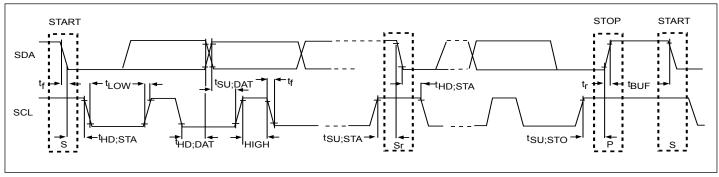

## Characteristics of the SDA and SCI bus lines for Standard Mode I<sup>2</sup>C-bus devices<sup>(1)</sup>

| Symbol              | Parameter                                                                                    | Conditions | Min. | Тур. | Max. | Units |

|---------------------|----------------------------------------------------------------------------------------------|------------|------|------|------|-------|

| f <sub>SCL</sub>    | SCL clock frequency                                                                          |            |      | 100  | _    | kHz   |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated. |            | 4.0  |      | _    |       |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                                                  |            | 4.7  |      | _    | μs    |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                 |            | 4.0  |      | _    |       |

| t <sub>SU;STA</sub> | Set-up time for a repeated START condition                                                   |            | 4.7  |      | _    |       |

| t <sub>HD;DAT</sub> | Data hold time                                                                               |            | 10   |      | _    | ns    |

| t <sub>SU;DAT</sub> | Data set-up time                                                                             |            | 250  |      | -    |       |

| t <sub>r</sub>      | Rise time of both SDA and SCL signals                                                        |            | -    |      | 1000 | ns    |

| t <sub>f</sub>      | Fall time of both SDA and SCL signals                                                        |            |      |      | 300  |       |

| t <sub>SU;STO</sub> | Set-up time for STOP condition                                                               |            | 4.0  |      | _    |       |

| t <sub>BUF</sub>    | Bus free time between a STOP and STOP condition                                              |            | 4.7  |      | _    | μs    |

| C <sub>b</sub>      | Capacitive load for each bus line                                                            |            | -    |      | 400  | pF    |

Notes:

1. All values referred to VIH min and VIL max levels

AC Test Circuit Referenced in the Electrical Characteristic Table

I<sup>2</sup>C Timing

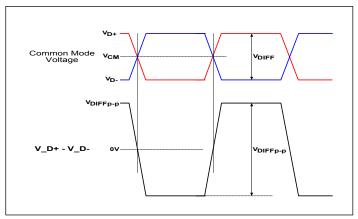

**Definition of Differential Voltage** and Differential Voltage Peak-to-Peak

A product Line of Diodes Incorporated

PI3EQX12908A2

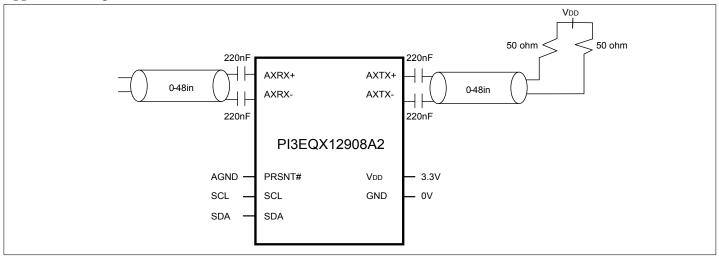

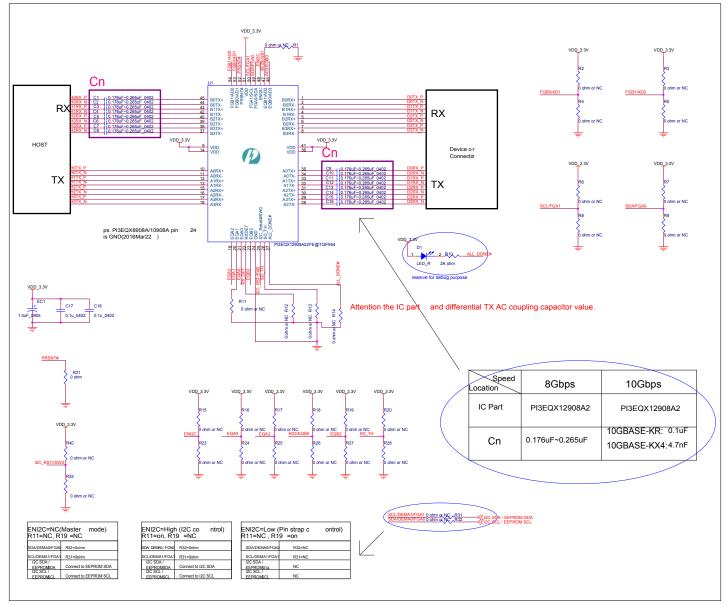

#### **Application Diagrams**

#### **Applications Information**

#### GENERAL RECOMMENDATIONS

The PI3EQX12908A2 is a high performance circuit capable of delivering excellent performance. Careful attention must be paid to the details associated with high-speed design as well as providing a clean power supply. Refer to the information below and Revision 4 of the LVDS Owner's Manual for more detailed information on high speed design tips to address signal integrity design issues.

#### PCB LAYOUT CONSIDERATIONS FOR DIFFERENTIAL PAIRS

The Differential inputs and LPDS outputs have been optimized to work with interconnects using a controlled differential impedance of 85 -  $100\Omega$ . It is preferable to route differential lines exclusively on one layer of the board, particularly for the input traces. The use of vias should be avoided if possible. If vias must be used, they should be used sparingly and must be placed symmetrically for each side of a given differential pair. Whenever differential vias are used the layout must also provide for a low inductance path for the return currents as well. Route the differential signals away from other signals and noise sources on the printed circuit board.

#### POWER SUPPLY BYPASSING

Two approaches are recommended to ensure that the PI3EQX12908A2 is provided with an adequate power supply. First, the supply (VDD) and ground (GND) pins should be connected to power planes routed on adjacent layers of the printed circuit board. The layer thickness of the dielectric should be minimized so that the VDD and GND planes create a low inductance supply with distributed capacitance. Second, careful attention to supply bypassing through the proper use of bypass capacitors is required. A 0.1  $\mu$ F bypass capacitor should be connected to each VDD pin such that the capacitor is placed as close as possible to the PI3EQX12908A2. Smaller body size capacitors can help facilitate proper component placement. Additionally, capacitor with capacitance in the range of 1  $\mu$ F to 10  $\mu$ F should be incorporated in the power supply bypassing design as well. These capacitors can be either tantalum or an ultra-low ESR ceramic.

#### Notes:

Hot Plug Detect feature operation is dependent on certain channel conditions, such as length. For hot plug detect, reset will automatically go back to receiver detect (RXDET) cycle.

#### **Application Schematics**

#### Packaging Information 54-TQFN (ZF)

| Thermal Resistance - 54-contact ZF Package/72-contact ZL Package: |  |  |  |

|-------------------------------------------------------------------|--|--|--|

| θJC11.5°C/W                                                       |  |  |  |

| θJANo Airflow, 4 layer JEDEC 19.1°C/W                             |  |  |  |

#### For latest package info.