Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

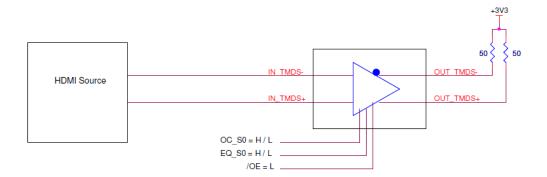

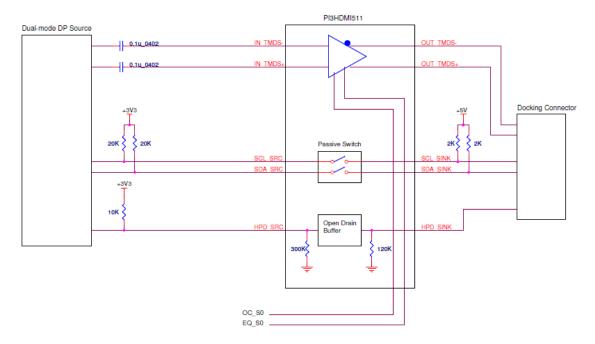

# **HDMI™1.4 Redriver Source-side Application**

#### **Features**

- → HDMI<sup>TM</sup> 1.4 compliant re-driver

- → Operation upto 3.4 Gbps per lane (340MHz pixel clock)

- 4K x 2K 24Hz(297MHz)

- 3D Video formats(1080p, 1080i, 720p)

- → Support up to 48-bit per pixel Deep Color<sup>TM</sup>

- → Convert low-swing DC or AC coupled differential input

- Open-drain current steering Rx terminated differential output

- Support Dual Mode DisplayPort source devices

- → Provide Output Squelch function to turn off TMDS common mode output buffer when TMDS clock is not present

- → Built-in Rx sense detection function

- → Programmable equalizer, emphasis and amplitude settings to achieve optimized HDMI signal integrity

- → Integrated Passive DDC level shifter

- 3.3V source to 5V sink

- → Idle clock detection function for output squelch and auto standby

- → Programmable input TMDS termination control (on or off)

- → 3.3V Power supply required

- → Integrated ESD protection on I/O pins

- □ 8kV contact per IEC61000-4-2, level 4

- □ 8kV HBM

- → Packaging

- □ Pb-free & Green

- □ 32-contact TQFN (ZL)Description

#### **Application**

- → Notebook computers and docking station

- → Set-Top Box(STB)

- → A/V Home entertainment systems

- → Dongle and switch boxes

## **Description**

PI3HDMI511 is TMDS Redriver supporting HDMI 1.4 and DVI specifications up to a data rate of 3.4Gbps with 48-bit per pixel Deep Color<sup>TM</sup>. It also support enhanced robust ESD/EOS protection of 8kV, which is required by many consumer video networks today.

It converts the DC and AC coupled source devices into the HDMI compliant signal with proper signal swing, espically in the Notebook HDMI and Dual mode DP PC systems.

Programmable termination settings at TMDS input help to avoid the compatibility issue caused by non standard HDMI source to determine the connection status of TMDS channel with proper termination voltage setting.

With Pericom's intelligent power management techniques, the PI3HDMI511 can automatically enter low power states when no valid signal presents on the TMDS link.

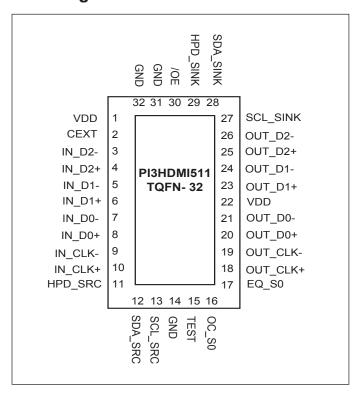

## **Pin Configuration**

P-0.2

# **Pin Description**

| Pin#       | Pin Name                                                                                                                                          | Type   | Description                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------|

| 2          | CEXT                                                                                                                                              | PWR    | LDO output for internal core supplier. External capacitor 2.2 to $4.7\mu F$ should be added to GND.           |

| 3          | IN_D2-                                                                                                                                            | I      |                                                                                                               |

| 4          | IN_D2+                                                                                                                                            | I      |                                                                                                               |

| 5          | IN_D1-                                                                                                                                            | I      |                                                                                                               |

| 6          | IN_D1+                                                                                                                                            | I      | TMDC: 4 B 50 l                                                                                                |

| 7          | IN_D0-                                                                                                                                            | I      | TMDS inputs. R <sub>T</sub> =50 ohm                                                                           |

| 8          | IN_D0+                                                                                                                                            | I      |                                                                                                               |

| 9          | IN_CLK-                                                                                                                                           | I      |                                                                                                               |

| 10         | IN_CLK+                                                                                                                                           | I      |                                                                                                               |

| 11         | HPD_SRC                                                                                                                                           | О      | HPD output; internal pull-down at 300K ohm                                                                    |

| 12         | SDA_SRC                                                                                                                                           | IO     | DDC Data on source side                                                                                       |

| 13         | SCL_SRC                                                                                                                                           | IO     | DDC Clock on source side                                                                                      |

| 15         | Test                                                                                                                                              | I      | Must be tied LOW for normal operation                                                                         |

| 16         | 00.00                                                                                                                                             | т      | TMDS output pre-emphasis selection. See OC_S0 truth table for functionality.                                  |

| 16         | OC_80                                                                                                                                             | I      | This pin has internal 100K ohm pull-up                                                                        |

|            |                                                                                                                                                   |        | TMDS input equalization selection.                                                                            |

|            |                                                                                                                                                   |        | If LOW or floating, EQ is set at 9dB for all TMDS data inputs                                                 |

| 17         | IN_D1+ IN_D0- IN_D0+ IN_CLK- IN_CLK- IN_CLK+ HPD_SRC SDA_SRC SCL_SRC Test OC_S0  EQ_S0  OUT_CLK- OUT_D0- OUT_D0- OUT_D1- OUT_D1- OUT_D2- SCL_SINK | Q_S0 I | If HIGH, EQ is set at 15dB for all TMDS data inputs (please note, TMDS clock inputs are always set to 3dB EQ) |

|            |                                                                                                                                                   |        | This pin has an internal 100K ohm pull-down                                                                   |

| 18         | OUT_CLK+                                                                                                                                          | О      |                                                                                                               |

| 19         | OUT_CLK-                                                                                                                                          | О      |                                                                                                               |

| 20         | OUT_D0+                                                                                                                                           | О      |                                                                                                               |

| 21         | OUT_D0-                                                                                                                                           | О      |                                                                                                               |

| 23         | OUT_D1+                                                                                                                                           | О      | TMDS outputs.                                                                                                 |

| 24         | OUT_D1-                                                                                                                                           | О      |                                                                                                               |

| 25         | OUT_D2+                                                                                                                                           | О      |                                                                                                               |

| 26         | OUT_D2-                                                                                                                                           | О      |                                                                                                               |

| 27         | SCL_SINK                                                                                                                                          | IO     | Sink side DDC Clock                                                                                           |

| 28         | SDA_SINK                                                                                                                                          | IO     | Sink side DDC Data                                                                                            |

| 29         | HPD_SINK                                                                                                                                          | I      | Sink side hot plug detector input; internal pull-down at 120K ohm.                                            |

| 30         | /OE                                                                                                                                               | I      | Output Enable control. Active low. Internal 100K ohm pull-down. See truth table for functionality.            |

| 1, 22      | VDD                                                                                                                                               | PWR    | 3.3V power supply                                                                                             |

| 14, 31, 32 | GND                                                                                                                                               | Ground | Power Ground                                                                                                  |

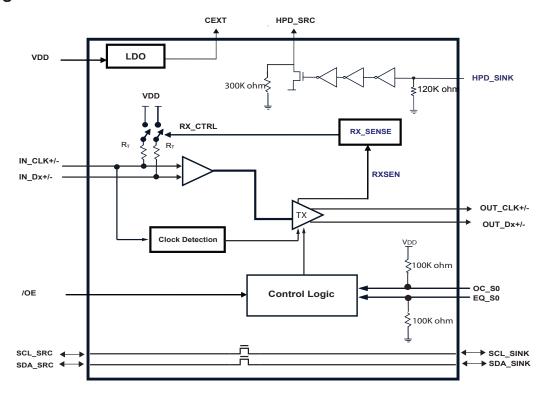

## **Block diagram:**

## **Description of Operation**

#### **Squelch function:**

Squelch control is using low frequency signal detection. When TMDS input clock frequency is less than 10MHz, it will show no input signal. When input signal is not present, IC will enter power-down mode.

#### **Rx-sense detector:**

The PI3HDMI511 will check 50 ohm termination resistor( $R_T$ ) within HDMI Rx chipset. If the  $R_T$ =50 ohm is not present, we assume no valid HDMI Rx is connected.

Therefore, IC will turn off our 50 ohm input termination resistor for all TMDS data and clock channels. When no valid  $R_{\rm T}$  = 50 ohm is detected in the HDMI Receiver, the IC will enter to the power-down mode.

#### OC\_S0 Truth Table

Note

#### **TMDS Output Pre-emphasis Setting**

| OC_S0<br>(internal<br>pull-up) | Single-end<br>Vswing (mV) | Pre-emphasis<br>(dB) |

|--------------------------------|---------------------------|----------------------|

| 0                              | 500                       | 0 (open drain)       |

| 1                              | 500                       | 2.5 (open drain)     |

#### Note

For clock channel, pre-emphesis value is fixed to 0 dB.

# EQ\_S0 Equalization

| EQ_S0 | Equalization |

|-------|--------------|

|       | (dB)         |

| 0     | 9dB          |

| 1     | 15dB         |

**TMDS Input Equalization Setting**

| /OE | Operation             |

|-----|-----------------------|

| 0   | Normal Operation Mode |

| 1   | Power Down Mode       |

#### Note

For CLK channel, the EQ value is fixed to 3dB.

**/OE Truth Table**

## **Absolute Maximum Ratings**

| Item                               | Rating                         |

|------------------------------------|--------------------------------|

| Supply Voltage to Ground Potential | 5.5V                           |

| All Inputs and Outputs             | -0.5V to V <sub>DD</sub> +0.5V |

| Storage Temperature                | -65 to +150°C                  |

| Junction Temperature               | 150°C                          |

| Soldering Temperature              | 260°C                          |

Note: Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **Recommended Operation Conditions**

| Parameter                                         | Min. | Тур. | Max. | Unit |

|---------------------------------------------------|------|------|------|------|

| Ambient Operating Temperature                     | -40  |      | +85  | °C   |

| Power Supply Voltage (measured in respect to GND) | 3.0  | 3.3  | 3.6  | V    |

## **DC** Specification

| Parameter            | Parameter                                   | Conditions                                                                     | Min. | Тур. | Max.                            | Unit |

|----------------------|---------------------------------------------|--------------------------------------------------------------------------------|------|------|---------------------------------|------|

| $V_{\mathrm{DD}}$    | Operating Voltage                           |                                                                                |      | 3.3  |                                 | V    |

| $I_{DD}$             | V <sub>DD</sub> Supply Current              | Output Enable (open drain 500mV single-ended 0dB pre-emphasis)                 |      | 120  | 150                             | mA   |

| Idd_Squelch          | Supply Current in squelch mode              | Input TMDS signal not valid,  /OE = Low                                        |      | 11   | 13                              | mA   |

| Idd_Rx<br>Sense      | supply current when no 50ohm detected in Rx | Input TMDS is valid, but 50ohm Rx<br>Sense(RXSEN) is not detected<br>/OE = Low |      | 4    | 5                               | mA   |

| I <sub>stb</sub>     | Standby mode                                | V <sub>DD</sub> =3.6V, HPD_SINK=0, /OE =<br>High                               |      | 4    | 5                               | mA   |

| V <sub>OL_HPD</sub>  | Open Drain Output Low Voltage               | $I_{OL} = 4 \text{ mA}$                                                        | 0    |      | 0.4                             | V    |

| Ionn repo            | Off leakage current                         | $V_{DD}$ =0, $V_{IN}$ =3.6 $V$                                                 |      |      | 20                              |      |

| I <sub>OFF_HPD</sub> | On leakage current                          | $V_{DD}=0, V_{IN}=5.5V$                                                        |      |      | 40                              |      |

| I                    | Open drain Output leakage                   | $V_{\rm DD}$ =3.6, $V_{\rm IN}$ =3.6 $V$                                       |      |      | 20                              | μΑ   |

| I <sub>OZ_HPD</sub>  | current                                     | $V_{\rm DD}$ =3.6, $V_{\rm IN}$ =5.5 $V$                                       |      |      | 13<br>5<br>5<br>0.4<br>20<br>40 |      |

| HDD OH            | ***                              |                                                                                                                     |      |      |      |       |

|-------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| HPD_SIN Symbol    | Parameter                        | Conditions                                                                                                          | Min. | Тур. | Max. | Units |

| I <sub>IH</sub>   | High level digital input current | V <sub>IH</sub> =VDD                                                                                                | 25   | тур. | 40   | μΑ    |

| I <sub>IL</sub>   | Low level digital input current  | V <sub>IL</sub> = GND                                                                                               | -10  |      | 10   | μΑ    |

|                   | High level digital input voltage | $V_{DD}=3.3V$                                                                                                       | 2.0  |      | 10   | V     |

| V <sub>IH</sub>   | Low level digital input voltage  | V DD=3.3 V                                                                                                          | 0    |      | 0.8  | V     |

| $V_{IL}$          | Low level digital input voltage  |                                                                                                                     | U    |      | 0.8  |       |

| Control P         | in (/OE)                         |                                                                                                                     |      |      |      |       |

| Symbol            | Parameter                        | Conditions                                                                                                          | Min. | Тур. | Max. | Unit  |

| I <sub>IH</sub>   | High level digital input current | V <sub>IH</sub> =VDD                                                                                                | 30   |      | 45   | μΑ    |

| $I_{\rm IL}$      | Low level digital input current  | V <sub>IL</sub> = GND                                                                                               | -10  |      | 10   | μΑ    |

| V <sub>IH</sub>   | High level digital input voltage |                                                                                                                     | 2.0  |      |      | V     |

| $V_{\mathrm{IL}}$ | Low level digital input voltage  |                                                                                                                     | 0    |      | 0.8  | V     |

| DDC Cha           | nnel Block                       |                                                                                                                     |      |      |      |       |

| Symbol            | Parameter                        | Conditions                                                                                                          | Min. | Тур. | Max. | Units |

| $C_{IO}$          | Input/Output capacitance         | $V_{\rm I}$ peak-peak = 1V, 100 KHz                                                                                 |      | 10   |      | pF    |

| R <sub>ON</sub>   | On resistance                    | $I_{O} = 3mA, V_{O} = 0.4V$                                                                                         |      | 25   | 50   | Ω     |

| V <sub>pass</sub> | Switch Output voltage            | $V_{I}$ =3.3V, $I_{I}$ =100uA<br>$V_{DD}$ =3.3V, External pull-up to<br>$VDD(15K \text{ ohm } \sim 5K \text{ ohm})$ | 1.5  | 2.0  | 2.5  | V     |

# Control Pins(OC\_S0 with 100K ohm pull-up)

| Symbol   | Parameter                      | Conditions           | Min. | Тур. | Max. | Units |

|----------|--------------------------------|----------------------|------|------|------|-------|

| $I_{IH}$ | High level logic input current | V <sub>IH</sub> =VDD |      |      | 10   | μΑ    |

| $I_{IL}$ | Low level logic input current  | V <sub>IL</sub> =GND |      | 35   | 50   | μΑ    |

## Control Pins(EQ\_S0 with 100K ohm pull-down)

| Symbol            | Parameter                      | Conditions           | Min. | Тур. | Max. | Units |

|-------------------|--------------------------------|----------------------|------|------|------|-------|

| $I_{IH}$          | High level logic input current | V <sub>IH</sub> =VDD |      | 35   | 50   | μΑ    |

| $I_{\mathrm{IL}}$ | Low level logic input current  | V <sub>IL</sub> =GND |      |      | 10   | μΑ    |

## **TMDS Differential Pins**

| Symbol Parameter | Conditions | Min. | Тур. | Max. | Units |

|------------------|------------|------|------|------|-------|

|------------------|------------|------|------|------|-------|

P-0.2

| V <sub>OH</sub>      | Single-ended high level output voltage                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>DD</sub> -10  |    | V <sub>DD</sub> +10  | mV |

|----------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----|----------------------|----|

| V <sub>OL</sub>      | Single-ended low level output voltage                           | tt $V_{DD}$ $V_{DD} = 3.3V, Rout=50 ohm$ | V <sub>DD</sub> -600 |    | V <sub>DD</sub> -400 | mV |

| V <sub>swing</sub>   | Single-ended output swing voltage                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 400                  |    | 600                  | mV |

| V <sub>OD(O)</sub>   | Overshoot of output differential voltage (1)                    | $V_{DD} = 3.3V$ , Rout=50 ohm                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |    | 180                  | mV |

| V <sub>OD(U)</sub>   | Undershoot of output differential voltage (2)                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |    | 200                  | mV |

| V <sub>OD(U)</sub>   | Change in steady-state common-mode output voltage between logic | - V <sub>DD</sub> = 3.3V, Rout=50 ohm                                                                                                                                                                                                                                                                                                                                                                                                                          |                      |    | 5                    | mV |

| т                    | Short Circuit output current                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -12                  |    | 12                   | A  |

| I <sub>OS</sub>      | Short Circuit output current                                    | at double termination mode                                                                                                                                                                                                                                                                                                                                                                                                                                     | -24                  |    | 24                   | mA |

| V <sub>I(open)</sub> | Single-ended input voltage under high impedance input or open   | $I_{\rm I} = 10 { m uA}$                                                                                                                                                                                                                                                                                                                                                                                                                                       | V <sub>DD</sub> -10  |    | V <sub>DD</sub> +10  | mV |

| R <sub>T</sub>       | Input termination resistance                                    | $V_{IN} = 2.9V$                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45                   | 50 | 55                   | Ω  |

| I <sub>OZ</sub>      | Leakage current with Hi-Z I/O                                   | $V_{DD} = 3.6V$ , /OE=High                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |    | 10                   | μΑ |

#### Note:

- 1. Overshoot of output differential voltage  $V_{OD(O)} = (V_{SWING(MAX)} * 2) * 15\%$ ,

- 2. Undershoot of output differential voltage  $V_{OD(U)} = (V_{SWING(MIN)} * 2) * 25\%$

## AC Characteristics (Over recommended operating conditions unless otherwise noted)

#### **TMDS Differential Pins**

| Symbol               | Parameter                                          | Conditions                                                               | Min. | Тур. | Max. | Units |

|----------------------|----------------------------------------------------|--------------------------------------------------------------------------|------|------|------|-------|

| t <sub>pd</sub>      | Propagation delay                                  | V <sub>DD</sub> = 3.3V, Rout = 50-ohm                                    |      |      | 2000 |       |

| t <sub>r</sub>       | Differential output signal rise time (20% - 80%)   |                                                                          |      |      | 190  | ps    |

| $t_{\mathrm{f}}$     | Differential output signal fall time (20% - 80%)   |                                                                          |      |      | 190  |       |

| t <sub>sk(p)</sub>   | Pulse skew                                         |                                                                          |      | 10   | 50   |       |

| t <sub>sk(D)</sub>   | Intra-pair differential skew                       |                                                                          |      | 23   | 50   |       |

| $t_{sk(o)}$          | Inter-pair differential skew                       |                                                                          |      |      | 100  |       |

| t <sub>jit(pp)</sub> | Peak-to-peak output jitter<br>CLK residual jitter  | Data Input = 1.65 Gbps HDMI<br>data pattern<br>CLK Input = 165 MHz clock |      | 15   | 30   | ps    |

| t <sub>jit(pp)</sub> | Peak-to-peak output jitter<br>DATA Residual Jitter |                                                                          |      | 18   | 50   |       |

| t <sub>en</sub>      | Enable time                                        |                                                                          |      |      | 1000 |       |

| t <sub>dis</sub>     | Disable time                                       |                                                                          |      |      | 10   | ns    |

## DDC I/O Pins (SCL\_SRC, SCL\_SINK, SDA\_SRC, SDA\_SINK)

| Symbol               | Parameter         | Conditions              | Min. | Тур. | Max. | Units |

|----------------------|-------------------|-------------------------|------|------|------|-------|

| t <sub>pd(DDC)</sub> | Propagation Delay | $C_{\rm L} = 10 \rm pF$ |      | 0.4  | 2.5  | ns    |

## Control and Status Pins (HPD\_SINK, HPD)

| Symbol               | Parameter         | Conditions                                                 | Min. | Тур. | Max. | Units |

|----------------------|-------------------|------------------------------------------------------------|------|------|------|-------|

| t <sub>pd(HPD)</sub> | Propagation Delay | $C_L = 10 pF$ , pull-up resistor=1K ohm, Open drain output |      | 10   |      | ns    |

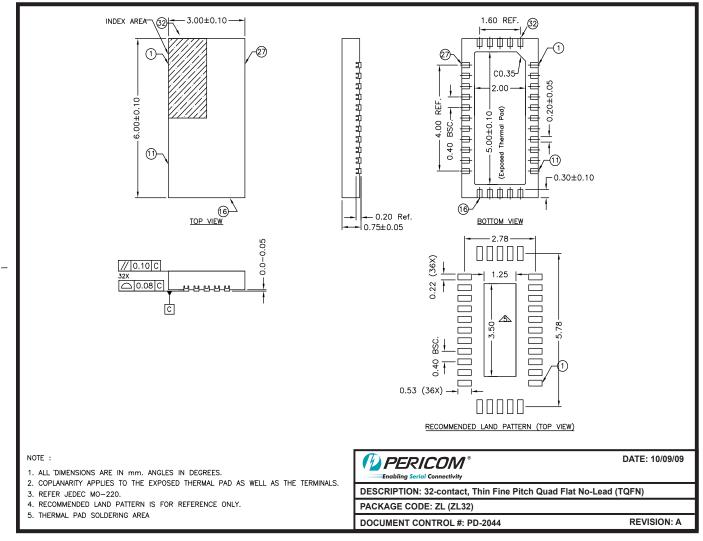

## Packaging Mechanical: 32-Contact TQFN (ZL)

Please check for the latest package information on the Pericom web site at www.pericom.com/packaging/.

07/10/12

www.pericom.com

# Related DisplayPort/Dual Mode DisplayPort Products

| Part Number  | Product Description                                                                                      | Availability |

|--------------|----------------------------------------------------------------------------------------------------------|--------------|

| PI3HDMI1201  | DisplayPort 1.2 Re-driver with built-in AUX listener                                                     | Now          |

| PI3VDP1430   | Dual Mode DisplayPort to HDMI Level Shifter and Re-driver                                                | Now          |

| PI3HDMI611   | 3.4G HDMI1.4 Re-driver for Sink application, supporting Dual Mode DisplayPort                            | Now          |

| PI3VDP3212   | 2-Lane DisplayPort1.2 Compliant Switch                                                                   | Now          |

| PI3VDP12412  | 4-Lane DisplayPort1.2 Compliant Switch                                                                   | Now          |

| PI3HDMI412AD | 1:2 Active 3.4Gbps HDMI1.4 compliant Splitter/Re-driver                                                  | Now          |

| PI3HDMI521   | 2:1 3.4Gbps HDMI1.4 Switch/Re-driver with built-in ARC and Fast Switching support for Source Application | Now          |

| PI3HDMI621   | 2:1 3.4Gbps HDMI1.4 Switch/Re-driver with built-in ARC and Fast Switching support for Sink Application   | Now          |

| PI3HDMI336   | 3:1 Active 3.4Gbps HDMI Switch/Re-driver with I <sup>2</sup> C control and ARC Transmitter               | Now          |

## **Reference Information**

| Document | Description                                                                                                                                                                                                                                                                                                                            |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN       | PI3HDMI511 HDMI1.4 Application Note                                                                                                                                                                                                                                                                                                    |

| VESA     | VESA DisplayPort Standard Version 1 Revision 2, Video Electronics Standards Association, January 5, 2010 VESA DisplayPort Dual-Mode Standard Version 1, Video Electronics Standards Association, February 10, 2012 VESA DisplayPort Interoperability Guideline Version 1.1a, Video Electronics Standards Association, February 5, 2009 |

| HDMI     | High-Definition Multimedia Interface Specification Version 1.4, HDMI Licensing, LLC, June 5, 2009                                                                                                                                                                                                                                      |

# **Ordering Information**

| Ordering Number | Package Code | Package Description             |

|-----------------|--------------|---------------------------------|

| PI3HDMI511ZLE   | ZLE          | Pb-free & Green 32-Contact TQFN |

<sup>•</sup> Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- E = Pb-free and Green

- X suffix = Tape/Reel

# **Revision Histroy**

| Date     | Changes                                                               |

|----------|-----------------------------------------------------------------------|

| 07/19/12 | Add Tr in the block diagram, IDD,Istb with Passive DDC level shifter. |

# **Appendix A: Generic Application Information**

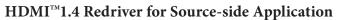

**Eye Diagram Performance:**

Figure 1: Eye Diagram at 1920x1080p 48bit Deep Color with 48" Input Trace, 9dB Equalization, 500mV Swing, 2.5dB Preemphasis.

## **Measurement setup:**

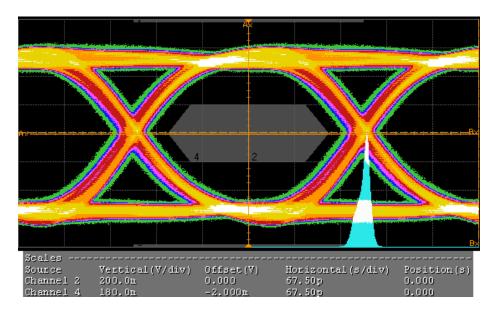

Figure 2: Test Setup of AC-coupled TMDS Input

Figure 3: Test Setup of DC-coupled TMDS Input

## **Application Information:**

Figure 4: Application Diagram

For more detailed application information, please refer to "PI3HDMI511\_HDMI\_ApplicationInformation.doc".

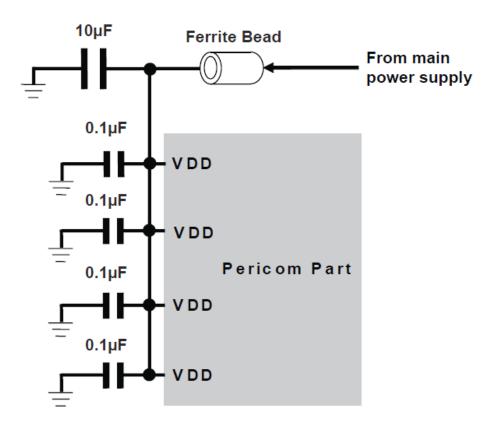

### **Recommended Power Supply Decoupling Circuit**

Figure 5 is the recommended power supply decoupling circuit configuration. It is recommended to put a  $0.1\mu F$  decoupling capacitors on each VDD pin of our part. Four  $0.1\mu F$  decoupling capacitors are put in Figure 5 with an assumption of only four VDD pins on our part.

On top of  $0.1\mu F$  decoupling capacitor on each VDD pin, it is recommended to put a  $10\mu F$  decoupling capacitor near our part's VDD for stabilizing the power supply for our part. Ferrite bead is also recommended for

isolating the power supply for our part and other power supplies in other parts of the circuit. But, it is optional and depends on the power supply conditions of other circuits.

Figure 5 Recommended Power Supply Decoupling Circuit Diagram

#### Requirements on the Decoupling Capacitors

- i: There is no special requirement on the material of the capacitors. Ceramic capacitors are generally being used with typically materials of X5R or X7R.

- ii: 0.1uF decoupling capacitor in 0402 package is recommended.

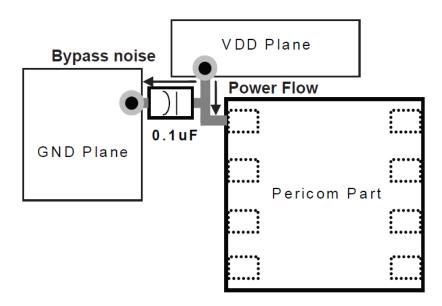

#### Layout and Decoupling Capacitor Placement Consideration

- i. Each 0.1µF decoupling capacitor should be placed as close as possible to each VDD pin.

- ii. VDD and GND planes should be used to provide a low impedance path for power and ground.

- iii. Via holes should be placed to connect to VDD and GND planes directly.

- iv. The width between the traces should be as wide as possible.

- v. Trace length should be as short as possible.

- vi. The placement of decoupling capacitor and the way of routing trace should consider the power flowing criteria.

- vii. 10µF capacitor should also be placed close to our part and should be placed in the middle location of 0.1µF capacitors.

- viii. Avoid the large current circuit placed close to our part; especially when it is shared the same VDD and GND planes, since large current flowing on our VDD or GND planes will generate a potential variation on the VDD or GND of our part.

Figure 6 Layout and Decoupling Capacitor Placement Diagram

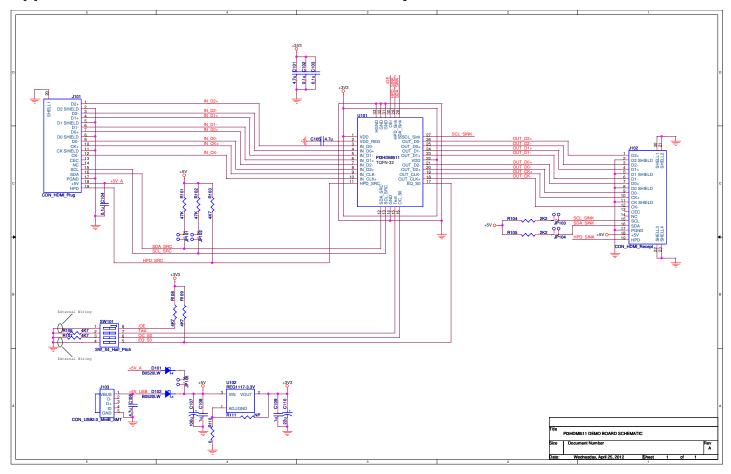

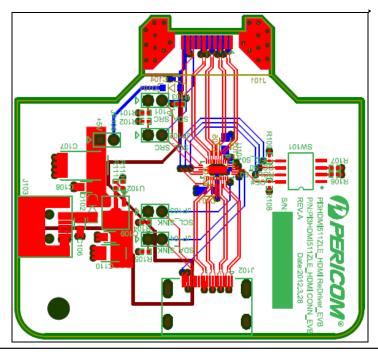

# **Appendix B: Evaluation Board Schematic and Layout**