Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# HDMI 2.0, DisplayPort 1.2 Video Switch

#### **Features**

- → 4-lane, 1:2 mux/demux that will support RBR, HBR1, or HBR2

- → Data rate: 3.4 Gbps to 6.0 Gbps for high data channels

- → 1-channel 1:2 mux/demux for HPD signal

- → Differential switch matrix for DP AUX and HDMI DDC

- → supports 720 Mbps high-speed DP AUX

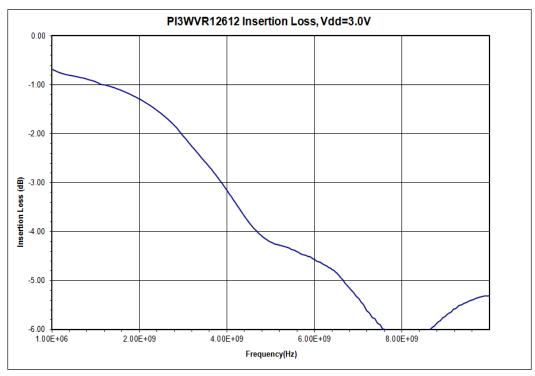

- → -2.0 dB Insertion Loss for Dx channels @ 3 GHz

- → -3 dB Bandwidth for Dx channels: 4.1 GHz

- → Return loss for Dx channels @ 3 GHz: -12 dB

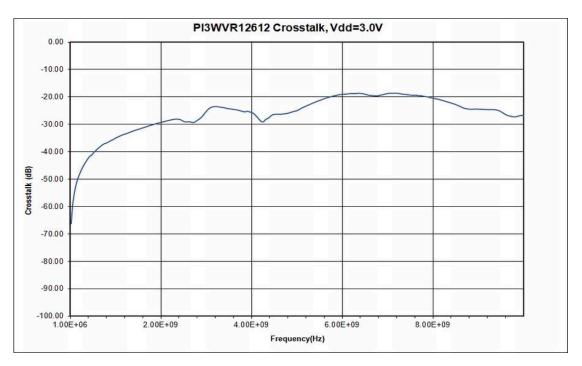

- → Low Crosstalk for high speed channels: -25 dB@ 6 Gbps

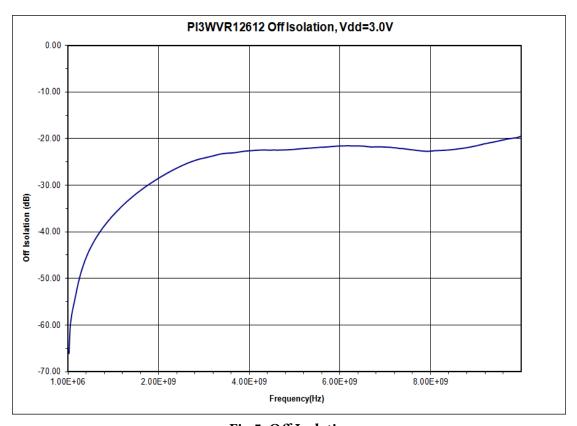

- → Low Off Isolation for high speed channels: -24dB@ 6 Gbps

- → Low channel-to-channel skew, 35ps max

- → Low Bit-to-Bit Skew, 5ps typ (between '+' and '-' bits)

- → V<sub>DD</sub> Operating Range: 3.3V +/-10%

- → ESD Tolerance: 2kV HBM

- → Packaging (Pb-free & Green):

- -50-ball TFBGA (NEE)

- -52-pin TQFN (ZL52)

#### **Description**

Pericom Semiconductor's PI3WVR12612 is a multi-standard video switch with wide voltage range capability. It supports DisplayPort 1.2, HDMI 2.0, and emerging and proprietary standards.

PI3WVR12612 can pass high-speed signals up to 1.2 V peak-to-peak differential with a common-mode voltage from 0 to 3.4V. The wide voltage range allows DC-coupled multi-standard operation. Eliminating AC coupling capacitors saves board space and improves signal integrity for dense PCB designs.

The high speed channels can also pass 0V-3.3V CMOS signals up to 1MHz.

In addition to four high-speed lanes, PI3WVR12612 also switches AUX, DDC, and HPD signals.

## **Application**

Routing of DisplayPort and HDMI signals with low signal attenuation between source and sink.

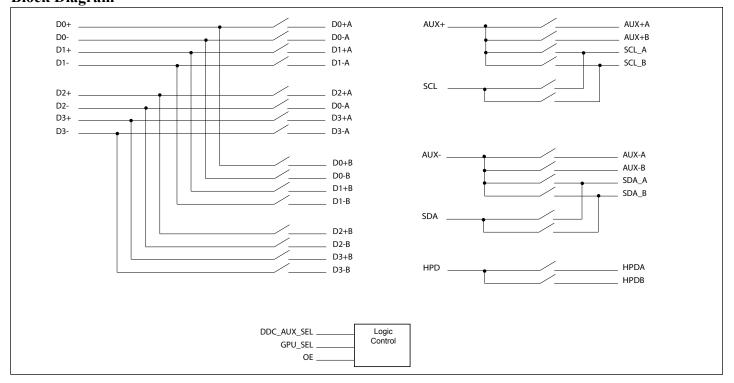

#### **Block Diagram**

### Pin Assignment (50-Ball TFBGA, NEE)

| D3-A  | D3+A                |     |       |       |      |       |                     | -       |             |

|-------|---------------------|-----|-------|-------|------|-------|---------------------|---------|-------------|

| D0-B  |                     |     | D2-A  | D1-A  | D0-A |       | VDD                 | GPU_SEL | А           |

|       | D0+B                | OE  | D2+A  | D1+A  | D0+A | GND   | D0+                 | D0-     | В           |

|       | GND                 |     |       |       |      |       | DDC_<br>AUX_<br>SEL |         | С           |

| D1-B  | D1+B                |     |       |       |      |       | D1+                 | D1-     | D           |

| D2-B  | D2+B                |     |       |       |      |       | D2+                 | D2-     | E           |

| D3-B  | D3+B                |     |       |       |      |       | D3+                 | D3-     | F           |

|       | GND                 |     |       |       |      |       | GND                 |         | G           |

| AUX+A | SCL_A               | GND | AUX+B | SCL_B | GND  | HPD_B | AUX+                | AUX-    | н           |

| AUX-A | SDA_A               | SDA | AUX-B | SDA_B | Vdd  | SCL   | HPD_A               | HPD     | J           |

|       | D2+B D3+B GND SCL_A |     |       |       |      |       | D2+ D3+ GND AUX+    | D2-     | E<br>F<br>G |

#### **Truth Table**

|      | Control     |                     |           | Switch | Functio | n     |

|------|-------------|---------------------|-----------|--------|---------|-------|

| OE   | GPU_<br>SEL | DDC_<br>AUX_<br>SEL | D0-<br>D3 | AUX    | HPD     | DDC   |

| High | Low         | Low                 | A         | AUX A  | HPD A   | Hi-Z  |

| High | High        | Low                 | В         | AUX B  | HPD B   | Hi-Z  |

| High | Low         | High                | A         | DDC A  | HPD A   | Hi-Z  |

| High | High        | High                | В         | DDC B  | HPD B   | Hi-Z  |

| High | Low         | Medium              | A         | AUX A  | HPD A   | DDC A |

| High | High        | Medium              | В         | AUX B  | HPD B   | DDC B |

| Low  | x           | x                   | Hi-Z      | Hi-Z   | Hi-Z    | Hi-Z  |

→ Medium level = 1/2 VDD = 1.65V

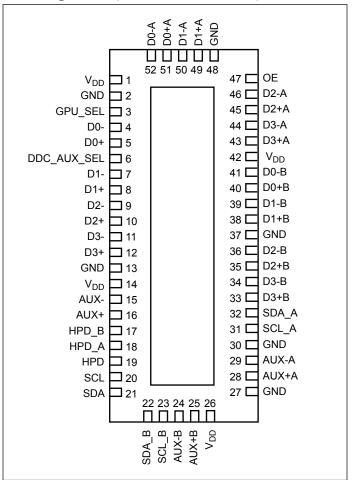

### Pin Assignment (52-Pin TQFN, ZL52)

## **Pin Description**

| pin# | pin Name | Signal Type | Description                                    |  |

|------|----------|-------------|------------------------------------------------|--|

| A1   | GPU_SEL  | I           | switch logic control                           |  |

| B1   | D0-      | I/O         | negative differential signal 0 for COM port    |  |

| B2   | D0+      | I/O         | positive differential signal 0 for COM port    |  |

| D1   | D1-      | I/O         | negative differential signal 1 for COM port    |  |

| D2   | D1+      | I/O         | positive differential signal 1 for COM port    |  |

| E1   | D2-      | I/O         | negative differential signal 2 for COM port    |  |

| E2   | D2+      | I/O         | positive differential signal 2 for COM port    |  |

| F1   | D3-      | I/O         | negative differential signal 3 for COM port    |  |

| F2   | D3+      | I/O         | positive differential signal 3 for COM port    |  |

| В3   | GND      | Ground      | Ground                                         |  |

| H1   | AUX-     | I/O         | negative differential signal for AUX COM port  |  |

| H2   | AUX+     | I/O         | posititve differential signal for AUX COM port |  |

| J1   | HPD      | I/O         | HPD for COM port                               |  |

| J2   | HPD_A    | I/O         | HPD for port A                                 |  |

| H3   | HPD_B    | I/O         | HPD for port B                                 |  |

| C8   | GND      | Ground      | Ground                                         |  |

| J4   | VDD      | Pwr         | 3.3V +/-10% power supply                       |  |

| G2   | GND      | Ground      | Ground                                         |  |

| H6   | AUX+B    | I/O         | positive differential signal for AUX, port B   |  |

| J6   | AUX-B    | I/O         | negative differential signal for AUX, port B   |  |

| H9   | AUX+A    | I/O         | positive differential signal for AUX, port A   |  |

| J9   | AUX-A    | I/O         | negative differential signal for AUX, port A   |  |

| G8   | GND      | Ground      | Ground                                         |  |

| F8   | D3+B     | I/O         | positive differential signal 3 for portB       |  |

| F9   | D3-B     | I/O         | negative differential signal 3 for portB       |  |

| E8   | D2+B     | I/O         | positive differential signal 2 for portB       |  |

| E9   | D2-B     | I/O         | negative differential signal 2 for portB       |  |

| D8   | D1+B     | I/O         | positive differential signal 1 for portB       |  |

| D9   | D1-B     | I/O         | negative differential signal 1 for portB       |  |

| B8   | D0+B     | I/O         | positive differential signal 0 for portB       |  |

| В9   | D0-B     | I/O         | negative differential signal 0 for portB       |  |

(Continued)

| pin# | pin Name        | Signal Type | Description                                                                                            |  |

|------|-----------------|-------------|--------------------------------------------------------------------------------------------------------|--|

| A8   | D3+A            | I/O         | positive differential signal 3 for port A                                                              |  |

| A9   | D3-A            | I/O         | negative differential signal 3 for port A                                                              |  |

| H4   | GND             | Ground      |                                                                                                        |  |

| В6   | D2+A            | I/O         | positive differential signal 2 for port A                                                              |  |

| A6   | D2-A            | I/O         | negative differential signal 2 for port A                                                              |  |

| B5   | D1+A            | I/O         | positive differential signal 1 for port A                                                              |  |

| A5   | D1-A            | I/O         | negative differential signal 1 for port A                                                              |  |

| B4   | D0+A            | I/O         | positive differential signal 0 for port A                                                              |  |

| A4   | D0-A            | I/O         | negative differential signal 0 for port A                                                              |  |

| A2   | VDD             | Pwr         | Power                                                                                                  |  |

| C2   | DDC_<br>AUX_SEL | I           | switch logic control                                                                                   |  |

| H5   | SCL_B           | I/O         | DDC_clock channel for port B                                                                           |  |

| H7   | GND             | Ground      |                                                                                                        |  |

| Н8   | SCL_A           | I/O         | DDC_clock channel for port A                                                                           |  |

| J5   | SDA_B           | I/O         | DDC_data channel for port B                                                                            |  |

| J8   | SDA_A           | I/O         | DDC_data channel for port A                                                                            |  |

| J3   | SCL             | I/O         | DDC_clock channel for COM port                                                                         |  |

| J7   | SDA             | I/O         | DDC_data channel for COM port                                                                          |  |

| B7   | OE              | I           | Output enable. if OE is high, IC is enabled. If OE is low, then IC is power down and all I/Os are hi-z |  |

15-0175

## **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.)

| , , ,                              | 9 , ,                   |

|------------------------------------|-------------------------|

| Storage Temperature                | 65°C to +150°C          |

| Supply Voltage to Ground Potential | 0.5V to +4.2V           |

| DC Input Voltage                   | 0.5V to V <sub>DD</sub> |

| High Speed Data Channel            | -0.5V to 3.8V           |

| HPD_x, SDA_x, SCL_x                | -0.5V to 5.5V           |

| DC Output Current                  | 120mA                   |

| Power Dissipation                  | 0.5W                    |

|                                    |                         |

Note: Stresses greater than those listed under MAXI-MUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### DC Electrical Characteristics for Switching over Operating Range ( $T_A = -40$ °C to +105°C, $V_{DD} = -40$ °C to +105°C, + $3.3V \pm 10\%$

| Parameter                    | Description                                                            | Test Conditions(1)                                                                                                                         | Min                          | Typ <sup>(2)</sup> | Max                          | Units    |

|------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------|------------------------------|----------|

| V <sub>IH</sub>              | Input HIGH Voltage (OE, GPU_SEL)                                       | Guaranteed HIGH level                                                                                                                      | 1.5                          |                    |                              |          |

| VIL                          | Input LOW Voltage (OE, GPU_SEL)                                        | Guaranteed LOW level                                                                                                                       |                              |                    | 0.75                         |          |

| V <sub>IH</sub>              | Input HIGH Voltage (DDC_AUX_SEL)                                       | Guaranteed HIGH level                                                                                                                      | 2.65                         |                    | $V_{\mathrm{DD}}$            |          |

| V <sub>IM</sub>              | Input Mid-Level Voltage (DDC_AUX_<br>SEL)                              | Guaranteed MID level                                                                                                                       | V <sub>DD</sub> /2-<br>300mV | V <sub>DD</sub> /2 | V <sub>DD</sub> /2+<br>300mV | V        |

| $v_{IL}$                     | Input LOW Voltage (DDC_AUX_SEL)                                        | Guaranteed LOW level                                                                                                                       | -0.5                         |                    | 0.6                          |          |

| V <sub>IK</sub>              | Clamp Diode Voltage (HS Channel)                                       | $V_{\mathrm{DD}} = \mathrm{Max.}, I_{\mathrm{IN}} = -18\mathrm{mA}$                                                                        |                              | -1.6V              | -1.8                         |          |

| V <sub>IK</sub>              | Clamp Diode Voltage (Aux, Cntrl )                                      | $V_{\mathrm{DD}} = \mathrm{Max.}, I_{\mathrm{IN}} = -18\mathrm{mA}$                                                                        |                              | -0.7               | -1.5                         |          |

| IIH                          | Input HIGH Current (All Control Pins)                                  | $V_{DD} = Max., V_{IN} = V_{DD}$                                                                                                           |                              |                    | ±5                           |          |

| IIL                          | Input LOW Current (All Control Pins)                                   | V <sub>DD</sub> = Max., V <sub>IN</sub> = GND                                                                                              |                              |                    | ±5                           | μΑ       |

| I <sub>OFF_SB</sub>          | I/O leakage when part is off for sideband signals only (DDC, AUX, HPD) | $V_{DD} = 0V$ , $V_{INPUT} = 0V$ to 3.6V                                                                                                   |                              |                    | 20                           | W11      |

| R <sub>ON_HS</sub>           | On resistance between input to output for high speed signals           | $\begin{split} V_{INPUT,cm} &= 0V \text{ to } 3.4V, \\ V_{INPUT,diff} &< 1.2V_{p-p,diff}, \\ V_{DD} &= 3.0V, I_{INPUT} = 20mA \end{split}$ |                              | 11                 |                              | Ohm      |

| R <sub>ON_AUX</sub>          | On resistance between input to output for side-band signals (AUX)      | $V_{\mathrm{DD}} = 3.0 \mathrm{V}$ , $V_{\mathrm{input}} = 0$ to $3.3 \mathrm{V}$ , $I_{\mathrm{INPUT}} = 20 \mathrm{mA}$                  |                              | 7                  |                              | Ohm      |

| R <sub>ON_DDC</sub>          | On resistance between input to output for DDC channel                  | $V_{\mathrm{DD}} = 3.0 \mathrm{V}$ , $V_{\mathrm{input}} = 0 \mathrm{V}$ , $I_{\mathrm{INPUT}} = 20 \mathrm{mA}$                           |                              | 12                 |                              | Ohm      |

| R <sub>ON_HPD</sub>          | On resistance between input to output for HPD channel                  | $V_{\mathrm{DD}}$ = 3.0V, Vinput = 0 to 3.0V, $I_{\mathrm{INPUT}}$ = 20mA                                                                  |                              | 7                  |                              | Ohm      |

| V <sub>AUX_SS</sub>          | Signal Swing Tolerance in Aux path                                     | $V_{DD} = 3.0V$                                                                                                                            | -0.5                         |                    | 5.5                          | V        |

| $V_{HPD\_I}$                 | Input voltage on HPD path                                              |                                                                                                                                            |                              |                    | 5.5                          | V        |

| V <sub>HPD_O</sub>           | Output voltage tolerance on HPD path                                   | HPD input from 3.3V to 5.25V                                                                                                               |                              | 3.3                | 3.6                          | V        |

| V <sub>SDA_X</sub>           | Input Voltage on SDA path                                              |                                                                                                                                            |                              | 5                  |                              | V        |

| V <sub>PASS</sub><br>(SDA_X) | Switch output voltage tolerance input                                  | V <sub>in</sub> = 5.25V, Ii = 100uA, V <sub>DD</sub><br>= 3.3V                                                                             | 1.8                          | 2.2                | 2.5                          | V        |

| $V_{SCL\_X}$                 | Input Voltage on SCL path                                              |                                                                                                                                            |                              | 5                  |                              | V        |

| V <sub>PASS</sub> (SCL_X)    | Switch output voltage tolerance input                                  | V <sub>in</sub> = 5.25V, Ii = 100uA, V <sub>DD</sub><br>= 3.3V                                                                             | 1.8                          | 2.2                | 2.5                          | V        |

| All trademarks are pr        | roperty of their respective owners. 15-0175                            | 5                                                                                                                                          | www.perio                    | com.com            |                              | 12/03/15 |

## Power Supply Characteristics ( $T_A = -40^{\circ}\text{C} \text{ to } +105^{\circ}\text{C}$ )

| Parameter         | ameter Description Test Conditions <sup>(1)</sup> |                                                                   | Min | Typ(2) | Max | Units |

|-------------------|---------------------------------------------------|-------------------------------------------------------------------|-----|--------|-----|-------|

| $I_{\mathrm{DD}}$ | Power Supply Current                              | $V_{DD}$ = 3.3V, $V_{IN}$ = GND or $V_{DD}$                       |     | 1      | 3   | mA    |

| $I_{ m DD,Off}$   | Power Supply Current, Disabled                    | $V_{DD}$ = 3.3V, $V_{IN}$ = GND or $V_{DD}$ , $V_{OE}$ < $V_{IL}$ |     | 1      | 50  | μΑ    |

<sup>1.</sup> For Max. or Min. conditions, use appropriate value specified under Electrical Characteristics for the applicable device type.

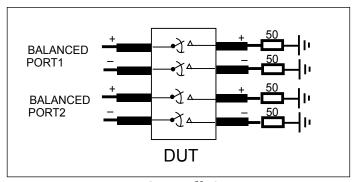

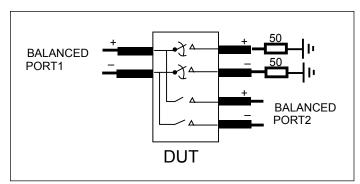

Dynamic Electrical Characteristics over Operating Range ( $T_A = -40^{\circ}$  to  $+105^{\circ}$ C,  $V_{DD} = 3.3$ V  $\pm 10\%$ )

| Parameter         | Description                                   | Test Conditions <sup>1</sup>     | - 7          | Min  | Typ <sup>2</sup> | MAX   | Units |

|-------------------|-----------------------------------------------|----------------------------------|--------------|------|------------------|-------|-------|

|                   |                                               |                                  | f= 3.0 GHz   |      | -25              | -22   |       |

| X <sub>TALK</sub> | Crosstalk on High Speed Channels              | See Fig. 1 for Measurement Setup | f= 2.7 GHz   |      | -28              | -25   |       |

|                   | licis                                         | ment setup                       | f = 1.35 GHz |      | -32              | -28   |       |

|                   |                                               | See Fig. 2 for Measure-          | f= 3.0 GHz   |      | -24              | -20   | dB    |

| O <sub>IRR</sub>  | OFF Isolation on High Speed<br>Channels       | ment Setup,                      | f= 2.7 GHz   |      | -25              | -22   |       |

|                   | Oldinicis                                     |                                  | f = 1.35 GHz |      | -30              | -27   |       |

| _                 | Differential Insertion Loss on                | @6.0Gbps (see figure 4)          |              | -2.3 | -2.0             |       | 1D    |

| $I_{LOSS}$        | High Speed Channels                           | @5.4Gbps (see figure 3)          |              | -2.0 | -1.8             |       | dB    |

| D.                | Differential Return Loss on high              | @3.0GHz (6.0Gbps)                |              |      | -12              | -11   | מנ    |

| R <sub>loss</sub> | speed channels                                | @ 2.7GHz (5.4Gbps)               |              |      | -14              | -12.5 | dB    |

| BW_Dx±            | Bandwidth -3dB for Main high speed path (Dx±) | See figure 3                     |              | 3.7  | 4.1              |       | GHz   |

| BW_AUX/<br>HPD    | -3dB BW for AUX, DDC, and<br>HPD signals      | See figure 3                     |              | 1.35 | 1.5              |       | GHz   |

<sup>1.</sup> For Max. or Min. conditions, use appropriate value specified under Electrical Characteristics for the applicable device type.

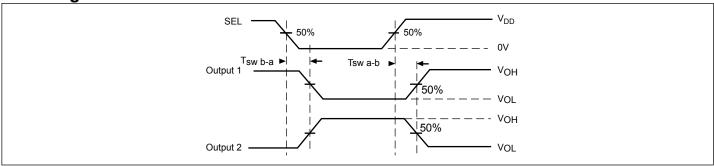

## Switching Characteristics ( $T_A = -40^{\circ} \text{ to } +105^{\circ}\text{C}$ , $V_{DD} = 3.3V \pm 10\%$ )

| Parameter          | Description                                                       |  | Тур. | Max. | Units |

|--------------------|-------------------------------------------------------------------|--|------|------|-------|

| $T_{pd}$           | Propagation delay (input pin to output pin) on Dx± channels       |  | 80   |      | ps    |

| t <sub>b-b</sub>   | Bit-to-bit skew within the same differential pair of Dx± channels |  | 5    | 7    | ps    |

| t <sub>ch-ch</sub> | Channel-to-channel skew of Dx± channels                           |  |      | 35   | ps    |

| Tsw a-b            | time it takes to switch from port A to port B                     |  |      | 0.1  | us    |

| Tsw b-a            | time it takes to switch from port B to port A                     |  |      | 0.1  | us    |

| Tstartup           | Vdd valid to channel enable                                       |  |      | 10   | us    |

| Twakeup            | Enabling output by changing OE from low to High                   |  |      | 10   | us    |

<sup>2.</sup> Typical values are at  $V_{DD}$  = 3.3V,  $T_A$  = 25°C ambient and maximum loading.

<sup>2.</sup> Typical values are at  $V_{DD}$  = 3.3V,  $T_A$  = 25°C ambient and maximum loading.

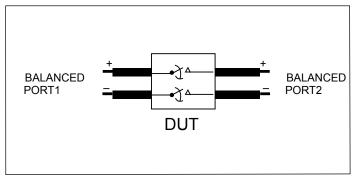

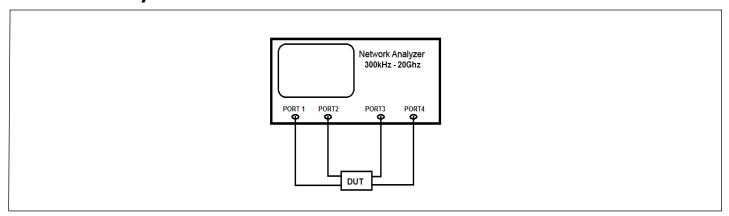

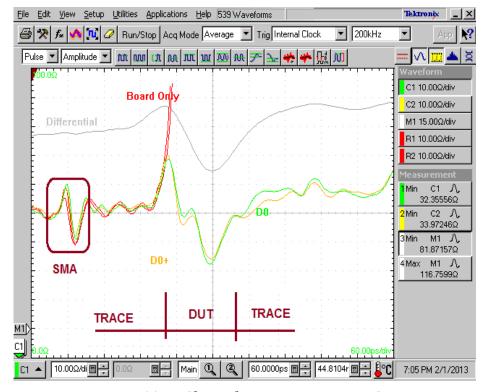

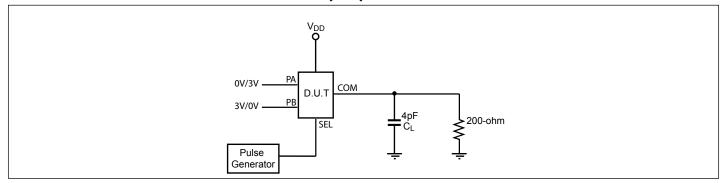

Fig 1. Crosstalk Setup

Fig 2. Off-isolation setup

Fig 3. Differential Insertion Loss

## **Test Circuit for Dynamic Electrical Characteristics**

Fig 4. Crosstalk

Fig 5. Off Isolation

Fig 6. Insertion Loss

Fig 7. TDR Channel D0, VDD= 3.0V, 25C

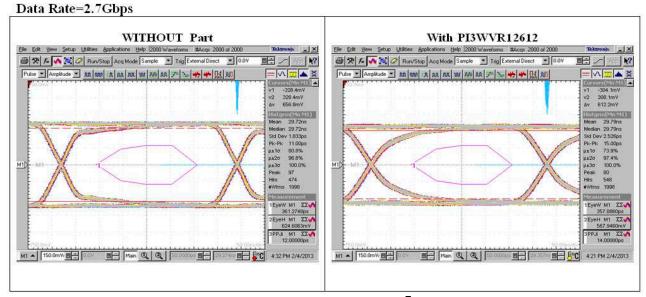

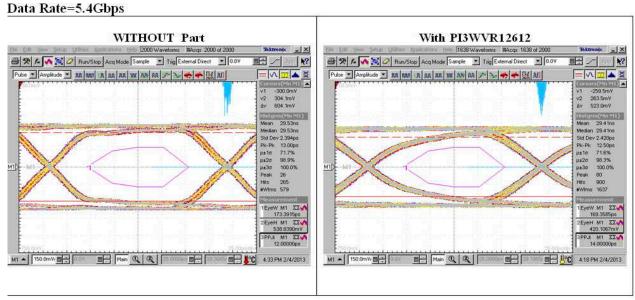

Fig 8. Differential output Eye at Input signal is a 2<sup>7</sup>-1 PRBS, Vdd=3.0V, 25C, Input swing is 800mV differential

Fig 9. Differential output Eye at Input signal is a 2<sup>7</sup>-1 PRBS, Vdd=3.0V, 25C, Input swing is 800mV differential

www.pericom.com

## Test Circuit for Electrical Characteristics(1-5)

#### Notes:

- 1.  $C_L$  = Load capacitance: includes jig and probe capacitance.

- 2.  $R_T$  = Termination resistance: should be equal to  $Z_{OUT}$  of the Pulse Generator

- 3. All input impulses are supplied by generators having the following characteristics:  $PRR \le MHz$ ,  $Z_O = 50\Omega$ ,  $t_R \le 2.5ns$ ,  $t_F \le 2.5ns$ .

- 4. The outputs are measured one at a time with one transition per measurement.

## **Switching Waveforms**

**Voltage Waveforms Enable and Disable Times**

#### **Test Condition**

| Output 1 Test Conditon | Output 2 Test Conditon |

|------------------------|------------------------|

| PA = Low               | PA = High              |

| PB = High              | PB = Low               |

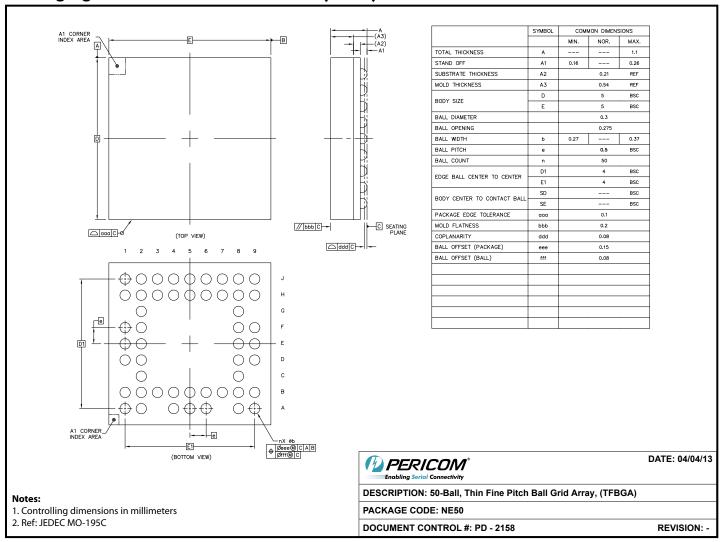

## Packaging Mechanical: 50-Ball TFBGA (NE50)

13-0150

15-0175

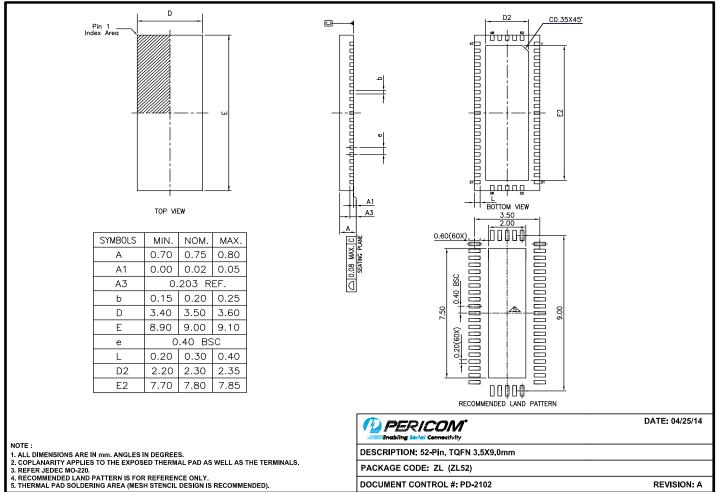

## Packaging Mechanical: 52-Pin TQFN (ZL52)

#### 14-0122

Note:

For latest package info, please check: http://www.pericom.com/products/packaging/mechanicals.php

## **Ordering Information**

| Ordering Code   | Package Code | Package Description                                          |

|-----------------|--------------|--------------------------------------------------------------|

| PI3WVR12612NEE  | NE           | 50-Pin, Thin Fine Pitch Ball Grid Array (TFBGA)              |

| PI3WVR12612NEEX | NE           | 50-Pin, Thin Fine Pitch Ball Grid Array (TFBGA), Tape & Reel |

| PI3WVR12612ZLE  | ZL           | 52-Pin, 3.5 x 9.0 mm (TQFN)                                  |

| PI3WVR12612ZLEX | ZL           | 52-Pin, 3.5 x 9.0 mm (TQFN), Tape & Reel                     |

#### Notes:

- Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- "E" denotes Pb-free and Green

- · Adding an "X" at the end of the ordering code denotes tape and reel packaging

Pericom Semiconductor Corporation • 1-800-435-2336

13

15-0175