# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

**PI4GTL2014**

4-bit LVTTL to GTL transceiver

# Features

- Operates as a 4-bit GTL /GTL/GTL+ sampling receiver or as a LVTTL to GTL /GTL/GTL+ driver

- 2.3 V to 3.6 V operation with 5 V tolerant LVTTL input

- GTL input and output 3.6 V tolerant

- Vref adjustable from 0.5 V to VCC/2

- Partial power-down permitted

- ESD protection exceeds 2000 V HBM per JESD22-A114 and 1000 V CDM per JESD22-CC101

- Latch-up protection exceeds 200 mA per JESD78

- Package offered: TSSOP14

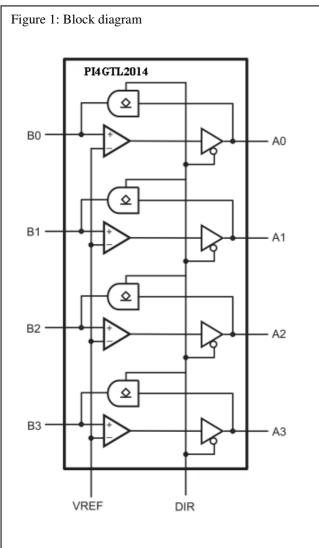

**Pin Configuration**

# Description

The PI4GTL2014 is a 4-bit translating transceiver designed for 3.3 V LVTTL system interface with a GTL – /GTL/GTL+ bus, where GTL – /GTL/GTL+ refers to the reference voltage of the GTL bus and the input/output voltage thresholds associated with it.

The direction pin allows the part to function as either a GTL to LVTTL sampling receiver or as a LVTTL to GTL interface.

The PI4GTL2014 LVTTL inputs (only) are tolerant up to 5.5 V allowing direct access to TTL or 5 V CMOS inputs. The LVTTL outputs are not 5.5 V tolerant.

The PI4GTL2014 GTL inputs and outputs operate up to 3.6 V, allowing the device to be used in higher voltage open-drain output applications.

# **Pin Description**

| DIR 1       | $\bigcirc$ | 14 | VCC |

|-------------|------------|----|-----|

| B0 2        | $\bigcirc$ | 13 | A0  |

| <b>B1</b> 3 |            | 12 | A1  |

| VREF 4      |            | 11 | GND |

| <b>B2</b> 5 |            | 10 | A2  |

| B3 6        |            | 9  | A3  |

| GND 7       |            | 8  | GND |

|             |            |    |     |

| DIR  | 1      | direction control input (LVTTL) |  |

|------|--------|---------------------------------|--|

| B0   | 2      | data inputs/outputs (GTL)       |  |

| B1   | 3      |                                 |  |

| B2   | 5      |                                 |  |

| B3   | 6      |                                 |  |

| A0   | 13     | data inputs/outputs (LVTTL)     |  |

| A1   | 12     |                                 |  |

| A2   | 10     |                                 |  |

| A3   | 9      |                                 |  |

| VREF | 4      | GTL reference voltage           |  |

| GND  | 7,8,11 | ground (0 V)                    |  |

| VCC  | 14     | positive supply voltage         |  |

1

**PI4GTL2014**

4-bit LVTTL to GTL transceiver

# **Maximum Ratings**

| Power supply                           | 0.5V to +4.6V     |

|----------------------------------------|-------------------|

| Voltage on an I/O pin                  | GND-0.5V to +7.0V |

| Supply current                         | ±160mA            |

| Ground supply current                  |                   |

| Total power dissipation                |                   |

| Operation temperature                  | 40~85°C           |

| Storage temperature                    | 65~150°C          |

| Maximum Junction temperature, T j(max) | 125°C             |

| Total power dissipation                |                   |

|                                        |                   |

### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

**Function Table:** H = HIGH voltage level; L = LOW voltage level.

| DIR | A (LVTTL) | B (GTL) |

|-----|-----------|---------|

| Н   | Input     | Output  |

| L   | Output    | Input   |

**PI4GTL2014**

### 4-bit LVTTL to GTL transceiver

# Limiting values

| Symbol          | Parameter                 | Conditions                                                 | Min.                | Max. | Unit |

|-----------------|---------------------------|------------------------------------------------------------|---------------------|------|------|

| VCC             | supply voltage            |                                                            | -0.5                | 4.6  | V    |

| I <sub>IK</sub> | input clamping current    | VI <0V                                                     | -                   | -50  | mA   |

| VI              | input voltage             | A port                                                     | -0.5 <sup>[1]</sup> | 7    | V    |

|                 |                           | B port                                                     | $-0.5^{[1]}$        | 4.6  | V    |

| I <sub>OK</sub> | output clamping current   | A port; VO <0V                                             | -                   | -50  | mA   |

| V <sub>0</sub>  | output voltage            | output in OFF or<br>HIGH state                             |                     |      |      |

|                 |                           | A port                                                     | $-0.5^{[1]}$        | 7    | V    |

|                 |                           | B port                                                     | $-0.5^{[1]}$        | 4.6  | V    |

| I <sub>OL</sub> | LOW-level output current  | current into any<br>output in the<br>LOW state             |                     |      |      |

|                 |                           | A port                                                     | -                   | 32   | mA   |

|                 |                           | B port                                                     | -                   | 80   | mA   |

| I <sub>OH</sub> | HIGH-level output current | current into any<br>output in the<br>HIGH state; A<br>port | -                   | -32  | mA   |

| Tstg            | storage temperature       |                                                            | [2] -60             | 150  | °C   |

Note:

[1] The input and output negative voltage ratings may be exceeded if the input and output clamp current ratings are observed.

[2] The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction temperatures which are detrimental to reliability. The maximum junction temperature of this integrated circuit should not exceed 150 °C.

**PI4GTL2014**

4-bit LVTTL to GTL transceiver

# **Operating conditions**<sup>[1]</sup>

| Symbol   | Parameter                          | Conditions                | Min.         | Тур.               | Max.               | Unit |

|----------|------------------------------------|---------------------------|--------------|--------------------|--------------------|------|

| VCC      | supply voltage                     |                           | 2.3          | -                  | 3.6                | V    |

|          |                                    | Lowest voltage            | 0.71         | 0.75               | 0.79               | V    |

| $V_{TT}$ | termination voltage <sup>[2]</sup> | GTL-                      | 0.85         | 0.9                | 0.95               | V    |

|          |                                    | GTL                       | 1.14         | 1.2                | 1.26               | V    |

|          |                                    | GTL+                      | 1.35         | 1.5                | 1.65               | V    |

| Vref     | reference voltage                  | overall                   | 0.43         | 2/3V <sub>TT</sub> | VCC/2              | V    |

|          |                                    | Lowest<br>voltage         | 0.43         | 0.5                | 0.55               |      |

|          |                                    | GTL-                      | 0.5          | 0.6                | 0.63               | V    |

|          |                                    | GTL                       | 0.76         | 0.8                | 0.84               | V    |

|          |                                    | GTL+                      | 0.87         | 1                  | 1.1                | V    |

| VI       | input voltage                      | B port                    | 0            | V <sub>TT</sub>    | 3.6                | V    |

|          |                                    | except B port             | 0            | 3.3                | 5.5 <sup>[3]</sup> | V    |

| VIH      | HIGH-level input<br>voltage        | B port                    | Vref + 0.050 | -                  | -                  | V    |

|          |                                    | except B port<br>VCC=3.3V | 2            | -                  | -                  | V    |

|          |                                    | except B port<br>VCC=2.5V | 1.7          |                    |                    | V    |

| VIL      | LOW-level input voltage            | B port                    | -            | -                  | Vref - 0.050       | V    |

|          |                                    | except B port<br>VCC=3.3V | -            | -                  | 0.8                | V    |

|          |                                    | except B port<br>VCC=2.5V |              |                    | 0.7                | V    |

| IOH      | HIGH-level output<br>current       | A port<br>VCC=3.3V        | -            | -                  | -16                | mA   |

|          |                                    | A port<br>VCC=2.5V        |              |                    | -6                 | mA   |

| IOL      | LOW-level output<br>current        | B port                    | -            | -                  | 40                 | mA   |

|          |                                    | A port<br>VCC=3.3V        | -            | -                  | 16                 | mA   |

|          |                                    | A port<br>VCC=2.5V        | -            | -                  | 12                 | mA   |

| Tamb     | ambient temperature                | operating in free-air     | -40          | -                  | -85                | °C   |

Note:

Unused inputs must be held HIGH or LOW to prevent them from floating.

V<sub>TT</sub> maximum of 3.6 V with resistor sized so IOL maximum is not exceeded.

A0, A1, A2, A3 VI(max) is 3.6 V if configured as outputs (DIR = L).

All trademarks are property of their respective owners. 2016-10-0014

PI4GTL2014

4-bit LVTTL to GTL transceiver

# **Static characteristics**

Recommended operating conditions; voltages are referenced to GND (ground = 0 V).  $T_{amb} = -40$  °C to +85 °C

| Symbol             | Parameter                                | Conditions                                                          | Min.      | Typ. <sup>[1]</sup> | Max. | Unit |

|--------------------|------------------------------------------|---------------------------------------------------------------------|-----------|---------------------|------|------|

| V <sub>OH</sub>    | HIGH-level output voltage                | A port; VCC = 2.3 V to 3.6 V;<br>IOH = $-100 \ \mu A^{[2]}$         | VCC - 0.2 |                     |      | V    |

|                    |                                          | A port; VCC = $3.0$ V; IOH = $-16$ mA <sup>[2]</sup>                | 2.0       |                     |      | V    |

|                    |                                          | A port; VCC = 2.3 V; IOH = $-6$ mA <sup>[2]</sup>                   | 1.7       |                     |      | V    |

| V <sub>OL</sub>    | LOW-level output voltage                 | B port; VCC = $3.0 \text{ V}$ ; $I_{OL} = 40 \text{ mA}^{[2]}$      |           | 0.23                | 0.4  | V    |

|                    |                                          | B port; VCC = 2.3V; $I_{OL} = 40$<br>mA <sup>[2]</sup>              |           | 0.26                | 0.4  | V    |

|                    |                                          | A port; VCC = 3.0 V; $I_{OL}$ =8 mA <sup>[2]</sup>                  |           | 0.28                | 0.4  | V    |

|                    |                                          | A port; VCC = 3.0 V; $I_{OL}$<br>=12mA <sup>[2]</sup>               |           | 0.4                 | 0.55 | V    |

|                    |                                          | A port; VCC = 3.0 V; $I_{OL}$ =16 mA <sup>[2]</sup>                 |           | 0.55                | 0.8  | V    |

|                    |                                          | A port; VCC = 2.3V; $I_{OL}$ =8 mA <sup>[2]</sup>                   |           | 0.3                 | 0.45 | V    |

|                    |                                          | A port; VCC = 2.3V; $I_{OL}$ =12 mA <sup>[2]</sup>                  |           | 0.47                | 0.7  | V    |

| $I_{I}$            | input current                            | control inputs; VCC = $3.6 \text{ V}$ ; V <sub>1</sub> = VCC or GND |           |                     | ±1   | uA   |

|                    |                                          | B port; VCC = $3.6 \text{ V}$ ; $V_I = V_{TT}$ or GND               |           |                     | ±1   | uA   |

|                    |                                          | A port; VCC = 0 V or 3.6 V; $V_I = 5.5 V$                           |           |                     | 10   | uA   |

|                    |                                          | A port; VCC = $3.6 \text{ V}$ ; $V_I = \text{VCC}$                  |           |                     | ±1   | uA   |

|                    |                                          | A port; VCC = $3.6 \text{ V}$ ; $V_I = 0 \text{ V}$                 |           |                     | -5   | uA   |

| I <sub>OZ</sub>    | OFF-state output current                 | A port; VCC =0 V; $V_1$ or $V_0 = 0$ V<br>to 3.6 V                  |           |                     | ±100 | uA   |

| I <sub>CC</sub>    | quiescent supply current                 | A port; VCC = $3.6$ V; V <sub>1</sub> = VCC or<br>GND; IO = $0$ mA  |           | 4                   | 10   | mA   |

|                    |                                          | B port; VCC = 3.6 V; $V_I = V_{TT}$ or<br>GND; IO =0 mA             |           | 4                   | 10   | mA   |

| $\Delta ICC^{[3]}$ | Additional quiescent current (per input) |                                                                     |           |                     | 500  | uA   |

| Ci                 | input capacitance                        | control inputs; $V_I = 3.0 V \text{ or } 0V$                        |           | 2                   |      | pF   |

| Cio                | input/output capacitance                 | A port; $V_0 = 3.0V$ or $0 V$                                       |           | 4.6                 |      | pF   |

|                    |                                          | B port; $V_0 = V_{TT}$ or 0 V                                       |           | 3.4                 |      | pF   |

Note:

[1] All typical values are measured at VCC = 3.3 V and Tamb =  $25 \circ C$ .

[2] The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

[3] This is the increase in supply current for each input that is at the specified TTL voltage level rather than VCC or GND.

**PI4GTL2014**

4-bit LVTTL to GTL transceiver

**Dynamic characteristics** All typical values are at VCC = 3.3 V and Tamb =  $25 \circ C$ .

| Symbol           | Parameter                     | Conditions | Min. | Typ. <sup>[1]</sup> | Max. | Unit |

|------------------|-------------------------------|------------|------|---------------------|------|------|

| GTL - ; Vref =   | 0.5V; VTT = 0.75 V            |            |      |                     |      |      |

| t <sub>PLH</sub> | LOW to HIGH propagation delay | An to Bn   |      | 2.1                 | 5    | ns   |

| t <sub>PHL</sub> | HIGH to LOW propagation delay | An to Bn   |      | 4.1                 | 7    | ns   |

| t <sub>PLH</sub> | LOW to HIGH propagation delay | Bn to An   |      | 6                   | 9    | ns   |

| t <sub>PHL</sub> | HIGH to LOW propagation delay | Bn to An   |      | 4.8                 | 8    | ns   |

| GTL - ; Vref =   | 0.6 V; VTT = 0.9 V            |            |      |                     |      |      |

| t <sub>PLH</sub> | LOW to HIGH propagation delay | An to Bn   |      | 2.0                 | 5    | ns   |

| t <sub>PHL</sub> | HIGH to LOW propagation delay | An to Bn   |      | 4.2                 | 7    | ns   |

| t <sub>PLH</sub> | LOW to HIGH propagation delay | Bn to An   |      | 6                   | 9    | ns   |

| t <sub>PHL</sub> | HIGH to LOW propagation delay | Bn to An   |      | 4.8                 | 8    | ns   |

| GTL -; Vref =    | 0.8 V; VTT = 1.2 V            |            |      |                     |      |      |

| t <sub>PLH</sub> | LOW to HIGH propagation delay | An to Bn   |      | 2.0                 | 5    | ns   |

| t <sub>PHL</sub> | HIGH to LOW propagation delay | An to Bn   |      | 4.9                 | 8    | ns   |

| t <sub>PLH</sub> | LOW to HIGH propagation delay | Bn to An   |      | 6                   | 9    | ns   |

| t <sub>PHL</sub> | HIGH to LOW propagation delay | Bn to An   |      | 4.7                 | 8    | ns   |

| GTL+; Vref = 1   | .0 V; VTT = 1.5 V             |            |      |                     |      |      |

| t <sub>PLH</sub> | LOW to HIGH propagation delay | An to Bn   |      | 2.0                 | 5    | ns   |

| t <sub>PHL</sub> | HIGH to LOW propagation delay | An to Bn   |      | 5.1                 | 8    | ns   |

| t <sub>PLH</sub> | LOW to HIGH propagation delay | Bn to An   |      | 6.1                 | 9    | ns   |

| t <sub>PHL</sub> | HIGH to LOW propagation delay | Bn to An   |      | 4.5                 | 7    | ns   |

**PI4GTL2014**

4-bit LVTTL to GTL transceiver

**Dynamic characteristics** All typical values are at VCC = 2.5 V and Tamb = 25 ° C.

| Symbol           | Parameter                        | Conditions | Min. | Typ. <sup>[1]</sup> | Max. | Unit |  |  |

|------------------|----------------------------------|------------|------|---------------------|------|------|--|--|

| GTL - ; Vref = 0 | GTL -; Vref = 0.5V; VTT = 0.75 V |            |      |                     |      |      |  |  |

| t <sub>PLH</sub> | LOW to HIGH propagation delay    | An to Bn   |      | 2.3                 | 5    | ns   |  |  |

| t <sub>PHL</sub> | HIGH to LOW propagation delay    | An to Bn   |      | 6.5                 | 10   | ns   |  |  |

| t <sub>PLH</sub> | LOW to HIGH propagation delay    | Bn to An   |      | 7.5                 | 12   | ns   |  |  |

| t <sub>PHL</sub> | HIGH to LOW propagation delay    | Bn to An   |      | 5.8                 | 9    | ns   |  |  |

| GTL - ; Vref = 0 | 0.6 V; VTT = 0.9 V               |            |      |                     |      |      |  |  |

| t <sub>PLH</sub> | LOW to HIGH propagation delay    | An to Bn   |      | 2.3                 | 5    | ns   |  |  |

| t <sub>PHL</sub> | HIGH to LOW propagation delay    | An to Bn   |      | 5.7                 | 10   | ns   |  |  |

| t <sub>PLH</sub> | LOW to HIGH propagation delay    | Bn to An   |      | 7.5                 | 12   | ns   |  |  |

| t <sub>PHL</sub> | HIGH to LOW propagation delay    | Bn to An   |      | 5.6                 | 9    | ns   |  |  |

| GTL - ; Vref = 0 | 0.8 V; VTT = 1.2 V               |            |      |                     |      |      |  |  |

| t <sub>PLH</sub> | LOW to HIGH propagation delay    | An to Bn   |      | 2.3                 | 5    | ns   |  |  |

| t <sub>PHL</sub> | HIGH to LOW propagation delay    | An to Bn   |      | 7.5                 | 12   | ns   |  |  |

| t <sub>PLH</sub> | LOW to HIGH propagation delay    | Bn to An   |      | 7.5                 | 12   | ns   |  |  |

| t <sub>PHL</sub> | HIGH to LOW propagation delay    | Bn to An   |      | 5.6                 | 9    | ns   |  |  |

| GTL+; Vref = 1.  | GTL+; Vref = 1.0 V; VTT = 1.5 V  |            |      |                     |      |      |  |  |

| t <sub>PLH</sub> | LOW to HIGH propagation delay    | An to Bn   |      | 2.3                 | 5    | ns   |  |  |

| t <sub>PHL</sub> | HIGH to LOW propagation delay    | An to Bn   |      | 8.6                 | 12   | ns   |  |  |

| t <sub>PLH</sub> | LOW to HIGH propagation delay    | Bn to An   |      | 8.8                 | 12   | ns   |  |  |

| t <sub>PHL</sub> | HIGH to LOW propagation delay    | Bn to An   |      | 5.6                 | 9    | ns   |  |  |

PI4GTL2014

4-bit LVTTL to GTL transceiver

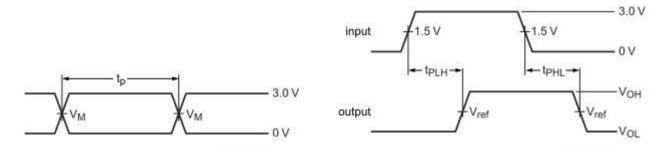

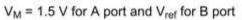

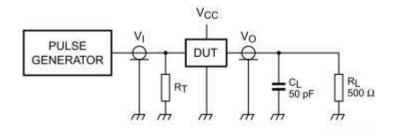

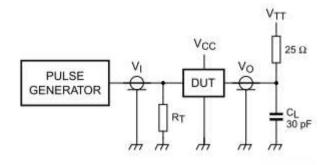

# Waveforms

VM = 1.5 V at VCC  $\ge$  3.0 V; VM = VCC/2 at VCC  $\le$  2.7 V for A ports and control pins; VM = Vref for B ports.

a. Pulse duration

b. Propagation delay times

Fig 2. Voltage waveforms

PRR  $\leq$  10 MHz; Z\_0 = 50  $\Omega;\,t_r \leq$  2.5 ns;  $t_f \leq$  2.5 ns

Fig 3. Propagation delay, Bn to An

# 4-bit LVTTL to GTL transceiver

Fig 4. Load circuitry for switching times

Fig 5. Load circuit for B outputs

RL — Load resistor

CL — Load capacitance; includes jig and probe capacitance

RT — Termination resistance; should be equal to output impedance of pulse generators.

PI4GTL2014

4-bit LVTTL to GTL transceiver

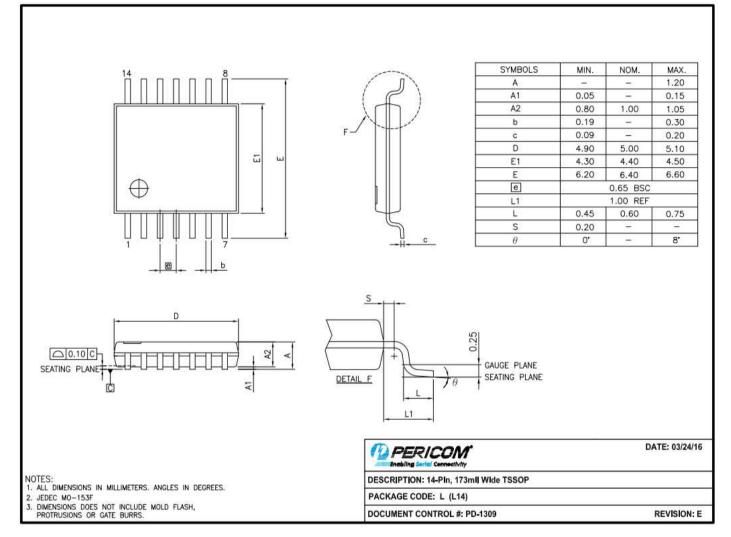

# **Mechanical Information**

TSSOP-14(L)

Note: For latest package info, please check: http://www.pericom.com/support/packaging/packaging-mechanicals-and-thermal-characteristics/

# **Ordering Information**

| Part No.      | Package Code | Package                                  |

|---------------|--------------|------------------------------------------|

| PI4GTL2014LE  | L            | 14-Pin,173 mil Wide (TSSOP)              |

| PI4GTL2014LEX | L            | 14-Pin,173 mil Wide (TSSOP), Tape & Reel |

Note:

• Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

• E = Pb-free and Green

• Adding X Suffix= Tape/Reel