Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## 1.2V-2.5V, 250MHz, 1:10 Networking Clock Buffer

#### **Features**

- High-speed, low-noise, non-inverting split 1-10 buffer

- Maximum Frequency up to 250 MHz

- Low output skew < 60ps (Bank A, 2.5V)

- Low duty cycle distortion < 200ps

- Low propagation delay < 2.0ns (2.5V)

- Choice of 1.2V, 1.5V, 1.8V or 2.5V supply voltage on Bank A, Bank B, Bank C

- Industrial temperature range: -40°C to 85°C

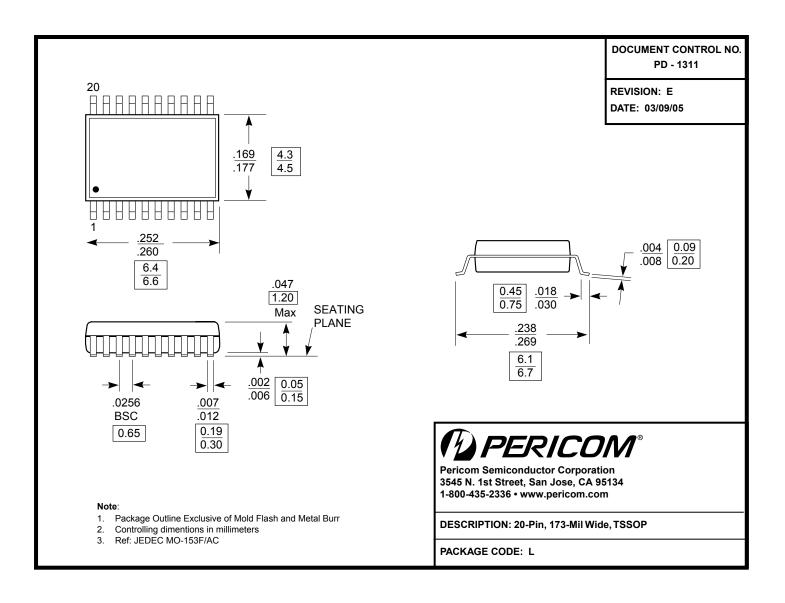

- Packages (Pb-free & Green): 20-pin, TSSOP (L20)

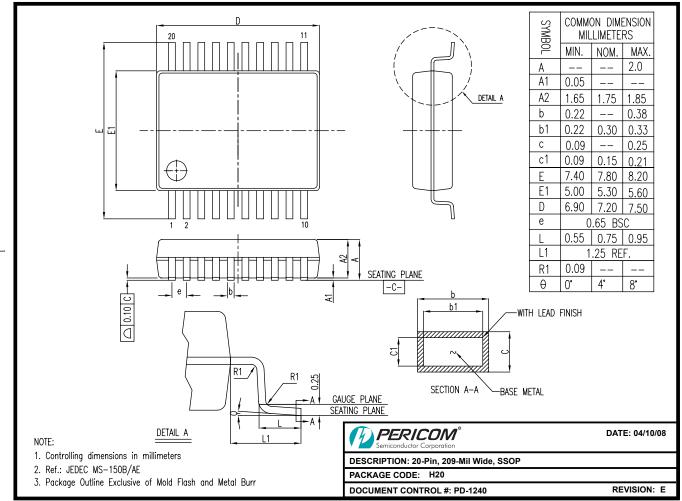

20-pin, SSOP (H20)

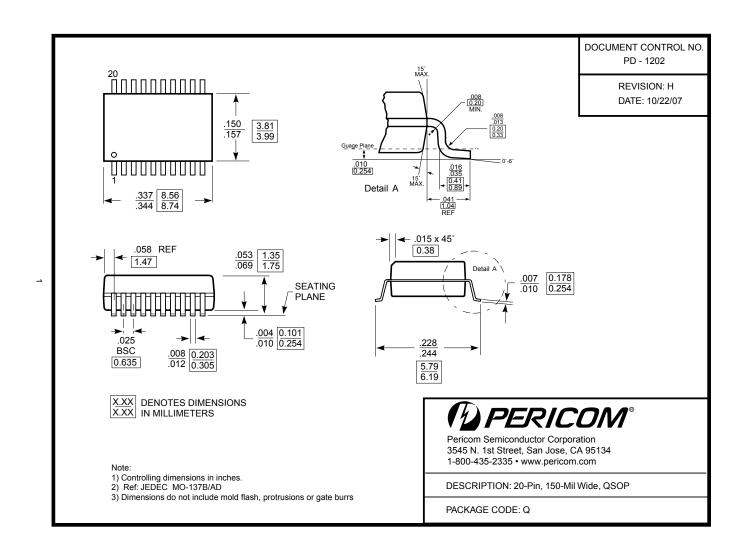

20-pin, QSOP (Q20)

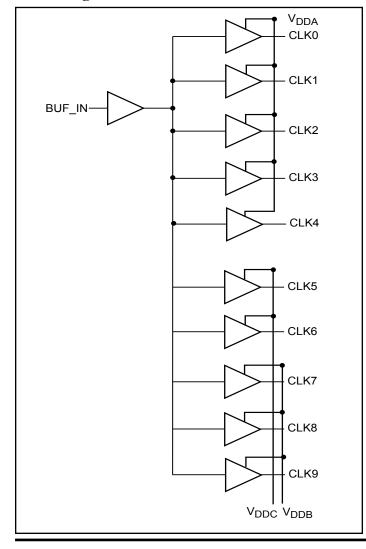

### **Block Diagram**

### **Description**

The PI6C10810 is a 1.2V to 2.5V high-speed, low-noise 1-10 non-inverting clock buffer. The key goal in designing the PI6C10810 is to target networking applications that require low-skew, low-jitter, and high-frequency clock distribution.

Providing output-to-output skew as low as 60ps, the PI6C10810 is an ideal clock distribution device for synchronous systems. Designing synchronous networking systems requires a tight level of skew from a large number of outputs.

CLK0-4 operate from V<sub>DDA</sub> supply.

CLK5-6 operate from V<sub>DDC</sub> supply.

CLK7-9 operate from V<sub>DDB</sub> supply.

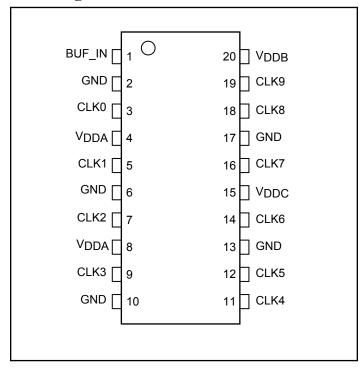

### Pin Configuration

### **Pin Description**

| Pin Name                    | Description                    |

|-----------------------------|--------------------------------|

| BUF_IN                      | Input                          |

| CLK [0:9]                   | Outputs                        |

| GND                         | Ground                         |

| $V_{DDA}, V_{DDB}, V_{DDC}$ | Power (1.2V, 1.5V, 1.8V, 2.5V) |

11-0015 1 PS9014A 02/23/11

### 2.5V Absolute Maximum Ratings (Above which the useful life may

be impaired. For user guidelines only, not tested.)

| Storage Temperature        | 65°C to +150°C                |

|----------------------------|-------------------------------|

| V <sub>DD</sub> Voltage    | 0.5V to +3.6V                 |

| Output Voltage (max. 3.6V) | 0.5V to V <sub>DD</sub> +0.5V |

| Input Voltage (max 3.6V)   | 0.5V to V <sub>DD</sub> +0.5V |

**Note:** Stresses greater than those listed under MAXI-MUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **2.5V DC Characteristics** (Over Operating Range: $V_{DDA}$ , $V_{DDB}$ , $V_{DDC} = 2.5V \pm 0.2V$ , $T_A = -40^{\circ}$ to 85°C)

| Parameters        | Description         | Test Conditions <sup>(1)</sup>                      | )                       | Min. | <b>Typ.</b> (2) | Max. | Units                                           |

|-------------------|---------------------|-----------------------------------------------------|-------------------------|------|-----------------|------|-------------------------------------------------|

| $V_{\mathrm{DD}}$ | Supply Voltage      |                                                     |                         | 2.3  | 2.5             | 2.7  |                                                 |

| $V_{\mathrm{IH}}$ | Input HIGH Voltage  | Logic HIGH level                                    |                         | 1.7  |                 | 3.6  | V                                               |

| $V_{ m IL}$       | Input LOW Voltage   | Logic LOW level                                     |                         | -0.3 |                 | 0.7  | ]                                               |

| $I_{\mathrm{I}}$  | Input Current       | $V_{DD} = Max$ , $Vin = V_{DD}$ or GND              | I pin                   |      |                 | 15   | μА                                              |

|                   | Output High Voltage | $V_{DD} = Min., V_{IN} = V_{IH} \text{ or } V_{IL}$ | $I_{OH} = -1 \text{mA}$ | 2.0  |                 |      |                                                 |

| $V_{OH}$          |                     |                                                     | $I_{OH} = -2mA$         | 1.7  |                 |      |                                                 |

|                   |                     |                                                     | $I_{OH} = -8mA$         | 1.7  |                 |      | $\left  \begin{array}{c} v \end{array} \right $ |

|                   | Output LOW Voltage  |                                                     | $I_{OL} = 1mA$          |      |                 | 0.1  | ]                                               |

| $V_{ m OL}$       |                     | $V_{DD} = Min., V_{IN} - V_{IH} \text{ or } V_{IL}$ | $I_{OL} = 2mA$          |      |                 | 0.2  |                                                 |

| N                 |                     |                                                     | $I_{OL} = 8mA$          |      |                 | 0.2  |                                                 |

#### Notes:

- 1. For Max. or Min. conditions, use appropriate operating range values.

- 2. Typical values are at  $V_{DD} = 2.5V$ , +25°C ambient and maximum loading.

### **2.5V AC Characteristics** (Over Operating Range: $V_{DDA}$ , $V_{DDB}$ , $V_{DDC} = 2.5V \pm 0.2V$ , $T_A = -40^{\circ}$ to 85°C)

| Parameters                           | Description                                                                                         | Description          |                                           |      | Тур | Max. | Units |

|--------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------|------|-----|------|-------|

| F <sub>IN</sub>                      | Input Frequency                                                                                     |                      |                                           | 0    |     | 250  | MHz   |

| $t_{PLH}$ , $t_{PHL}$ <sup>(2)</sup> | Propagation Delay BUF_IN                                                                            | N to CLKn            |                                           | 1.0  | 1.5 | 2.0  |       |

|                                      | Output to Output Skew                                                                               | Bank A (CLK0 - CLK4) |                                           | -60  |     | 60   |       |

| $t_{SK(O)}^{(3)}$                    | between any two outputs of the same device @                                                        | Bank C (CLK5 - CLK6) |                                           | -30  |     | 30   |       |

|                                      | same transition                                                                                     | Bank B (CLK7 - CLK9) | $R_{L} = 500$ -Ohm, $C_{L} =$             | -150 |     | 150  |       |

| $t_{SK(P)}^{(3)}$                    | Pulse Skew between opposite transitions (t <sub>PHL</sub> -t <sub>PLH</sub> ) of the same output    |                      | 3pF, 125 MHz Outputs are measured @ VDD/2 |      | 100 | 200  | ps    |

| $t_{SK(T)}^{(3)(5)}$                 | Part to Part Skew between two identical outputs of different parts on the same board <sup>(4)</sup> |                      | V DD/ Z                                   |      |     | 300  |       |

| t <sub>dc_in</sub>                   | Duty Cycle In @ Ins edge                                                                            | rate                 |                                           | 45   |     | 55   | %     |

| t <sub>dc_out</sub>                  | Duty Cycle Out                                                                                      |                      |                                           | 40   |     | 57.5 | 70    |

| t <sub>j</sub> (5)                   | Additive Jitter                                                                                     |                      |                                           |      |     | 50   | ps    |

| t <sub>R(O)</sub>                    | Output Rise Time 20%-80% CLKn                                                                       |                      | $R_{L} = 500$ -Ohm, $C_{L} =$             |      | 0.5 | 0.7  | ns    |

| $t_{F(O)}$                           | Output Fall Time 80%-20%                                                                            | 6 CLKn               | 3pF                                       |      | 0.5 | 0.7  | 115   |

Notes:

5. Guaranteed by design

<sup>1.</sup> See test circuit and waveforms.

<sup>2.</sup> Minimum limits are guaranteed but not tested on Propagation Delays.

<sup>3.</sup> Skew measured at worst case temperature (max. temp).

<sup>4.</sup> Identical conditions: loading, transitions, supply voltage, temperature, package type and speed grade.

# **1.8V Absolute Maximum Ratings** (Above which the useful life may be impaired. For user guidelines only, not tested.)

**Note:** Stresses greater than those listed under MAXI-MUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **1.8V DC Characteristics** (Over Operating Range: $V_{DDA}$ , $V_{DDB}$ , $V_{DDC} = 1.8V \pm 0.15V$ , $T_A = -40^{\circ}$ to 85°C)

| Parameters        | Description                  | Test Conditions <sup>(1)</sup>                                 |                 | Min. | <b>Typ.</b> (2) | Max.                 | Units |

|-------------------|------------------------------|----------------------------------------------------------------|-----------------|------|-----------------|----------------------|-------|

| $V_{\mathrm{DD}}$ | Supply Voltage               |                                                                |                 | 1.65 | 1.8             | 1.95                 |       |

| $V_{ m IH}$       | Input HIGH Voltage           | Logic HIGH level                                               |                 | 1.1  |                 | 2.7                  | V     |

| $V_{ m IL}$       | Input LOW Voltage            | Logic LOW level                                                | Logic LOW level |      |                 | 0.35*V <sub>DD</sub> | V     |

| $I_{\mathrm{I}}$  | Input Current <sup>(3)</sup> | $V_{DD} = Max,$<br>$Vin = V_{DD}$ or GND                       | I pin           |      |                 | 15                   | μА    |

| Vor               | Output High Voltage          | gh Voltage $V_{DD} = Min., V_{IN} = V_{IH} \text{ or } V_{IL}$ | $I_{OH} = -2mA$ | 1.35 |                 |                      |       |

| $V_{ m OH}$       |                              |                                                                | $I_{OH} = -8mA$ | 1.2  |                 |                      | V     |

| Vor               | Output LOW Voltage           | to di OW Valence V — Min V — V — NV                            | $I_{OL} = 2mA$  |      |                 | 0.1                  | v     |

| $V_{ m OL}$       |                              | $V_{DD} = Min., V_{IN} - V_{IH} \text{ or } V_{IL}$            | $I_{OL} = 8mA$  |      |                 | 0.2                  |       |

#### **Notes:**

- 1. For Max. or Min. conditions, use appropriate operating V<sub>DD</sub> and Ta values.

- 2. Typical values are at  $V_{DD} = 1.8V$ ,  $+25^{\circ}C$  ambient and maximum loading.

- 3. This parameter is determined by device characterization but is not production tested.

### **1.8V AC Characteristics** (Over Operating Range: $V_{DDA}$ , $V_{DDB}$ , $V_{DDC} = 1.8V \pm 0.15V$ , $T_A = -40^{\circ}$ to $85^{\circ}$ C)

| Parameters                                         | Description                                                                                      |                                                                                                     | Test Conditions <sup>(1)</sup>             | Min. | Тур | Max. | Units |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------|------|-----|------|-------|

| F <sub>IN</sub>                                    | Input Frequency                                                                                  |                                                                                                     |                                            | 0    |     | 200  | MHz   |

| t <sub>PLH</sub> , t <sub>PHL</sub> <sup>(2)</sup> | Propagation Delay BU                                                                             | JF_IN to CLKn                                                                                       |                                            | 1.0  | 2.3 | 2.8  |       |

|                                                    | Output to Output                                                                                 | Bank A (CLK0 - CLK4)                                                                                |                                            | -60  |     | 60   |       |

| $t_{SK(O)}^{(3)}$                                  | Skew between any two outputs of the                                                              | Bank C (CLK5 - CLK6)                                                                                |                                            | 30   |     | 30   | ]     |

|                                                    | same device @ same transition                                                                    | Bank B (CLK7 - CLK9)                                                                                | $C_L = 3pF, R_L = 500-Ohm, 125 MHz$        | -200 |     | 200  | ps    |

| $t_{SK(P)}^{(3)}$                                  | Pulse Skew between opposite transitions (t <sub>PHL</sub> -t <sub>PLH</sub> ) of the same output |                                                                                                     | Outputs are measured  @ V <sub>DD</sub> /2 |      | 100 | 200  |       |

| t <sub>SK(T)</sub> (3)(5)                          |                                                                                                  | Part to Part Skew between two identical outputs of different parts on the same board <sup>(4)</sup> |                                            |      |     | 300  |       |

| t <sub>dc_in</sub>                                 | Duty Cycle In @ 1 ns                                                                             | edge rate                                                                                           | ]                                          | 45   |     | 55   | %     |

| t <sub>dc_out</sub>                                | Duty Cycle Out                                                                                   |                                                                                                     |                                            | 40   |     | 57.5 | 70    |

| t <sub>j</sub> (5)                                 | Additive Jitter                                                                                  |                                                                                                     |                                            |      |     | 50   | ps    |

| t <sub>R(o)</sub>                                  | Output Rise Time 20%                                                                             | % - 80% CLKn                                                                                        |                                            |      | 0.5 | 0.8  |       |

| t <sub>F(o)</sub>                                  | Output Fall Time 80%                                                                             | 5 - 20% CLKn                                                                                        |                                            |      | 0.5 | 0.8  | ns    |

#### Notes:

- See test circuit and waveforms.

- 2. Minimum limits are guaranteed but not tested on Propagation Delays.

- 3. Skew measured at worst case temperature (max. temp).

- 4. Identical conditions: loading, transitions, supply voltage, temperature, package type and speed grade.

- 5. Guaranteed by design.

11-0015 3 PS9014A 02/23/11

### 1.5V Absolute Maximum Ratings (Above which the useful life may

be impaired. For user guidelines only, not tested.)

| Storage Temperature        | 65°C to +150°C                |

|----------------------------|-------------------------------|

| V <sub>DD</sub> Voltage    |                               |

| Output Voltage (max. 3.6V) | 0.5V to V <sub>DD</sub> +0.5V |

| Input Voltage (max 3.6V)   | 0.5V to V <sub>DD</sub> +0.5V |

**Note:** Stresses greater than those listed under MAXI-MUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **1.5V DC Characteristics** (Over Operating Range: $V_{DDA}$ , $V_{DDB}$ , $V_{DDC} = 1.5V \pm 0.1V$ , $T_A = -40^{\circ}$ to 85°C)

| Parameters        | Description         | Test Conditions <sup>(1)</sup>                                         | Test Conditions <sup>(1)</sup> |      | <b>Typ.</b> (2) | Max.                 | Units         |

|-------------------|---------------------|------------------------------------------------------------------------|--------------------------------|------|-----------------|----------------------|---------------|

| $V_{\mathrm{DD}}$ | Supply Voltage      |                                                                        |                                | 1.4  | 1.5             | 1.6                  |               |

| $V_{\mathrm{IH}}$ | Input HIGH Voltage  | Logic HIGH level                                                       | Logic HIGH level               |      |                 | $V_{\mathrm{DD}}$    | V             |

| $V_{ m IL}$       | Input LOW Voltage   | Logic LOW level                                                        | Logic LOW level                |      |                 | $0.35 \times V_{DD}$ | V             |

| $I_{\mathrm{I}}$  | Input Current       | $V_{DD} = Max$ , $Vin = V_{DD}$ or $GND$                               | I pin                          |      |                 | 15                   | μA            |

| N/                | Output High Voltage | $V_{DD} = Min., V_{IN} = V_{IH} \text{ or } V_{IL}$                    | $I_{OH} = -2mA$                | 1.05 |                 |                      |               |

| $V_{\mathrm{OH}}$ |                     |                                                                        | $I_{OH} = -8mA$                | 1.75 |                 |                      | $\mid v \mid$ |

| 17                | Output LOW Voltage  | Output LOW Voltage $V_{DD} = Min., V_{IN} - V_{IH} \text{ or } V_{IL}$ | $I_{OL} = 2mA$                 |      |                 | 0.35                 |               |

| $V_{ m OL}$       |                     |                                                                        | $I_{OL} = 8mA$                 |      |                 | 0.65                 |               |

#### Notes:

- 1. For Max. or Min. conditions, use appropriate operating range values.

- 2. Typical values are at  $V_{DD} = 1.5V$ ,  $+25^{\circ}C$  ambient and maximum loading.

### **1.5V AC Characteristics** (Over Operating Range: $V_{DDA}$ , $V_{DDB}$ , $V_{DDC} = 1.5V \pm 0.1V$ , $T_A = -40^{\circ}$ to $85^{\circ}$ C)

| Parameters                              | Description                                                                                      |                                               | Test Conditions <sup>(1)</sup>            | Min. | Тур | Max. | Units |

|-----------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------|------|-----|------|-------|

| F <sub>IN</sub>                         | Input Frequency                                                                                  |                                               |                                           | 0    |     | 200  | MHz   |

| $t_{\rm R}/t_{\rm F}$                   | CLKn Rise/Fall Time                                                                              |                                               | 20% to 80%                                |      |     | 1.0  | ns    |

| t <sub>PLH</sub> , t <sub>PHL</sub> (2) | Propagation Delay BUF_1                                                                          | N to CLKn                                     |                                           | 2.0  | 2.8 | 3.5  | ns    |

|                                         | Output to Output Skew                                                                            | Bank A (CLK0 - CLK4)                          |                                           | -100 |     | 100  |       |

| $t_{SK(O)}^{(3)}$                       | between any two outputs of the same device @                                                     | Bank C (CLK5 - CLK6)                          |                                           | -50  |     | 50   |       |

|                                         | same transition                                                                                  | Bank B (CLK7 - CLK9)                          | $C_L = 3pF$ ,                             | -200 |     | 200  |       |

| $t_{SK(P)}^{(3)}$                       | Pulse Skew between opposite transitions (t <sub>PHL</sub> -t <sub>PLH</sub> ) of the same output |                                               | $R_L = 500$ -Ohms, 125<br>MHz Outputs are |      | 100 | 200  | ps    |

| $t_{SK(T)}^{(3)(5)}$                    | Part to Part Skew between different parts on the same                                            | two identical outputs of board <sup>(4)</sup> | measured @ V <sub>DD</sub> /2             |      |     | 300  |       |

| t <sub>dc_in</sub>                      | Duty Cycle In @ Ins edge                                                                         | rate                                          |                                           | 45   |     | 55   | %     |

| t <sub>dc_out</sub> (5)                 | Duty Cycle Out                                                                                   |                                               |                                           | 40   |     | 60   | 70    |

| tj                                      | Additive Jitter                                                                                  |                                               |                                           |      |     | 50   | ps    |

| t <sub>R(o)</sub>                       | Output Rise Time 20% - 8                                                                         | 80% CLKn                                      |                                           |      | 0.6 | 0.9  |       |

| $t_{F(o)}$                              | Output Fall Time 80% - 2                                                                         | 0% CLKn                                       |                                           |      | 0.6 | 0.9  | ns    |

#### Notes:

- See test circuit and waveforms.

- 2. Minimum limits are guaranteed but not tested on Propagation Delays.

- 3. Skew measured at worst case temperature (max. temp).

- 4. Identical conditions: loading, transitions, supply voltage, temperature, package type and speed grade.

- 5. Guaranteed by design.

### 1.2V Absolute Maximum Ratings (Above which the useful life may

be impaired. For user guidelines only, not tested.)

| Storage Temperature        | 65°C to +150°C                |

|----------------------------|-------------------------------|

| V <sub>DD</sub> Voltage    | 0.5V to +3.6V                 |

| Output Voltage (max. 3.6V) | 0.5V to V <sub>DD</sub> +0.5V |

| Input Voltage (max 3.6V)   | 0.5V to V <sub>DD</sub> +0.5V |

**Note:** Stresses greater than those listed under MAXI-MUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **1.2V DC Characteristics** (Over Operating Range: $V_{DDA}$ , $V_{DDB}$ , $V_{DDC}$ = 1.2V ± 0.1V, $T_A$ = -40° to 85°C)

| Parameters        | Description         | Test Conditions <sup>(</sup>                          | 1)              | Min.                 | Тур. (2) | Max.                 | Units         |

|-------------------|---------------------|-------------------------------------------------------|-----------------|----------------------|----------|----------------------|---------------|

| $V_{\mathrm{DD}}$ | Supply Voltage      |                                                       |                 | 1.1                  | 1.2      | 1.3                  |               |

| $V_{ m IH}$       | Input HIGH Voltage  | Logic HIGH leve                                       | 1               | $0.65 \times V_{DD}$ |          | V <sub>DD</sub> +0.3 | V             |

| $V_{ m IL}$       | Input LOW Voltage   | Logic LOW level                                       | Logic LOW level |                      |          | $0.35 \times V_{DD}$ | V             |

| II                | Input Current       | $V_{DD} = Max$ , $Vin = V_{DD}$ or $GND$              | I pin           |                      |          | 15                   | μА            |

| V                 | Output High Voltage | V                                                     | $I_{OH} = -2mA$ | 1.05                 |          |                      |               |

| $V_{\mathrm{OH}}$ | Output High Voltage | $V_{DD} = Min., V_{IN} = V_{IH} \text{ or } V_{IL}$   | $I_{OH} = -8mA$ | 1.75                 |          |                      | $\mid V \mid$ |

| Vor               | Output LOW Voltage  | e $V_{DD} = Min., V_{IN} - V_{IH} \text{ or } V_{IL}$ | $I_{OL} = 2mA$  |                      |          | 0.35                 |               |

| $V_{ m OL}$       |                     |                                                       | $I_{OL} = 8mA$  |                      |          | 0.65                 |               |

#### Notes:

- 1. For Max. or Min. conditions, use appropriate operating range values.

- 2. Typical values are at  $V_{DD} = 1.2V$ ,  $+25^{\circ}C$  ambient and maximum loading.

### **1.2V AC Characteristics** (Over Operating Range: $V_{DDA}$ , $V_{DDB}$ , $V_{DDC} = 1.2V \pm 0.1V$ , $T_A = -40^{\circ}$ to 85°C)

| Parameters               | Description                                                                                      |                                                     | Test Conditions <sup>(1)</sup>                                 | Min. | Тур | Max. | Units |

|--------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------|------|-----|------|-------|

| F <sub>IN</sub>          | Input Frequency                                                                                  |                                                     |                                                                | 0    |     | 150  | MHz   |

| $t_{PLH,} t_{PHL}^{(2)}$ | Propagation Delay BUI                                                                            | F_IN to CLKn                                        |                                                                | 4    | 5   | 6    | ns    |

|                          | Output to Output                                                                                 | Bank A (CLK0 - CLK4)                                |                                                                | -150 |     | 150  |       |

| $t_{SK(O)}^{(3)}$        | Skew between any two outputs of the                                                              | Bank C (CLK5 - CLK6)                                | G 1.F.P.                                                       | -50  |     | 50   |       |

| tSK(O)\                  | same device @ same transition                                                                    | Bank B (CLK7 - CLK9)                                | $C_L = 3pF, R_L =$<br>500-Ohm, 125 MHz<br>Outputs are measured | -300 |     | 300  | ps    |

| $t_{SK(P)}^{(3)}$        | Pulse Skew between opposite transitions (t <sub>PHL</sub> -t <sub>PLH</sub> ) of the same output |                                                     | $@V_{\mathrm{DD}}/2$                                           |      | 200 | 300  |       |

| $t_{SK(T)}^{(3)(5)}$     | Part to Part Skew betwee of different parts on the                                               | een two identical outputs same board <sup>(4)</sup> |                                                                |      |     | 300  |       |

| t <sub>DC_IN</sub>       | Duty Cycle In @ 1ns ed                                                                           | dge rate                                            |                                                                | 45   |     | 55   | %     |

| t <sub>DC_OUT</sub>      | Duty Cycle Out                                                                                   |                                                     |                                                                | 40   |     | 60   | 70    |

| $t_j^{(5)}$              | Additive Jitter                                                                                  |                                                     |                                                                |      |     | 50   | ps    |

| $t_{R(o)}$               | Output Rise Time 20%                                                                             | - 80% CLKn                                          |                                                                |      | 0.9 | 1    | ne    |

| $t_{F(o)}$               | Output Fall Time 80%                                                                             | - 20% CLKn                                          |                                                                |      | 0.9 | 1    | ns    |

#### Notes:

- 1. See test circuit and waveforms.

- 2. Minimum limits are guaranteed but not tested on Propagation Delays.

- 3. Skew measured at worst case temperature (max. temp).

- 4. Identical conditions: loading, transitions, supply voltage, temperature, package type and speed grade.

- 5. Guaranteed by design.

### **Power Supply Characteristics**

| Parameters       | Description                       | Test Conditions <sup>(1)</sup>                         |                                                                          |  | Typ. (2)                 | Max. | Units |

|------------------|-----------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------|--|--------------------------|------|-------|

| I <sub>DDQ</sub> | Quiescent Power<br>Supply Current | $V_{DDA} = V_{DDB} = V_{DDC} = 2.7V$                   | No Load. F <sub>IN</sub> = 40MHz<br>(Bank A, Bank B, Bank C<br>included) |  | 16                       |      |       |

|                  |                                   | $V_{DDA} = V_{DDB} = V_{DDC} = 1.95V$                  |                                                                          |  | 12                       |      | 4     |

|                  |                                   | $V_{DDA} = V_{DDB} = V_{DDC} = 1.6V$                   |                                                                          |  | 8                        |      | mA    |

|                  |                                   | $V_{DDA} = V_{DDB} = V_{DDC} = 1.2V$                   |                                                                          |  | 8                        |      |       |

| I <sub>OS</sub>  | Short Circuit Current             | V <sub>DDA</sub> = V <sub>DDB</sub> = V <sub>DDC</sub> | 2.7V<br>1.95V<br>1.6V<br>1.2V                                            |  | ±80<br>±50<br>±35<br>±15 |      | mA    |

#### **Notes:**

- 1. For Max. or Min. conditions, use appropriate value specified under Electrical Characteristics.

- 2. Typical values are at  $V_{DD} = 1.2V$ , 1.5V, 1.8V or 2.5V, and +25°C ambient.

- 3. Per TTL driven input ( $V_{IN} = V_{DD} 0.6V$ ); all other inputs at  $V_{DD}$  or GND.

### Capacitance ( $T_A = 25$ °C, f = 1 MHz)

| Parameters <sup>(1)</sup> | Description        | Test Conditions | Тур | Max. | Units |

|---------------------------|--------------------|-----------------|-----|------|-------|

| $C_{IN}$                  | Input Capacitance  | $V_{IN} = 0V$   | 3.0 | 4    | nE    |

| $C_{OUT}$                 | Output Capacitance | $V_{OUT} = 0V$  | _   | 6    | рF    |

#### Note:

1. This parameter is determined by device characterization but is not production tested.

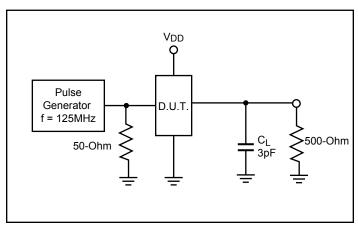

### **Test Circuits for All Outputs**

#### **Definitions:**

$C_L$  = Load capacitance: includes jig and probe capacitance.

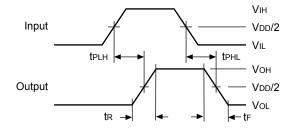

### **Switching Waveforms**

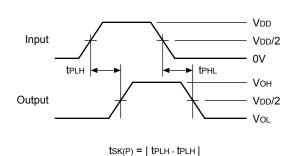

### **Propagation Delay**

### Pulse Skew $-t_{SK(P)}$

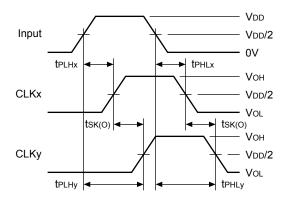

Output Skew –  $t_{SK(O)}$

tsk(O) = | tplhy - tplhx | or | tphly - tphlx |

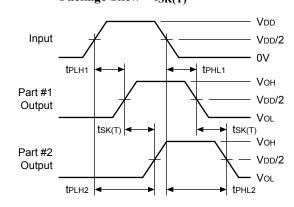

### Package Skew - t<sub>SK(T)</sub>

tsk(T) = |tPLH2 - tPLH1| or |tPHL2 - tPHL1|

08-01**4**0

11-0015 9 PS9014A 02/23/11

# Ordering Information<sup>(1-3)</sup>

| Ordering Code | Package Code | Package Type                               |

|---------------|--------------|--------------------------------------------|

| PI6C10810LE   | L            | Pb-free & Green, 20-pin 173-mil wide TSSOP |

| PI6C10810HE   | Н            | Pb-free & Green, 20-pin 209-mil wide SSOP  |

| PI6C10810QE   | Q            | Pb-free & Green, 20-pin 150-mil wide QSOP  |

#### Notes

- 1. Thermal Characteristics can be found on the web at www.pericom.com/packaging/

- 2. E = Lead-free and Green

- 3. Adding an X suffix = Tape/Reel

Pericom Semiconductor Corporation • 1-800-435-2336 • www.pericom.com