Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 1:4 Clock Driver for Intel PCIe® Chipsets

#### **Features**

- Phase jitter filter for PCIe® 2.0 application

- · Four Pairs of Differential Clocks

- Low skew < 50ps

- Low jitter < 50ps cycle-to-cycle

- < 1 ps additive RMS phase jitter

- Output Enable for all outputs

- · Outputs tristate control via SMBus

- · Programmable PLL Bandwidth

- 100 MHz PLL Mode operation

- 100 400 MHz Bypass Mode operation

- 3.3V Operation

- Packaging (Pb-free and Green):

- $\rightarrow$ 28-Pin SSOP (H28)

- $\rightarrow$ 28-Pin TSSOP (L28)

#### **Description**

Pericom Semiconductor's PI6C20400A is a PCIe® 2.0 compliant high-speed, low-noise differential clock buffer designed to be companion to PI6C410BS. The device distributes the differential SRC clock from PI6C410BS to four differential pairs of clock outputs either with or without PLL. The clock outputs are controlled by input selection of SRC\_STOP#, PWRDWN# and SMBus, SCLK and SDA. When input of either SRC\_STOP# or PWRDWN# is low, the output clocks are Tristated. When PWRDWN# is low, the SDA and SCLK inputs must be Tri-stated.

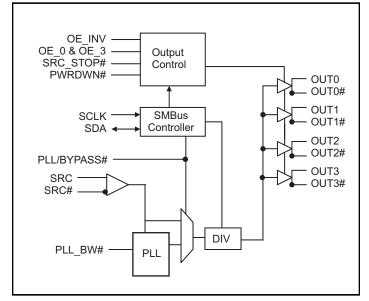

### **Block Diagram**

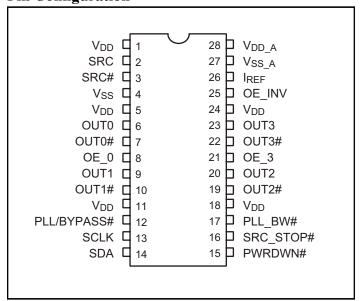

#### **Pin Configuration**

14-0195 1 www.pericom.com 03/27/13

## **Pin Descriptions**

| Pin Name             | Type   | Pin No                         | Description                                                                                                                              |

|----------------------|--------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| SRC & SRC#           | Input  | 2, 3                           | 0.7V Differential SRC input from PI6C410 clock synthesizer                                                                               |

| OE_0 & OE_3          | Input  | 8, 21                          | 3.3V LVTTL input for enabling outputs, active high. OE_0 for OUT0 / OUT0# OE_3 for OUT3 / OUT3#                                          |

| OE_INV               | Input  | 25                             | 3.3V LVTTL input for inverting the OE, SRC_STOP# and PWRDWN# pins. When 0 = same stage When 1 = OE_0, OE_3, SRC_STOP#, PWRDWN# inverted. |

| OUT[0:3] & OUT[0:3]# | Output | 6, 7, 9, 10, 19, 20,<br>22, 23 | 0.7V Differential outputs                                                                                                                |

| PLL/BYPASS#          | Input  | 12                             | 3.3V LVTTL input for selecting fan-out of PLL operation.                                                                                 |

| SCLK                 | Input  | 13                             | SMBus compatible SCLOCK input                                                                                                            |

| SDA                  | I/O    | 14                             | SMBus compatible SDATA                                                                                                                   |

| IREF                 | Input  | 26                             | External resistor connection to set the differential output current                                                                      |

| SRC_STOP#            | Input  | 16                             | 3.3V LVTTL input for SRC stop, active low                                                                                                |

| PLL_BW#              | Input  | 17                             | 3.3V LVTTL input for selecting the PLL bandwidth                                                                                         |

| PWRDWN#              | Input  | 15                             | 3.3V LVTTL input for Power Down operation, active low                                                                                    |

| $V_{DD}$             | Power  | 1, 5, 11, 18, 24               | 3.3V Power Supply for Outputs                                                                                                            |

| VSS                  | Ground | 4                              | Ground for Outputs                                                                                                                       |

| VSS_A                | Ground | 27                             | Ground for PLL                                                                                                                           |

| VDD_A                | Power  | 28                             | 3.3V Power Supply for PLL                                                                                                                |

### **Serial Data Interface (SMBus)**

This part is a slave only SMBus device that supports indexed block read and indexed block write protocol using a single 7-bit address and read/write bit as shown below.

### **Address Assignment**

| A6 | A5 | A4 | A3 | A2 | A1 | <b>A0</b> | W/R |

|----|----|----|----|----|----|-----------|-----|

| 1  | 1  | 0  | 1  | 1  | 1  | 0         | 0/1 |

#### **Data Protocol**

| 1 bit        | 7 bits        | 1   | 1   | 8 bits             | 1   | 8 bits               | 1   | 8 bits         | 1   | 8 bits                    | 1   | 1 bit       |

|--------------|---------------|-----|-----|--------------------|-----|----------------------|-----|----------------|-----|---------------------------|-----|-------------|

| Start<br>bit | Slave<br>Addr | R/W | Ack | Register<br>offset | Ack | Byte<br>Count<br>= N | Ack | Data<br>Byte 0 | Ack | <br>Data<br>Byte N<br>- 1 | Ack | Stop<br>bit |

#### **Notes:**

1. Register offset for indicating the starting register for indexed block write and indexed block read. Byte Count in write mode cannot be 0.

## **Data Byte 0: Control Register**

| Bit | Descriptions                                         | Туре | Power Up Condition      | Output(s) Affected  | Source<br>Pin |

|-----|------------------------------------------------------|------|-------------------------|---------------------|---------------|

| 0   | Outputs Mode<br>0 = Divide by 2<br>1 = Normal        | RW   | 1 = Normal              | OUT[0:3], OUT[0:3]# | NA            |

| 1   | PLL/BYPASS#<br>0 = Fanout<br>1 = PLL                 | RW   | 1 = PLL                 | OUT[0:3], OUT[0:3]# | NA            |

| 2   | PLL Bandwidth 0 = High Bandwidth, 1 = Low Bandwidth  | RW   | 1 = Low                 | OUT[0:3], OUT[0:3]# | NA            |

| 3   | Reserved                                             |      |                         |                     | NA            |

| 4   | Reserved                                             |      |                         |                     | NA            |

| 5   | Reserved                                             |      |                         |                     | NA            |

| 6   | SRC_STOP#<br>0 = Driven when stopped<br>1 = Tristate | RW   | 0 = Driven when stopped | OUT[0:3], OUT[0:3]# | NA            |

| 7   | PWRDWN# 0 = Driven when stopped 1 = Tristate         | RW   | 0 = Driven when stopped | OUT[0:3], OUT[0:3]# | NA            |

## **Data Byte 1: Control Register**

| Bit | Descriptions                | Туре | Power Up Condition | Output(s) Affected | Source<br>Pin |

|-----|-----------------------------|------|--------------------|--------------------|---------------|

| 0   | Reserved                    |      |                    |                    | NA            |

| 1   | OUTPUTS enable              | RW   | 1 = Enabled        | OUT0, OUT0#        | NA            |

| 2   | 1 = Enabled<br>0 = Disabled | RW   | 1 = Enabled        | OUT1, OUT1#        | NA            |

| 3   | Reserved                    |      |                    |                    | NA            |

| 4   | Reserved                    |      |                    |                    | NA            |

| 5   | OUTPUTS enable              | RW   | 1 = Enabled        | OUT2, OUT2#        | NA            |

| 6   | 1 = Enabled<br>0 = Disabled | RW   | 1 = Enabled        | OUT3, OUT3#        | NA            |

| 7   | Reserved                    |      |                    |                    | NA            |

**Data Byte 2: Control Register**

| Bit | Descriptions                                                                         | Туре | Power Up Condition | Output(s) Affected | Source<br>Pin |

|-----|--------------------------------------------------------------------------------------|------|--------------------|--------------------|---------------|

| 0   | Reserved                                                                             |      |                    |                    | NA            |

| 1   | Allow control of OUTPUTS with                                                        | RW   | 0 = Free running   | OUT0, OUT0#        | NA            |

| 2   | assertion of SRC_STOP# $0 = \text{Free running}$ $1 = \text{Stopped with SRC_Stop#}$ | RW   | 0 = Free running   | OUT1, OUT1#        | NA            |

| 3   | Reserved                                                                             |      |                    |                    | NA            |

| 4   | Reserved                                                                             |      |                    |                    | NA            |

| 5   | Allow control of OUTPUTS with                                                        | RW   | 0 = Free running   | OUT2, OUT2#        | NA            |

| 6   | assertion of SRC_STOP# $0 = \text{Free running}$ $1 = \text{Stopped with SRC_Stop#}$ | RW   | 0 = Free running   | OUT3, OUT3#        | NA            |

| 7   | Reserved                                                                             |      |                    |                    | NA            |

**Data Byte 3: Control Register**

| Bit | Descriptions | Туре | Power Up Condition | Output(s) Affected | Source<br>Pin |

|-----|--------------|------|--------------------|--------------------|---------------|

| 0   |              | RW   |                    |                    |               |

| 1   |              | RW   |                    |                    |               |

| 2   |              | RW   |                    |                    |               |

| 3   | Danamad      | RW   |                    |                    |               |

| 4   | Reserved     | RW   |                    |                    |               |

| 5   |              | RW   |                    |                    |               |

| 6   |              | RW   |                    |                    |               |

| 7   |              | RW   |                    |                    |               |

## **Data Byte 4: Pericom ID Register**

| Bit | Descriptions | Туре | Power Up Condition | Output(s) Affected | Pin |

|-----|--------------|------|--------------------|--------------------|-----|

| 0   |              | R    | 0                  | NA                 | NA  |

| 1   |              | R    | 0                  | NA                 | NA  |

| 2   |              | R    | 0                  | NA                 | NA  |

| 3   | Davissan ID  | R    | 0                  | NA                 | NA  |

| 4   | Pericom ID   | R    | 0                  | NA                 | NA  |

| 5   |              | R    | 1                  | NA                 | NA  |

| 6   |              | R    | 0                  | NA                 | NA  |

| 7   |              | R    | 0                  | NA                 | NA  |

## **Functionality**

| PWRDWN# | OUT                         | OUT#   | SRC_Stop# | OUT                         | OUT#   |

|---------|-----------------------------|--------|-----------|-----------------------------|--------|

| 1       | Normal                      | Normal | 1         | Normal                      | Normal |

| 0       | $I_{REF} \times 2$ or Float | Low    | 0         | $I_{REF} \times 6$ or Float | Low    |

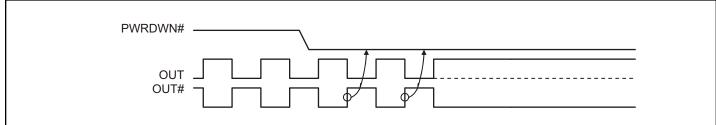

Figure 1. Power down sequence

## Power Down (PWRDWN# De-assertion)

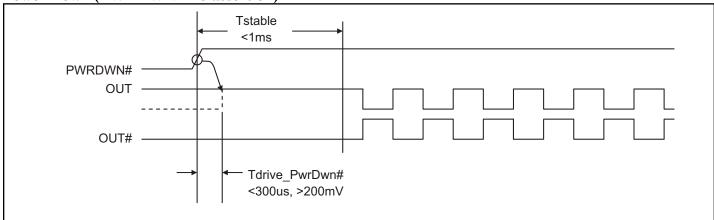

Figure 2. Power down de-assert sequence

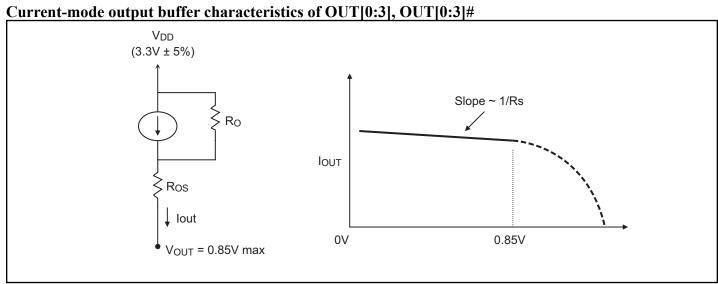

Figure 9. Simplified diagram of current-mode output buffer

### **Differential Clock Buffer characteristics**

| Symbol          | Minimum     | Maximum     |

|-----------------|-------------|-------------|

| $R_{O}$         | 3000Ω       | N/A         |

| R <sub>OS</sub> | unspecified | unspecified |

| $ m V_{OUT}$    | N/A         | 850mV       |

## **Current Accuracy**

| Symbol           | Conditions              | Configuration                                          | Load                                      | Min.                         | Max.                         |

|------------------|-------------------------|--------------------------------------------------------|-------------------------------------------|------------------------------|------------------------------|

| I <sub>OUT</sub> | $V_{DD} = 3.30 \pm 5\%$ | $R_{REF} = 475\Omega \ 1\%$ $I_{REF} = 2.32 \text{mA}$ | Nominal test load for given configuration | -12%<br>I <sub>NOMINAL</sub> | +12%<br>I <sub>NOMINAL</sub> |

#### Note:

## **Differential Clock Output Current**

| Board Target Trace/Term Z                     | Reference R, Iref = $V_{DD}/(3xRr)$             | Output Current              | V <sub>OH</sub> @ Z |

|-----------------------------------------------|-------------------------------------------------|-----------------------------|---------------------|

| 100Ω (100Ω differential ≈ 15% coupling ratio) | $R_{REF} = 475\Omega \ 1\%,$ $I_{REF} = 2.32mA$ | $I_{OH} = 6 \times I_{REF}$ | 0.7V @ 50           |

<sup>1.</sup> I<sub>NOMINAL</sub> refers to the expected current based on the configuration of the device.

## Absolute Maximum Ratings (Over operating free-air temperature range)

| Symbol               | Parameters               | Min. | Max. | Units |

|----------------------|--------------------------|------|------|-------|

| $V_{\mathrm{DD\_A}}$ | 3.3V Core Supply Voltage | -0.5 | 4.6  |       |

| $V_{\mathrm{DD}}$    | 3.3V I/O Supply Voltage  | -0.5 | 4.6  |       |

| $V_{\mathrm{IH}}$    | Input High Voltage       |      | 4.6  | '     |

| $V_{ m IL}$          | Input Low Voltage        | -0.5 |      |       |

| Ts                   | Storage Temperature      | -65  | 150  | °C    |

| $V_{\mathrm{ESD}}$   | ESD Protection           | 2000 |      | V     |

#### Note:

## **DC Electrical Characteristics** ( $V_{DD} = 3.3 \pm 5\%$ , $V_{DD A} = 3.3 \pm 5\%$ )

| Symbol                  | Parameters                        | Condition                           | Min.         | Max.               | Units |  |

|-------------------------|-----------------------------------|-------------------------------------|--------------|--------------------|-------|--|

| $V_{\mathrm{DD\_A}}$    | 3.3V Core Supply Voltage          |                                     | 3.135        | 3.465              | V     |  |

| $V_{ m DD}$             | 3.3V I/O Supply Voltage           |                                     | 3.135        | 3.465              |       |  |

| $V_{ m IH}$             | 3.3V Input High Voltage           | $V_{ m DD}$                         | 2.0          | $V_{\rm DD} + 0.3$ |       |  |

| $ m V_{IL}$             | 3.3V Input Low Voltage            |                                     | $V_{SS}-0.3$ | 0.8                |       |  |

| ${ m I}_{ m IL}$        | Input Leakage Current             | $0 < V_{IN} < V_{DD}$               | -5           | +5                 | μΑ    |  |

| $ m V_{OH}$             | 3.3V Output High Voltage          | $I_{OH} = -1 \text{mA}$             | 2.4          |                    | V     |  |

| $V_{ m OL}$             | 3.3V Output Low Voltage           | $I_{OL} = 1 \text{mA}$              |              | 0.4                |       |  |

| T                       | 0.4.411.1.0                       | $I_{OH} = 6 \times I_{REF}$         | 12.2         |                    | mA    |  |

| $I_{OH}$                | Output High Current               | $I_{REF} = 2.32 \text{mA}$          |              | 15.6               |       |  |

| $C_{IN}$                | Input Pin Capacitance             |                                     | 2            | 5                  | Г     |  |

| $C_{ m OUT}$            | Output Pin Capacitance            |                                     |              | 6                  | pF    |  |

| $L_{PIN}$               | Pin Inductance                    |                                     |              | 7                  | nН    |  |

| I <sub>DD(BYPASS)</sub> | Power Supply Current (PLL Bypass) | $V_{DD} = 3.465V, F_{CPU} = 100MHz$ |              | 90                 |       |  |

| I <sub>DD</sub>         | Darriag Crosseller Crossesset     | $V_{DD} = 3.465V$                   | Bypass mode  | 100                | mA    |  |

|                         | Power Supply Current              | $F_{CPU} = 100MHz$                  | PLL mode     | 130                |       |  |

| $I_{SS}$                | Power Down Current                | Driven outputs                      |              | 40                 |       |  |

| $I_{SS}$                | Power Down Current                | Tristate outputs                    |              | 12                 |       |  |

| $T_{\mathbf{A}}$        | Ambient Temperature               |                                     | -40          | 85                 | °C    |  |

<sup>1.</sup> Stress beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

## **AC Switching Characteristics** (V<sub>DD</sub> = 3.3±5%, V<sub>DD\_A</sub> = 3.3±5%)

| Symbol                                     | Parameters                                             | Min  | Max. | Units | Notes |

|--------------------------------------------|--------------------------------------------------------|------|------|-------|-------|

| F <sub>IN</sub>                            | PLL Mode                                               | 95   | 105  | MHz   |       |

|                                            | Bypass Mode                                            | 100  | 400  | MHz   |       |

| Trise / Tfall                              | Rise and Fall Time (measured between 0.175V to 0.525V) | 175  | 700  | ps    | 2     |

| DT <sub>rise</sub> /<br>DT <sub>fall</sub> | Rise and Fall Time Variation                           |      | 125  | ps    | 2     |

| $T_{pd}$                                   | PLL Mode                                               |      | ±250 | ps    |       |

|                                            | Non-PLL Mode                                           | 2.5  | 6.5  | ns    |       |

| T <sub>jitter</sub>                        | Cycle – Cycle Jitter                                   |      | 50   | ps    | 3, 4  |

| V <sub>HIGH</sub>                          | Voltage High including overshoot                       | 660  | 1150 | mV    | 2     |

| $V_{ m LOW}$                               | Voltage Low including undershoot                       | -300 |      | mV    | 2     |

| V <sub>cross</sub>                         | Absolute crossing point voltages                       | 250  | 550  | mV    | 2     |

| DV <sub>cross</sub>                        | Total Variation of Vcross over all edges               |      | 140  | mV    | 2     |

| T <sub>DC</sub>                            | Duty Cycle                                             | 45   | 55   | %     | 3     |

| T <sub>jadd</sub>                          | Additive RMS phase jitter for PCIe 2.0                 | <0   | 1    | ps    | 5     |

#### **Notes:**

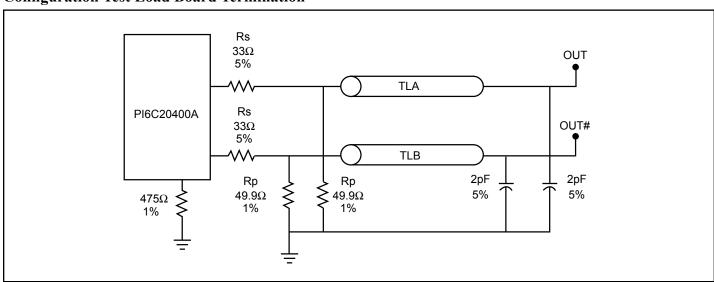

- 1. Test configuration is  $R_s = 33.2\Omega$ ,  $Rp = 49.9\Omega$ , and 2pF.

- 2. Measurement taken from Single Ended waveform.

- 3. Measurement taken from Differential waveform.

- 4. Measurement taken using M1 data capture analysis tool.

- 5. Additive jitter is calculated from input and output RMS phase jitter by using PCIe 2.0 filter.  $(T_{jadd} = \sqrt{(output\ jitter)^2 (input\ jitter)^2}$

## **Configuration Test Load Board Termination**

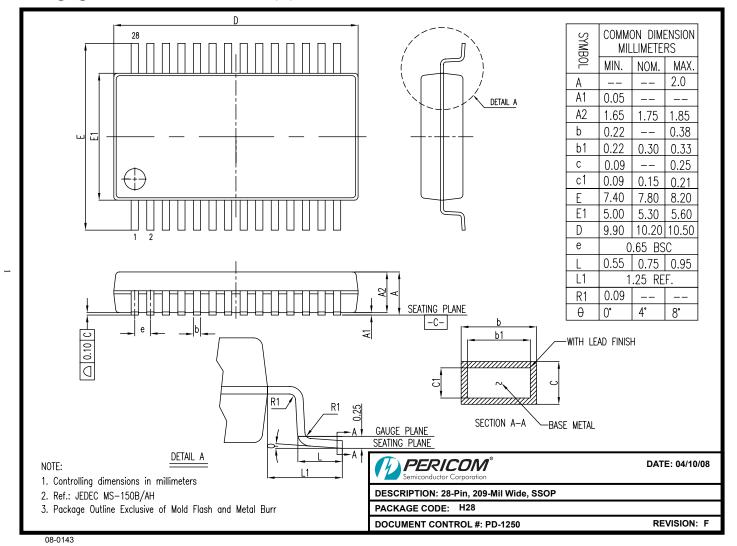

### Packaging Mechanical: 28-Pin SSOP (H)

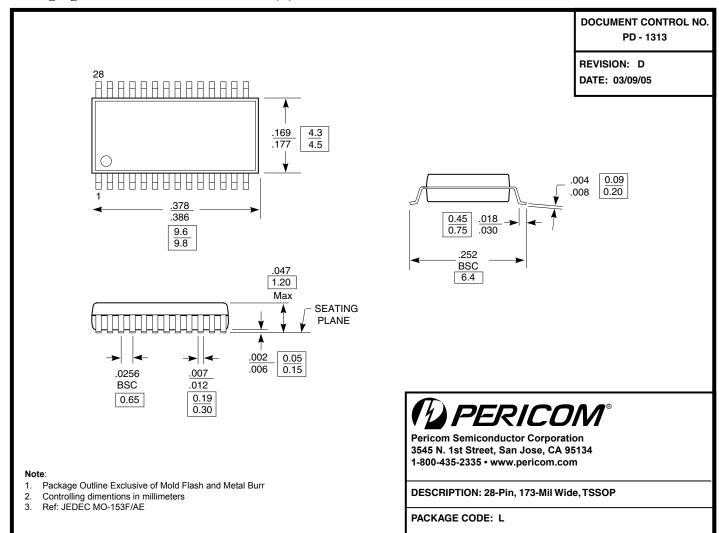

### Packaging Mechanical: 28-Pin TSSOP (L)

# Ordering Information<sup>(1-3)</sup>

| Ordering Code | Package Code | Package Description                            |

|---------------|--------------|------------------------------------------------|

| PI6C20400AHE  | HE           | 28-pin, 209-mil wide, SSOP, Pb-Free and Green  |

| PI6C20400ALE  | LE           | 28-pin, 173-mil wide, TSSOP, Pb-Free and Green |

#### Notes:

- 1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- 2. E = Pb-free and Green

- 3. Adding an X suffix = Tape/Reel

Pericom Semiconductor Corporation • 1-800-435-2336 • www.pericom.com