Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## Low-Noise Phase-Locked Loop Clock Driver with 9 Clock Outputs

#### **Features**

- Operating Frequency up to 150 MHz

- Low-Noise Phase-Locked Loop Clock Distribution to meet 133 MHz Registered DIMM Synchronous DRAM module specifications for server/workstation/PC applications

- Allows Clock Input to have Spread Spectrum modulation for EMI reduction

- Zero input-to-output delay: Distribute One Clock Input to one bank of five and one bank of four outputs, with separate output enables

- Low jitter: cycle-to-cycle jitter ±75ps max.

- 30-ohm on-chip series damping resistor at clock output drivers for low noise and EMI reduction

- Operates at 3.3V V<sub>CC</sub>

- Package (Pb-free and Green available):

- 24-pin TSSOP(L)

#### **Description**

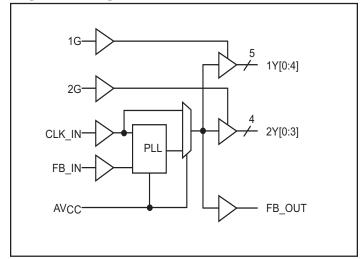

The PI6C2509-133 is a "quiet," low-skew, low-jitter, phase-locked loop (PLL) clock driver, distributing low-noise clock signals for SDRAM and server applications. By connecting the feedback FB\_OUT output to the feedback FB\_IN input, the propagation delay from the CLK\_IN input to any clock output will be nearly zero. This zero-delay feature allows the CLK\_IN input clock to be distributed, providing 5 clocks for the first bank, and an additional 4 clocks for the second bank.

This clock driver is designed to meet the PC133 SDRAM Registered DIMM specification. For test purposes, the PLL can be bypassed by strapping AV<sub>CC</sub> to ground.

#### Logic Block Diagram

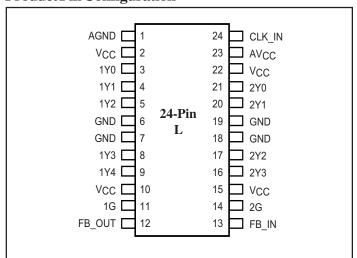

### **Product Pin Configuration**

### **Functional Table**

| Input Control      | Outputs                 |        |  |

|--------------------|-------------------------|--------|--|

| X <sup>(1)</sup> G | X <sup>(1)</sup> Y[0:3] | FB_OUT |  |

| L                  | L                       | CLK_IN |  |

| Н                  | CLK_IN                  | CLK_IN |  |

#### Note:

1. X is either 1 or 2

### **Pin Functions**

| Pin Name         | Pin No.          | Туре   | Description                                                                                                                                                                                        |

|------------------|------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK_IN           | 24               | I      | Clock input. CLK_IN allows spread spectrum.                                                                                                                                                        |

| FB_IN            | 13               | I      | Feedback input. FB_IN provides the feedback signal to the internal PLL.                                                                                                                            |

| 1G               | 11               | Ι      | Output bank enable. When 1G is LOW, outputs 1Y[0:4] are disabled to a logic low state. When 1G is HIGH, all outputs 1Y[0:4] are enabled.                                                           |

| 2G               | 14               | Ι      | Output bank enable. When 2G is LOW, outputs 2Y[0:3] are disabled to a logic low state. When 2G is HIGH, all outputs 2Y[0:3] are enabled.                                                           |

| FB_OUT           | 12               | О      | Feedback output. FB_OUT is dedicated for external feedback. FB_OUT has an embedded series-damping resistor of the same value as the clock outputs 1Yx, 2Yx.                                        |

| 1Y[0:4]          | 3,4,5,8,9        | О      | Clock outputs. These outputs provide low-skew copies of CLK_IN.  Each output has an embedded series-damping resistor.                                                                              |

| 2Y[3:0]          | 16,17,<br>20, 21 | O      | Clock outputs. These outputs provide low-skew copies of CLK_IN.  Each output has an embedded series-damping resistor.                                                                              |

| AV <sub>CC</sub> | 23               | Power  | Analog power supply. $AV_{CC}$ can be also used to bypass the PLL for test purposes. When $AV_{CC}$ is strapped to ground, PLL is bypassed and CLK_IN. is buffered directly to the device outputs. |

| AGND             | 1                | Ground | Analog ground. AGND provides the ground reference for the analog circuitry.                                                                                                                        |

| V <sub>CC</sub>  | 2,10,15,22       | Power  | Power supply.                                                                                                                                                                                      |

| GND              | 6,7,18,19        | Ground | Ground.                                                                                                                                                                                            |

PS8544D 11/17/09 09-0006 2

## DC Specifications (Absolute maximum ratings over operating free-air temperature range)

| Symbol             | Parameter                                               | Min. | Max.                  | Units |

|--------------------|---------------------------------------------------------|------|-----------------------|-------|

| V <sub>I</sub>     | Input voltage range                                     |      | V <sub>CC</sub> + 0.5 |       |

| $V_{O}$            | Output voltage range                                    | -0.5 |                       | V     |

| V <sub>L</sub> DC  | DC input voltage                                        |      | +5.0                  |       |

| I <sub>O</sub> _DC | DC output current                                       |      | 100                   | mA    |

| Power              | Maximum power dissipation at $T_A = 55$ °C in still air |      | 1.0                   | W     |

| $T_{STG}$          | Storage temperature                                     | -65  | 150                   | °C    |

#### Note:

Stress beyond those listed under "absolute maximum ratings" may cause permanent damage to the device.

| Parameter      | Test Conditions                                        | V <sub>CC</sub> | Min. | Тур. | Max. | Units |

|----------------|--------------------------------------------------------|-----------------|------|------|------|-------|

| $I_{CC}$       | $V_{\rm I} = V_{\rm CC}$ or GND; $I_{\rm O} = 0^{(1)}$ | 3.6V            |      |      | 10   | μΑ    |

| C <sub>I</sub> | $V_{I} = V_{CC}$ or GND                                | 2.27/           |      | 4    |      | F     |

| C <sub>O</sub> | $V_O = V_{CC}$ or GND                                  | 3.3V            |      | 6    |      | pF    |

#### Note:

### **Recommended Operating Conditions**

| Symbol          | Parameter                                   | Min.  | Max.            | Units |

|-----------------|---------------------------------------------|-------|-----------------|-------|

| V <sub>CC</sub> | Supply voltage (Commercial)                 | 3.0   | 3.6             |       |

|                 | Supply voltage (Industrial)                 | 3.135 | 3.465           |       |

| $V_{ m IH}$     | High level input voltage                    | 2.0   |                 | V     |

| $V_{ m IL}$     | Low level input voltage                     |       | 0.8             |       |

| V <sub>I</sub>  | Input voltage                               | 0.0   | V <sub>CC</sub> |       |

| $T_{A}$         | Operating free-air temperature (Commercial) | 0     | 70              | °C    |

|                 | Operating free-air temperature (Industrial) | -40   | 85              |       |

## Electrical Characteristics (Over recommended operating free-air temperature range)

## Pull Up/Down Currents: $V_{CC} = 3.0 \text{V} (V_{CC} = 3.135 \text{V})$

| Symbol   | Parameter         | Condition         | Min. | Max.  | Units |

|----------|-------------------|-------------------|------|-------|-------|

| I        | Pull-up current   | $V_{OUT} = 2.4V$  |      | -13.6 |       |

| $I_{OH}$ | Pull-up current   | $V_{OUT} = 2.0V$  |      | -22   |       |

| Ţ        | Pull-down current | $V_{OUT} = 0.8V$  | 19   |       | mA    |

| $I_{OL}$ | Pull-down current | $V_{OUT} = 0.55V$ | 13   |       |       |

<sup>1.</sup> Continuous output current

#### **AC Specifications**

(Timing requirements over recommended ranges of supply voltage and operating free-air temperature.)

| Symbol           | Parameter                          | Min. | Max. | Units |  |

|------------------|------------------------------------|------|------|-------|--|

| F <sub>CLK</sub> | Input clock frequency (Commercial) | 25   | 150  | MHz   |  |

|                  | Input clock frequency (Industrial) | 25   | 125  | MHZ   |  |

|                  | Input clock duty cycle             | 40   | 60   | %     |  |

|                  | Stabilization time after power up  |      | 1    | ms    |  |

## **Switching Characteristics**

(Over recommended ranges of supply voltage and commercial temperature,  $V_{CC}=3.3V\pm0.3V$ ,  $T_A=0\sim70^{\circ}C$ ,  $C_L=15pF$ )

| Parameter                                | Test Conditions                 | Min. | Тур. | Max. | Units |

|------------------------------------------|---------------------------------|------|------|------|-------|

| t <sub>pe</sub> , Phase error            | CLK_IN to FB_IN, f = 133 MHz    | -150 |      | 150  |       |

| t <sub>j</sub> , Jitter (cycle-to-cycle) | f = 133 MHz                     | -75  |      | 75   | ps    |

| t <sub>sk</sub> , Output skew            | Yn or FB_OUT to Yn or FB_OUT    |      |      | 150  |       |

| t <sub>dc</sub> , Duty cycle             | $f = 133 \text{ MHz}, V_{CC}/2$ | 45   | 50   | 55   | %     |

| t <sub>r</sub> , Rise time               | $V_O = 0.4 V$ to $2V$           |      | 1.0  |      |       |

| t <sub>f</sub> , Fall time               | $V_O = 2V$ to $0.4V$            |      | 1.1  |      | ns    |

#### **Switching characteristics**

(Over recommended ranges of supply voltage and industrial temperature,  $V_{CC}=3.3V\pm0.165V$ ,  $T_A=-40\sim85^{\circ}C$ ,  $C_L=15pF$ )

| Parameter                                | Test Conditions                 | Min. | Тур. | Max. | Units |

|------------------------------------------|---------------------------------|------|------|------|-------|

| t <sub>pe</sub> , Phase error            | CLK_IN to FB_IN, f = 125 MHz    | -150 |      | 150  |       |

| t <sub>j</sub> , Jitter (cycle-to-cycle) | f = 125 MHz                     | -75  |      | 75   | ps    |

| t <sub>sk</sub> , Output skew            | Yn or FB_OUT to Yn or FB_OUT    |      |      | 150  |       |

| t <sub>dc</sub> , Duty cycle             | $f = 125 \text{ MHz}, V_{CC}/2$ | 45   | 50   | 55   | %     |

| t <sub>r</sub> , Rise time               | $V_O = 0.4 V$ to $2V$           |      | 1.0  |      | ne    |

| t <sub>f</sub> , Fall time               | $V_O = 2V$ to $0.4V$            |      | 1.1  |      | ns    |

**Note:** These switching parameters are guaranteed, but not production tested.

09-0006 4 PS8544D 11/17/09

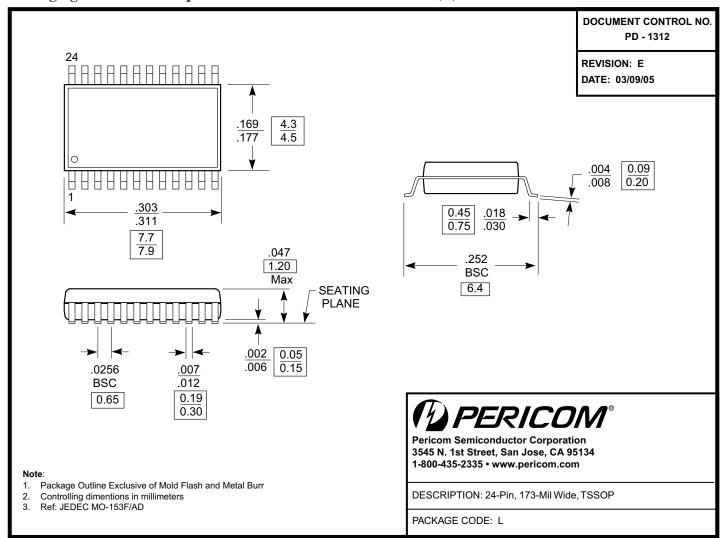

#### Packaging Mechanical: 24-pin Plastic Thin Shrink Small-Outline (L)

#### Note:

For latest package info, please check: http://www.pericom.com/products/packaging/mechanicals.php

### **Ordering Information**

| Ordering Code   | Packaging Code | Package Types                            |

|-----------------|----------------|------------------------------------------|

| PI6C2509-133LEX | L              | Pb-free and Green, 24-pin, 173 mil TSSOP |

#### **Notes:**

- Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- E = Pb-free and Green

- Adding an X suffix = Tape/Reel

Pericom Semiconductor Corporation • 1-800-435-2336 • http://www.pericom.com