# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# PI6C48543

# **3.3V Low Skew 1-to-4, 800MHz,** Differential to LVDS Fanout Buffer

#### Features

- Maximum operation frequency: 800 MHz

- 4 pair of differential LVDS outputs

- Selectable differential CLK and PCLK inputs

- CLK, nCLK pair accepts LVDS, LVPECL, LVHSTL, SSTL and HCSL input level

- PCLK, nPCLK pair supports LVPECL, CML and SSTL input level

- Output Skew: 40ps (maximum)

- Part-to-part skew: 300ps (maximum)

- Propagation delay: 2.2ns (maximum)

- 3.3V power supply

- Pin-to-pin compatible to ICS8543

- Operating Temperature: -40°C to 85°C

- Packaging (Pb-free & Green): -20-pin TSSOP (L)

#### Description

The PI6C48543 is a high-performance low-skew LVDS fanout buffer. PI6C48543 features two selectable differential inputs and translates to four LVDS outputs. The inputs can also be configured to single-ended with external resistor bias circuit. The CLK input accepts LPECL or LVDS or LVHSTL or SSTL or HCSL signals, and PCLK input accepts LVPECL or SSTL or CML signals. The outputs are synchronized with input clock during asynchronous assertion/deassertion of CLK\_EN pin. PI6C48543 is ideal for differential to LVDS translations and/or LVDS clock distribution. Typical clock translation and distribution applications are datacommunications and telecommunications.

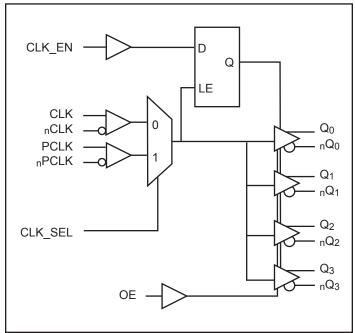

#### **Block Diagram**

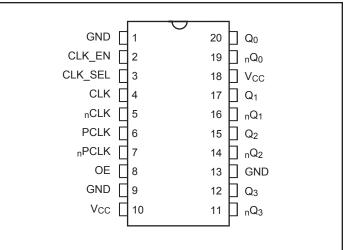

#### **Pin Diagram**

#### **Pin Description**

| Name                                         | Pin #    | Туре | Description                                                                                                                                                                                    |

|----------------------------------------------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND                                          | 1, 9, 13 | Р    | Connect to Ground                                                                                                                                                                              |

| CLK_EN                                       | 2        | I_PU | Synchronized clock enable. When high, clock outputs follow clock input. When low, $Q_x$ outputs are forced low, $_nQ_x$ outputs are forced high. LVCMOS/LVTTL level with 80k $\Omega$ pull up. |

| CLK_<br>SEL                                  | 3        | I_PD | Clock select input. When high, selects $CLK_1$ input. When low, selects $CLK_0$ input. LVCMOS/LVTTL level with $80k\Omega$ pull down.                                                          |

| CLK                                          | 4        | I_PD | Non-inverting differential clock input                                                                                                                                                         |

| nCLK                                         | 5        | I_PU | Inverting differential clock input                                                                                                                                                             |

| PCLK                                         | 6        | I_PD | Non-inverting differential clock input                                                                                                                                                         |

| nPCLK                                        | 7        | I_PU | Inverting differential clock input                                                                                                                                                             |

| OE                                           | 8        | I_PU | Output Enable, Controls outputs Q <sub>0</sub> , <sub>n</sub> Q <sub>0</sub> through Q <sub>3</sub> , <sub>n</sub> Q <sub>3</sub>                                                              |

| V <sub>CC</sub>                              | 10, 18   | Р    | Connect to 3.3V.                                                                                                                                                                               |

| Q3, nQ3                                      | 11, 12   | 0    | Differential output pair, LVDS interface level.                                                                                                                                                |

| Q2, nQ2                                      | 14, 15   | 0    | Differential output pair, LVDS interface level.                                                                                                                                                |

| Q <sub>1</sub> , <sub>n</sub> Q <sub>1</sub> | 16, 17   | 0    | Differential output pair, LVDS interface level.                                                                                                                                                |

| Q <sub>0</sub> , <sub>n</sub> Q              | 19, 20   | 0    | Differential output pair, LVDS interface level.                                                                                                                                                |

Notes:

1. I = Input, O = Output, P = Power supply connection, I\_PD = Input with pull down, I\_PU = Input with pull up

#### **Pin Characteristics**

| Symbol          | Parameter                 | Conditions | Min. | Тур. | Max. | Units |

|-----------------|---------------------------|------------|------|------|------|-------|

| C <sub>IN</sub> | Input Capacitance         |            |      | 6    |      | pF    |

| R_pullup        | Input Pullup Resistance   |            |      | 80   |      | 1-0   |

| R_pulldown      | Input Pulldown Resistance |            |      | 80   |      | kΩ    |

#### **Control Input Function Table**

|    |        | Inputs  |                 | Outputs       |                |  |

|----|--------|---------|-----------------|---------------|----------------|--|

| OE | CLK_EN | CLK_SEL | Selected Source | Q0:Q3         | nQ0:nQ3        |  |

| 1  | 0      | 0       | CLK, nCLK       | Diasbled: Low | Diasbled: High |  |

| 1  | 0      | 1       | PCLK, nPCLK     | Disabled: Low | Disabled: High |  |

| 1  | 1      | 0       | CLK, nCLK       | Enabled       | Enabled        |  |

| 1  | 1      | 1       | PCLK, nPCLK     | Enabled       | Enabled        |  |

| 0  | X      | Х       |                 | Hi-Z          | Hi-Z           |  |

#### Notes:

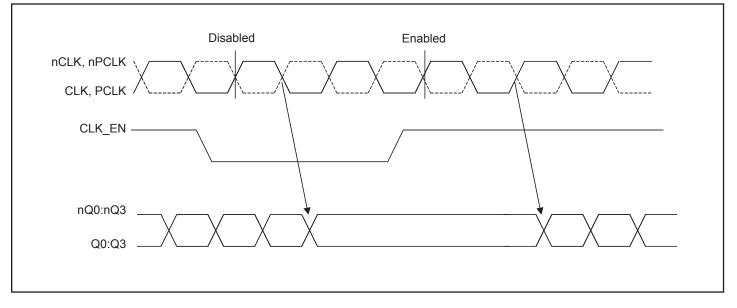

1. After CLK\_EN switches, the clock outputs are disabled or enabled following a rising and falling input clock edge as show below.

#### Figure 1. CLK\_EN Timing Diagram

#### Clock Input Function Table (See Figure 2)

| In                              | nputs                       | Ou    | tputs                             | Input to Output Mode         | Dolowity       |

|---------------------------------|-----------------------------|-------|-----------------------------------|------------------------------|----------------|

| CLK or PCLK                     | nCLK or nPCLK               | Q0:Q3 | nQ0:nQ3                           | Input to Output Widde        | Polarity       |

| 0                               | 1                           | LOW   | HIGH Differential to Differential |                              | None Inverting |

| 1                               | 0                           | HIGH  | LOW                               | Differential to Differential | None Inverting |

| 0                               | Biased; $V_{IN} = V_{CC}/2$ | LOW   | HIGH                              | Single Ended to Differential | None Inverting |

| 1                               | Biased; $V_{IN} = V_{CC}/2$ | HIGH  | LOW                               | Single Ended to Differential | None Inverting |

| Biased; V <sub>IN</sub> = Vcc/2 | 0                           | HIGH  | LOW                               | Single Ended to Differential | Inverting      |

| Biased; $V_{IN} = V_{CC}/2$     | 1                           | LOW   | HIGH                              | Single Ended to Differential | Inverting      |

#### **Absolute Maximum Ratings**

| Symbol           | Parameter           | Conditions        | Min. | Тур. | Max.                  | Units |

|------------------|---------------------|-------------------|------|------|-----------------------|-------|

| V <sub>CC</sub>  | Supply voltage      | Referenced to GND |      |      | 4.6                   |       |

| V <sub>IN</sub>  | Input voltage       | Referenced to GND | -0.5 |      | V <sub>CC</sub> +0.5V | V     |

| V <sub>OUT</sub> | Output voltage      | Referenced to GND | -0.5 |      | V <sub>CC</sub> +0.5V |       |

| T <sub>STG</sub> | Storage temperature |                   | -65  |      | 150                   | °C    |

Notes:

1. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are stress speci fications only and correct functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

#### **Operating Conditions**

| Symbol          | Parameter            | Conditions | Min.  | Тур. | Max.  | Units |

|-----------------|----------------------|------------|-------|------|-------|-------|

| V <sub>CC</sub> | Power Supply Voltage |            | 3.135 | 3.3  | 3.465 | V     |

| TA              | Ambient Temperature  |            | -40   |      | 85    | °C    |

| I <sub>CC</sub> | Power Supply Current |            |       |      | 60    | mA    |

#### **LVCMOS/LVTTL DC Characteristics** ( $T_A = -40^{\circ}C$ to 85°C, $V_{CC} = 3.135V$ to 3.465V unless otherwise stated below.)

| Symbol          | Pa              | rameter    | Conditions                             | Min. | Тур. | Max.  | Units |

|-----------------|-----------------|------------|----------------------------------------|------|------|-------|-------|

| V <sub>IH</sub> | Input High Volt | age        |                                        | 2    |      | 3.765 | V     |

| V <sub>IL</sub> | Input Low Volt  | age        |                                        | -0.3 |      | 0.8   | v     |

| T               | Input High      | CLK_SEL    | $V_{IN} = V_{CC} = 3.465 V$            |      |      | 150   |       |

| I <sub>IH</sub> | Current         | CLK_EN, OE | $V_{IN} = V_{CC} = 3.465 V$            |      |      | 5     | μA    |

| I               | Input Low       | CLK_SEL    | $V_{\rm IN} = 0V, V_{\rm CC} = 3.465V$ | -5   |      |       | μΑ    |

| I <sub>IL</sub> | Current         | CLK_EN, OE | $V_{\rm IN} = 0V, V_{\rm CC} = 3.465V$ | -150 |      |       |       |

# **Differential DC Characteristics** ( $T_A = -40^{\circ}$ C to 85°C, $V_{CC} = 3.135$ V to 3.465V unless otherwise stated below.)

| Symbol           | Parar               | neter                      | Conditions                       | Min. | Тур. | Max.                       | Units |

|------------------|---------------------|----------------------------|----------------------------------|------|------|----------------------------|-------|

| T                | Input High          | nCLK, nPCLK                | $V_{IN} = V_{CC} = 3.465 V$      |      |      | 5                          | uA    |

| I <sub>IH</sub>  | Current             | CLK, PCLK                  | $V_{IN} = V_{CC} = 3.465 V$      |      |      | 150                        | uA    |

| T                | Input Low           | nCLK, nPCLK                | $V_{CC} = 3.465 V, V_{IN} = 0 V$ | -150 |      |                            | uA    |

| I <sub>IL</sub>  | Current             | CLK, PCLK                  | $V_{CC} = 3.465 V, V_{IN} = 0 V$ | -5   |      |                            | uA    |

| V <sub>PP</sub>  | Peak-to-peak Voltag | ge                         |                                  | 0.15 |      | 1.3                        | V     |

| V <sub>CMR</sub> | Common Mode Inp     | out Voltage <sup>(1)</sup> |                                  | 0.5  |      | V <sub>CC</sub> -<br>0.85V | V     |

Notes:

1. For single ended applications, the maximum input voltage for CLK and nCLK is  $V_{CC}\mbox{+}0.3V$

## **LVPECL DC Characteristics** ( $T_A = -40^{\circ}$ C to 85°C, $V_{CC} = 3.135$ V to 3.465V unless otherwise stated below.)

| Symbol           | Pa                | arameter                          | Conditions                       | Min. | Тур. | Max.            | Units |

|------------------|-------------------|-----------------------------------|----------------------------------|------|------|-----------------|-------|

| т                | Input High        | nCLK, nPCLK                       | $V_{IN} = V_{CC} = 3.465 V$      |      |      | 5               |       |

| I <sub>IH</sub>  | Current           | CLK, PCLK                         | $V_{IN} = V_{CC} = 3.465 V$      |      |      | 150             | μA    |

| I                | Input Low         | nCLK, nPCLK                       | $V_{CC} = 3.465 V, V_{IN} = 0 V$ | -150 |      |                 | μΑ    |

| IIL              | Current           | CLK, PCLK                         | $V_{CC} = 3.465 V, V_{IN} = 0 V$ | -5   |      |                 |       |

| $V_{PP}$         | Peak-to-peak Volt | age                               |                                  | 0.3  |      | 1               | V     |

| V <sub>CMR</sub> | Common Mode In    | nput Voltage; Note <sup>(1)</sup> |                                  | 1.5  |      | V <sub>CC</sub> | v     |

Notes:

1. For single ended applications, the maximum input voltage for PCLK and  $_{n}$ PCLK is V<sub>CC</sub>+0.3V.

| Symbol           | Parameter                                 | Conditions | Min.  | Тур. | Max.  | Units |

|------------------|-------------------------------------------|------------|-------|------|-------|-------|

| V <sub>OD</sub>  | Differential Output Voltage               |            | 200   | 280  | 360   | mV    |

| $\Delta V_{OD}$  | VOD Magnitude Change                      |            |       | 0    | 40    |       |

| V <sub>OS</sub>  | Offset Voltage                            |            | 1.125 | 1.25 | 1.375 | V     |

| $\Delta V_{OS}$  | VOS Magnitude Change                      |            |       | 5    | 25    | mV    |

| I <sub>OZ</sub>  | High Impedance Leakage Current            |            | -10   |      | +10   |       |

| I <sub>OFF</sub> | Power OFF Leakage                         |            | -20   | ±1   | +20   | μΑ    |

| I <sub>OSD</sub> | Differential Output Short Circuit Current |            |       | -3.5 | -5    | A     |

| I <sub>OS</sub>  | Output Short Circuit Current              |            |       | -3.5 | -5    | mA    |

| V <sub>OH</sub>  | Output Voltage High                       |            |       | 1.34 | 1.6   | v     |

| V <sub>OL</sub>  | Output Voltage Low                        |            | 0.9   | 1.06 |       | ]     |

#### **LVDS DC Characteristics** ( $T_A = -40^{\circ}$ C to 85°C, $V_{CC} = 3.135$ V to 3.465V unless otherwise stated below.)

#### **AC Characteristics** ( $T_A = -40^{\circ}C$ to 85°C, $V_{CC} = 3.135V$ to 3.465V)

| Symbol                         | Parameter                            | Conditions              | Min. | Тур. | Max. | Units |

|--------------------------------|--------------------------------------|-------------------------|------|------|------|-------|

| f <sub>max</sub>               | Output Frequency                     |                         |      |      | 800  | MHz   |

| t <sub>Pd</sub>                | Propagation Delay <sup>(1)</sup>     | $f \le 800 \text{ MHz}$ | 1.0  |      | 2.2  | ns    |

| Tsk(o)                         | Output-to-output Skew <sup>(2)</sup> |                         |      |      | 40   |       |

| Tsk(pp)                        | Part-to-part Skew <sup>(3)</sup>     |                         |      |      | 300  | ps    |

| t <sub>r</sub> /t <sub>f</sub> | Output Rise/Fall time                | 20% - 80%               | 100  |      | 300  |       |

| odc                            | Output duty cycle                    |                         | 48   |      | 52   | %     |

Notes:

2 Skew between outputs with the same supply voltage and equal load conditions. Measured at the differential outputs crossing point.

3. Skew between outputs on different parts operating with the same supply voltage and equal load conditions. Measured at the differential out-

puts crossing point.All parameters are measured at 500 MHz unless noted otherwise

#### **Applications Information**

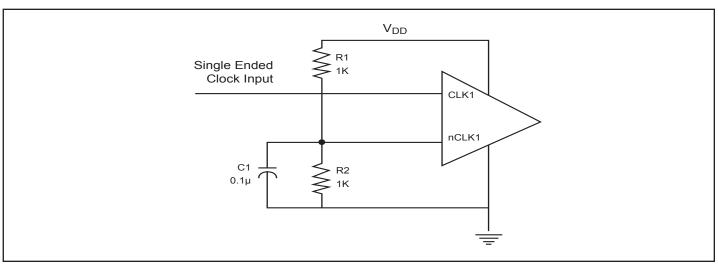

#### Wiring the differential input to accept single ended levels

Figure 1 shows how the differential input can be wired to accept single ended levels. The reference voltage  $V_REF = V_{DD}/2$  is generated by the bias resistors R1, R2 and C1. This bias circuit should be located as close as possible to the input pin. The ratio of R1 and R2 might need to be adjusted to postion the V\_REF in the center of the input voltage swing. For example, if the input clock swing is only 2.5V and  $V_{DD} = 3.3V$ , V\_REF should be 1.25V and R1/R2 = 0.609.

<sup>1.</sup> Measured from the differenital input crossing point to the differential output crossing point

Figure 1: Single-ended Signal Driving Differential Input

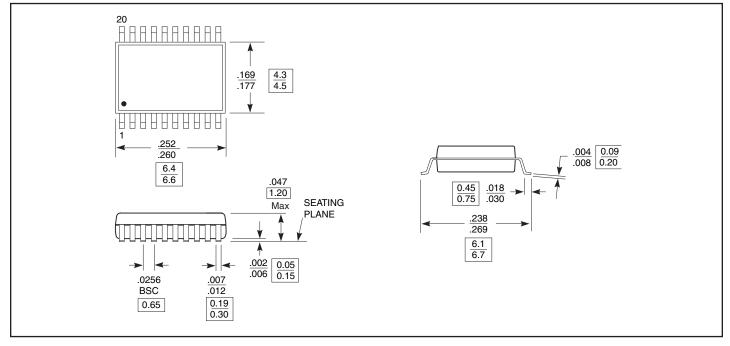

## Packaging Mechanical: 20-Pin TSSOP (L)

# **Ordering Information**

| Ordering Code | Package Code | Package Description                       |

|---------------|--------------|-------------------------------------------|

| PI6C48543LE   | L            | Pb-free & Green 20-pin 173-mil wide TSSOP |

Notes:

1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/