# mail

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

PERICOM<sup>®</sup>

## PI6CDBL402B

### 4 -Output Low Power PCIE GEN 1-2-3 Buffer

#### **Features**

- → Phase jitter filter for PCIe 3.0/ 2.0/ 1.0 application

- ➔ Low power consumption with independent output power supply 1.8V~3.3V

- ➔ Low skew < 60ps</p>

- → Low cycle-to-cycle jitter 45ps (typ.) @100MHz

- → < 1 ps additive RMS phase jitter</p>

- → Output Enable for all outputs

- → Programmable PLL Bandwidth

- → 100 MHz PLL Mode operation

- → 1 400 MHz Bypass Mode operation

- → 3.3V Operation

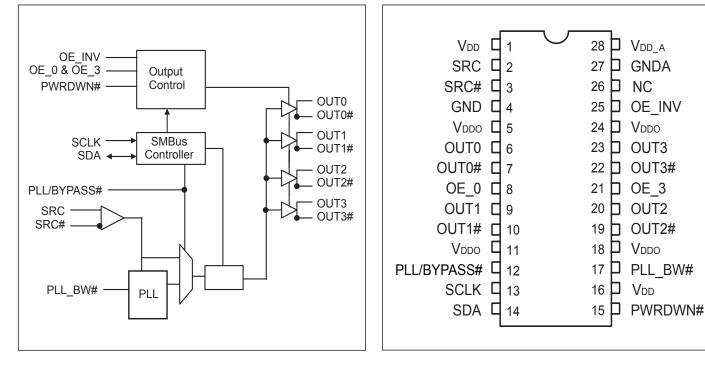

**Block Diagram**

➔ Packaging (Pb-free and Green): -28-Pin TSSOP (L28)

### Description

Pericom Semiconductor's PI6CDBL402B is a PCIe 3.0 compliant high-speed, low-noise differential clock buffer designed to be companion to PCIe 3.0 clock generator. It is backward compatible with PCIe 1.0 and 2.0 specification.

The device distributes the differential SRC clock from PCIe 3.0 clock generator to four differential pairs of clock outputs either with or without PLL. The clock outputs are controlled by input selection of PWRDWN# and SMBus, SCLK and SDA.

#### **Pin Configuration**

#### **Pin Description**

| Pin #                       | Pin Name             | Туре   | Description                                                                      |

|-----------------------------|----------------------|--------|----------------------------------------------------------------------------------|

| 2, 3                        | SRC & SRC#           | Input  | 0.7V Differential SRC input from PI6C410 clock synthesizer                       |

|                             |                      |        | 3.3V LVTTL input for enabling outputs, active high.                              |

| 8, 21                       | OE_0 & OE_3          | Input  | OE_0 for OUT0 / OUT0#                                                            |

|                             |                      |        | OE_3 for OUT3 / OUT3#                                                            |

|                             |                      |        | 3.3V LVTTL input for inverting the OE and PWRDWN# pins.                          |

| 25                          | OE_INV               | Input  | When $0 = $ same stage                                                           |

|                             |                      |        | When 1 = OE_0, OE_3, PWRDWN# inverted.                                           |

| 6, 7, 9, 10, 19, 20, 22, 23 | OUT[0:3] & OUT[0:3]# | Output | 0.7V Differential outputs, refer Power Management Table for detail output status |

| 12                          | PLL/BYPASS#          | Input  | 3.3V LVTTL input for selecting fan-out of PLL operation.                         |

| 13                          | SCLK                 | Input  | SMBus compatible SCLOCK input                                                    |

| 14                          | SDA                  | I/O    | SMBus compatible SDATA                                                           |

| 26                          | NC                   |        | No Connect                                                                       |

| 17                          | PLL_BW#              | Input  | 3.3V LVTTL input for selecting the PLL bandwidth                                 |

| 15                          | PWRDWN#              | Input  | 3.3V LVTTL input for Power Down operation, active low                            |

| 5, 11, 18, 24               | V <sub>DDO</sub>     | Power  | Power supply for outputs, range from 1.8V~3.3V                                   |

| 4                           | GND                  | Ground | Ground for Outputs                                                               |

| 27                          | GNDA                 | Ground | Ground for PLL                                                                   |

| 28                          | V <sub>DD_A</sub>    | Power  | 3.3V Power Supply for PLL                                                        |

| 1, 16                       | V <sub>DD</sub>      | Power  | 3.3V Power Supply for PLL                                                        |

#### **Power Management Table**

Output[0]/ Output[3] state choose

| OE_INV | PWRDWN# | Byte0/Bit7 | OE_0/OE_3(Pin) | OE(SMBus bit) | OUT0/ OUT3   | OUT0#/ OUT3# |

|--------|---------|------------|----------------|---------------|--------------|--------------|

| 0      | X       | Х          | 0              | X             | LOW          | LOW          |

| 0      | X       | Х          | X              | 0             | LOW          | LOW          |

| 0      | 0       | 0          | 1              | 1             | HIGH         | LOW          |

| 0      | 0       | 1          | X              | X             | LOW          | LOW          |

| 0      | 1       | Х          | 1              | 1             | Clock output | Clock output |

| 1      | X       | Х          | 1              | Х             | LOW          | LOW          |

| 1      | Х       | Х          | X              | 0             | LOW          | LOW          |

| 1      | 1       | 0          | 0              | 1             | HIGH         | LOW          |

| 1      | 1       | 1          | Х              | X             | LOW          | LOW          |

| 1      | 0       | X          | 0              | 1             | Clock output | Clock output |

#### Output[1]/ Output[2] state choose

| OE_INV | PWRDWN# | Byte0/Bit7 | OE(Pin) | OE(SMBus bit) | OUT1/OUT2    | OUT1#/ OUT2# |

|--------|---------|------------|---------|---------------|--------------|--------------|

| 0      | X       | X          | NA      | 0             | LOW          | LOW          |

| 0      | 0       | 0          | NA      | 1             | HIGH         | LOW          |

| 0      | 0       | 1          | NA      | Х             | LOW          | LOW          |

| 0      | 1       | X          | NA      | 1             | Clock output | Clock output |

| 1      | X       | X          | NA      | 0             | LOW          | LOW          |

| 1      | 1       | 0          | NA      | 1             | HIGH         | LOW          |

| 1      | 1       | 1          | NA      | Х             | LOW          | LOW          |

| 1      | 0       | X          | NA      | 1             | Clock output | Clock output |

Notes:

1. all registers can't be written/read during PWRDWN# active

#### Serial Data Interface (SMBus)

This part is a slave only device that supports blocks read and block write protocol using a single 7-bit address and read/write bit as shown below.

Read and write block transfers can be stopped after any complete byte transfer by issuing STOP.

#### Address Assignment

| A6 | A5 | A4 | A3 | A2 | A1 | A0 | W/R |

|----|----|----|----|----|----|----|-----|

| 1  | 1  | 0  | 1  | 1  | 1  | 0  | 0/1 |

#### Data Protocol

| 1 bit        | 7 bits        | 1   | 1   | 8 bits             | 1   | 8 bits               | 1   | 8 bits         | 1   | 8 bits                    | 1   | 1 bit    |

|--------------|---------------|-----|-----|--------------------|-----|----------------------|-----|----------------|-----|---------------------------|-----|----------|

| Start<br>bit | Slave<br>Addr | R/W | Ack | Register<br>offset | Ack | Byte<br>Count<br>= N | Ack | Data<br>Byte 0 | Ack | <br>Data<br>Byte N<br>- 1 | Ack | Stop bit |

Notes:

1. Register offset for indicating the starting register for indexed block write and indexed block read. Byte Count in write mode cannot be 0.

15-0083

### Data Byte 0: Control Register

| Bit | Descriptions                 | Туре | Power Up Condition | Output(s) Affected  | Source Pin |

|-----|------------------------------|------|--------------------|---------------------|------------|

| 0   | Reserved                     |      |                    |                     | NA         |

|     | PLL/BYPASS#                  |      |                    |                     |            |

| 1   | 0 = Fanout                   | RW   | 1 = PLL            | OUT[0:3], OUT[0:3]# | NA         |

|     | 1 = PLL                      |      |                    |                     |            |

|     | PLL Bandwidth                |      |                    |                     |            |

| 2   | 0 = High Bandwidth,          | RW   | 1 = Low            | OUT[0:3], OUT[0:3]# | NA         |

|     | 1 = Low Bandwidth            |      |                    |                     |            |

| 3   | Reserved                     |      |                    |                     | NA         |

| 4   | Reserved                     |      |                    |                     | NA         |

| 5   | Reserved                     |      |                    |                     | NA         |

| 6   | Reserved                     |      |                    |                     | NA         |

| 7   | PD_Mode                      | DIAZ | 0                  |                     | NT A       |

| 7   | Refer Power Management Table | RW   | 0                  | OUT[0:3], OUT[0:3]# | NA         |

### **Data Byte 1: Control Register**

| Bit | Descriptions                | Туре | Power Up Condition | Output(s) Affected | Source Pin |

|-----|-----------------------------|------|--------------------|--------------------|------------|

| 0   | Reserved                    |      |                    |                    | NA         |

| 1   | OUTPUTS enable              | RW   | 1 = Enabled        | OUT0, OUT0#        | NA         |

| 2   | 1 = Enabled<br>0 = Disabled | RW   | 1 = Enabled        | OUT1, OUT1#        | NA         |

| 3   | Reserved                    |      |                    |                    | NA         |

| 4   | Reserved                    |      |                    |                    | NA         |

| 5   | OUTPUTS enable              | RW   | 1 = Enabled        | OUT2, OUT2#        | NA         |

| 6   | 1 = Enabled<br>0 = Disabled | RW   | 1 = Enabled        | OUT3, OUT3#        | NA         |

| 7   | Reserved                    |      |                    |                    | NA         |

4

#### Data Byte 2: Control Register

| Bit | Descriptions | Туре | Power Up Condition | Output(s) Affected | Source Pin |

|-----|--------------|------|--------------------|--------------------|------------|

| 0   | Reserved     |      |                    |                    | NA         |

| 1   | Reserved     |      |                    |                    | NA         |

| 2   | Reserved     |      |                    |                    | NA         |

| 3   | Reserved     |      |                    |                    | NA         |

| 4   | Reserved     |      |                    |                    | NA         |

| 5   | Reserved     |      |                    |                    | NA         |

| 6   | Reserved     |      |                    |                    | NA         |

| 7   | Reserved     |      |                    |                    | NA         |

#### **Data Byte 3: Control Register**

| Bit | Descriptions | Туре | Power Up Condition | Output(s) Affected | Source Pin |

|-----|--------------|------|--------------------|--------------------|------------|

| 0   |              | RW   |                    |                    |            |

| 1   |              | RW   |                    |                    |            |

| 2   |              | RW   |                    |                    |            |

| 3   | D 1          | RW   |                    |                    |            |

| 4   | Reserved     | RW   |                    |                    |            |

| 5   |              | RW   |                    |                    |            |

| 6   |              | RW   |                    |                    |            |

| 7   |              | RW   |                    |                    |            |

#### Data Byte 4: Control Register

| Bit | Descriptions | Туре | Power Up Condition | Output(s) Affected | Source Pin |

|-----|--------------|------|--------------------|--------------------|------------|

| 0   |              | R    | 0                  | NA                 | NA         |

| 1   |              | R    | 0                  | NA                 | NA         |

| 2   |              | R    | 0                  | NA                 | NA         |

| 3   | Pericom ID   | R    | 0                  | NA                 | NA         |

| 4   |              | R    | 0                  | NA                 | NA         |

| 5   |              | R    | 1                  | NA                 | NA         |

| 6   |              | R    | 0                  | NA                 | NA         |

| 7   |              | R    | 0                  | NA                 | NA         |

5

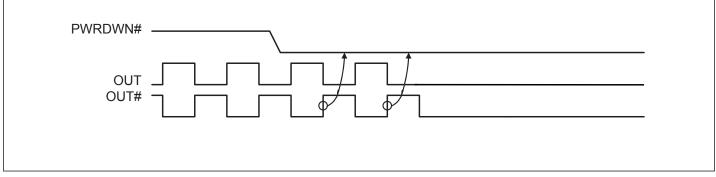

#### Power Down (PWRDWN# assertion)

Figure 1. Power down sequence

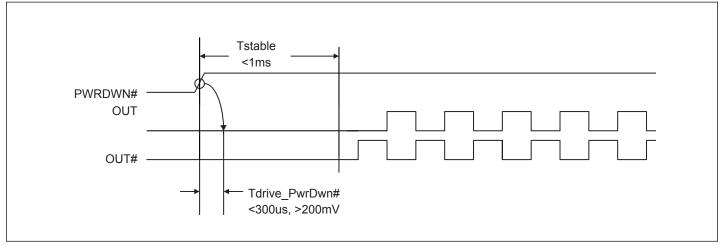

#### Power Down (PWRDWN# De-assertion)

Figure 2. Power down de-assert sequence

6

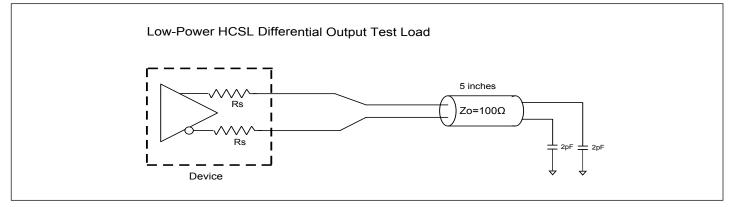

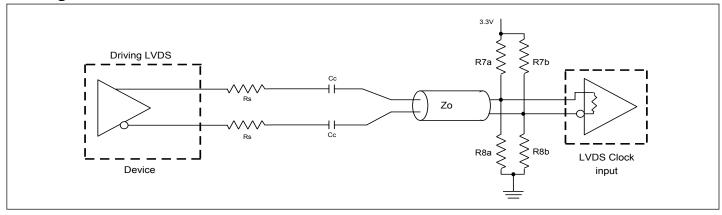

#### **Test Loads**

#### **Driving LVDS**

#### Driving LVDS inputs with the PI6CDBL402B

|           | Va                       | Value                              |      |  |  |  |  |  |

|-----------|--------------------------|------------------------------------|------|--|--|--|--|--|

| Component | Receiver has termination | Receiver does not have termination | Note |  |  |  |  |  |

| R7a, R7b  | 10Κ Ω                    | 140 Ω                              |      |  |  |  |  |  |

| R8a, R8b  | 5.6Κ Ω                   | 75 Ω                               |      |  |  |  |  |  |

| Cc        | 0.1 uF                   | 0.1 uF                             |      |  |  |  |  |  |

| Vcm       | 1.2 volts                | 1.2 volts                          |      |  |  |  |  |  |

#### **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.)

| Supply Voltage to Ground Potential | 4.6V                         |

|------------------------------------|------------------------------|

| All Inputs and Output              | 0.5V toV <sub>DD</sub> +0.5V |

| Ambient Operating Temperature      | -40 to +85°C                 |

| Storage Temperature                | 65°C to +150°C               |

| Junction Temperature               | 125°C                        |

| Soldering Temperature              |                              |

| ESD Protection (Input)             | 2000V(HBM)                   |

**Note:** Stresses greater than those listed under MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### Electrical Characteristics–Clock Input Parameters ( $T_A = -40 \sim 85^{\circ}C$ ; VDD = 3.3V+/-10%; VDDO =

| Symbol             | Parameters                                         | Condition                                                     | Min.              | Туре | Max. | Units |

|--------------------|----------------------------------------------------|---------------------------------------------------------------|-------------------|------|------|-------|

| V                  | Input High Voltage DIE INI                         | Differential inputs                                           | (00               | 000  | 1150 | mV    |

| $V_{_{IHDIF}}$     | Input High Voltage - DIF_IN <sup>1</sup>           | (single-ended measurement)                                    | 600               | 800  |      | 111V  |

| V                  | Innut Low Voltage DIE IN13                         | Differential inputs                                           | V <sub>ss</sub> - | 0    | 300  | mV    |

| $V_{ILDOF}$        | Input Low Voltage - DIF_IN <sup>1,3</sup>          | (single-ended measurement)                                    | 300               | U    |      | IIIV  |

| V <sub>com</sub>   | Input Common Mode Voltage -<br>DIF_IN <sup>1</sup> | Common Mode Input Voltage                                     | 300               |      | 725  | mV    |

| V <sub>swing</sub> | Input Amplitude - DIF_IN <sup>1</sup>              | Peak to Peak value (V <sub>IHDIF</sub> - V <sub>ILDIF</sub> ) | 300               |      | 1450 | mV    |

| dv/dt              | Input Slew Rate - DIF_IN <sup>1,2</sup>            | Measured differentially                                       | 0.4               |      |      | V/ns  |

| I                  | Input Leakage Current <sup>1</sup>                 | $V_{IN} = V_{DD}$ , $V_{IN} = GND$                            | -5                |      | 5    | uA    |

| $d_{tin}$          | Input Duty Cycle <sup>1</sup>                      | Measurement from differential wave-<br>from                   | 45                |      | 55   | %     |

| J <sub>DIFIn</sub> | Input Jitter - Cycle to Cycle <sup>1</sup>         | Differential Measurement                                      | 0                 |      | 150  | ps    |

3.3V+/-10%, VDDO = 2.5V+/-10%, VDDO = 1.8V+/-10%, See Test Loads for Loading Conditions)

Note:

1. Guaranteed by design and characterization, not 100% tested in production.

2. Slew rate measured through +/-75mV window centered around differential zero

3. The device can be driven from a single ended clock by driving the true clock and biasing the complement clock input to the VBIAS, where VBIAS is (VIH-HIGH - VIHLOW)/2

#### Electrical Characteristics-Input/Supply/Common Parameters-Normal Operating

**Conditions** ( $T_A = -40 \sim 85^{\circ}C$ ; SVDD = 3.3V+/-10%; VDDO = 3.3V+/-10%, VDDO = 2.5V+/-10%, VDDO = 1.8V+/-10%, See Test Loads for Loading Conditions)

| Symbol                | Parameters                                    | Condition                                                                                                                                       |                           | Туре   | Max.                     | Units  |

|-----------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------|--------------------------|--------|

| $V_{DD_A}, V_{DD}$    | Supply Voltage <sup>1</sup>                   | Supply voltage for core, analog                                                                                                                 | 3.0                       | 3.3    | 3.6                      | V      |

|                       |                                               | 3.3V Operation                                                                                                                                  | 2.97                      | 3.3    | 3.63                     |        |

| V <sub>DDO</sub>      | Supply Voltage <sup>1</sup>                   | 2.5V Operation                                                                                                                                  | 2.25                      | 2.5    | 2.75                     | V      |

|                       |                                               | 1.8V Operation                                                                                                                                  | 1.62                      | 1.8    | 1.98                     | 1      |

| $V_{_{\rm IH}}$       | Input High Voltage <sup>1</sup>               | Single-ended inputs, except SMBus                                                                                                               |                           |        | V <sub>DD</sub> +<br>0.3 | V      |

| V <sub>IL</sub>       | Input Low Voltage <sup>1</sup>                | Single-ended inputs, except SMBus                                                                                                               | -0.3                      |        | 0.35<br>V <sub>DD</sub>  | V      |

| V <sub>IH</sub>       | Output High Voltage <sup>1</sup>              | Single-ended outputs, except SMBus. $I_{OH} = -2mA$                                                                                             | V <sub>DD</sub> -<br>0.45 |        |                          | V      |

| V <sub>IL</sub>       | Outputt Low Voltage <sup>1</sup>              | Single-ended outputs, except SMBus. $I_{OL} = -2mA$                                                                                             |                           |        | 0.45                     | V      |

| I                     |                                               | Single-ended inputs, $V_{IN} = GND$ , $V_{IN} = VDD$                                                                                            | -5                        |        | 5                        | uA     |

| I <sub>inp</sub>      | Input Current <sup>1</sup>                    | Single-ended inputs<br>$V_{IN} = 0$ V; Inputs with internal pull-up resistors<br>$V_{IN} = VDD$ ; Inputs with internal pull-down resis-<br>tors | -200                      |        | 200                      | uA     |

| F <sub>ibyp</sub>     |                                               | Bypass mode                                                                                                                                     | 1                         |        | 400                      | MHz    |

| F <sub>ipll100</sub>  | Input Frequency <sup>2</sup>                  | 100MHz PLL mode                                                                                                                                 | 95                        | 100.00 | 105                      | MHz    |

| Lpin                  | Pin Inductance <sup>1</sup>                   |                                                                                                                                                 |                           |        | 7                        | nH     |

| C <sub>IN</sub>       |                                               | Logic Inputs, except DIF_IN                                                                                                                     | 1.5                       |        | 5                        | pF     |

| C <sub>INDIF_IN</sub> | Capacitance <sup>1,4</sup>                    | DIF_IN differential clock inputs                                                                                                                | 1.5                       |        | 2.7                      | pF     |

| C <sub>OUT</sub>      |                                               | Output pin capacitance                                                                                                                          |                           |        | 6                        | pF     |

| T <sub>stab</sub>     | Clk Stabilization <sup>1,2</sup>              | From V <sub>DD</sub> Power-Up and after input clock<br>stabilization or de-assertion of PD# to 1st clock 0.6                                    |                           | 1      | ms                       |        |

| f <sub>modin</sub>    | Input SS Modulation<br>Frequency <sup>1</sup> | Allowable Frequency<br>(Triangular Modulation)                                                                                                  | 30                        | 31.500 | 33                       | kHz    |

| t <sub>latoe#</sub>   | OE# Latency <sup>1,3</sup>                    | DIF start after OE# assertion<br>DIF stop after OE# deassertion                                                                                 | 1                         |        | 3                        | clocks |

| t <sub>drvpd</sub>    | Tdrive_PD# <sup>1,3</sup>                     | DIF output enable after<br>PD# de-assertion                                                                                                     |                           | 300    | us                       |        |

| t <sub>F</sub>        | Tfall <sup>1,2</sup>                          | Fall time of single-ended control inputs                                                                                                        |                           |        | 5                        | ns     |

| t <sub>R</sub>        | Trise <sup>1,2</sup>                          | Rise time of single-ended control inputs                                                                                                        |                           |        | 5                        | ns     |

| V <sub>ILSMB</sub>    | SMBus Input Low<br>Voltage <sup>1</sup>       |                                                                                                                                                 |                           |        | 0.8                      | V      |

| V <sub>IHSMB</sub>    | SMBus Input High<br>Voltage <sup>1</sup>      |                                                                                                                                                 |                           |        | 3.6                      | V      |

9

All trademarks are property of their respective owners.

# Electrical Characteristics–Input/Supply/Common Parameters–Normal Operating Conditions Cont...

| Symbol              | Parameters                            | Condition                            | Min. | Туре | Max. | Units  |

|---------------------|---------------------------------------|--------------------------------------|------|------|------|--------|

| V <sub>olsmb</sub>  | SMBus Output Low Voltage <sup>1</sup> | @ I <sub>pullup</sub>                |      |      | 0.4  | V      |

| I <sub>PULLUP</sub> | SMBus Sink Current <sup>1</sup>       | @ V <sub>0L</sub>                    | 4    |      |      | mA     |

| V <sub>DDSMB</sub>  | Nominal Bus Voltage <sup>1</sup>      | 3.3V bus voltage                     | 2.7  |      | 3.6  | V      |

| t <sub>RSMB</sub>   | SCLK/SDATA Rise Time <sup>1</sup>     | (Max VIL - 0.15) to (Min VIH + 0.15) |      |      | 1000 | ns     |

| t <sub>FSMB</sub>   | SCLK/SDATA Fall Time <sup>1</sup>     | (Min VIH + 0.15) to (Max VIL - 0.15) |      |      | 300  | ns     |

| £                   | SMBus Operating                       | Marine CMP and an anti-              |      |      | 400  | 1_1.1_ |

| I <sub>MAXSMB</sub> | Frequency <sup>1,5</sup>              | Maximum SMBus operating frequency    |      |      | 400  | kHz    |

#### Note:

1. Guaranteed by design and characterization, not 100% tested in production.

2. Control input must be monotonic from 20% to 80% of input swing. Input Frequency Capacitance

3. Time from deassertion until outputs are >200 mV

4. DIF\_IN input

5. The differential input clock must be running for the SMBus to be active

#### Electrical Characteristics–DIF 0.7V Low Power HCSL Outputs ( $T_A = -40 \sim 85^{\circ}C$ ; VDD = 3.3V + /-10%;

VDDO = 3.3V + -10%, VDDO = 2.5V + -10%, VDDO = 1.8V + -10%, See Test Loads for Loading Conditions)

| Symbol                    | Parameters                  | Condition                                            |     | Туре | Max. | Units |

|---------------------------|-----------------------------|------------------------------------------------------|-----|------|------|-------|

| Trf                       | Slew rate <sup>1,2,3</sup>  |                                                      | 1.1 | 2    | 4.5  | V/ns  |

| V <sub>HIGH</sub>         | Voltage High <sup>1,7</sup> | Statistical measurement on single-ended signal using | 660 |      | 950  | mV    |

| V <sub>LOW</sub>          | Voltage Low <sup>1,7</sup>  | oscilloscope math function. (Scope averaging on)     |     |      | 200  | mV    |

| Vmax                      | Max Voltage <sup>1</sup>    | Measurement on single ended signal using             |     |      | 1150 | mV    |

| Vmin                      | Min Voltage <sup>1</sup>    | absolute value. (Scope averaging off)                |     |      |      | mV    |

| Vswing                    | Vswing <sup>1,2,7</sup>     | Scope averaging off                                  |     |      |      | mV    |

| Crossing Voltage<br>(abs) | Vcross_abs                  | Scope averaging off                                  |     |      | 550  | mV    |

| Crossing Voltage<br>(var) | Δ-Vcross                    | Scope averaging off                                  |     |      | 140  | mV    |

#### Note:

1. Guaranteed by design and characterization, not 100% tested in production.

2. Measured from differential waveform

3. Slew rate is measured through the Vswing voltage range centered around differential 0V. This results in a +/-150mV window around differential 0V.

4. Matching applies to rising edge rate for Clock and falling edge rate for Clock#. It is measured using a +/-75mV window centered on the average cross point where Clock rising meets Clock# falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations.

5. Vcross is defined as voltage where Clock = Clock# measured on a component test board and only applies to the differential rising edge (i.e. Clock rising and Clock# falling).

6. The total variation of all Vcross measurements in any particular system. Note that this is a subset of Vcross\_min/max (Vcross absolute) allowed. The intent is to limit Vcross induced modulation by setting Δ-Vcross to be smaller than Vcross absolute.

7. At default SMBus settings.

Electrical Characteristics–Current Consumption ( $T_A = -40 \sim 85^{\circ}$ C; VDD = 3.3V+/-10%; VDDO = 3.3V+/-

10%, VDDO = 2.5V+/-10%, VDDO = 1.8V+/-10%, See Test Loads for Loading Conditions)

| Symbol            | Parameters                            | Condition                                                                                                  |  | Туре | Max. | Units |

|-------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------|--|------|------|-------|

|                   |                                       | Total power consumption, All outputs active<br>@100MHz, typical value under VDDO = 1.8V                    |  | 50   | 60   | mA    |

| I <sub>ddop</sub> | Operating Supply Current <sup>1</sup> | Total power consumption, All outputs active<br>@100MHz PLL bypass mode, typical value<br>under VDDO = 1.8V |  | 24   | 28   | mA    |

| I                 | Powerdown Current <sup>1,2</sup>      | Total power consumption, Outputs Low                                                                       |  |      | 1.3  | mA    |

Note:

1. Guaranteed by design and characterization, not 100% tested in production.

2. Input clock stopped.

### Electrical Characteristics–Output Duty Cycle, Jitter, Skew and PLL Characterisitics ( $T_A =$

$-40 \sim 85^{\circ}$ C; VDD = 3.3V+/-10%; VDDO = 3.3V+/-10%, VDDO = 2.5V+/-10%, VDDO = 1.8V+/-10%, See Test Loads for Loading Conditions)

| Symbol                | Parameters                            | Condition                                            | Min. | Туре | Max. | Units |

|-----------------------|---------------------------------------|------------------------------------------------------|------|------|------|-------|

| t <sub>DC</sub>       | Duty Cycle <sup>1</sup>               | Measured differentially, PLL Mode                    | 45   |      | 55   | %     |

| t <sub>DCD</sub>      | Duty Cycle Distortion <sup>1,3</sup>  | Measured differentially, Bypass Mode<br>@100MHz -1.3 |      | 0    | 1.3  | %     |

| t <sub>pdBYP</sub>    |                                       | Bypass Mode, VT = 50%                                | 2500 |      | 5000 | ps    |

| t <sub>pdPLL</sub>    | Skew, Input to Output <sup>1,4</sup>  | PLL Mode VT = 50%                                    | -260 |      | 260  | ps    |

| t <sub>skew</sub>     | Skew, Output to Output <sup>1,2</sup> | PLL Mode VT = 50%                                    |      |      | 60   | ps    |

| t <sub>jcyc-cyc</sub> | Jitter, Cycle to cycle <sup>1,2</sup> | PLL mode                                             |      |      | 60   | ps    |

|                       |                                       | Additive Jitter in Bypass Mode                       |      |      | 25   | ps    |

Note:

1. Guaranteed by design and characterization, not 100% tested in production.

2. Measured from differential waveform

3. Duty cycle distortion is the difference in duty cycle between the output and the input clock when the device is operated in bypass mode.

4. All outputs at default slew rate

5. The MIN/TYP/MAX values of each BW setting track each other, i.e., Low BW MAX will never occur with Hi BW MIN.

**Electrical Characteristics–Phase Jitter Parameters** ( $T_A = -40 \sim 85^{\circ}C$ ; VDD = 3.3V+/-10%; VDDO =

3.3V+/-10%, VDDO = 2.5V+/-10%, VDDO = 1.8V+/-10%, See Test Loads for Loading Conditions)

| Symbol                 | Parameters                               | Condition                                                                                            | Min. | Туре | Industry<br>Limit | Units       |

|------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------|------|------|-------------------|-------------|

| t <sub>jphPCIeG1</sub> |                                          | PCIe Gen 1 <sup>1,2,3</sup>                                                                          |      | 34   | 86                | ps<br>(p-p) |

|                        |                                          | PCIe Gen 2 Lo Band<br>10kHz < f < 1.5MHz <sup>1,2</sup>                                              |      | 0.9  | 3                 | ps<br>(rms) |

| t <sub>jphPCIeG2</sub> | Phase Jitter,<br>PLL Mode                | PCIe Gen 2 High Band<br>1.5MHz < f < Nyquist (50MHz) <sup>1,2</sup>                                  |      | 2.2  | 3.1               | ps<br>(rms) |

| t <sub>jphPCIeG3</sub> |                                          | PCIe Gen 3<br>(PLL BW of 2-4MHz, CDR = $10MHz$ ) <sup>1,2,3,4</sup>                                  |      | 0.5  | 1                 | ps<br>(rms) |

| t <sub>jphSGMII</sub>  |                                          | 125MHz, 1.5MHz to 20MHz, -20dB/decade rollover < 1.5MHz, -40db/decade rolloff > 10MHz <sup>1,6</sup> |      | 1.9  | NA                | ps<br>(rms) |

| t <sub>jphPCIeG1</sub> |                                          | PCIe Gen 1 <sup>1,2,3</sup>                                                                          |      | 0.6  | N/A               | ps<br>(p-p) |

|                        |                                          | PCIe Gen 2 Lo Band<br>10kHz < f < 1.5MHz <sup>1,2,5</sup>                                            |      | 0.1  | N/A               | ps<br>(rms) |

| t <sub>jphPCIeG2</sub> | Additive<br>Phase Jitter,<br>Bypass Mode | PCIe Gen 2 High Band<br>1.5MHz < f < Nyquist (50MHz) <sup>1,2,5</sup>                                |      | 0.05 | N/A               | ps<br>(rms) |

| t <sub>jphPCIeG3</sub> | bypass mode                              | PCIe Gen 3<br>(PLL BW of 2-4MHz, CDR = $10MHz$ ) <sup>1,2,4,5</sup>                                  |      | 0.05 | N/A               | ps<br>(rms) |

| t <sub>jphSGMII</sub>  |                                          | 125MHz, 1.5MHz to 10MHz, -20dB/decade rollover < 1.5MHz, -40db/decade rolloff > 10MHz <sup>1,6</sup> |      | 0.15 | N/A               | ps<br>(rms) |

Note:

1. Applies to all outputs, with device driven by 9FG432AKLF or equivalent.

2. See http://www.pcisig.com for complete specs

3. Sample size of at least 100K cycles. This figures extrapolates to 108ps pk-pk @ 1M cycles for a BER of 1-12.

4. Subject to final ratification by PCI SIG.

5. For RMS figures, additive jitter is calculated by solving the following equation: Additive jitter =  $SQRT[(total jitter)^2 - (input jitter)^2]$

6. Applies to all differential outputs

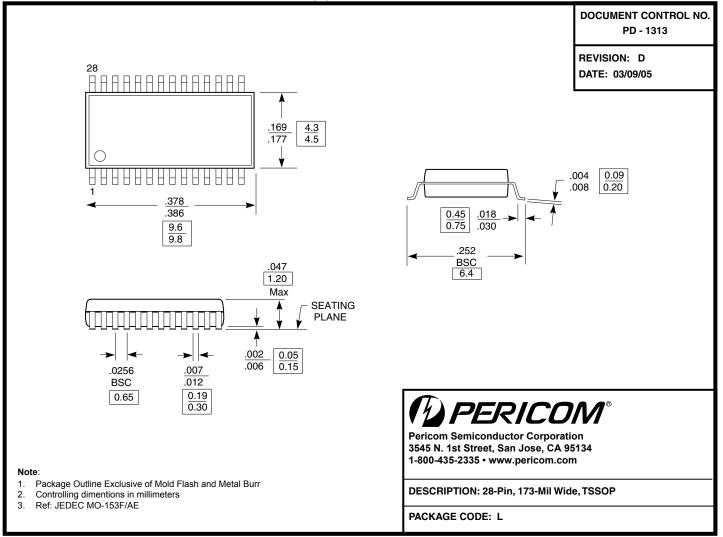

#### Packaging Mechanical: 28-Pin TSSOP (L)

#### Ordering Information<sup>(1-3)</sup>

| Ordering Code   | Package Code | Package Description                       |

|-----------------|--------------|-------------------------------------------|

| PI6CDBL402BLIE  | LE           | 28-pin, 173-mil wide (TSSOP)              |

| PI6CDBL402BLIEX | LE           | 28-pin, 173-mil wide (TSSOP), Tape & Reel |

#### Notes:

1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

15-0083

- 2. E = Pb-free and Green

- 3. Adding an X suffix = Tape/Reel

Pericom Semiconductor Corporation • 1-800-435-2336