Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# PLL Clock Driver for 2.5V DDR-SDRAM Memory

#### **Product Features**

- PLL clock distribution optimized for Double Data Rate SDRAM applications.

- Distributes one differential clock input pair to ten differential clock output pairs.

- Inputs (CLK, CLK) and (FBIN, FBIN): SSTL 2

- Input PWRDWN: LVCMOS

- Outputs (Yx, Yx), (FBOUT, FBOUT): SSTL\_2

- External feedback pins (FBIN, FBIN) are used to synchronize the outputs to the clock input.

- Operates at AV<sub>DD</sub> = 2.5V for core circuit and internal PLL, and V<sub>DDO</sub> = 2.5V for differential output drivers

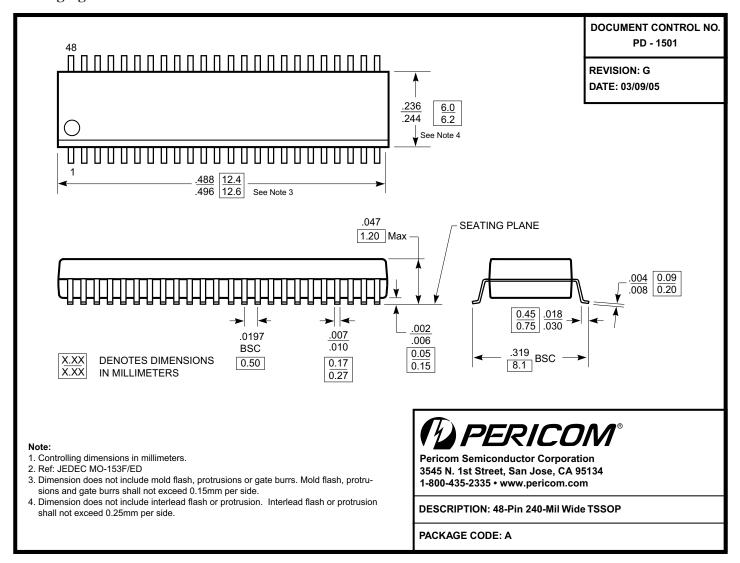

- Packages (Pb-free & Green Available):- Plastic 48-pin TSSOP

#### **Product Description**

PI6CV857L PLL clock device is developed for registered DDR DIMM applications This PLL Clock Buffer is designed for 2.5  $V_{DDQ}$  and 2.5  $V_{AV_{DD}}$  operation and differential data input and output levels. The device is a zero delay buffer that distributes a differential clock inputpair (CLK,  $\overline{CLK}$ ) to ten differential pairs of clock outputs (Y[0:9],  $\overline{Y[0:9]}$ ) and one differential pair feedback clock outputs (FBOUT,  $\overline{FBOUT}$ ). The clock outputs are controlled by the input clocks (CLK,  $\overline{CLK}$ ), the feedback clocks (FBIN,  $\overline{FBIN}$ ), the 2.5  $V_{CV}$  LVCMOS input ( $\overline{PWRDWN}$ ) and the Analog Power input (AVDD). When input PWRDWN is low while power is applied, the input receivers are disabled, the PLL is turned off and the differential clock outputs are 3-stated. When the AVDD is strapped low, the PLL is turned off and bypassed for test purposes.

When the input frequency falls below a suggested detection frequency that is below the operating frequency of the PLL, the device will enter a low power mode. An input frequency detection circuit will detect the low frequency condition and perform the same low power features as when the PWRDWN input is low.

The PLL in the PI6CV857L clock driver uses the input clocks (CLK,  $\overline{\text{CLK}}$ ) and the feedback clocks (FBIN,  $\overline{\text{FBIN}}$ ) to provide high-performance, low-skew, low-jitter output differential clocks ( $\overline{\text{Y[0:9]}}$ , Y[0:9]). The PI6CV857L is also able to track Spread Spectrum Clocking for reduced EMI.

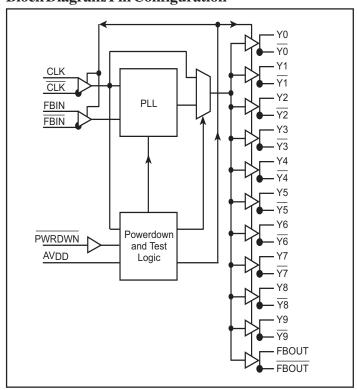

#### **Block Diagram/Pin Configuration**

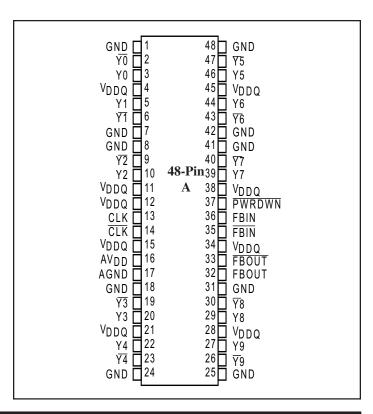

#### **Pinout Table**

| Pin Name         | Pin No.                     | I/O Type | Description                                                                                                                                                                                                                                                                                                 |

|------------------|-----------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK<br>CLK       | 13<br>14                    | Ι        | Reference Clock input                                                                                                                                                                                                                                                                                       |

| Yx               | 3,5,10,20,22,27,29,39,44,46 |          | Clock outputs.                                                                                                                                                                                                                                                                                              |

| $\overline{Yx}$  | 2,6,9,19,23,26,30,40,43,47  | O        | Complement Clock outputs.                                                                                                                                                                                                                                                                                   |

| FBOUT<br>FBOUT   | 32<br>33                    |          | Feedback output, and Complement Feedback Output                                                                                                                                                                                                                                                             |

| FBIN<br>FBIN     | 36<br>35                    |          | Feedback Input, and Complement Feedback Input                                                                                                                                                                                                                                                               |

| PWRDWN           | 37                          | I        | Power down and output disable for all Yx and $\overline{Yx}$ outputs. When $\overline{PWRDWN} = 0$ , the part is powered down and the differential clock outputs are disabled to a 3-state. When $\overline{PWRDWN} = 1$ , all differential clock outputs are enabled and run at the same frequency as CLK. |

| V <sub>DDQ</sub> | 4,11,12,15,21,28,34,38,45   |          | Power Supply for I/O.                                                                                                                                                                                                                                                                                       |

| AV <sub>DD</sub> | 16                          | Power    | Analog /core power supply. AV <sub>DD</sub> can be used to bypass the PLL for testing purposes. When AV <sub>DD</sub> is strapped to ground, PLL is bypassed and CLK is buffered directly to the device outputs.                                                                                            |

| AGND             | 17                          | Ground   | Analog/core ground. Provides the ground reference for the analog/core circuitry                                                                                                                                                                                                                             |

| GND              | 1,7,8,18,24,25,31,41,42,48  | Ground   | Ground                                                                                                                                                                                                                                                                                                      |

#### **Function Table**

|                  | Inputs |       |                    | Outputs |   |       |       | PLL          |

|------------------|--------|-------|--------------------|---------|---|-------|-------|--------------|

| AV <sub>DD</sub> | PWRDWN | CLK   | CLK                | Y       | Y | FBOUT | FBOUT |              |

| GND              | Н      | L     | Н                  | L       | Н | L     | Н     | Bypassed/off |

| GND              | Н      | Н     | L                  | Н       | L | Н     | L     | Bypassed/off |

| X                | L      | L     | Н                  | Z       | Z | Z     | Z     | off          |

| X                | L      | Н     | L                  | Z       | Z | Z     | Z     | off          |

| 2.5V(nom)        | Н      | L     | Н                  | L       | Н | L     | Н     | on           |

| 2.5V(nom)        | Н      | Н     | L                  | Н       | L | Н     | L     | on           |

| 2.5V(nom)        | X      | <20 M | ſНz <sup>(1)</sup> | Z       | Z | Z     | Z     | off          |

**Notes:** For testing and power saving purposes, PI6CV857L will power down if the frequency of the reference inputs CLK,  $\overline{\text{CLK}}$  is well below the operating frequency range. The maximum power down clock frequency is below 20 MHz. For example, PI6CV857L will be powered down when the CLK,  $\overline{\text{CLK}}$  stop running.

Z = High impedance

X = Don't care

#### **Absolute Maximum Ratings** (Over operating free-air temperature range)

| Symbol                               | Parameter                                                     |                  | Max.               | Units |

|--------------------------------------|---------------------------------------------------------------|------------------|--------------------|-------|

| V <sub>DDQ</sub> , AV <sub>DD</sub>  | I/O supply voltage range and analog/core supply voltage range | - 0.5            | 3.6                |       |

| VI                                   | Input voltage range                                           |                  | V +0.5             | V     |

| $V_{O}$                              | Output voltage range                                          | - 0.5            | $V_{\rm DDQ}$ +0.5 |       |

| I <sub>IK</sub>                      | Input Clamp Current                                           | - 50             | 50                 |       |

| I <sub>OK</sub> Output Clamp Current |                                                               | - 50             | 50                 | A     |

| I <sub>O</sub>                       | Continuous output Current                                     | - 50             | 50                 | mA    |

| I <sub>O(PWR)</sub>                  | Continuous current through each $V_{DD},V_{DDQ},$ or GND      | or GND - 100 100 |                    |       |

| Tstg Storage temperature             |                                                               | - 65             | 150                | °C    |

Note: Stress beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

#### **DC Specifications**

### **Recommended Operating Conditions**

| Symbol           | Parameter                                                                                   | Min.                           | Nom.     | Max.                           | Units |

|------------------|---------------------------------------------------------------------------------------------|--------------------------------|----------|--------------------------------|-------|

| $AV_{DD}$        | Analog/core supply voltage                                                                  | 2.3                            | 2.5      | 2.7                            |       |

| V <sub>DDQ</sub> | Output supply voltage                                                                       | 2.3                            | 2.5      | 2.7                            |       |

| $V_{ m IL}$      | Low-level input voltage for PWRDWN pin                                                      | -0.3                           | -0.3 0.7 |                                | V     |

| V <sub>IH</sub>  | High-level input voltage for PWRDWN pin                                                     | 1.7                            |          | V <sub>DDQ</sub> +0.3          |       |

| $V_{\rm I}$      | Input Voltage                                                                               | 0                              |          | V <sub>DDQ</sub>               |       |

| I <sub>OH</sub>  | High-level output current                                                                   | _                              |          | 12                             | mA    |

| $I_{OL}$         | Low-level output current                                                                    | _                              |          | -12                            | ША    |

| $V_{\rm IX}$     | Input differential-pair crossing voltage                                                    | $(V_{DDQ}/2) -0.2$             |          | (V <sub>DDQ</sub> /2) +0.2     |       |

| V <sub>OX</sub>  | Output differential-pair crossing voltage at the DRAM clock input                           | (V <sub>DDQ</sub> /2)<br>-0.15 |          | (V <sub>DDQ</sub> /2)<br>+0.15 |       |

| V <sub>IN</sub>  | Input voltage level                                                                         | -0.3                           |          | V <sub>DDQ</sub> +0.3          | V     |

| $V_{ m ID}$      | Input differential voltage between CLK and $\overline{\text{CLK}}$                          | 0.36                           |          | V <sub>DDQ</sub> +0.6          |       |

| V <sub>OD</sub>  | Output differential voltage between Y[n] & $\overline{Y[n]}$ and FBOUT & $\overline{FBOUT}$ | 0.7                            |          | V <sub>DDQ</sub> +0.6          |       |

| TA               | Operating free air temperature                                                              | 0                              |          | 70                             | °C    |

#### **Timing Requirements** (Over recommended operating free-air temperature)

| Symbol            | Description                                | AV <sub>DD</sub> , V <sub>DDQ</sub> | Units |       |  |

|-------------------|--------------------------------------------|-------------------------------------|-------|-------|--|

| Symbol            | Description                                | Min.                                | Max.  | Cints |  |

| r.                | Operating clock frequency <sup>(1,2)</sup> | 60                                  | 170   | MHz   |  |

| $f_{CK}$          | Application clock frequency(3)             | 95                                  | 170   |       |  |

| t <sub>DC</sub>   | Input clock duty cycle                     | 40                                  | 60    | %     |  |

| t <sub>STAB</sub> | PLL stabilization time after powerup       |                                     | 100   | μs    |  |

#### **Notes:**

- 1. The PLL is able to handle spread spectrum induced skew.

- 2. Operating clock frequency indicates a range over which the PLL is able to lock, but in which the clock is not required to meet the other timing parameters. (Used for low-speed debug).

- 3. Application clock frequency indicates a range over which the PLL meets all of the timing parameters.

#### **Electrical Characteristics**

| Parameter               |                                                            | Test Conditions                                                                | $A_{\mathrm{VDD}}, V_{\mathrm{DDQ}}$ | Min.      | Тур. | Max. | Units |

|-------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------|-----------|------|------|-------|

| V <sub>IK</sub>         | All inputs                                                 | $I_{\rm I} = -18 \rm mA$                                                       | 2.3V                                 |           |      | -1.2 |       |

| W.                      | High output voltage                                        | $I_{\mathrm{OH}} = -100 \mu\mathrm{A}$                                         | 2.3 to 2.7V                          | VDDQ- 0.1 |      |      |       |

| V <sub>OH</sub>         | rigii output voltage                                       | $I_{OH} = -12mA$                                                               | 2.3V                                 | 1.7       |      |      | V     |

| 17                      | Lovy output voltogo                                        | $I_{\rm OL} = 100 \mu A$                                                       | 2.3 to 2.7V                          |           |      | 0.1  |       |

| V <sub>OL</sub>         | Low output voltage                                         | $I_{OL} = 12mA$                                                                | 2.3V                                 |           |      | 0.6  |       |

| $I_{\mathrm{I}}$        | CLK, FBIN                                                  | $V_{\rm I} = V_{\rm DDQ}$ or GND                                               |                                      |           |      | ±10  |       |

|                         | PWRDWN                                                     | $V_{I} = V_{DDQ}$ or GND                                                       |                                      |           |      | ±10  | μA    |

| T                       | Dynamic supply current of V <sub>DDQ</sub>                 | $V_{\rm DD} = 2.7 \mathrm{V}$                                                  | 2.7V                                 |           |      | 300  | mA    |

| I <sub>DDQ</sub>        | Static supply current                                      | $\frac{\text{CLK \& }\overline{\text{CLK}}}{\text{PWRDWN}} = \text{Low}^{(4)}$ |                                      |           |      | 100  | μА    |

|                         | Dynamic supply current of AV <sub>DD</sub>                 | $V_{\rm DD} = 2.7 \mathrm{V}$                                                  |                                      |           |      | 12   | mA    |

| $I_{ADD}$               | Static supply current                                      | $\frac{\text{CLK \& }\overline{\text{CLK}}}{\text{PWRDWN}} = \text{Low}^{(4)}$ |                                      |           |      | 100  | μА    |

| C                       | CLK and CLK                                                | V = V or CND                                                                   | 2.51/                                | 2.0       |      | 3.5  |       |

| $C_{I}$                 | FBIN and FBIN                                              | $V_{\rm I} = V_{\rm DDQ}$ or GND                                               | 2.5V                                 |           |      |      |       |

| C                       | CLK and CLK                                                | W - W - CND                                                                    | 2.511                                | 0.25      |      | 0.25 | рF    |

| $C_{I(\Delta)}$         | FBIN and FBIN                                              | $V_{\rm I} = V_{\rm DDQ}$ or GND                                               | 2.5V                                 | -0.25     |      | 0.25 | P.    |

| $\Delta C_{\mathrm{I}}$ | Part to Part input Capacitance<br>Variation <sup>(5)</sup> | $V_{I} = V_{DDQ}$ or GND                                                       | 2.5V                                 |           |      | 1    |       |

#### Note:

- 4. The maximum power-down clock frequency is below 20 MHz.

- 5. Guaranteed by design, but not production tested.

#### **AC Specifications**

Switching characteristics over recommended operating free-air temperature range (unless otherwise noted)( See Figure 1 & 2 )

| Downwater                                       | Description                            | Diagram                | AV <sub>CC</sub> , | T Inaida      |                  |         |

|-------------------------------------------------|----------------------------------------|------------------------|--------------------|---------------|------------------|---------|

| Parameter                                       |                                        |                        | Min.               | Nom.          | Max              | Units   |

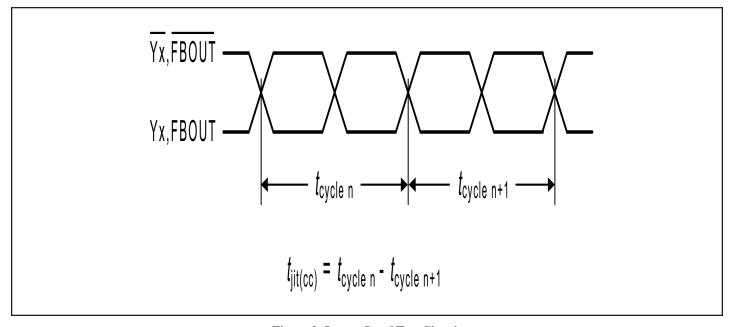

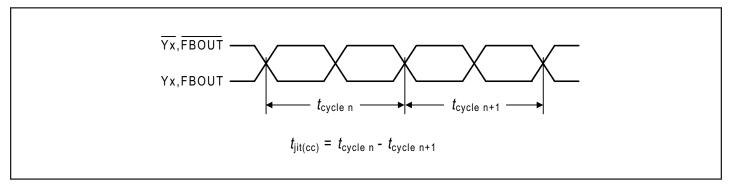

| tjit(cc)                                        | Cycle-to-cycle jitter                  | see Figure 3           | -75                |               | 75               |         |

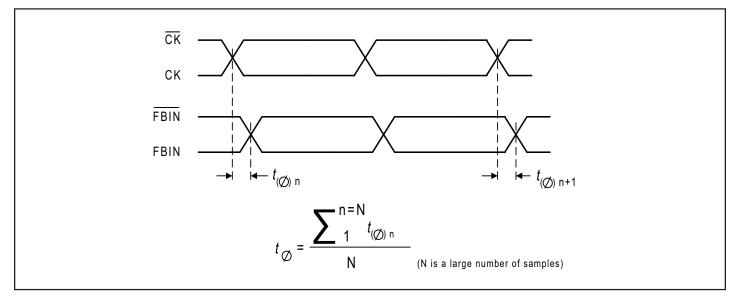

| t(0)                                            | Static phase offset <sup>(1)</sup>     | see Figure 4           | -50                | 0             | 50               |         |

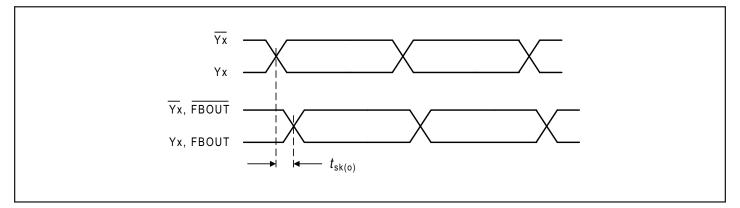

| tsk(o)                                          | Output clock skew                      | see Figure 5           |                    |               | 100              | ps      |

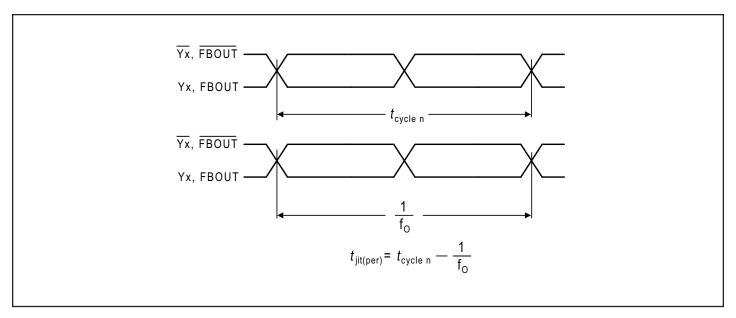

| tjit(per)                                       | Period jitter                          | see Figure 6           | -75                |               | 75               |         |

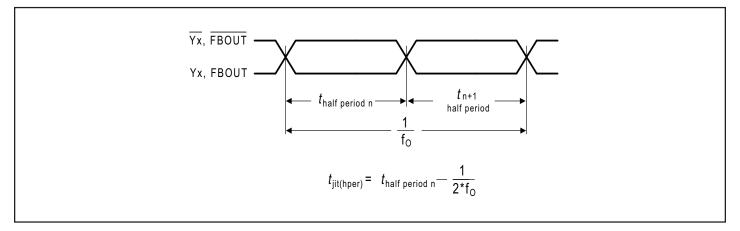

| tjit(hper)                                      | Half-period jitter                     | see Figure 7           | -100               |               | 100              |         |

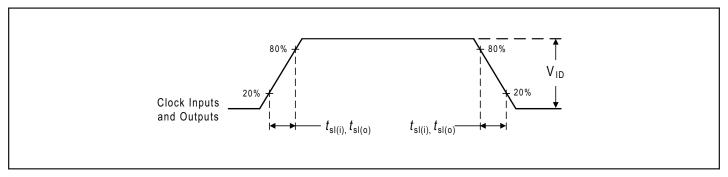

| tsl(i)                                          | Input clock slew rate <sup>(2)</sup>   | see Figure 8           | 1.0                |               | 4.0              | 37/     |

| tsl(o)                                          | Output clock slew rate <sup>(2)</sup>  | see Figure 8           | 1.0                |               | 2.0              | - V/ns  |

| The PLL on the PI60 parameters <sup>(3)</sup> . | CV857L is capable of meeting all the a | above parameters while | supporting SS      | C synthesizer | s with the follo | wing    |

|                                                 | SSC modulation frequency               |                        | 30.00              |               | 50.00            | kHz     |

|                                                 | SSC clock input frequency deviation    | n                      | 0.00               |               | -0.50            | %       |

|                                                 | PLL loop bandwidth                     |                        | 2                  |               |                  | MHz     |

|                                                 | Phase angle                            |                        |                    |               | -0.031           | degrees |

#### **Notes:**

- 1. Static Phase offset does not include Jitter.

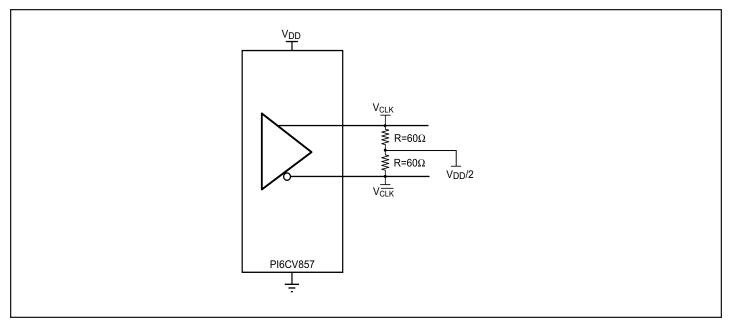

- 2. The slew rate is determined from the IBIS model with test load shown in Figure 1.

- $3. \, The \, SSC \, requirements \, meet \, the \, Intel \, PC100 \, SDRAM \, Registered \, DIMM \, specification.$

......

Figure 1. IBIS Model Output Load

Figure 2. Output Load Test Circuit

Figure 3. Cycle-to-Cycle Jitter

Figure 4. Static Phase Offset

Figure 5. Output Skew

09-0025 7 PS8543D 08/17/09

Figure 6. Period Jitter

Figure 7. Half-Period Jitter

Figure 8. Input and Output Slew Rates

09-0025 8 PS8543D 08/17/09

#### Packaging Mechanical: 48-Pin TSSOP

#### **Ordering Information**

| Ordering Code | Package Code | Package Description                       |

|---------------|--------------|-------------------------------------------|

| PI6CV857LA    | A            | 48-pin 240-mil wide TSSOP                 |

| PI6CV857LAE   | A            | Pb-free & Green 48-pin 240-mil wide TSSOP |

- 1. PackageThermal characteristics can be found on the company web site at www.pericom.com/packaging/

- 2. E = Pb-free and Green