Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## 3-Output LVPECL Networking Clock Generator

#### **Features**

- → Three differential LVPECL output pairs

- → Selectable crystal oscillator interface or LVCMOS/LVTTL single-ended clock input

- → Supports the following output frequencies: 125MHz, 156.25MHz, 312.5MHz, 625MHz

- → RMS phase jitter @ 156.25MHz, using a 31.25MHz or 26.041666MHz crystal (12kHz 20MHz): 0.3ps (typical)

- → Full 3.3V or 2.5V supply modes

- → Industrial operating temperature

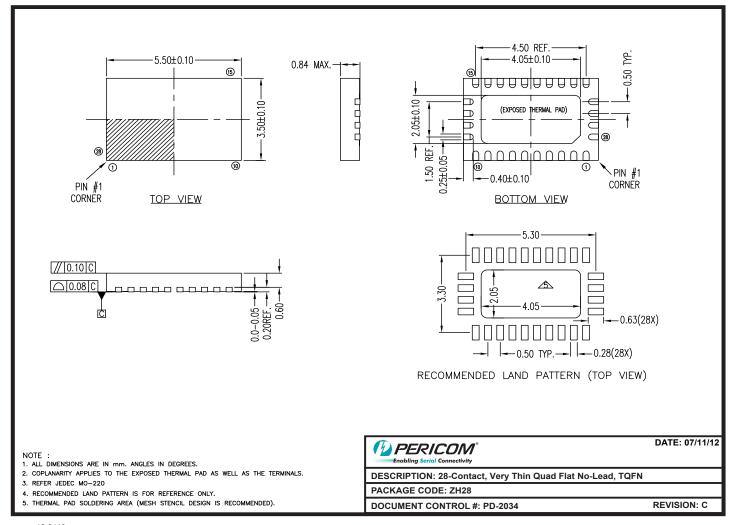

- → Available in lead-free package: 28-TQFN

## **Description**

The PI6LC48P03A is a 3-output LVPECL synthesizer optimized to generate Ethernet reference clock frequencies and is a member of Pericom's HiFlex family of high performance clock solutions. Using a 31.25MHz or 26.041666MHz crystal, the most popular Ethernet frequencies can be generated based on the settings of 4 frequency select pins.

The PI6LC48P03A uses Pericom's proprietary low phase noise PLL technology to achieve ultra low phase jitter, so it is ideal for Ethernet interface in all kind of systems.

## **Applications**

→ Networking systems

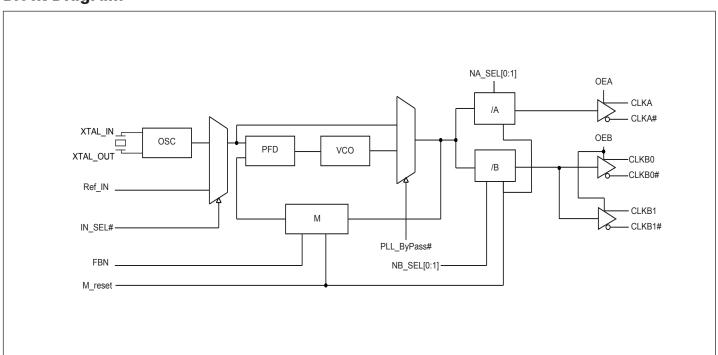

## **Block Diagram**

15-0119 1 www.pericom.com PI6LC48P03A Rev. A 6/9/2015

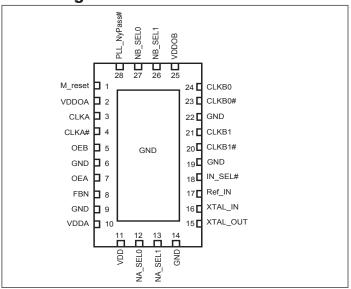

## **Pin Configuration**

## **Pinout Table**

| Pin No.             | Pin Name             | I/O Type |           | Description                                                                                         |

|---------------------|----------------------|----------|-----------|-----------------------------------------------------------------------------------------------------|

| 1                   | M_reset              | Input    | Pull-down | Master Reset. When HIGH, CLKx goes to "low" and CLKx# goes to "high"; When LOW outputs are enabled. |

| 2                   | VDDOA                | Power    |           | Bank A Output Power Supply                                                                          |

| 3,<br>4             | CLKA, CLKA#          | Output   |           | Bank A LVPECL Output Clock                                                                          |

| 5                   | OEB                  | Input    | Pull-up   | Bank B Output Enable. When LOW, output is differential low.                                         |

| 6, 9, 14,<br>19, 22 | GND                  | Ground   |           | Ground                                                                                              |

| 7                   | OEA                  | Input    | Pull-up   | Bank A Output Enable. When LOW, output is differential low.                                         |

| 8                   | FBN                  | Input    | Pull-down | Feedback Divider Select                                                                             |

| 10                  | VDDA                 | Power    |           | Analog Power Supply                                                                                 |

| 11                  | VDD                  | Power    |           | Core Power Supply                                                                                   |

| 12, 13              | NA_SEL0, NA_<br>SEL1 | Input    | Pull-up   | Bank A Output Divider Select                                                                        |

| 15, 16              | XTAL_OUT,<br>XTAL_IN | Crystal  |           | Crystal Input and Output                                                                            |

| 17                  | Ref_IN               | Input    | Pull-down | CMOS Reference Clock Input                                                                          |

| 18                  | IN_SEL#              | Input    | Pull-up   | When HIGH, Crystal is selected; When LOW, reference input is selected.                              |

| Pin No. | Pin Name            | I/O Type |         | Description                  |

|---------|---------------------|----------|---------|------------------------------|

| 20, 21  | CLKB1#,<br>CLKB1    | Output   |         | Bank B LVPECL Output Clock 1 |

| 23, 24  | CLKB0#,<br>CLKB0    | Output   |         | Bank B LVPECL Output Clock 0 |

| 25      | VDDOB               | Power    |         | Bank B Output Power Supply   |

| 26, 27  | NB_SEL1,<br>NB_SEL0 | Input    | Pull-up | Bank B Output Divider Select |

| 28      | PLL_ByPass#         | Input    | Pull-up | Active Low PLL Bypass        |

## **Output Frequency Selection Table**

| Xtal Frequency<br>(MHz) | NA_SEL1 / NB_<br>SEL1 | NA_SEL0 / NB_<br>SEL0 | FBN | Output Frequency (MHz)  |

|-------------------------|-----------------------|-----------------------|-----|-------------------------|

| 31.25                   | 0                     | 0                     | 0   | 625                     |

| 31.25                   | 0                     | 1                     | 0   | 312.5 (Bank A Default)  |

| 31.25                   | 1                     | 0                     | 0   | 156.25 (Bank B Default) |

| 31.25                   | 1                     | 1                     | 0   | 125                     |

| 26.041666               | 0                     | 0                     | 1   | 625                     |

| 26.041666               | 0                     | 1                     | 1   | 312.5 (Bank A Default)  |

| 26.041666               | 1                     | 0                     | 1   | 156.25 (Bank B Default) |

| 26.041666               | 1                     | 1                     | 1   | 125                     |

## **Typical Crystal Requirement**

| Parameter                          |         | Minimum | Typical     | Maximum | Units |  |  |

|------------------------------------|---------|---------|-------------|---------|-------|--|--|

| Mode of Oscillation                |         |         | Fundamental |         |       |  |  |

| Engavonav                          | FBN = 0 | 28      | 31.25       | 35      | MHz   |  |  |

| Frequency                          | FBN = 1 | 23.33   | 26.04166    | 29.167  | MHz   |  |  |

| Equivalent Series Resistance (ESR) |         |         |             | 50      | Ω     |  |  |

| Shunt Capacitance                  |         |         |             | 7       | pF    |  |  |

| Drive I                            | Level   |         |             | 1       | mW    |  |  |

## **Recomended Crystal Specification**

Pericom recommends:

a) FY3120001, SMD 5x3.2(4P), 31.25MHz, CL=18pF, +/-20ppm http://www.pericom.com/pdf/datasheets/se/FY\_F9.pdf

b) FL2600155, SMD 3.2x2.5(4P), 26.041666MHz, CL18pF, +/-20ppm https://www.pericom.com/assets/Datasheets/FL.pdf

15-0119 3 www.pericom.com PI6LC48P03A Rev. A 6/9/2015

### **Maximum Ratings** (Over operating free-air temperature range)

| Storage Temperature6           | 55°C to+155°C |

|--------------------------------|---------------|

| Temperature with Power Applied | 40°C to+85°C  |

| 3.3V Supply Voltage            | 0.5 to +3.6V  |

| ESD Protection (HBM)           | 2000V         |

#### Note

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **DC Electrical Characteristics**

Power Supply DC Characterisitcs,  $(T_A = -40 \text{ to } 85^{\circ}\text{C})$

| Symbol                                   | Parameter             | Condition | Min   | Тур | Max   | Units |

|------------------------------------------|-----------------------|-----------|-------|-----|-------|-------|

| $V_{\mathrm{DD}}$                        | Core Supply Voltage   |           | 3.135 | 3.3 | 3.465 | V     |

| $V_{\mathrm{DDA}}$                       | Analog Supply Voltage |           | 3.135 | 3.3 | 3.465 | V     |

| V <sub>DDO_A</sub><br>V <sub>DDO_B</sub> | Output Supply Voltage |           | 3.135 | 3.3 | 3.465 | V     |

| $V_{\mathrm{DD}}$                        | Core Supply Voltage   |           | 2.375 | 2.5 | 2.625 | V     |

| $V_{\mathrm{DDA}}$                       | Analog Supply Voltage |           | 2.375 | 2.5 | 2.625 | V     |

| V <sub>DDO_A</sub><br>V <sub>DDO_B</sub> | Output Supply Voltage |           | 2.375 | 2.5 | 2.625 | V     |

| I <sub>GND</sub>                         | Power Supply Current  |           |       |     | 132   | mA    |

| $I_{\mathrm{DDA}}$                       | Analog Supply Current |           |       |     | 30    | mA    |

## $\underline{\text{LVCMOS/LVTTL DC Characterisitcs,}}$ (T<sub>A</sub> = -40 to 85°C)

| Symbol          | Parameter          |                                                           | Condition                                                      | Min  | Тур | Max                   | Units |

|-----------------|--------------------|-----------------------------------------------------------|----------------------------------------------------------------|------|-----|-----------------------|-------|

| 3.7             | x                  |                                                           | V <sub>DD</sub> = 3.3 V +/- 5%                                 | 2    |     | V <sub>DD</sub> + 0.3 | V     |

| $V_{IH}$        | Input High Voltage |                                                           | V <sub>DD</sub> = 2.5 V +/- 5%                                 | 1.7  |     | V <sub>DD</sub> + 0.3 |       |

| 3.7             | T T W-14           |                                                           | V <sub>DD</sub> = 3.3 V +/- 5%                                 | -0.3 |     | 0.8                   | V     |

| V <sub>IL</sub> | Input Low Voltage  |                                                           | V <sub>DD</sub> = 2.5 V +/- 5%                                 | -0.3 |     | 0.7                   | V     |

|                 |                    | Ref_IN, FBN, M_reset,<br>NA_SEL1, NB_SEL0                 | $V_{\rm DD} = V_{\rm IN} = 3.465 V$                            |      |     | 100                   | μΑ    |

| $I_{IH}$        | Input High Current | OEA, OEB, PLL_By-<br>pass#, IN_SEL#, NB_<br>SEL1, NA_SEL0 | $V_{\rm DD} = V_{\rm IN} = 3.465 V$                            |      |     | 5                     | μΑ    |

|                 |                    | Ref_IN, FBN, M_reset,<br>NA_SEL1, NB_SEL0                 | $V_{_{\rm DD}} = 3.465 \text{V}, \ V_{_{\rm IN}} = 0 \text{V}$ | -5   |     |                       | μΑ    |

| I <sub>IL</sub> | Input Low Current  | OEA, OEB, PLL_By-<br>pass#, IN_SEL#, NB_<br>SEL1, NA_SEL0 | $V_{\rm DD} = 3.465 \text{V},$ $V_{\rm IN} = 0 \text{V}$       | -100 |     |                       | μΑ    |

### **LVPECL DC Characterisitcs,** $(T_A = -40 \text{ to } 85^{\circ}\text{C})$

| Symbol          | Parameter                         | Condition            | Min | Тур | Max | Units |

|-----------------|-----------------------------------|----------------------|-----|-----|-----|-------|

| 3.7             | Output High Waltage(I)            | $V_{DD} = 3.3V$      | 1.9 |     | 2.4 | 17    |

| V <sub>OH</sub> | Output High Voltage(1)            | $V_{\rm DD} = 2.5 V$ | 1.1 |     | 1.6 | V     |

| 3.7             | O-tt I V-1t(1)                    | $V_{DD} = 3.3V$      | 1.2 |     | 1.6 | 3.7   |

| Vol             | Output Low Voltage <sup>(1)</sup> | $V_{\rm DD} = 2.5 V$ | 0.4 |     | 0.8 | V     |

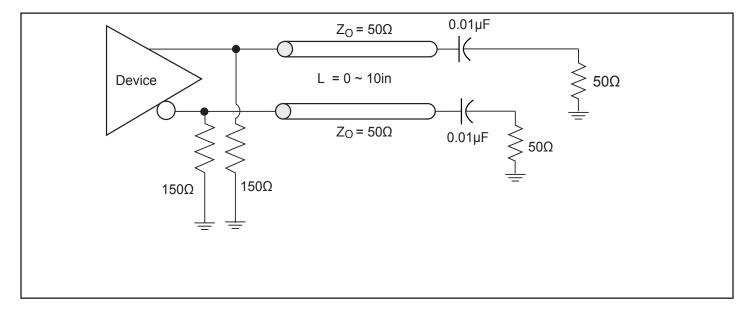

Note: 1. LVPECL Termination: Source 150ohm to GND and 100ohm across CLK and CLK#.

## AC Electrical Characteristics ( $T_A = -40 \text{ to } 85^{\circ}\text{C}$ )

LVPECL Termination: Source 150ohm to GND and using 0.01uF ac-coupled to 50ohm to GND

| Symbol                          | Parameter                    | Condition                                                                                          | Min. | Тур. | Max | Units |

|---------------------------------|------------------------------|----------------------------------------------------------------------------------------------------|------|------|-----|-------|

|                                 |                              | NA_SEL[1:0] / NB_SEL[1:0] = 00                                                                     | 560  |      | 700 | MHz   |

| C                               |                              | NA_SEL[1:0] / NB_SEL[1:0] = 01                                                                     | 280  |      | 350 | MHz   |

| $f_{OUT}$                       | Output Frequency             | NA_SEL[1:0] / NB_SEL[1:0] = 10                                                                     | 140  |      | 175 | MHz   |

|                                 |                              | NA_SEL[1:0] / NB_SEL[1:0] = 11                                                                     | 112  |      | 140 | MHz   |

| $t_{ m sk(B)}$                  | Output Skew <sup>(1)</sup>   | NA_SEL[1:0] / NB_SEL[1:0] = 00<br>NA_SEL[1:0] / NB_SEL[1:0] = 01<br>NA_SEL[1:0] / NB_SEL[1:0] = 10 |      |      | 30  | ps    |

| ,                               |                              | Output @ Same Frequencies                                                                          |      |      | 60  | ps    |

| $t_{ m sk(o)}$                  | Output Skew <sup>(2,4)</sup> | Output @ Different Frequencies                                                                     |      |      | 75  | ps    |

|                                 |                              | •                                                                                                  |      | 0.15 |     | ps    |

|                                 | RMS Phase Jitter,            | •                                                                                                  |      | 0.3  |     | ps    |

|                                 |                              |                                                                                                    |      | 0.15 |     | ps    |

|                                 |                              |                                                                                                    |      | 0.3  |     | ps    |

| $t_{ m jit}(\emptyset)$         | (Random) <sup>(3)</sup>      | 156.25MHz,<br>(1.875MHz - 20MHz)                                                                   |      | 0.15 |     | ps    |

|                                 |                              | 156.25MHz,<br>(12kHz - 20MHz)                                                                      |      | 0.3  |     | ps    |

|                                 |                              | 125MHz,<br>(1.875MHz - 20MHz)                                                                      |      | 0.15 |     | ps    |

|                                 |                              | 125MHz,                                                                                            |      |      |     |       |

|                                 |                              | (12kHz - 20MHz)                                                                                    |      | 0.3  |     | ps    |

| t <sub>R</sub> / t <sub>F</sub> | Output Rise/Fall Time        | 20% to 80%                                                                                         |      |      | 400 | ps    |

| O <sub>DC</sub>                 | Output Duty Cycle (5)        |                                                                                                    | 48   |      | 52  | %     |

#### Note:

- 1. Defined as skew within a bank of outputs at the same supply voltage and with equal load conditions.

- 2. Defined as skew between outputs at the same supply voltage and with equal load conditions. Measured at the differential cross points.

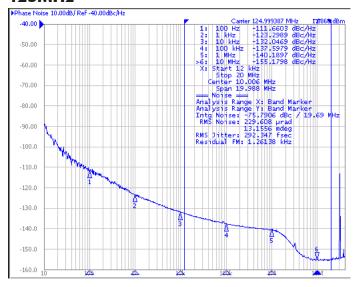

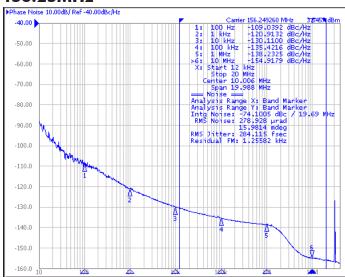

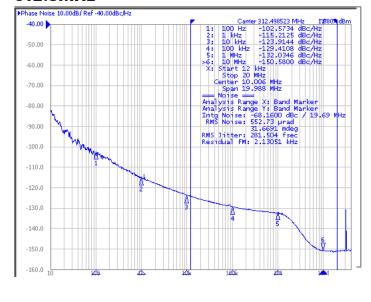

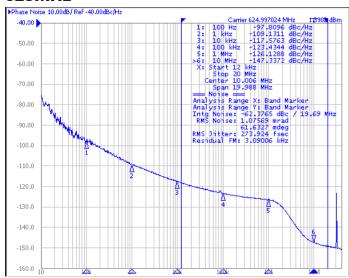

- **3.** Please refer to the Phase Noise Plots.

- 4. This parameter is defined in accordance with JEDEC Standard 65. Measured at the differential cross points.

- **5.** Measured at the differential cross points.

15-0119 5 www.pericom.com PI6LC48P03A Rev. A 6/9/2015

#### **LVPECL Test Circuit**

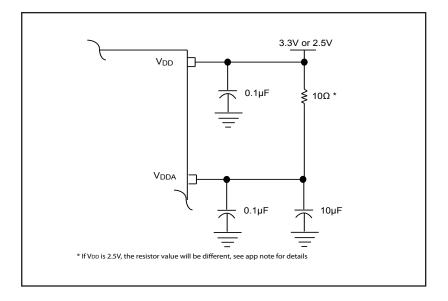

### **Power Supply Filtering Techniques**

As in any high speed analog circuitry, the power supply pins are vulnerable to random noise. To achieve optimum jitter performance, power supply isolation is required. The PI6LC48P03A provides separate power supplies to isolate any high switching noise from the outputs to the internal PLL.  $V_{DD}$ ,  $V_{DDA}$  and  $V_{DDO}$  should be individually connected to the power supply plane through vias, and  $0.1\mu F$  bypass capacitors should be used for each pin. Figure below illustrates this for a generic  $V_{DD}$  pin and also shows that  $V_{DDA}$  requires that an additional  $10\Omega$  resistor along with a  $10\mu F$  bypass capacitor be connected to the  $V_{DDA}$  pin.

### **Recommendations for Unused Input and Output Pins**

#### Inputs:

Crystal Inputs:

For applications not requiring the use of the crystal oscillator input, both XTAL\_IN and XTAL\_OUT can be left floating. A  $1k\Omega$  resistor can be tied from XTAL\_IN to ground for additional protection.

Ref\_IN Input:

For applications not requiring the use of the clock, it can be left floating. A  $1k\Omega$  resistor tied from the Ref\_IN to ground can provide additional protection.

LVCMOS Control Pins:

All control pins have internal pulldowns/pullups; A  $1k\Omega$  resistor tied from internal pulldown control pins to ground, and a  $4.7k\Omega$  tied from internal pullup control pins to power supply can provide additional protection.

#### **Outputs:**

LVPECL Outputs:

All unused LVPECL outputs can be left floating.

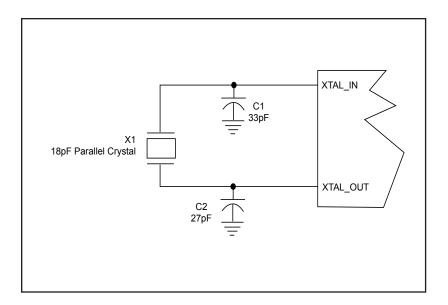

### **Crystal Input Interface**

The clock generator has been characterized with 18pF parallel resonant crystals. The capacitor values shown in the figure below were determined using a 31.25MHz or 26.041666MHz, 18pF parallel resonant crystal and were chosen to minimize the ppm error.

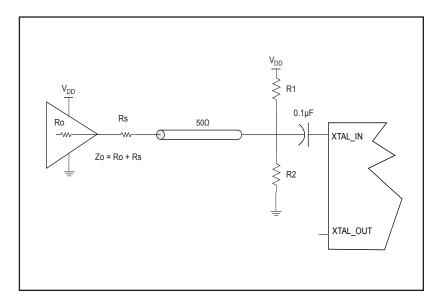

### **LVCMOS to XTAL Interface**

The XTAL\_IN input can accept a single-ended LVCMOS signal through an AC coupling capacitor. A general interface diagram is shown in the figure below. The XTAL\_OUT pin can be left floating. The input edge rate can be as slow as 10ns. For LVCMOS signals, it is recommended that the amplitude be reduced from full swing to half swing in order to prevent signal interference with the power rail and to reduce noise. This configuration requires that the output impedance of the driver (Ro) plus the series resistance (Rs) equals the transmission line impedance. In addition, matched termination at the crystal input will attenuate the signal in half. This can be done in one of the two ways. First, R1 and R2 in parallel should equal the transmission line empedance. For most  $50\Omega$  applications, R1 and R2 can be  $100\Omega$ . This can also be accomplished by removing R1 and making R2  $50\Omega$ . By overdriving the crystal oscillator, the device will be functional, but note, the device performance is quaranteed by using a quartz crystal.

### **Phase Noise Plots**

#### 125MHz

#### 156.25MHz

#### 312.5MHz

#### 625MHz

### **Thermal Information**

| Symbol                                                           | Description                         |            |

|------------------------------------------------------------------|-------------------------------------|------------|

| $\Theta_{_{\mathrm{JA}}}$ Junction-to-ambient thermal resistance |                                     | 41.68 °C/W |

| $\Theta_{ m JC}$                                                 | Junction-to-case thermal resistance | 23.78 °C/W |

## Packaging Mechanical: 28-Contact TQFN (ZH)

# Ordering Information

| Ordering Code    | Packaging<br>Type | Package Description                       | Operating Temperature |

|------------------|-------------------|-------------------------------------------|-----------------------|

| PI6LC48P03AZHIE  | ZH                | Pb-free & Green, 28-pin TQFN              | Industrial            |

| PI6LC48P03AZHIEX | ZH                | Pb-free & Green, 28-pin TQFN, Tape & reel | Industrial            |

#### Notes:

- Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- "E" denotes Pb-free and Green

- Adding an "X" at the end of the ordering code denotes tape and reel packaging

Pericom Semiconductor Corporation • 1-800-435-2336 • www.pericom.com