# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### Dual bidirectional I<sup>2</sup>C-bus and SMBus voltage-level translator

#### Features

- 2-bit bidirectional translator for SDA and SCL lines in mixed-mode I<sup>2</sup>C-bus applications

- Standard-mode, Fast-mode, and Fast-mode Plus I<sup>2</sup>C-bus and SMBus compatible

- Less than 1.5 ns maximum propagation delay to accommodate Standard mode and Fast mode I<sup>2</sup>C-bus devices and multiple masters

- Allows voltage level translation between:

- ▷ 0.9V VREF1 and 1.8 V, 2.5 V, 3.3 V or 5 V VREF2

- 1.2 V VREF1 and 1.8 V, 2.5 V, 3.3 V or 5 V VREF2

- > 1.5 V VREF1 and 2.5 V, 3.3 V or 5 V VREF2

- ▶ 1.8 V VREF1 and 3.3 V or 5 V VREF2

- ➤ 2.5 V VREF1 and 5 V VREF2

- > 3.3 V VREF1 and 5 V VREF2

- Provides bidirectional voltage translation with no direction pin

- Low 3.5 ohm ON-state connection between input and output ports provides less signal distortion

- Open-drain I<sup>2</sup>C-bus I/O ports (SCL1, SDA1, SCL2 and SDA2)

- 5 V tolerant I<sup>2</sup>C-bus I/O ports to support mixedmode signal operation

- High-impedance SCL1, SDA1, SCL2 and SDA2 pins for EN = LOW

- Lock-up free operation for isolation when EN = LOW

- Flow through pin out for ease of printed-circuit board trace routing

- ESD protection exceeds 4KV HBM per JESD22-A114

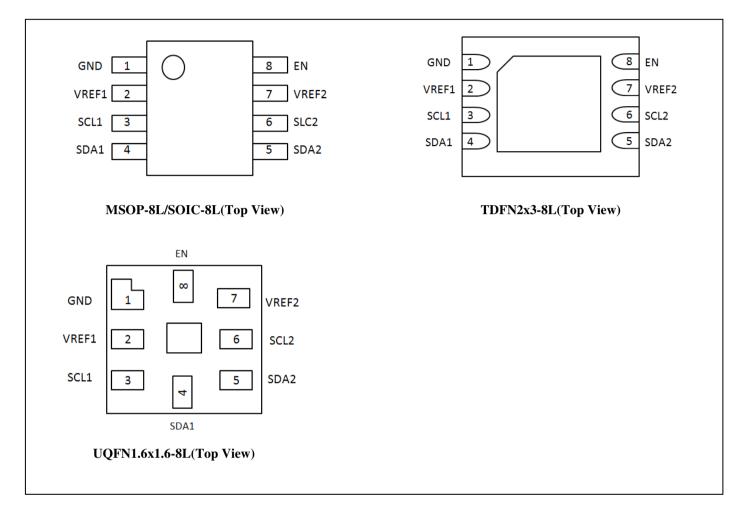

- Package: TDFN2x3-8L, MSOP-8L, SOIC-8L, UDFN1.6x1.6-8L

## Description

The PI6ULS5V9306 is a dual bidirectional  $I^2$ C-bus and SMBus voltage-level translator with an enable (EN) input, and is operational from 1.0 V to 3.3 V (VREF1) and 1.8 V to 5.5 V(VREF2).

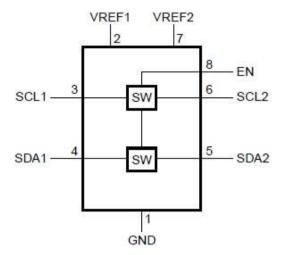

The PI6ULS5V9306 allows bidirectional voltage translations between 1.0 V and 5 V without the use of a direction pin. The low ON-state resistance (Ron) of the switch allows connections to be made with minimal propagation delay. When EN is HIGH, the translator switch is on, and the SCL1 and SDA1 I/O are connected to the SCL2 and SDA2 I/O respectively, allowing bidirectional data flow between ports. When EN is LOW, the translator switch is off, and a high-impedance state

exists between ports.

The PI6UL\$5V9306 is not a bus buffer that provides both level translation and physically isolates to either side of the bus when both sides are connected. The PI6UL\$5V9306 only isolates both sides when the device is disabled and provides voltage level translation when active.

The PI6ULS5V9306 can also be used to run two buses, one at 400 kHz operating frequency and the other at 100 kHz operating frequency. If the two buses are operating at different frequencies, the 100 kHz bus must be isolated when the 400 kHz operation of the other bus is required. If the master is running at 400 kHz, the maximum system operating frequency may be less than 400 kHz because of the delays added by the translator.

As with the standard  $I^2C$ -bus system, pull-up resistors are required to provide the logic HIGH levels on the translator's bus. The PI6ULS5V9306 has a standard open-collector configuration of the  $I^2C$ -bus. The size of these pull-up resistors depends on the system, but each side of the translator must have a pull-up resistor. The device is designed to work with Standardmode, Fast-mode and Fast mode Plus  $I^2C$ -bus devices in addition to SMBus devices.

When the SDA1 or SDA2 port is LOW, the clamp is in the ON-state and a low resistance connection exists between the SDA1 and SDA2 ports. When the higher voltage is on the SDA2 port, and the SDA2 port is HIGH, the voltage on the SDA1 port is limited to the voltage set by VREF1. When the SDA1 port is HIGH, the SDA2 port is pulled to the drain pull-up supply voltage (VDPU) by the pull-up resistors. This functionality allows a seamless translation between higher and lower voltages selected by the user without the need for directional control. The SCL1/SCL2 channel also functions as the SDA1/SDA2 channel.

All channels have the same electrical characteristics and there is minimal deviation from one output to another in voltage or propagation delay. This is a benefit over discrete transistor voltage translation solutions, since the fabrication of the switch is symmetrical. The translator provides excellent ESD protection to lower voltage devices, and at the same time protects less ESDresistant devices.

## **Pin Configuration**

#### **Pin Description**

| Pin No | Name  | Description                                                                  |

|--------|-------|------------------------------------------------------------------------------|

| 1      | GND   | ground (0 V)                                                                 |

| 2      | VREF1 | low-voltage side reference supply voltage for SCL1 and SDA1                  |

| 3      | SCL1  | serial clock, low-voltage side; connect to VREF1 through a pull-up resistor  |

| 4      | SDA1  | serial data, low-voltage side; connect to VREF1 through a pull-up resistor   |

| 5      | SDA2  | serial data, high-voltage side; connect to VREF2 through a pull-up resistor  |

| 6      | SCL2  | serial clock, high-voltage side; connect to VREF2 through a pull-up resistor |

| 7      | VREF2 | high-voltage side reference supply voltage for SCL2 and SDA2                 |

| 8      | EN    | switch enable input; connect to VREF2 and pull-up through a high resistor    |

A Product Line of Diodes Incorporated

## **Block Diagram**

| EN | Function                    |

|----|-----------------------------|

| Н  | SCL1 = SCL2;<br>SDA1 = SDA2 |

| L  | disabled                    |

#### Figure.1Block Diagram

## **Maximum Ratings**

| Storage Temperature              | 65°C to +150°C |

|----------------------------------|----------------|

| Reference Voltage <sup>(2)</sup> |                |

| Reference bias voltage           | 0.5V to+6.0V   |

| DC Input Voltage                 |                |

| Control Input Votage(EN)         | 0.5V to+6.0V   |

| channel current (DC)             |                |

| Input clamping Current           | 50mA           |

| ESD: HBM Mode                    |                |

|                                  |                |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Recommended operation conditions**

Vcc = 2.7 V to 5.5 V;  $\overline{\text{GND}}$  = 0 V;  $T_{\text{A}}$  = -40 °C to +85 °C; unless otherwise specified

| Symbol              | Parameter                      | Test Conditions        | Min. | Тур. | Max. | Unit |

|---------------------|--------------------------------|------------------------|------|------|------|------|

| V <sub>I/O</sub>    | Voltage on an input/output pin | SCL1, SDA1, SCL2, SDA2 | 0    | -    | 5    | V    |

| $V_{REF1}$          | Reference voltage (1)          | VREF1                  | 0    | -    | 5    | V    |

| V <sub>REF2</sub>   | Reference bias voltage (2)     | VREF2                  | 0    | -    | 5    | V    |

| V <sub>I(EN)</sub>  | Input voltage on pin EN        | -                      | 0    | -    | 5    | V    |

| I <sub>(pass)</sub> | Pass switch current            | -                      | -    | -    | 64   | mA   |

| T <sub>A</sub>      | Ambient temperature            | -                      | -40  | -    | 85   | °C   |

## **DC Electrical Characteristics**

$T_A = -40 \text{ °C to } +85 \text{ °C}$ ; unless otherwise specified

| Parameter            | Description                                        | Test C                                           | onditions <sup>(1)</sup> | Min | <b>Typ.</b> <sup>(2)</sup> | Max  | Unit |

|----------------------|----------------------------------------------------|--------------------------------------------------|--------------------------|-----|----------------------------|------|------|

| Input and outp       | out SDAB and SCLB                                  |                                                  |                          | -   | -                          |      |      |

| V <sub>IK</sub>      | input clamping voltage                             | $I_{I} = -18 \text{mA}; V_{I(EN)} = 0 \text{ V}$ |                          | -   | -                          | -1.2 | V    |

| I <sub>IH</sub>      | HIGH-level input current                           | $V_{I} = 5 V; V_{I(EN)}$                         | = 0 V                    | -   | -                          | 5    | μA   |

| C <sub>i(EN)</sub>   | input capacitance on pin EN                        | $V_{I} = 3 V \text{ or } 0 V$                    |                          | -   | 11                         | -    | pF   |

| C <sub>io(off)</sub> | off-state input/output capacitance<br>(SCLn, SDAn) | $V_0 = 3 V \text{ or } 0 V; V_{I(EN)} = 0 V$     |                          | -   | 4                          | -    | pF   |

| C <sub>io(on)</sub>  | on-state input/output capacitance<br>(SCLn, SDAn)  | $V_{O} = 3 V \text{ or } 0 V; V_{I(EN)} = 3 V$   |                          | -   | 10.5                       | -    | pF   |

|                      |                                                    |                                                  | $V_{I(EN)} = 4.5 V$      | -   | 3.5                        | 5.5  | Ω    |

|                      |                                                    | $V_{I} = 0V;$                                    | $V_{I(EN)} = 3 V$        | -   | 4.7                        | 7.0  | Ω    |

|                      |                                                    | $I_0 = 64mA$                                     | $V_{I(EN)} = 2.3 V$      | -   | 6.3                        | 9.5  | Ω    |

| Ron                  | ON-state resistance <sup>(2)</sup>                 |                                                  | $V_{I(EN)} = 1.5 V$      | -   | 60                         | 140  | Ω    |

|                      | (SCLn, SDAn)                                       | $V_{I} = 2.4 V; I_{O}$                           | $V_{I(EN)} = 4.5 V$      | 1   | 6                          | 15   | Ω    |

|                      |                                                    | = 15mA                                           | $V_{I(EN)} = 3 V$        | 20  | 60                         | 140  | Ω    |

|                      |                                                    | $V_{I} = 1.7V;$<br>$I_{O} = 15mA$                | $V_{I(EN)} = 2.3 V$      | 20  | 60                         | 140  | Ω    |

Notes:

1) All typical values are at  $T_A = 25$  °C. 2) Measured by the voltage drop between the SCL1 and SCL2, or SDA1 and SDA2 terminals at the indicated current through the switch. ON-state resistance is determined by the lowest voltage of the two terminals.

## **Dynamic characteristics**

$T_A = -40$  °C to +85 °C; unless otherwise specified. Values guaranteed by design.

| Symbol            | Parameter                                                                                                                                    | Conditions                                                                                                         | C <sub>L</sub> = | 50 pF | C <sub>L</sub> = | $C_L = 30 \text{ pF}$ |     | C <sub>L</sub> = 15 pF |      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------|-------|------------------|-----------------------|-----|------------------------|------|

| Symbol            | rarameter                                                                                                                                    | Conditions                                                                                                         | Min              | Max   | Min              | Max                   | Min | Max                    | Unit |

| Dynamic           | Dynamic characteristics (translating down)                                                                                                   |                                                                                                                    |                  |       |                  |                       |     |                        |      |

| $V_{I(EN)} = 3.3$ | $V; V_{IH} = 3.3 V; V_{IL} =$                                                                                                                | $= 0 \text{ V}; \text{ V}_{\text{M}} = 1.15 \text{ V}$                                                             |                  |       |                  |                       |     |                        |      |

| t <sub>PLH</sub>  | LOW-to-HIGH propagation delay                                                                                                                | from (input) SCL2 or SDA2<br>to (output) SCL1 or SDA1                                                              | 0                | 0.8   | 0                | 0.6                   | 0   | 0.3                    | ns   |

| t <sub>PHL</sub>  | HIGH-to-LOW<br>propagation delay                                                                                                             | from (input) SCL2 or SDA2<br>to (output) SCL1 or SDA1                                                              | 0                | 1.2   | 0                | 1                     | 0   | 0.5                    | ns   |

| $V_{I(EN)} = 2.5$ | $V_{I(EN)} = 2.5 V; V_{IH} = 2.5 V; V_{IL} = 0 V; V_{M} = 0.75 V$                                                                            |                                                                                                                    |                  |       |                  |                       |     |                        |      |

| t <sub>PLH</sub>  | LOW-to-HIGH propagation delay                                                                                                                | from (input) SCL2 or SDA2<br>to (output) SCL1 or SDA1                                                              | 0                | 1     | 0                | 0.7                   | 0   | 0.4                    | ns   |

| t <sub>PHL</sub>  | HIGH-to-LOW<br>propagation delay                                                                                                             | from (input) SCL2 or SDA2<br>to (output) SCL1 or SDA1                                                              | 0                | 1.3   | 0                | 1                     | 0   | 0.6                    | ns   |

| Dynamic           | characteristics (transl                                                                                                                      | ating up)                                                                                                          |                  | •     | •                | •                     |     |                        |      |

| $V_{I(EN)} = 3.3$ | $V; V_{IH} = 2.3 V; V_{IL} =$                                                                                                                | $= 0 \text{ V}; \text{ V}_{\text{T}} = 3.3 \text{ V}; \text{ V}_{\text{M}} = 1.15 \text{ V}; \text{ R}_{\text{H}}$ | _ = 300 Ω        |       |                  |                       |     |                        |      |

| t <sub>PLH</sub>  | LOW-to-HIGH<br>propagation delay                                                                                                             | ffrom (input) SCL1 orSDA1<br>to (output) SCL2 or SDA2                                                              | 0                | 0.9   | 0                | 0.6                   | 0   | 0.4                    | ns   |

| t <sub>PHL</sub>  | HIGH-to-LOW<br>propagation delay                                                                                                             | from (input) SCL1 or SDA1<br>to (output) SCL2 or SDA2                                                              | 0                | 1.4   | 0                | 1.1                   | 0   | 0.7                    | ns   |

| $V_{I(EN)} = 2.5$ | $V_{I(EN)} = 2.5 \text{ V}; V_{IH} = 1.5 \text{ V}; V_{IL} = 0 \text{ V}; V_{T} = 2.5 \text{ V}; V_{M} = 0.75 \text{ V}; R_{L} = 300 \Omega$ |                                                                                                                    |                  |       |                  |                       |     |                        |      |

| t <sub>PLH</sub>  | LOW-to-HIGH propagation delay                                                                                                                | from (input) SCL1 orSDA1<br>to (output) SCL2 or SDA2                                                               | 0                | 1     | 0                | 0.6                   | 0   | 0.4                    | ns   |

| t <sub>PHL</sub>  | HIGH-to-LOW<br>propagation delay                                                                                                             | from (input) SCL1 or SDA1<br>to (output) SCL2 or SDA2                                                              | 0                | 1.3   | 0                | 1.3                   | 0   | 0.8                    | ns   |

SWITCH USAGE Translating up S1 R Translating down \$2 S1 Open From Output 0 V<sub>IH</sub> Under Test **S2** Input V. V<sub>M</sub> /11 (see Note A) 10H Output LOAD CIRCUIT VOL TRANSLATING UP Input VM VOH Output V<sub>M</sub> Voi TRANSLATING DOWN

#### PARAMETER MEASUREMENT INFORMATION

NOTES: A. CL includes probe and jig capacitance.

B. All input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, Z<sub>Q</sub> = 50 Ω, t<sub>f</sub> ≤ 2 ns, t<sub>f</sub> ≤ 2 ns.

C. The outputs are measured one at a time, with one transition per measurement.

#### Figure.2 Load Circuit for Outputs

## **Functional Description**

The PI6ULS5V9306 is a dual bidirectional  $I^2$ C-bus and SMBus voltage-level translator with an enable (EN) input, and is operational from 1.2 V to 3.3 V (VREF1) and 1.8 V to 5.5 V(VREF2).

The PI6ULS5V9306 allows bidirectional voltage translations between 1.2 V and 5 V without the use of a direction pin. The low ON-state resistance (Ron) of the switch allows connections to be made with minimal propagation delay. When EN is HIGH, the translator switch is on, and the SCL1 and SDA1 I/O are connected to the SCL2 and SDA2 I/O respectively, allowing bidirectional data flow between ports. When EN is LOW, the translator switch is off, and a high-impedance state exists between ports.

The PI6ULS5V9306 is not a bus buffer that provides both level translation and physically isolates to either side of the bus when both sides are connected. The PI6ULS5V9306 only isolates both sides when the device is disabled and provides voltage level translation when active.

The PI6ULS5V9306 can also be used to run two buses, one at 400kHz operating frequency and the other at 100 kHz operating frequency. If the two buses are operating at different frequencies, the 100 kHz bus must be isolated when the 400 kHz operation of the other bus is required. If the master is running at 400kHz, the maximum system operating frequency may be less than 400 kHz because of the delays added by the translator.

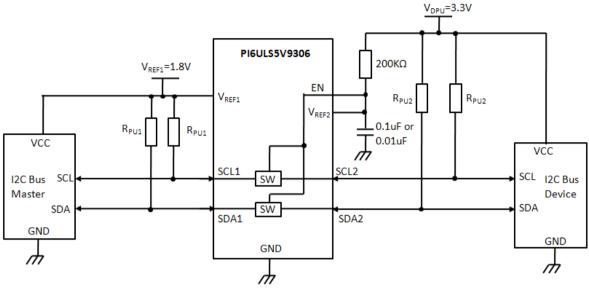

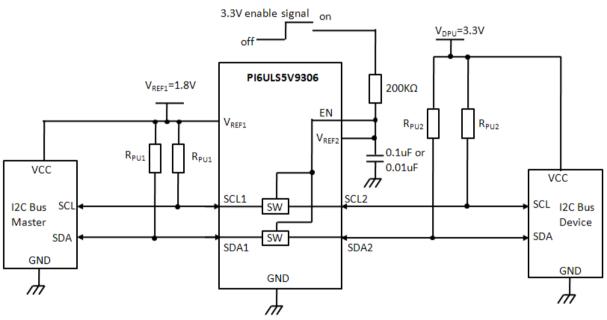

As with the standard  $I^2C$ -bus system, pull-up resistors are required to provide the logic HIGH levels on the translator's bus. The PI6ULS5V9306 has a standard open-collector configuration of the  $I^2C$ -bus. The size of these pull-up resistors depends on the system, but each side of the translator must have a pull-up resistor. The device is designed to work with Standard-mode, Fast-mode and Fast mode Plus  $I^2C$ -bus devices in addition to SMBus devices.

When the SDA1 or SDA2 port is LOW, the clamp is in the ON-state and a low resistance connection exists between the SDA1 and SDA2 ports. When the higher voltage is on the SDA2 port, and the SDA2 port is HIGH, the voltage on the SDA1 port is limited to the voltage set by VREF1. When the SDA1 port is HIGH, the SDA2 port is pulled to the drain pull-up supply voltage (VDPU) by the pull-up resistors. This functionality allows a seamless translation between higher and lower voltages selected by the user without the need for directional control. The SCL1/SCL2 channel also functions as the SDA1/SDA2 channel.

All channels have the same electrical characteristics and there is minimal deviation from one output to another in voltage or propagation delay. This is a benefit over discrete transistor voltage translation solutions, since the fabrication of the switch is symmetrical. The translator provides excellent ESD protection to lower voltage devices, and at the same time protects less ESD-resistant devices.

## **Application Information**

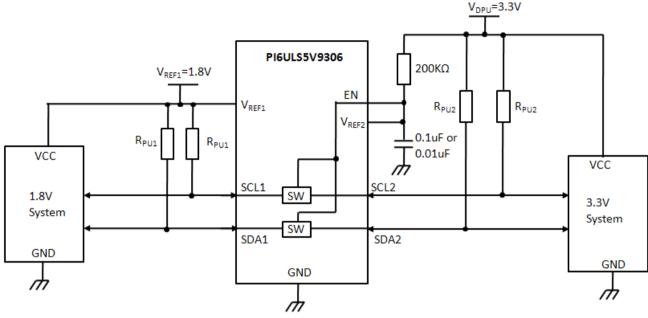

Figure.3 Typical Open Drain Application Circuit (Switch Always Enabled )

Figure.4 Typical Open Drain Application Circuit (Switch Enabled Control)

## **Open Drain Application**

For the bidirectional clamping configuration (higher voltage to lower voltage or lower voltage to higher voltage), the EN input must be connected to VREF2 and both pins pulled to high-side VDPU through a pull-up resistor (typically 200 k $\Omega$ ). This allows VREF2 to regulate the EN input. A filter capacitor on VREF2 is recommended.

Figure.5 Typical push-pull Application Circuit (Switch Enabled Control)

#### **Push Pull Application**

If used in push-pull system, the pull-up resistors on REF side are also needed. The data must be unidirectional or the outputs must be 3-stateable and be controlled by some direction-control mechanism to prevent high-to-low contentions in either direction.

#### **Operating Voltage**

Refer to Figure 2

|       |                                           | MIN TYP(        | 1) MAX | UNIT |

|-------|-------------------------------------------|-----------------|--------|------|

| VDPU  | Ref2 side pull-up voltage on $200k\Omega$ | VREF1 + 0.6 2.1 | 5      | V    |

| EN    | Enable input voltage                      | VREF1 + 0.6 2.1 | 5      | V    |

| VREF1 | Reference voltage                         | 0 1.5           | 4.4    | V    |

| IPASS | Pass switch current                       | 14              |        | mA   |

| IREF  | Reference-transistor current              |                 | 5      | μA   |

| TA    | Operating free-air temperature            | -40             | 85     | °C   |

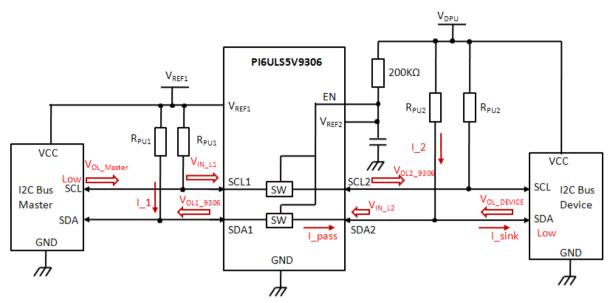

#### The pass through current : I\_pass

I\_pass is determined by the pull-up and the low voltage added on the PI6LS5V9306 In figure 6, I\_pass= ( $V_{REF1}$ - $V_{OL1_9306}$ )/ $R_{PU1}$

When V\_IN is 0V, the PI6ULS5V9306 can support as large as 64mA pass through current in theory. But we recommend it's better to limit the I\_pass in 15mA

Figure 6. Typical Open Drain Application Circuit

(1) The sink current : I\_sink

The device would sink the total current from both pull-up resistors. For example, in figure bellow, when the SDA2 is pulled low by the I<sup>2</sup>C device, the sink current of the I<sup>2</sup>C device I\_sink=Ipass+I\_2=I\_1+I\_2 . The same thing will happen when I<sup>2</sup>C master pull low the I<sup>2</sup>C bus. The I\_sink should be limited to not larger than the tolerance of the I<sup>2</sup>C devices.

(2)  $V_{IL}\!,\!V_{OL}$  of the external drive and  $V_{OL}$  of PI6ULS5V9306

In normal application, the V<sub>IL</sub> of external devices should always be larger than the V<sub>OL</sub> of PI6ULS5V9306. The value of PI6ULS5V9306's V<sub>OL</sub> is determined by the pass through current and the low voltage added on the SDA,SCL pins. The V<sub>OL\_9306</sub> = V<sub>IN\_L</sub> + V<sub>UP</sub> (V<sub>UP</sub> is mainly determined by the I\_pass, it always less than 0.35V.)

#### (3) Low VREF application

The PI6ULS5V9306 can support very low Vref1 application in theory ,but we recommend not lower than 0.9V.Because when VREF1 is less than 1.8V, the  $V_{OL}$  of REF1 side is a concern in system .

For example, in figure 6, if VREF1=0.9V, VDPU=3.3V he  $V_{IL}$  of the REF1 side I<sup>2</sup>C master is normally 0.3\*VREF1=0.25V, but the  $V_{OL}$  of REF2 side can up to 0.1\*VDPU=0.36V sometimes.

The system designer must make sure this situation doesn't happen. A limit for the V<sub>OL</sub> of REF2 side devices is required then.

The bellow table shows the requirement for  $V_{OL}$  of VREF2 side devices when using PI6ULS5V9306 (Requirement for  $V_{OL\_DEVICE}$  in figure 6)

| The V <sub>OL</sub> requirement of V <sub>REF2</sub> side external devices |                                                                                |        |                 |  |  |  |  |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------|-----------------|--|--|--|--|

| (Temp=25°C, Assum                                                          | (Temp=25°C, Assume the $V_{IL}$ of $V_{REF1}$ side devices is $0.3*V_{REF1}$ ) |        |                 |  |  |  |  |

| I_pass                                                                     | ≤3mA                                                                           | 10mA   | 15mA            |  |  |  |  |

| V <sub>REF1</sub>                                                          |                                                                                |        |                 |  |  |  |  |

| 0.9V                                                                       | ≤0.15V                                                                         | ≤0.1V  | Not Recommended |  |  |  |  |

| 1.2V                                                                       | ≤0.2V                                                                          | ≤0.15V | Not Recommended |  |  |  |  |

| 1.5V                                                                       | ≤0.3V                                                                          | ≤0.25V | ≤0.2V           |  |  |  |  |

| 1.8V                                                                       | ≤0.4V                                                                          | ≤0.35V | ≤0.3V           |  |  |  |  |

#### Pull-up resistors and minimum values

Sizing the pull-up resistor on an open-drain bus is specific to the individual application and is dependent on the following driver characteristics:

- The driver sink current

- The V<sub>OL</sub> of driver

- The  $V_{OL}$  of the PI6ULS5V9306

- The  $V_{IL}$  of the driver

- Frequency of operation

The following tables can be used to estimate the pull-up resistor value in different use cases so that the minimum resistance for the pull-up resistor can be found.

Tables in bellow contain suggested minimum values of pull-up resistors for the PI6UILS5V9306 with typical voltage translation levels and drive currents.

The calculated values assume that both drive currents are the same.

$V_{OL} = V_{IL} = 0.1*VCC$  and accounts for a 5 % VCC tolerance of the supplies, 1 % resistor values. It should be noted that the resistor chosen in the final application should be equal to or larger than the values shown in the table to ensure that the pass voltage is less than 10 % of the VCC voltage, and the external driver should be able to sink the total current from both pull-up resistors.

Pull-up resistor minimum values, 3 mA driver sink current for PI6ULS5V9306

| A Side |                        | B side                    |                           |                           |                           |  |  |  |  |

|--------|------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--|--|--|--|

|        | 1.5V                   | 1.8V                      | 2.5V                      | 3.3V                      | 5.0V                      |  |  |  |  |

| 0.9V   | $R_{RPU1} = 859\Omega$ | $R_{RPU1} = 970\Omega$    | $R_{RPU1} = none$         | $R_{RPU1} = none$         | $R_{RPU1} = none$         |  |  |  |  |

|        | $R_{RPU2} = 859\Omega$ | $R_{RPU2} = 970\Omega$    | $R_{RPU2} = 896\Omega$    | $R_{RPU2} = 1.19k\Omega$  | $R_{RPU2} = 1.82k\Omega$  |  |  |  |  |

|        |                        |                           | Or both $1.23k\Omega$     | Or both $1.53k\Omega$     | Or both $2.16k\Omega$     |  |  |  |  |

| 1.2V   |                        | $R_{RPU1} = 1.07 k\Omega$ | $R_{RPU1} = none$         | $R_{RPU1} = none$         | $R_{RPU1} = none$         |  |  |  |  |

|        |                        | $R_{RPU2} = 1.07 k\Omega$ | $R_{RPU2} = 886\Omega$    | $R_{RPU2} = 1.18 k\Omega$ | $R_{RPU2} = 1.81 k\Omega$ |  |  |  |  |

|        |                        |                           | Or both $1.33k\Omega$     | Or both $1.63k\Omega$     | Or both $2.26k\Omega$     |  |  |  |  |

| 1.5V   |                        |                           | $R_{RPU1} = none$         | $R_{RPU1} = none$         | $R_{RPU1} = none$         |  |  |  |  |

|        |                        |                           | $R_{RPU2} = 875\Omega$    | $R_{RPU2} = 1.17 k\Omega$ | $R_{RPU2} = 1.8k\Omega$   |  |  |  |  |

|        |                        |                           | Or both $1.43k\Omega$     | Or both $1.73k\Omega$     | Or both $2.36k\Omega$     |  |  |  |  |

| 1.8V   |                        |                           | $R_{RPU1} = 1.53 k\Omega$ | $R_{RPU1} = none$         | $R_{RPU1} = none$         |  |  |  |  |

|        |                        |                           | $R_{RPU2} = 1.53 k\Omega$ | $R_{RPU2} = 1.16 k\Omega$ | $R_{RPU2} = 1.79 k\Omega$ |  |  |  |  |

|        |                        |                           |                           | Or both $1.82k\Omega$     | Or both 2.46k $\Omega$    |  |  |  |  |

| 2.5V   |                        |                           |                           | $R_{RPU1} = 2.06 k\Omega$ | $R_{RPU1} = none$         |  |  |  |  |

|        |                        |                           |                           | $R_{RPU2} = 2.06 k\Omega$ | $R_{RPU2} = 1.77 k\Omega$ |  |  |  |  |

|        |                        |                           |                           |                           | Or both 2.69k $\Omega$    |  |  |  |  |

| 3.3V   |                        |                           |                           |                           | $R_{RPU1} = none$         |  |  |  |  |

|        |                        |                           |                           |                           | $R_{RPU2} = 1.74 k\Omega$ |  |  |  |  |

|        |                        |                           |                           |                           | Or both 2.96k $\Omega$    |  |  |  |  |

| A Side | B side                 |                        |                        |                        |                        |  |  |  |

|--------|------------------------|------------------------|------------------------|------------------------|------------------------|--|--|--|

|        | 1.5V                   | 1.8V                   | 2.5V                   | 3.3V                   | 5.0V                   |  |  |  |

| 0.9V   | $R_{RPU1} = 258\Omega$ | $R_{RPU1} = 291\Omega$ | $R_{RPU1} = none$      | $R_{RPU1} = none$      | $R_{RPU1} = none$      |  |  |  |

|        | $R_{RPU2} = 258\Omega$ | $R_{RPU2} = 291\Omega$ | $R_{RPU2} = 269\Omega$ | $R_{RPU2} = 358\Omega$ | $R_{RPU2} = 546\Omega$ |  |  |  |

|        |                        |                        | Or both $369\Omega$    | Or both $458\Omega$    | Or both $646\Omega$    |  |  |  |

| 1.2V   |                        | $R_{RPU1} = 321\Omega$ | $R_{RPU1} = none$      | $R_{RPU1} = none$      | $R_{RPU1} = none$      |  |  |  |

|        |                        | $R_{RPU2} = 321\Omega$ | $R_{RPU2} = 266\Omega$ | $R_{RPU2} = 355\Omega$ | $R_{RPU2} = 543\Omega$ |  |  |  |

|        |                        |                        | Or both $399\Omega$    | Or both $488\Omega$    | Or both $677\Omega$    |  |  |  |

| 1.5V   |                        |                        | $R_{RPU1} = none$      | $R_{RPU1} = none$      | $R_{RPU1} = none$      |  |  |  |

|        |                        |                        | $R_{RPU2} = 263\Omega$ | $R_{RPU2} = 352\Omega$ | $R_{RPU2} = 540\Omega$ |  |  |  |

|        |                        |                        | Or both $429\Omega$    | Or both $518\Omega$    | Or both $707\Omega$    |  |  |  |

| 1.8V   |                        |                        | $R_{RPU1} = 460\Omega$ | $R_{RPU1} = none$      | $R_{RPU1} = none$      |  |  |  |

|        |                        |                        | $R_{RPU2} = 460\Omega$ | $R_{RPU2} = 348\Omega$ | $R_{RPU2} = 537\Omega$ |  |  |  |

|        |                        |                        |                        | Or both $548\Omega$    | Or both $737\Omega$    |  |  |  |

| 2.5V   |                        |                        |                        | $R_{RPU1} = 619\Omega$ | $R_{RPU1} = none$      |  |  |  |

|        |                        |                        |                        | $R_{RPU2} = 619\Omega$ | $R_{RPU2} = 521\Omega$ |  |  |  |

|        |                        |                        |                        |                        | Or both $808\Omega$    |  |  |  |

| 3.3V   |                        |                        |                        |                        | $R_{RPU1} = none$      |  |  |  |

|        |                        |                        |                        |                        | $R_{RPU2} = 522\Omega$ |  |  |  |

|        |                        |                        |                        |                        | Or both $889\Omega$    |  |  |  |

Pull-up resistor minimum values, 10 mA driver sink current for PI6ULS5V9306

Pull-up resistor minimum values, 15 mA driver sink current for PI6ULS5V9306

| A Side | B side                 |                        |                        |                        |                        |  |  |  |

|--------|------------------------|------------------------|------------------------|------------------------|------------------------|--|--|--|

|        | 1.5V                   | 1.8V                   | 2.5V                   | 3.3V                   | 5.0V                   |  |  |  |

| 0.9V   | $R_{RPU1} = 172\Omega$ | $R_{RPU1} = 194\Omega$ | $R_{RPU1} = none$      | $R_{RPU1} = none$      | $R_{RPU1} = none$      |  |  |  |

|        | $R_{RPU2} = 172\Omega$ | $R_{RPU2} = 194\Omega$ | $R_{RPU2} = 179\Omega$ | $R_{RPU2} = 238\Omega$ | $R_{RPU2} = 364\Omega$ |  |  |  |

|        |                        |                        | Or both $246\Omega$    | Or both $305\Omega$    | Or both $431\Omega$    |  |  |  |

| 1.2V   |                        | $R_{RPU1} = 214\Omega$ | $R_{RPU1} = none$      | $R_{RPU1} = none$      | $R_{RPU1} = none$      |  |  |  |

|        |                        | $R_{RPU2} = 214\Omega$ | $R_{RPU2} = 177\Omega$ | $R_{RPU2} = 236\Omega$ | $R_{RPU2} = 362\Omega$ |  |  |  |

|        |                        |                        | Or both $266\Omega$    | Or both $325\Omega$    | Or both $451\Omega$    |  |  |  |

| 1.5V   |                        |                        | $R_{RPU1} = none$      | $R_{RPU1} = none$      | $R_{RPU1} = none$      |  |  |  |

|        |                        |                        | $R_{RPU2} = 175\Omega$ | $R_{RPU2} = 234\Omega$ | $R_{RPU2} = 360\Omega$ |  |  |  |

|        |                        |                        | Or both $286\Omega$    | Or both $345\Omega$    | Or both $471\Omega$    |  |  |  |

| 1.8V   |                        |                        | $R_{RPU1} = 306\Omega$ | $R_{RPU1} = none$      | $R_{RPU1} = none$      |  |  |  |

|        |                        |                        | $R_{RPU2} = 306\Omega$ | $R_{RPU2} = 232\Omega$ | $R_{RPU2} = 358\Omega$ |  |  |  |

|        |                        |                        |                        | Or both $366\Omega$    | Or both $492\Omega$    |  |  |  |

| 2.5V   |                        |                        |                        | $R_{RPU1} = 413\Omega$ | $R_{RPU1} = none$      |  |  |  |

|        |                        |                        |                        | $R_{RPU2} = 413\Omega$ | $R_{RPU2} = 354\Omega$ |  |  |  |

|        |                        |                        |                        |                        | Or both $539\Omega$    |  |  |  |

| 3.3V   |                        |                        |                        |                        | $R_{RPU1} = none$      |  |  |  |

|        |                        |                        |                        |                        | $R_{RPU2} = 348\Omega$ |  |  |  |

|        |                        |                        |                        |                        | Or both $593\Omega$    |  |  |  |

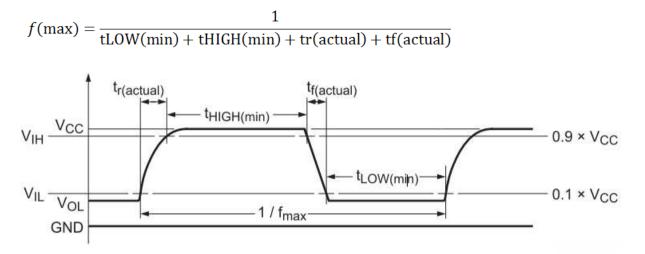

#### **Max Frequency Application**

The maximum frequency is limited by the minimum pulse width LOW and HIGH as well as rise time and fall time.

The rise and fall times are dependent upon translation voltages, the drive strength, the total node capacitance (CL) and the pullup resistors (RPU) that are present on the bus. The node capacitance is the addition of the PCB trace capacitance and the device capacitance that exists on the bus.

Because of the dependency of the external components, PCB layout and the different device operating states the calculation of rise and fall times is complex and has several inflection points along the curve.

The main component of the rise and fall times is the RC time constant of the bus line when the device is in its two primary operating states: when device is in the ON state and it is low-impedance, the other is when the device is OFF isolating the A-side from the B-side.

There are some basic guidelines to follow that will help maximize the performance of the device:

- Keep trace length to a minimum by placing the PI6ULS5V9306 close to the processor.

- The signal round trip time on trace should be shorter than the rise or fall time of signal to reduce reflections.

- The faster the edge of the signal, the higher the chance for ringing.

- The higher drive strength controlled by the pull-up resistor (up to 15 mA), the higher the frequency the device can use.

The system designer must design the pull-up resistor value based on external current drive strength and limit the node capacitance (minimize the wire, stub, connector and trace length) to get the desired operation frequency result.

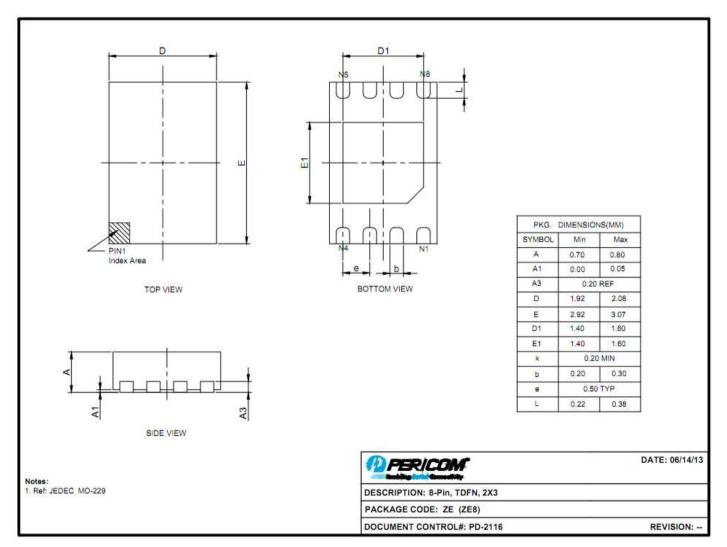

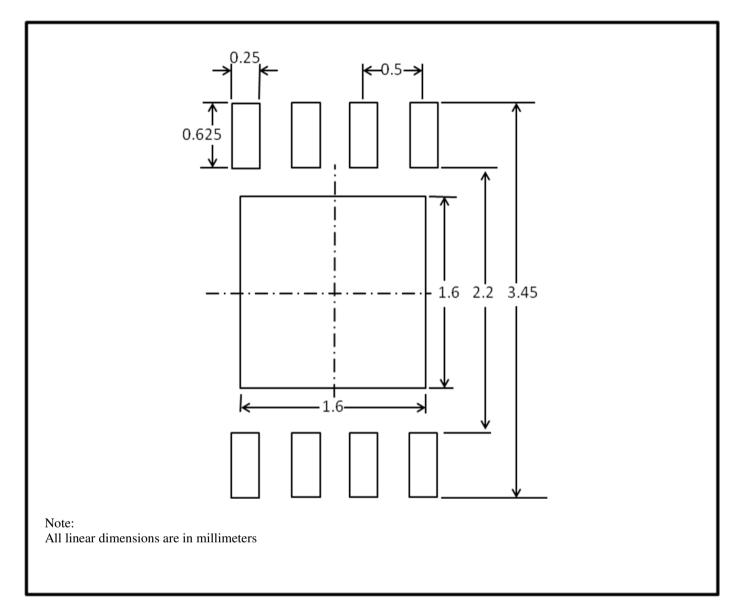

**Mechanical Information**

TDFN2x3-8(ZE)

## Recommended Land pattern for TDFN2x3-8L

A Product Line of Diodes Incorporated

PI6ULS5V9306

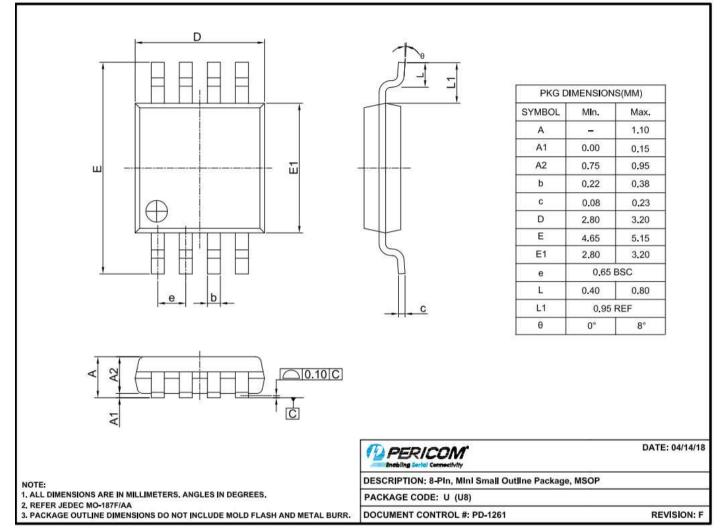

#### MSOP-8(U)

A Product Line of Diodes Incorporated

PI6ULS5V9306

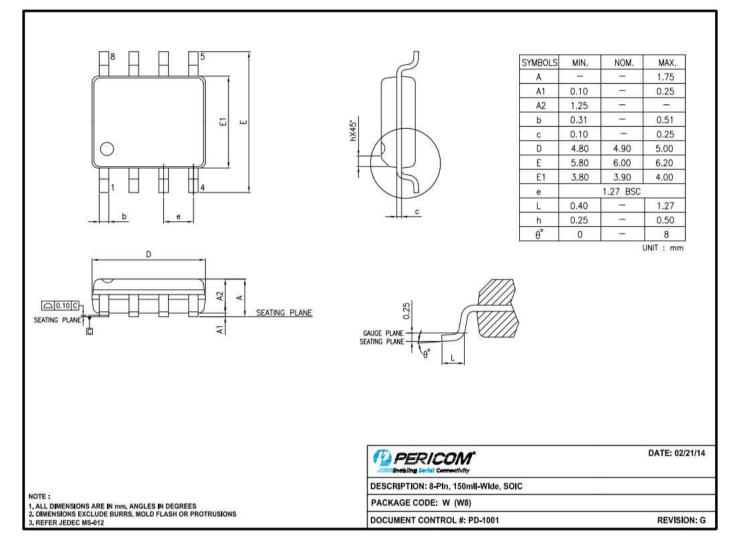

#### SOIC-8(W)

A Product Line of Diodes Incorporated

PI6ULS5V9306

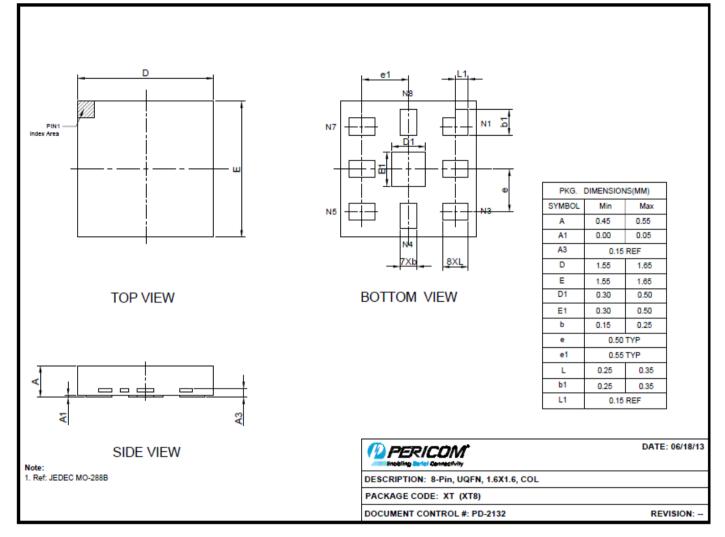

#### UQFN-8 (XT)

Note: For latest package info, please check: http://www.pericom.com/support/packaging/packaging-mechanicals-and-thermal-characteristics/ Ordering Information

| 8                |              |                                            |

|------------------|--------------|--------------------------------------------|

| Part No.         | Package Code | Package                                    |

| PI6ULS5V9306ZEEX | ZE           | Lead free and Green TDFN2x3-8L,Tape & Reel |

| PI6ULS5V9306UE   | U            | Lead free and Green MSOP-8L                |

| PI6ULS5V9306UEX  | U            | Lead free and Green MSOP-8L, Tape & Reel   |

| PI6ULS5V9306WE   | W            | 8-Pin,150 mil Wide SOIC                    |

| PI6ULS5V9306WEX  | W            | 8-Pin,150 mil Wide SOIC, Tape & Reel       |

| PI6ULS5V9306XTEX | XT           | 8-pin UDFN 1.6x1.6, Tape & Reel            |

Note:

• Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

• E = Pb-free and Green

• Adding X Suffix= Tape/Reel