Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Level Translating I<sup>2</sup>C-Bus/SMBus Repeater with Tiny Package

#### **Features**

- Bidirectional buffer isolates capacitance and allows 400 pF on port B of the device

- Port A operating supply voltage range of 1.1 V to  $V_{CC(B)}$  1.0 V

- Port B operating supply voltage range of 2.5 V to 5.5 V

- Voltage level translation from 1.1V to V<sub>CC(B)</sub> -1.0V and from 2.5 V to 5.5 V

- Requires no external pull-up resistors on lower voltage port A

- Open-drain port B inputs/outputs

- Lock-up free operation

- Supports arbitration and clock stretching across the repeater

- Accommodates Standard-mode and Fast-mode I<sup>2</sup>Cbus devices and multiple masters

- Powered-off high-impedance I<sup>2</sup>C-bus pins

- 5 V tolerant B SCL, SDA and enable pins

- 0 Hz to 400 kHz clock frequency (Remark: The maximum system operating frequency may be less than 400 kHz because of the delays added by the repeater.)

- ESD protection exceeds 8KV HBM per JESD22-A114

- Package: MSOP-8, SOIC-8 and UQFN1.6x1.6-8L

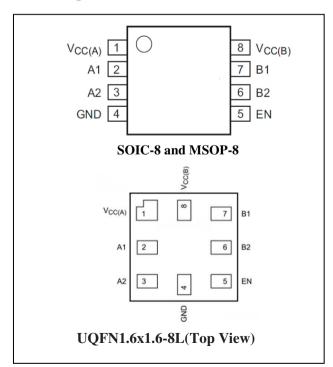

# **Pin Configuration**

### **Description**

The PI6ULS5V9509 is a level translating I<sup>2</sup>C-bus/SMBus repeater. It can provide bidirectional level translation between low voltage (down to 1.1V) and higher voltage (2.5V to 5.5V) in mixed-mode applications. And it enables I<sup>2</sup>C and similar bus system to be extended, without degradation of performance even during level shifting.

The PI6ULS5V9509 enables the system designer to isolate two halves of a bus for both voltage and capacitance, accommodating more I<sup>2</sup>C devices or longer trace length. It also permits extension of the I<sup>2</sup>C-bus by providing bidirectional buffering for both the data (SDA) and the clock (SCL) lines, thus allowing two buses of 400 pF to be connected in an I<sup>2</sup>C application.

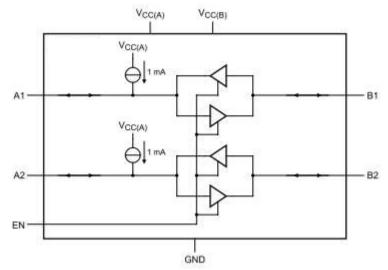

The bus port B drivers are compliant with SMBus I/O levels, while port A uses a current sensing mechanism to detect the input or output LOW signal which prevents bus lock-up. Port A uses a 1 mA current source for pull-up and a  $200\Omega$  pull-down driver. This result in a LOW on the port A accommodating smaller voltage swings. The output pull-down on the port A internal buffer LOW is set for approximately 0.2V, while the input threshold of the internal buffer is set about 50 mV lower than that of the output voltage LOW. When the port A I/O is driven LOW internally, the LOW is not recognized as a LOW by the input. This prevents a lock-up condition from occurring. The output pull-down on the port B drives a hard LOW and the input level is set at 0.3 of SMBus or I<sup>2</sup>C-bus voltage level which enables port B to connect to any other I<sup>2</sup>C-bus devices or buffer.

The PI6ULS5V9509 drivers are not enabled unless  $V_{\text{CC(A)}}$  is above 0.8 V and  $V_{\text{CC(B)}}$  is above 2.5 V. The enable (EN) pin can also be used to turn the drivers on and off under system control. Caution should be observed to only change the state of the EN pin when the bus is idle.

# **Pin Description**

| Pin No | Pin Name    | Description                              |  |

|--------|-------------|------------------------------------------|--|

| 1      | $V_{CC(A)}$ | port A supply voltage                    |  |

| 2      | A1          | port A (lower voltage side)              |  |

| 3      | A2          | port A (lower voltage side)              |  |

| 4      | GND         | supply ground (0 V)                      |  |

| 5      | EN          | active HIGH repeater enable input        |  |

| 6      | B2          | port B (SMBus/I <sup>2</sup> C-bus side) |  |

| 7      | B1          | port B (SMBus/I <sup>2</sup> C-bus side) |  |

| 8      | $V_{CC(B)}$ | port B supply voltage                    |  |

# **Block Diagram**

| EN | Function            |

|----|---------------------|

| Н  | A1 = B1;<br>A2= B2; |

| L  | disabled            |

Figure 1: Block Diagram

# **Maximum Ratings**

| Storage Temperature                                               | 55°C to +125°C |

|-------------------------------------------------------------------|----------------|

| Supply Voltage port B                                             | 0.5V to +6.0V  |

| Supply Voltage port A                                             | 0.5V to+6.0V   |

| DC Input Voltage                                                  | 0.5V to +6.0V  |

| Control Input Votage(EN)                                          | 0.5V to+6.0V   |

| Total Power Dissipation                                           | 100mA          |

| Input/Output Current (portA&B)                                    | 20mA           |

| Input Current (EN, V <sub>CC(A)</sub> , V <sub>CC(B)</sub> , GND) | 20mA           |

| ESD; HBM Mode                                                     | 8000V          |

#### Note

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Recommended operation conditions**

GND = 0 V; Tamb = -40 °C to +85 °C; unless otherwise specified

| Symbol             | Parameter                                | Test Conditions        | Min  | Typ <sup>[1]</sup> | Max                     | Unit |

|--------------------|------------------------------------------|------------------------|------|--------------------|-------------------------|------|

| Vcc <sub>(B)</sub> | supply voltage port B                    | -                      | 2.5  | -                  | 5.5                     | V    |

| Vcc <sub>(A)</sub> | supply voltage port A                    | -                      | 1.1  | -                  | V <sub>CC(B)</sub> -1.0 | V    |

| I <sub>CC(A)</sub> | supply current on pin $V_{\text{CC(A)}}$ | all port A static HIGH | 0.25 | 0.45               | 0.9                     | A    |

|                    |                                          | all port A static LOW  | 1.25 | 3.0                | 5                       | mA   |

| $I_{CC(B)}$        | supply current on pin V <sub>CC(B)</sub> | all port B static HIGH | 0.5  | 0.9                | 1.1                     | mA   |

#### Note:

[1] Typical values with  $V_{CC(A)} = 1.1 \text{ V}$ ,  $V_{CC(B)} = 5 \text{ V}$ .

#### **DC** Electrical Characteristics

GND = 0 V;  $T_{amb} = -40 \, ^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ ; unless otherwise specified

| Parameter                          | Description                                                                | Test Conditions                                                | Min                   | Typ <sup>[1]</sup> | Max                        | Unit |

|------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------|--------------------|----------------------------|------|

| Input and output of port A (A1&A2) |                                                                            |                                                                |                       |                    |                            |      |

| $V_{ m IH}$                        | HIGH-level input voltage                                                   | -                                                              | $0.7V_{CC(A)}$        | -                  | $V_{\text{CC(A)}}$         | V    |

| $V_{IL}^{[2]}$                     | LOW-level input voltage                                                    | -                                                              | -0.5                  | -                  | +0.3                       | V    |

| $ m V_{ILc}$                       | contention LOW-level input voltage                                         | -                                                              | -0.5                  | +0.15              | -                          | V    |

| $V_{IK}$                           | input clamping voltage                                                     | $I_L$ = -18 mA                                                 | -1.5                  | -                  | -0.5                       | V    |

| $I_{LI}$                           | input leakage current                                                      | $V_I = V_{CC(A)}$                                              | -                     | -                  | ±1                         | μΑ   |

| ${ m I}_{ m IL}$                   | LOW-level input current                                                    | SDA, SCL; $V_I = 0.2 \text{ V}$                                | -1.5                  | -1.0               | -0.45                      | mA   |

|                                    |                                                                            | $V_{CC(A)} = 0.95 \text{ V to } 1.2 \text{V}$                  | -                     | 0.18               | 0.25                       |      |

| $V_{ m OL}$                        | LOW-level output voltage                                                   | $V_{CC(A)} = > 1.2V \text{ to}$<br>$(V_{CC(B)} - 1 \text{ V})$ | -                     | 0.2                | 0.3                        | V    |

| V <sub>OL</sub> -V <sub>ILc</sub>  | difference between LOW-level output and LOW-level input voltage contention | guaranteed by design                                           | -                     | 50                 | -                          | mV   |

| $I_{LOH}$                          | HIGH-level output leakage current                                          | $V_O = V_{CC(A)}$                                              | -                     | -                  | 10                         | μΑ   |

| $C_{io}$                           | input/output capacitance                                                   | -                                                              | -                     | 6                  | -                          | pF   |

| Input and outp                     | out of port B (B1&B2)                                                      |                                                                |                       |                    |                            |      |

| $V_{IH}$                           | HIGH-level input voltage                                                   | -                                                              | 0.7V <sub>CC(B)</sub> | _                  | $V_{\text{CC(B)}}$         | V    |

| $V_{\rm IL}$                       | LOW-level input voltage                                                    | -                                                              | -0.5                  | _                  | +0.3<br>V <sub>CC(B)</sub> | v    |

| $V_{IK}$                           | input clamping voltage                                                     | $I_I = -18 \text{ mA}$                                         | -1.5                  | -                  | -0.5                       | V    |

| $I_{LI}$                           | input leakage current                                                      | $V_{I} = 3.6 \text{ V}$                                        | -1                    | -                  | 1                          | μΑ   |

| ${ m I}_{ m IL}$                   | LOW-level input current                                                    | $V_{I} = 0.2 \text{ V}$                                        | -                     | ı                  | 10                         | μΑ   |

| $V_{OL}$                           | LOW-level output voltage                                                   | $I_{OL} = 6 \text{ mA}$                                        | -                     | 0.1                | 0.2                        | V    |

| $I_{LOH}$                          | HIGH-level output leakage current                                          | $V_0 = 3.6 \text{ V}$                                          | -                     | -                  | 10                         | μΑ   |

| $C_{io}$                           | input/output capacitance                                                   | -                                                              | -                     | 3                  | -                          | pF   |

| Enable                             |                                                                            |                                                                |                       |                    |                            |      |

| $V_{\mathrm{IH}}$                  | HIGH-level input voltage                                                   | -                                                              | 0.9V <sub>CC(A)</sub> | -                  | $V_{\text{CC(B)}}$         | V    |

| $V_{\rm IL}$                       | LOW-level input voltage                                                    | -                                                              | -0.5                  | -                  | +0.1<br>V <sub>CC(A)</sub> | V    |

| ${ m I}_{ m IL}$                   | LOW-level input current                                                    | $V_{I} = 0.2 \text{ V, EN;}$<br>$V_{CC} = 3.6 \text{ V}$       | -1                    | -                  | +1                         | μΑ   |

| $I_{LI}$                           | input leakage current                                                      | $V_{\rm I} = V_{\rm CC}$                                       | -1                    | -                  | +1                         | μΑ   |

| $C_{i}$                            | input capacitance                                                          | $V_{I} = 3.0 \text{ V or } 0\text{V}$                          | -                     | 2                  | -                          | pF   |

- 1. Typical values with  $V_{CC(A)} = 1.1 \text{ V}$ ,  $V_{CC(B)} = 5 \text{ V}$ . 2.  $V_{IL}$  specification is for the falling edge seen by the port A input.  $V_{ILC}$  is for the static LOW levels seen by the port A input resulting in port B output staying LOW.

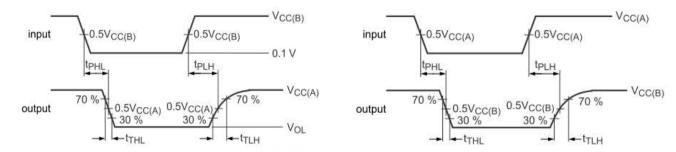

# **Dynamic characteristics**

$V_{CC(A)} = 1.1 \text{ V}; V_{CC(B)} = 3.3 \text{ V}^{[1]}$

| Symbol               | Parameter                          | Test Conditions                                                                                   | Min | Тур | Max  | Unit |

|----------------------|------------------------------------|---------------------------------------------------------------------------------------------------|-----|-----|------|------|

| t <sub>PLH</sub>     | LOW-to-HIGH propagation delay      | port B to port A                                                                                  | I   | 65  | 216  | ns   |

| $t_{ m PHL}$         | HIGH-to-LOW propagation delay      | port B to port A                                                                                  | -   | 25  | 140  | ns   |

| $t_{ m TLH}$         | LOW to HIGH output transition time | port A                                                                                            | 14  | 22  | 96   | ns   |

| t <sub>THL</sub>     | HIGH to LOW output transition time | port A                                                                                            | ı   | 20  | 1    | ns   |

| $t_{PLH}$            | LOW to HIGH propagation delay      | port A to port B                                                                                  | -   | -69 | -139 | ns   |

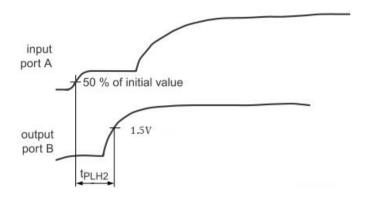

| t <sub>PLH</sub> 2   | LOW to HIGH propagation delay      | port A to port B; measured from<br>the 50 % of initial LOW on port A<br>to 1.5 V rising on port B | ı   | 100 | 226  | ns   |

| $t_{ m PHL}$         | HIGH to LOW propagation delay      | port A to port B                                                                                  | 20  | 50  | 183  | ns   |

| t <sub>TLH</sub> [2] | LOW to HIGH output transition time | port B                                                                                            | -   | 61  | -    | ns   |

| t <sub>THL</sub>     | HIGH to LOW output transition time | port B                                                                                            | 1   | 2   | 40   | ns   |

| $t_{su}$             | set-up time                        | EN HIGH before START condition                                                                    | 100 | -   | -    | ns   |

| t <sub>h</sub>       | hold time                          | EN HIGH after STOP condition                                                                      | 100 | -   | -    | ns   |

$V_{CC(A)} = 1.9 \text{ V}; V_{CC(B)} = 5.0 \text{ V}^{[1]}$

| Symbol               | Parameter                          | Test Conditions                                                                                   | Min | Тур | Max  | Unit |

|----------------------|------------------------------------|---------------------------------------------------------------------------------------------------|-----|-----|------|------|

| $t_{\rm PLH}$        | LOW-to-HIGH propagation delay      | port B to port A                                                                                  | -   | 75  | 216  | ns   |

| $t_{\mathrm{PHL}}$   | HIGH-to-LOW propagation delay      | port B to port A                                                                                  | -   | 20  | 140  | ns   |

| $t_{TLH}$            | LOW to HIGH output transition time | port A                                                                                            | 14  | 27  | 96   | ns   |

| $t_{THL}$            | HIGH to LOW output transition time | port A                                                                                            | -   | 20  | -    | ns   |

| t <sub>PLH</sub>     | LOW to HIGH propagation delay      | port A to port B                                                                                  | -   | -69 | -139 | ns   |

| t <sub>PLH2</sub>    | LOW to HIGH propagation delay      | port A to port B; measured from<br>the 50 % of initial LOW on port A<br>to 1.5 V rising on port B | -   | 91  | 226  | ns   |

| $t_{PHL}$            | HIGH to LOW propagation delay      | port A to port B                                                                                  | 20  | 50  | 183  | ns   |

| t <sub>TLH</sub> [2] | LOW to HIGH output transition time | port B                                                                                            | -   | 65  | -    | ns   |

| $t_{THL}$            | HIGH to LOW output transition time | port B                                                                                            | 1   | 2   | 40   | ns   |

| $t_{su}$             | set-up time                        | EN HIGH before START condition                                                                    | 100 | -   | -    | ns   |

| t <sub>h</sub>       | hold time                          | EN HIGH after STOP condition                                                                      | 100 | -   | -    | ns   |

#### Note:

- [1] Load capacitance = 50 pF; load resistance on port B = 1.35 k

- [2] Value is determined by RC time constant of bus line

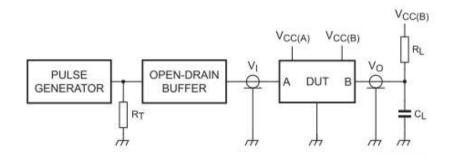

Figure 2: Propagation Delay and Transition Times B→A

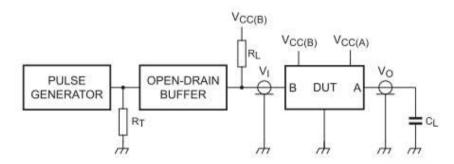

Figure 3: Propagation Delay and Transition Times A→B

Figure 4: Propagation delay from the port A's external driver switching off to port B LOW-to-HIGH transition; (A→B)

$R_L$  = load resistor; 1.35 k $\Omega$  on port B

C<sub>L</sub> = load capacitance includes jig and probe capacitance; 50 pF

R<sub>T</sub> = termination resistance should be equal to Z<sub>o</sub> of pulse generators

$R_L$  = load resistor; 1.35 k $\Omega$  on port B

C<sub>L</sub> = load capacitance includes jig and probe capacitance; 50 pF

R<sub>T</sub> = termination resistance should be equal to Z<sub>o</sub> of pulse generators

Figure 5: Test Circuit

# PI6ULS5V9509 Level Translating I<sup>2</sup>C-Bus/SMBus Repeater with Tiny Package

#### **Functional Description**

The PI6ULS5V9509 is a level translating  $I^2C$ -bus/SMBus repeater. It can provide bidirectional level translation between low voltage (down to 1.1V) and higher voltage (2.5V to 5.5V) in mixed-mode applications. And it enables  $I^2C$  and similar bus system to be extended, without degradation of performance even during level shifting.

The PI6ULS5V9509 enables the system designer to isolate two halves of a bus for both voltage and capacitance, accommodating more  $I^2C$  devices or longer trace length. It also permits extension of the  $I^2C$ -bus by providing bidirectional buffering for both the data (SDA) and the clock (SCL) lines, thus allowing two buses of 400 pF to be connected in an  $I^2C$  application.

The bus port B drivers are compliant with SMBus I/O levels, while port A uses a current sensing mechanism to detect the input or output LOW signal which prevents bus lock-up. Port A uses a 1 mA current source for pull-up and a  $200\,\Omega$  pull-down driver. This result in a LOW on the port A accommodating smaller voltage swings. The output pull-down on the port A internal buffer LOW is set for approximately 0.2 V, while the input threshold of the internal buffer is set about 50 mV lower than that of the output voltage LOW. When the port A I/O is driven LOW internally, the LOW is not recognized as a LOW by the input. This prevents a lock-up condition from occurring. The output pull-down on the port B drives a hard LOW and the input level is set at 0.3 of SMBus or I<sup>2</sup>C-bus voltage level which enables port B to connect to any other I<sup>2</sup>C-bus devices or buffer.

The PI6ULS5V9509 drivers are not enabled unless  $V_{\text{CC(A)}}$  is above 0.8 V and  $V_{\text{CC(B)}}$  is above 2.5 V. The enable (EN) pin can also be used to turn the drivers on and off under system control. Caution should be observed to only change the state of the EN pin when the bus is idle.

# **Application Information**

A typical application is shown in Figure 6. In this example, the system master is running on a 1.1 V I<sup>2</sup>C-bus while the slave is connected to a 3.3 V bus. Both buses run at 400 kHz. Master devices can be placed on either bus.

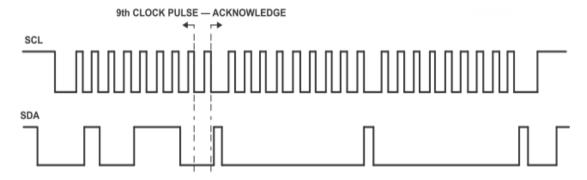

When port B of the PI6ULS5V9509 is pulled LOW by a driver on the  $I^2$ C-bus, a CMOS hysteresis detects the falling edge when it goes below  $0.3V_{CC(B)}$  and causes the internal driver on port A to turn on, causing port A to pull down to about 0.2 V. When port A of the PI6ULS5V9509 falls, first a comparator detects the falling edge and causes the internal driver on port B to turn on and pull the port B pin down to ground. In order to illustrate what would be seen in a typical application, refer to Figure 7 and Figure 8. If the bus master in Figure 6 were to write to the slave through the PI6ULS5V9509, waveforms shown in Figure 7 would be observed on the B bus. This looks like a normal  $I^2$ C-bus transmission.

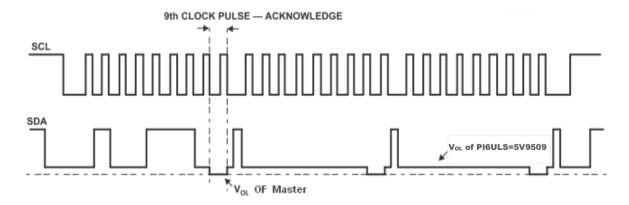

On the A bus side of the PI6ULS5V9509, the clock and data lines would have a positive offset from ground equal to the  $V_{OL}$  of the PI6ULS5V9509. After the eighth clock pulse, the data line will be pulled to the Vol of the master device, which is very close to ground in this example. At the end of the acknowledge, the level rises only to the LOW level set by the driver in the PI6ULS5V9509 for a short delay while the B bus side rises above 0.5  $V_{CC(B)}$ , then it continues HIGH. It is important to note that any arbitration or clock stretching events require that the LOW level on the A bus side at the input of the PI6ULS5V9509 ( $V_{IL}$ ) is below  $V_{ILC}$  to be recognized by the PI6ULS5V9509 and then transmitted to the B bus side.

Figure 6: Typical Application

Figure 7: Bus B I<sup>2</sup>C/SMBusWaveform

Figure 8: Bus A Lower Voltage Waveform

## **Mechanical Information**

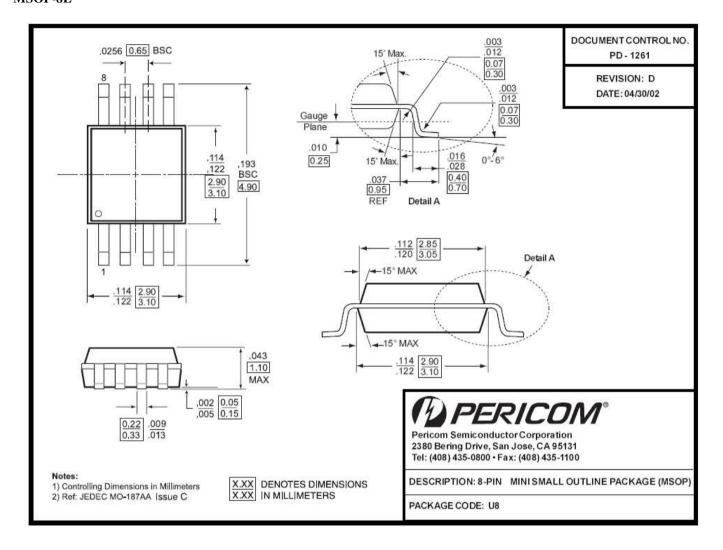

MSOP-8L

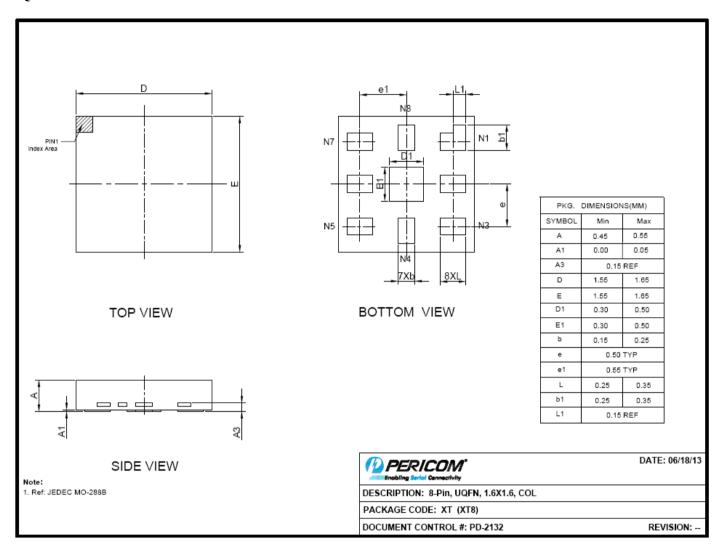

#### UQFN1.6x1.6-8L

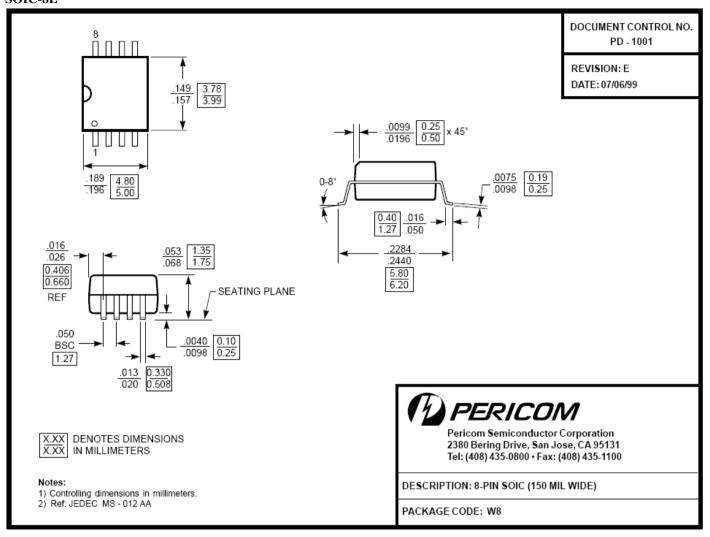

#### SOIC-8L

# **Ordering Information**

| Part No.         | Package Code | Package                                            |

|------------------|--------------|----------------------------------------------------|

| PI6ULS5V9509UE   | U            | Lead free and Green 8-pin MSOP                     |

| PI6ULS5V9509UEX  | U            | Lead free and Green 8-pin MSOP, Tape & Reel        |

| PI6ULS5V9509WE   | W            | Lead free and Green 8-pin SOIC                     |

| PI6ULS5V9509WEX  | W            | Lead free and Green 8-pin SOIC, Tape & Reel        |

| PI6ULS5V9509XTEX | XT           | Lead free and Green UQFN1.6x1.6-8L,<br>Tape & Reel |

#### Note:

- E = Pb-free

- Adding X Suffix= Tape/Reel

#### Pericom Semiconductor Corporation • 1-800-435-2336 • www.pericom.com

Pericom reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. Pericom does not assume any responsibility for use of any circuitry described other than the circuitry embodied in Pericom product. The company makes no representations that circuitry described herein is free from patent infringement or other rights, of Pericom.