# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **PI74SSTU32864A**

## 25-Bit 1:1 or 14-Bit 1:2 Configurable Registered Buffer

## Features

- PI74SSTU32864A is designed for low-voltage operation,  $V_{DD} = 1.8V$

- Supports Low Power Standby Operation

- Enhanced Signal Integrity for 1 and 2 Rank Modules

- All Inputs are SSTL\_18 Compatible, except RST, C0, C1, which are LVCMOS.

- · Output drivers are optimized to drive DDR2 DIMM loads

- Designed for DDR2 Memory

- Packaging (Pb-free & Green available):

-96 Ball LFBGA (NB)

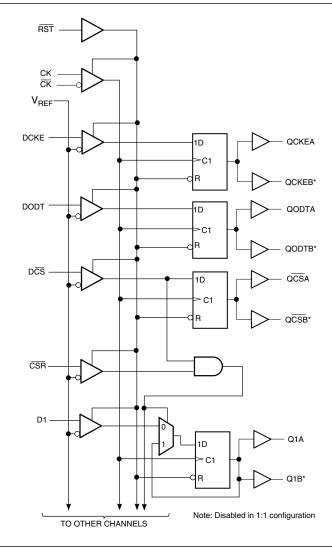

## Block Diagram 1:2 Mode (Positive Logic)

## Description

Pericom Semiconductor's PI74SSTU32864A logic circuit is produced using advanced CMOS technology. This 25-Bit 1:1 or 14-Bit 1:2 configurable registered buffer is designed for 1.7V to 1.9V V<sub>DD</sub> operation.

All clock and data inputs are compatible with the JEDEC standard for SSTL\_18. The control inputs are LVCMOS. All outputs are 1.8V LVCMOS drivers that have been optimized to drive the DDR2 DIMM load.

The SSTU32864A operates from a differential clock ( $\overline{CK}$  and CK). Data is registered at the crossing of CK going high, and  $\overline{CK}$  going low.

The C0 input controls the pinout configuration of the 1:2 pinout from A configuration (when LOW) to B configuration (when HIGH). The C1 input controls the pinout configuration for 25-Bit 1:1 (when LOW) to 14-Bit 1:2 (when HIGH).

The device supports low-power standby operation. When the reset input ( $\overline{RST}$ ) is low, the differential input receivers are disabled and undriven (floating) data, clock and reference voltage ( $V_{REF}$ ) inputs are allowed. In addition , when  $\overline{RST}$  is low, all registers are reset, and all outputs are forced low. The LVCMOS  $\overline{RST}$  and Cn inputs must always be held at a valid logic high or low level.

To ensure defined outputs from the register before a stable clock has been supplied,  $\overline{\text{RST}}$  must be held in the low state during power up.

In the DDR-II RDIMM application,  $\overline{RST}$  is specified to be completely asynchronous with respect to CK and  $\overline{CK}$ . Therefore, no timing relationship can be guaranteed between the two. When entering reset, the register will be cleared and the outputs will be driven low quickly, relative to the time to disable the differential input receivers. However, when coming out of reset, the register will become active quickly, relative to the time to enable the differential input receivers.

As long as the data inputs are low, and the clock is stable during the time from the low-to-high transition of  $\overline{\text{RST}}$  until the input receivers are fully enabled, the design of the SSTU32864A must ensure that the outputs remain low, thus ensuring no glitches on the output.

The device monitors both  $\overline{\text{DCS}}$  and  $\overline{\text{CSR}}$  inputs and will gate the Qn outputs from changing states when both  $\overline{\text{DCS}}$  and  $\overline{\text{CSR}}$  inputs are high. If either  $\overline{\text{DCS}}$  or  $\overline{\text{CSR}}$  input is low, the Qn outputs will function normally. The  $\overline{\text{RST}}$  input has priority over the  $\overline{\text{DCS}}$  and  $\overline{\text{CSR}}$  control will force the outputs low. If the  $\overline{\text{DCS}}$  control functionality is not desired, then the CSR input can be hardwired to ground, in which case, the set-up time requirement for  $\overline{\text{DCS}}$  would be the same as for the other D data inputs.

|   | 1    | 2                       | 3                | 4               | 5    | 6   |

|---|------|-------------------------|------------------|-----------------|------|-----|

| Α | DCKE | NC                      | V <sub>REF</sub> | V <sub>DD</sub> | QCKE | NC  |

| В | D2   | D15                     | GND              | GND             | Q2   | Q15 |

| С | D3   | D16                     | V <sub>DD</sub>  | V <sub>DD</sub> | Q3   | Q15 |

| D | DODT | NC                      | GND              | GND             | QODT | NC  |

| Е | D5   | D17                     | V <sub>DD</sub>  | V <sub>DD</sub> | Q5   | Q17 |

| F | D6   | D18                     | GND              | GND             | Q6   | Q18 |

| G | NC   | RST                     | V <sub>DD</sub>  | V <sub>DD</sub> | C1   | C0  |

| Н | СК   | $D\overline{CS}$        | GND              | GND             | QCS  | NC  |

| J | CK   | $\overline{\text{CSR}}$ | V <sub>DD</sub>  | V <sub>DD</sub> | ZOH  | ZOL |

| К | D8   | D19                     | GND              | GND             | Q8   | Q19 |

| L | D9   | D20                     | V <sub>DD</sub>  | V <sub>DD</sub> | Q9   | Q20 |

| Μ | D10  | D21                     | GND              | GND             | Q10  | Q21 |

| Ν | D11  | D22                     | V <sub>DD</sub>  | V <sub>DD</sub> | Q11  | Q22 |

| Р | D12  | D23                     | GND              | GND             | Q12  | Q23 |

| R | D13  | D24                     | V <sub>DD</sub>  | V <sub>DD</sub> | Q13  | Q24 |

| Т | D14  | D25                     | V <sub>REF</sub> | V <sub>DD</sub> | Q14  | Q25 |

## Pin Configuration 1:1 Register (C0 = 0, C1 = 0)

## Pin Configuration 1:2 Register (C0 = 0, C1 = 1)

|   | 1    | 2                       | 3                | 4               | 5     | 6     |

|---|------|-------------------------|------------------|-----------------|-------|-------|

| Α | DCKE | NC                      | V <sub>REF</sub> | V <sub>DD</sub> | QCKEA | QCKEB |

| В | D2   | NC                      | GND              | GND             | Q2A   | Q2B   |

| С | D3   | NC                      | V <sub>DD</sub>  | V <sub>DD</sub> | Q3A   | QODTB |

| D | DODT | NC                      | GND              | GND             | QODTA | Q4B   |

| Е | D5   | NC                      | V <sub>DD</sub>  | V <sub>DD</sub> | Q5A   | Q5B   |

| F | D6   | NC                      | GND              | GND             | Q6A   | Q6B   |

| G | NC   | RST                     | V <sub>DD</sub>  | V <sub>DD</sub> | C1    | C0    |

| Н | СК   | $D\overline{CS}$        | GND              | GND             | QCSA  | QCSB  |

| J | CK   | $\overline{\text{CSR}}$ | V <sub>DD</sub>  | V <sub>DD</sub> | ZOH   | ZOL   |

| К | D8   | NC                      | GND              | GND             | Q8A   | Q8B   |

| L | D9   | NC                      | V <sub>DD</sub>  | V <sub>DD</sub> | Q9A   | Q9B   |

| Μ | D10  | NC                      | GND              | GND             | Q10A  | Q10B  |

| Ν | D11  | NC                      | V <sub>DD</sub>  | V <sub>DD</sub> | Q11A  | Q11B  |

| Р | D12  | NC                      | GND              | GND             | Q12A  | Q12B  |

| R | D13  | NC                      | V <sub>DD</sub>  | V <sub>DD</sub> | Q13A  | Q13B  |

| Т | D14  | NC                      | V <sub>REF</sub> | V <sub>DD</sub> | Q14A  | Q14B  |

| The Configuration 1.2 Register (C0 – 1, C1 – 1) |      |                         |                  |                 |       |       |  |

|-------------------------------------------------|------|-------------------------|------------------|-----------------|-------|-------|--|

|                                                 | 1    | 2                       | 3                | 4               | 5     | 6     |  |

| Α                                               | D1   | NC                      | V <sub>REF</sub> | V <sub>DD</sub> | Q1A   | QB    |  |

| В                                               | D2   | NC                      | GND              | GND             | Q2A   | Q2B   |  |

| С                                               | D3   | NC                      | V <sub>DD</sub>  | V <sub>DD</sub> | Q3A   | Q3B   |  |

| D                                               | D4   | NC                      | GND              | GND             | Q4A   | Q4B   |  |

| E                                               | D5   | NC                      | V <sub>DD</sub>  | V <sub>DD</sub> | Q5A   | Q5B   |  |

| F                                               | D6   | NC                      | GND              | GND             | Q6A   | Q6B   |  |

| G                                               | NC   | RST                     | V <sub>DD</sub>  | V <sub>DD</sub> | C1    | C0    |  |

| Н                                               | СК   | DCS                     | GND              | GND             | QTSA  | QCSB  |  |

| J                                               | CK   | $\overline{\text{CSR}}$ | V <sub>DD</sub>  | V <sub>DD</sub> | ZOH   | ZOL   |  |

| К                                               | D8   | NC                      | GND              | GND             | Q8A   | Q8B   |  |

| L                                               | D9   | NC                      | V <sub>DD</sub>  | V <sub>DD</sub> | Q9A   | Q9B   |  |

| Μ                                               | D10  | NC                      | GND              | GND             | Q10A  | Q10B  |  |

| Ν                                               | DODT | NC                      | V <sub>DD</sub>  | V <sub>DD</sub> | QODTA | QODTB |  |

| Р                                               | D12  | NC                      | GND              | GND             | Q12A  | Q12B  |  |

| R                                               | D13  | NC                      | V <sub>DD</sub>  | V <sub>DD</sub> | Q13A  | Q13B  |  |

| Т                                               | DCKE | NC                      | V <sub>REF</sub> | V <sub>DD</sub> | QCKEA | QCKEB |  |

## Pin Configuration 1:2 Register (C0 = 1, C1 = 1)

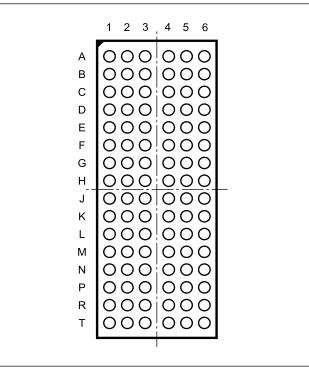

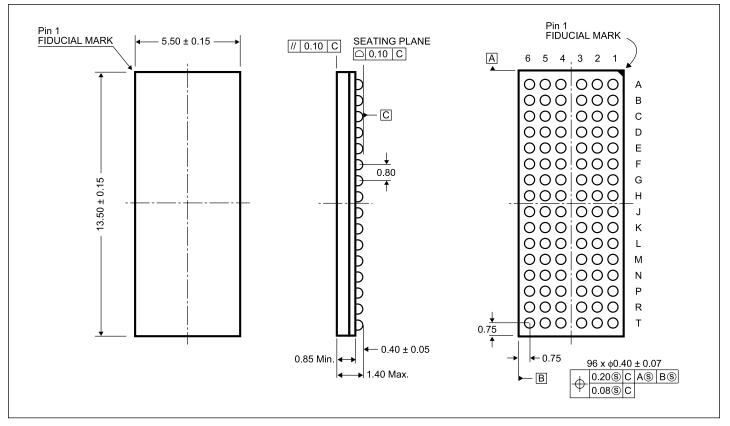

#### NB 96-ball LFBGA (MO-205CC) Top View

## **Terminal Functions**

| Name                                           | Description                                                                                                               | Characteristics          |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------|

| GND                                            | Ground                                                                                                                    | Ground Input             |

| V <sub>DD</sub>                                | Power Supply                                                                                                              | 1.8V nominal             |

| V <sub>REF</sub>                               | Input Reference Voltage                                                                                                   | 0.9V nominal             |

| Z <sub>OH</sub>                                | Reserved for future use                                                                                                   | Input                    |

| Z <sub>OL</sub>                                | Reserved for future use                                                                                                   | Input                    |

| CK                                             | Positive master clock input                                                                                               | Differential Clock input |

| CK                                             | Negative master clock input                                                                                               | Differential Clock input |

| C0, C1                                         | Configuration control inputs                                                                                              | LVCMOS inputs            |

| RST                                            | Asynchronous reset input - resets registers and disables $V_{\text{REF}}$ data and clock differential - input receivers   | LVCMOS inputs            |

| $\overline{\text{CSR}}, \overline{\text{DCS}}$ | Chip select inputs disables D1-D24 outputs switching when both inputs are high                                            | SSTL_18 input            |

| D1, D25                                        | Data input - clocked in on the crossing of the rising edge of CK and the falling edge of $\overline{CK}$                  | SSTL_18 input            |

| DODT                                           | The outputs of this register bit will not be suspended by the $\overline{\text{DCS}}$ and $\overline{\text{CSR}}$ control | SSTL_18 input            |

| DCKE                                           | The outputs of this register bit will not be suspended by the $D\overline{CS}$ and $\overline{CSR}$ control               | SSTL_18 input            |

| Q1-Q25                                         | Data outputs that are suspended by the $D\overline{CS}$ and $\overline{CSR}$ control                                      | 1.8V CMOS                |

| QCS                                            | Data output that will not be suspended by the $\overline{\text{DCS}}$ and $\overline{\text{CSR}}$ controll                | 1.8V CMOS                |

| QODT                                           | Data output that will not be suspended by the $\overline{\text{DCS}}$ and $\overline{\text{CSR}}$ controll                | 1.8V CMOS                |

| QCKE                                           | Data output that will not be suspended by the $D\overline{CS}$ and $\overline{CSR}$ controll                              | 1.8V CMOS                |

## Function Table (each flip flop)

| Inputs |               |               |               |               |                   | Outputs |     |               |

|--------|---------------|---------------|---------------|---------------|-------------------|---------|-----|---------------|

| RST    | DCS           | CSR           | СК            | CK            | Dn, DODT,<br>DCKE | Qn      | QCS | QODT,<br>QCKE |

| Н      | L             | L             | 1             | $\downarrow$  | L                 | L       | L   | L             |

| Н      | L             | L             | 1             | $\downarrow$  | Н                 | Н       | L   | Н             |

| Н      | L             | L             | L or H        | L or H        | Х                 | Q0      | Q0  | Q0            |

| Н      | L             | Н             | 1             | $\downarrow$  | L                 | L       | L   | L             |

| Н      | L             | Н             | 1             | $\downarrow$  | Н                 | Н       | L   | Н             |

| Н      | L             | Н             | L or H        | L or H        | Х                 | Q0      | Q0  | Q0            |

| Н      | Н             | L             | 1             | $\downarrow$  | L                 | L       | Н   | L             |

| Н      | Н             | L             | 1             | $\downarrow$  | Н                 | Н       | Н   | Н             |

| Н      | Н             | L             | L or H        | L or H        | Х                 | Q0      | Q0  | Q0            |

| Н      | Н             | Н             | 1             | $\downarrow$  | L                 | Q0      | Н   | L             |

| Н      | Н             | Н             | 1             | $\downarrow$  | Н                 | Q0      | Н   | Н             |

| Н      | Н             | Н             | L or H        | L or H        | Х                 | Q0      | Q0  | Q0            |

| L      | X or floating     | L       | L   | L             |

#### **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature65°C to +150°C                                                    |

|--------------------------------------------------------------------------------------|

| Supply Voltage Range, V <sub>DD</sub> 0.5V to 2.5V                                   |

| Input Voltage Range, V <sub>I</sub> : (See Notes 2 and 3):–0.5V to 2.5V              |

| Output Voltage Range, $V_0$ (See Notes 2 and 3)–0.5V to $V_{DD}$ + 0.5V              |

| Input Clamp current, $I_{IK}$ ( $V_I < 0$ or $V_I = V_{DD}$ )                        |

| Output Clamp current, $I_{OK}$ ( $V_O < 0$ or $V_O > V_{DD}$ ) ±50mA                 |

| Continous Output Current, $I_O (V_O = 0 \text{ to } V_{DD}) \dots \pm 50 \text{ mA}$ |

| Continous Current through each $V_{DD}$ or GND ±100mA                                |

|                                                                                      |

#### Notes:

- Stresses greater than those listed under MAXIMUM RAINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

- 3. This value is limited to 2.5V maximum

## **Recommended Operating Conditions**<sup>(1)</sup>

| Parameters       | Descrition                     |                                         | Min.                   | Nom.                   | Max.                    | Units |

|------------------|--------------------------------|-----------------------------------------|------------------------|------------------------|-------------------------|-------|

| V <sub>DD</sub>  | Supply Voltage                 |                                         | 1.7                    |                        | 1.9                     |       |

| V <sub>REF</sub> | Reference Voltage              |                                         | 0.49 x V <sub>DD</sub> | 0.50 x V <sub>DD</sub> | 0.51 x V <sub>DD</sub>  |       |

| V <sub>TT</sub>  | Termination Voltage            |                                         | V <sub>REF</sub> -40mA | V <sub>REF</sub>       | V <sub>REF</sub> -40mA  |       |

| VI               | Input Voltage                  |                                         | 0                      |                        | V <sub>DD</sub>         |       |

| V <sub>IH</sub>  | AC High - Level Input Voltage  |                                         | V <sub>REF</sub> 250mV |                        |                         |       |

| V <sub>IL</sub>  | AC Low- Level Input Voltage    | Data                                    |                        |                        | V <sub>REF</sub> -250mV | V     |

| V <sub>IH</sub>  | DC High - Level Input Voltage  | Inputs                                  | V <sub>REF</sub> 125mV |                        |                         |       |

| V <sub>IL</sub>  | DC Low- Level Input Voltage    |                                         |                        |                        | V <sub>REF</sub> -125mV |       |

| V <sub>IH</sub>  | High Level Input Voltage       | $\overline{RST}$ , CN                   | 0.65 x V <sub>DD</sub> |                        |                         |       |

| V <sub>IL</sub>  | Low Level Input Voltage        | $\begin{bmatrix} KSI, CN \end{bmatrix}$ |                        |                        | 0.35 x V <sub>DD</sub>  |       |

| V <sub>ICR</sub> | Common-mode input Voltage      |                                         | 0.675                  |                        | 1.125                   |       |

| V <sub>ID</sub>  | Differential Input Voltage     | CK, CK                                  | 600                    |                        |                         | mV    |

| I <sub>OH</sub>  | High-Level Output Current      | -                                       |                        |                        | -8                      | 4     |

| I <sub>OL</sub>  | Low-Level Output Current       |                                         |                        |                        | -8                      | mA    |

| TA               | Operating Free-air Temperature |                                         | 0                      |                        | 70                      | °C    |

#### Notes:

1. The  $\overline{\text{RST}}$  and Cn inputs of the device must be held at valid levels (not floating) to ensure proper device operation. The differential inputs must not be floating, unless  $\overline{\text{RST}}$  is low.

| Parameters       | Description                                                                                                                                                                                                                   | Test Conditions                                                                                                                                                                                                 |  | V <sub>DD</sub> Min. Nom. Max. |     |     | Max.                 | Units               |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--------------------------------|-----|-----|----------------------|---------------------|

| V <sub>OH</sub>  |                                                                                                                                                                                                                               | $I_{OH} = -6 \text{ mA}$                                                                                                                                                                                        |  | 1.7V                           | 1.2 |     |                      | v                   |

| V <sub>OL</sub>  |                                                                                                                                                                                                                               | $I_{OL} = 6 \text{ mA}$                                                                                                                                                                                         |  | 1.7V                           |     |     | 0.5                  | v                   |

| II               | All inputs                                                                                                                                                                                                                    | $V_{I} = V_{DD}$ or GND                                                                                                                                                                                         |  |                                |     |     | ±5                   |                     |

| I <sub>DD</sub>  | Static Stand-by                                                                                                                                                                                                               | $\overline{\text{RST}} = \text{GND}$                                                                                                                                                                            |  | 1.9V                           |     |     | 100                  | μA                  |

|                  | Static Operating                                                                                                                                                                                                              | $\overline{\text{RST}} = V_{\text{DD}}, V_{\text{I}} = V_{\text{IH}(\text{AC})} \text{ or } V_{\text{IL}(\text{AC})}$                                                                                           |  |                                |     |     | 40                   | mA                  |

|                  | Dynamic Operating<br>Clock only                                                                                                                                                                                               | $\overline{RST} = V_{DD}, V_I = V_{IH(AC)}, \text{ or}$<br>$V_{IL(AC)} CK \text{ and } \overline{CK} \text{ switching } 50\%$<br>duty cycle                                                                     |  |                                |     | 28  |                      | μA/<br>clock<br>MHz |

| I <sub>DDD</sub> | Dynamic Operating - per<br>each data input, 1:1 mode                                                                                                                                                                          | $\overline{RST} = V_{DD}, V_I = V_{IH(AC)}, \text{ or}$ $V_{IL(AC)} CK \text{ and } \overline{CK} \text{ switching } 50\%$ duty cycle. One data input switch-<br>ing at half clock frequency, 50%<br>duty cycle |  | 1.8V                           | 18  |     |                      | μA/<br>clock        |

|                  | Dynamic Operating - per<br>each data input, 1:2 mode $\overline{RST} = V_{DD}, V_I = V_{IH(AC)}, orV_{IL(AC)} CK and \overline{CK} switching 50%duty cycle. One data input switch-ing at half clock frequency, 50%duty cycle$ |                                                                                                                                                                                                                 |  | 36                             |     |     | MHz<br>data<br>input |                     |

|                  | Data inputsp                                                                                                                                                                                                                  | $V_I = V_{REF} \pm 250 mV$                                                                                                                                                                                      |  |                                | 2.5 |     | 3.5                  |                     |

| CI               | CK and $\overline{CK}$                                                                                                                                                                                                        | $V_{ICR} = 0.9V, V_{ID} = 600mV$                                                                                                                                                                                |  |                                | 2   |     | 3                    | pF                  |

|                  | RST                                                                                                                                                                                                                           | $V_{I} = V_{DD}$ or GND                                                                                                                                                                                         |  |                                |     | 2.5 |                      |                     |

#### Electrical Characteristics Over Recommended Operating Free Air Temperature range

Notes:

1. The vendor must supply this value for full device description.

#### Timing Requirements Over Recommended Operating Free Air Temperature range (See Figure 1)

| Parameter                       | Description                                      |                                                                                                   |     | Max | Units |

|---------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------|-----|-----|-------|

| f <sub>clock</sub>              | Clock frequency                                  |                                                                                                   |     | 270 | MHz   |

| t <sub>W</sub>                  | Pulse Duration, CK, CK, High or low              |                                                                                                   |     |     |       |

| t <sub>act</sub> <sup>(1)</sup> | Differential inputs active time <sup>(1)</sup>   |                                                                                                   |     | 10  |       |

| tinact <sup>(1)</sup>           | Differential inputs inactive time <sup>(2)</sup> |                                                                                                   |     | 15  |       |

|                                 |                                                  | $D\overline{CS}$ before $CK\uparrow$ , $\overline{CK}\downarrow$ , $\overline{CSR}$ high          | 0.7 |     | ns    |

| t <sub>su</sub>                 | Setup time                                       | D $\overline{CS}$ before CK $\uparrow$ , $\overline{CK}\downarrow$ , $\overline{CSR}$ low         | 0.5 |     |       |

|                                 |                                                  | $\overline{\text{CSR}}$ DODT, CKE anddata before $\overline{\text{CK}\uparrow}$ , CK $\downarrow$ | 0.5 |     |       |

| th                              | Hold Time                                        | $D\overline{CS}$ , CSR DODT, CKE adn data before CK $\uparrow$ , $\overline{CK}\downarrow$        | 0.5 |     |       |

#### Notes

1. This parameter is not necessarily production tested.

2. Data and  $V_{\text{REF}}$  inputs must be a low minimum time of  $t_{\text{act}}$  max, after RST is taken high.

3. Data and clock inputs must be held at valid levels (not floating) a minimum time of t<sub>inact</sub> max after RST is taken low.

| Switching Characteristics Over Recommended | Operating Free Air Temperature range (See Figure 1) |

|--------------------------------------------|-----------------------------------------------------|

|--------------------------------------------|-----------------------------------------------------|

| De verse stans                                       | From                   | То       | V <sub>DD</sub> = 1 | T.L.s.*4 m |       |

|------------------------------------------------------|------------------------|----------|---------------------|------------|-------|

| Parameters                                           | (Input)                | (Output) | Min.                | Max.       | Units |

| f <sub>max</sub>                                     |                        |          | 270                 |            | MHz   |

| t <sub>pdm</sub>                                     | CK and $\overline{CK}$ | Q        | 1.41                | 2.15       |       |

| tpdmss<br>(simultaneous switching) <sup>(1, 2)</sup> | CK and $\overline{CK}$ | Q        |                     | 2.35       | ns    |

| t <sub>RPHL</sub>                                    | RST                    | Q        | 0                   | 3          |       |

Note:

1. Includes 350ps test load transmission-line delay.

2. This parameter is not necessarily production tested.

| Output Edge Rates O | ver Recommended Operating | Free Air Temperature | range (See Figure 2) |

|---------------------|---------------------------|----------------------|----------------------|

|                     |                           |                      |                      |

| Parameters    | $V_{DD} = 1.8V \pm 0.1V$ |      | Units |

|---------------|--------------------------|------|-------|

|               | Min.                     | Max. | Units |

| dV/dt_r       | 1                        | 4    |       |

| dV/dt_f       | 1                        | 4    | V/ns  |

| $dV/dt^{(1)}$ |                          | 1    |       |

Notes:

1. Difference between  $dV/dt_r$  (rising edge rate) and  $dV/dt_f$  (falling edge rate).

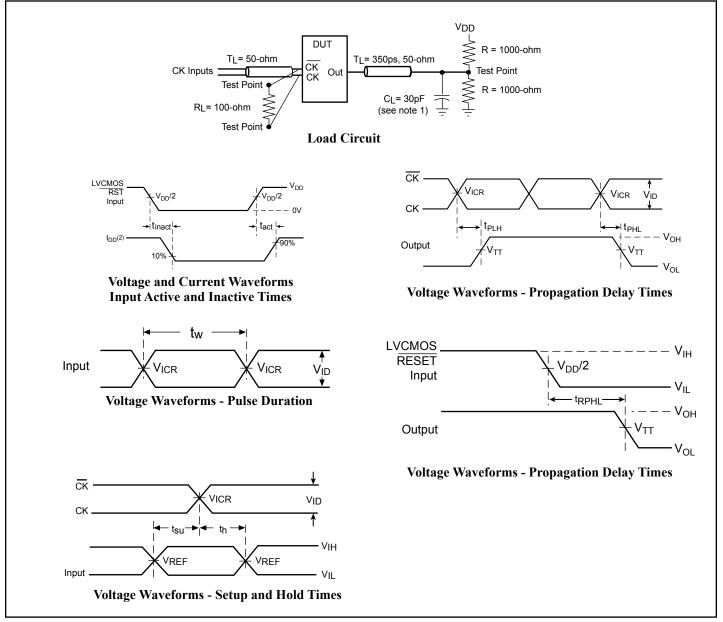

#### **Test Circuit and Switching Waveforms**

Figure 1. Parameter Measurement Information ( $V_{DD} = 1.8V \pm 0.1V$ )

#### Notes:

- $1. \quad C_L \ includes \ probe \ and \ jig \ capacitance$

- 2.  $I_{DD}$  tested with clock and data inputs held at  $V_{DD}$  or GND and  $I_O = 0mA$

- 3. All input pulses are supplied by generators having the following characteristics: Pulse Repertition Rate  $\geq$  10 MHz, ZO = 50 $\Omega$ , input slew rate = 1V/ns  $\pm$  20% (unless otherwise specified).

- 4. The outputs are measured one at a time with one transition per measurement.

- 5.  $V_{\text{REF}} = V_{\text{DD}}/2$

- 6.  $V_{IH} = V_{REF} + 250 \text{mV}$  (ac voltage levels) for differential inputs.  $V_{IH} = V_{DD}$  for LVCMOS input.

- 7.  $V_{IL} = V_{REF}$  -250mV (ac voltage levels) for differential inputs.  $V_{IL} = GND$  for LVCMOS input.

- 8.  $V_{ID} = 600 \text{mV}$

- 9.  $t_{PLH}$  and  $t_{PHL}$  are the same as  $t_{pdm}$ .

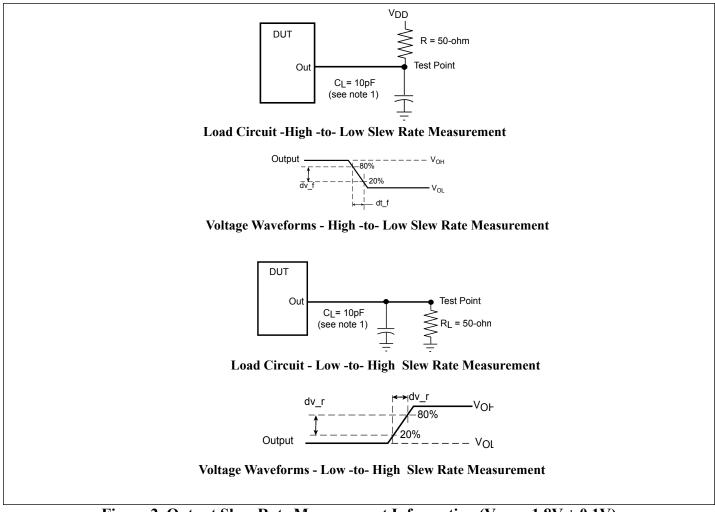

## Figure 2. Output Slew-Rate Measurement Information ( $V_{DD} = 1.8V \pm 0.1V$ )

#### Notes:

- $1. \quad C_L \ includes \ probe \ and \ jig \ capacitance$

- 2. All input pulses are supplied by generators having the following characteristics: PRR  $\leq 10$  MHz, ZO = 50 $\Omega$ , input slew rate = 1 V/ns  $\pm 20\%$  (unless otherwise specified).

## Packaging Mechanical: 96-ball LFBGA (NB)

#### **Ordering Information**

| Ordering Code     | Package Code | Package Type                   |

|-------------------|--------------|--------------------------------|

| PI74SSTU32864ANB  | NB           | 96-Ball LFBGA                  |

| PI74SSTU32864ANBE | NB           | Pb-free & Green, 96-Ball LFBGA |

Notes:

1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

2. Number of Transistors = TBD