# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## PI7C7300D 3-PORT PCI-to-PCI BRIDGE Revision 1.01

3545 North 1<sup>ST</sup> Street, San Jose, CA 95134 Telephone: 1-877-PERICOM (1-877-737-4266) FAX: 408-435-1100 Internet: <u>http://www.pericom.com</u>

#### LIFE SUPPORT POLICY

Pericom Semiconductor Corporation's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of PSC.

1. Life support devices or systems are devices or systems which:

a) are intended for surgical implant into the body or

b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. Pericom Semiconductor Corporation reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. Pericom Semiconductor does not assume any responsibility for use of any circuitry described other than the circuitry embodied in a Pericom Semiconductor product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Pericom Semiconductor Corporation.

All other trademarks are of their respective companies.

#### **REVISION HISTORY**

| Revision | Date       | Description                                  |  |

|----------|------------|----------------------------------------------|--|

| 1.00     | 09/21/2004 | Initial release of datasheet                 |  |

| 1.01     | 11/21/2005 | Removed "Advance Information" from datasheet |  |

|          |            | Renamed pin Y4 from BYPASS to BY_PASS        |  |

This page intentionally left blank.

## TABLE OF CONTENTS

| 1 | INTRODUCTION                                                                                | . 11 |

|---|---------------------------------------------------------------------------------------------|------|

| 2 | BLOCK DIAGRAM                                                                               | . 12 |

| 3 | SIGNAL DEFINITIONS                                                                          | . 13 |

|   | 3.1 SIGNAL TYPES                                                                            |      |

|   | 3.2 PRIMARY BUS INTERFACE SIGNALS                                                           |      |

|   | 3.3 SECONDARY BUS INTERFACE SIGNALS                                                         |      |

|   | 3.4 CLOCK SIGNALS                                                                           |      |

|   | 3.5 MISCELLANEOUS SIGNALS                                                                   |      |

|   | 3.6 COMPACT PCI HOT-SWAP SIGNALS                                                            |      |

|   | 3.7 JTAG BOUNDARY SCAN SIGNALS                                                              |      |

|   | 3.8 POWER AND GROUND                                                                        |      |

|   | 3.9 PI7C7300D PBGA PIN LIST                                                                 |      |

| 4 | PCI BUS OPERATION                                                                           |      |

|   | 4.1 TYPES OF TRANSACTIONS                                                                   |      |

|   | 4.2 SINGLE ADDRESS PHASE                                                                    |      |

|   | 4.3 DUAL ADDRESS PHASE                                                                      |      |

|   | 4.4 DEVICE SELECT (DEVSEL#) GENERATION                                                      |      |

|   | 4.5 DATA PHASE                                                                              |      |

|   | 4.6 WRITE TRANSACTIONS                                                                      |      |

|   | 4.6.2 MEMORY WRITE AND INVALIDATE TRANSACTIONS                                              |      |

|   | 4.6.3 DELAYED WRITE TRANSACTIONS                                                            |      |

|   | 4.6.4 WRITE TRANSACTION ADDRESS BOUNDARIES                                                  |      |

|   | 4.6.5 BUFFERING MULTIPLE WRITE TRANSACTIONS                                                 |      |

|   | 4.6.6 FAST BACK-TO-BACK WRITE TRANSACTIONS                                                  |      |

|   | 4.7 READ TRANSACTIONS                                                                       |      |

|   | 4.7.1 PREFETCHABLE READ TRANSACTIONS                                                        |      |

|   | 4.7.2 NON-PREFETCHABLE READ TRANSACTIONS                                                    | . 27 |

|   | 4.7.3 READ PREFETCH ADDRESS BOUNDARIES                                                      | . 28 |

|   | 4.7.4 DELAYED READ REQUESTS                                                                 |      |

|   | 4.7.5 DELAYED READ COMPLETION WITH TARGET                                                   |      |

|   | 4.7.6 DELAYED READ COMPLETION ON INITIATOR BUS                                              |      |

|   | 4.7.7 FAST BACK-TO-BACK READ TRANSACTION                                                    |      |

|   | 4.8 CONFIGURATION TRANSACTIONS                                                              |      |

|   | 4.8.1 TYPE 0 ACCESS TO PI7C7300D                                                            |      |

|   | 4.8.2 TYPE 1 TO TYPE 0 CONVERSION<br>4.8.3 TYPE 1 TO TYPE 1 FORWARDING.                     |      |

|   |                                                                                             |      |

|   | <ul> <li>4.8.4 SPECIAL CYCLES</li></ul>                                                     |      |

|   | 4.9 TRANSACTION TERMINATION                                                                 |      |

|   | 4.9.1 MASTER TERMINATION INITIATED BY PI/C/300D<br>4.9.2 MASTER ABORT RECEIVED BY PI/C/300D |      |

|   | 4.9.2 MASTER ABORT RECEIVED BT F1/C/300D                                                    |      |

|   | 4.9.4 TARGET TERMINATION RECEIVED BY PI7C7300D                                              |      |

|   | 4.10 CONCURRENT MODE OPERATION                                                              |      |

| 5 | ADDRESS DECODING                                                                            |      |

|   |                                                                                             |      |

| 5.       | 1 ADDRESS RANGES                                               | 43   |

|----------|----------------------------------------------------------------|------|

| 5.2      | 2 I/O ADDRESS DECODING                                         | 43   |

|          | 5.2.1 I/O BASE AND LIMIT ADDRESS REGISTER                      | . 44 |

|          | 5.2.2 ISA MODE                                                 | . 45 |

| 5.       | 3 MEMORY ADDRESS DECODING                                      | 45   |

|          | 5.3.1 MEMORY-MAPPED I/O BASE AND LIMIT ADDRESS REGISTERS       | . 46 |

|          | 5.3.2 PREFETCHABLE MEMORY BASE AND LIMIT ADDRESS REGISTERS     | . 47 |

| 5.4      | 4 VGA SUPPORT                                                  | 48   |

|          | 5.4.1 VGA MODE                                                 | . 48 |

|          | 5.4.2 VGA SNOOP MODE                                           | . 48 |

| 6        | TRANSACTION ORDERING                                           | . 49 |

| 6.       | 1 TRANSACTIONS GOVERNED BY ORDERING RULES                      | 49   |

| 6.       |                                                                |      |

| 6.       | 3 ORDERING RULES                                               | 50   |

| 6.4      | 4 DATA SYNCHRONIZATION                                         | 52   |

| 7        | ERROR HANDLING                                                 | 52   |

| 7.       | 1 ADDRESS PARITY ERRORS                                        | 52   |

| 7.       |                                                                |      |

|          | 7.2.1 CONFIGURATION WRITE TRANSACTIONS TO CONFIGURATION SPACE  |      |

|          | 7.2.2 READ TRANSACTIONS                                        |      |

|          | 7.2.3 DELAYED WRITE TRANSACTIONS                               |      |

|          | 7.2.4 POSTED WRITE TRANSACTIONS                                |      |

| 7.       |                                                                |      |

| 7.4      |                                                                |      |

| 8        | EXCLUSIVE ACCESS                                               |      |

| 8.       | 1 CONCURRENT LOCKS                                             | 64   |

| 8.       |                                                                |      |

|          | 8.2.1 LOCKED TRANSACTIONS IN DOWSTREAM DIRECTION               |      |

|          | 8.2.2 LOCKED TRANSACTION IN UPSTREAM DIRECTION                 |      |

| 8.       |                                                                |      |

|          | PCI BUS ARBITRATION                                            |      |

| 9.       |                                                                |      |

| 9.<br>9. |                                                                |      |

|          | 9.2.1 SECONDART FEI BUS ARBITRATION USING THE INTERNAL ARBITER |      |

|          | 9.2.1 SECONDART DUSARDITRATION USING THE INTERNAL ARDITER      |      |

|          | 9.2.3 SECONDARY BUS ARBITRATION USING AN EXTERNAL ARBITER      | . 07 |

|          | 9.2.4 BUS PARKING                                              |      |

| 10       | COMPACT PCI HOT SWAP                                           |      |

| 10       |                                                                | . 70 |

| 11       | CLOCKS                                                         |      |

| 11       |                                                                |      |

| 11       | .2 SECONDARY CLOCK OUTPUTS                                     | . 70 |

| 12       | RESET                                                          | . 71 |

| 12       | 2.1 PRIMARY INTERFACE RESET                                    |      |

| 12       |                                                                |      |

|          |                                                                |      |

| 13 SUPP  | ORTED COMMANDS                                                    |       |

|----------|-------------------------------------------------------------------|-------|

| 13.1 PRI | MARY INTERFACE                                                    | 72    |

|          | CONDARY INTERFACE                                                 |       |

|          |                                                                   |       |

| 14 CONE  | FIGURATION REGISTERS                                              |       |

| 14.1 CO  | NFIGURATION REGISTER 1 AND 2                                      |       |

| 14.1.1   | VENDOR ID REGISTER – OFFSET 00h                                   |       |

| 14.1.2   | DEVICE ID REGISTER – OFFSET 00h                                   |       |

| 14.1.3   | COMMAND REGISTER – OFFSET 04h                                     |       |

| 14.1.4   | STATUS REGISTER – OFFSET 04h                                      |       |

| 14.1.5   | REVISION ID REGISTER – OFFSET 08h                                 | 78    |

| 14.1.6   | CLASS CODE REGISTER – OFFEST 08h                                  |       |

| 14.1.7   | CACHE LINE SIZE REGISTER – OFFSET 0Ch                             | 78    |

| 14.1.8   | PRIMARY LATENCY TIMER REGISTER – OFFSET 0Ch                       | 78    |

| 14.1.9   | HEADER TYPE REGISTER – OFFSET 0Ch                                 | 79    |

| 14.1.10  | PRIMARY BUS NUMBER REGISTER – OFFSET 18h                          |       |

| 14.1.11  | SECONDARY (S1 or S2) BUS NUMBER REGISTER – OFFSET 18h             | 79    |

| 14.1.12  | SUBORDINATE (S1 or S2) BUS NUMBER REGISTER – OFFSET 18h           | 79    |

| 14.1.13  | SECONDARY LATENCY TIMER REGISTER – OFFSET 18h                     | 79    |

| 14.1.14  | I/O BASE REGISTER – OFFSET 1Ch                                    | 80    |

| 14.1.15  | I/O LIMIT REGISTER – OFFSET 1Ch                                   |       |

| 14.1.16  | SECONDARY STATUS REGISTER – OFFSET 1Ch                            |       |

| 14.1.17  | MEMORY BASE REGISTER – OFFSET 20h                                 | 81    |

| 14.1.18  | MEMORY LIMIT REGISTER – OFFSET 20h                                |       |

| 14.1.19  | PREFETCHABLE MEMORY BASE REGISTER – OFFSET 24h                    |       |

| 14.1.20  | PREFETCHABLE MEMORY LIMIT REGISTER – OFFSET 24h                   |       |

| 14.1.21  | PREFETCHABLE MEMORY BASE ADDRESS UPPER 32-BITS REGISTER – O       | FFSET |

| 28h      |                                                                   |       |

| 14.1.22  | PREFETCHABLE MEMORY LIMIT ADDRESS UPPER 32-BITS REGISTER – C      |       |

| 2Ch      |                                                                   |       |

| 14.1.23  | I/O BASE ADDRESS UPPER 16-BITS REGISTER – Offset 30h              |       |

| 14.1.24  | I/O LIMIT ADDRESS UPPER 16-BITS REGISTER – OFFSET 30h             |       |

| 14.1.25  | ECP POINTER REGISTER – OFFSET 34h                                 |       |

| 14.1.26  | BRIDGE CONTROL REGISTER – OFFSET 3Ch                              |       |

| 14.1.27  | DIAGNOSTIC / CHIP CONTROL REGISTER – OFFSET 40h                   |       |

| 14.1.28  | ARBITER CONTROL REGISTER – OFFSET 40h                             |       |

| 14.1.29  | UPSTREAM MEMORY CONTROL REGISTER – OFFSET 48h                     |       |

| 14.1.30  | HOT SWAP SWITCH TIME SLOT REGISTER – OFFSET 4Ch                   |       |

| 14.1.31  | UPSTREAM (S1 or S2 to P) MEMORY BASE REGISTER – OFFSET 50h        |       |

| 14.1.32  | UPSTREAM (S1 or S2 to P) MEMORY LIMIT REGISTER – OFFSET 50h       |       |

| 14.1.33  | UPSTREAM (S1 or S2 to P) MEMORY BASE UPPER 32-BITS REGISTER – OF  |       |

| 54h      |                                                                   |       |

| 14.1.34  | UPSTREAM (S1 or S2 to P) MEMORY LIMIT UPPER 32 BITS REGISTER – OF |       |

| 58h      |                                                                   |       |

| 14.1.35  | P_SERR# EVENT DISABLE REGISTER – OFFSET 64h                       |       |

| 14.1.36  | SECONDARY CLOCK CONTROL REGISTER – OFFSET 68h                     |       |

| 14.1.37  | PORT OPTION REGISTER – OFFSET 74h                                 |       |

| 14.1.38  | MASTER TIMEOUT COUNTER REGISTER – OFFSET 74h                      |       |

| 14.1.39  | RETRY COUNTER REGISTER – OFFSET 78h                               |       |

| 14.1.40  | SAMPLING TIMER REGISTER – OFFSET 7Ch                              |       |

| 14.1.41  | SECONDARY SUCCESSFUL I/O READ COUNTER REGISTER – OFFSET 80h       | 91    |

| 14.1 | 1.42 SECONDARY SUCCESSFUL I/O WRITE COUNTER REGISTER – OFFSET 84h 9 | 1  |

|------|---------------------------------------------------------------------|----|

| 14.1 |                                                                     |    |

| 14.1 | 1.44 SECONDARY SUCCESSFUL MEMORY WRITE COUNTER REGISTER – OFFSET 80 |    |

| 14.1 |                                                                     |    |

|      | 1.46 PRIMARY SUCCESSFUL I/O WRITE COUNTER REGISTER – OFFSET 94h     |    |

|      | 1.47 PRIMARY SUCCESSFUL MEMORY READ COUNTER REGISTER – OFFSET 98h9  |    |

| 14.1 |                                                                     |    |

|      | 1.49 CAPABILITY ID REGISTER – OFFSET B0h                            |    |

| 14.1 | 1.50 NEXT POINTER REGISTER – OFFSET B0h                             |    |

| 14.1 |                                                                     |    |

| 14.1 | 1.52 CHASSIS NUMBER REGISTER – OFFSET B0h                           | )3 |

| 14.1 | 1.53 CAPABILITY ID REGISTER – OFFSET COh                            | )4 |

|      | 1.54 NEXT POINTER REGISTER – OFFSET COh                             |    |

|      | 1.55 HOT SWAP CONTROL AND STATUS REGISTER – OFFSET COh              |    |

| 15 B | RIDGE BEHAVIOR                                                      | 4  |

| 15.1 | BRIDGE ACTIONS FOR VARIOUS CYCLE TYPES                              | 95 |

| 15.2 | TRANSACTION ORDERING                                                | 95 |

| 15.3 | ABNORMAL TERMINATION (INITIATED BY BRIDGE MASTER)                   | 96 |

| 15.3 |                                                                     |    |

| 15.3 | 3.2 PARITY AND ERROR REPORTING                                      | 6  |

| 15.3 |                                                                     |    |

| 15.3 | 3.4 SECONDARY IDSEL MAPPING                                         | 17 |

| 16 I | EEE 1149.1 COMPATIBLE JTAG CONTROLLER 9                             | 7  |

| 16.1 | BOUNDARY SCAN ARCHITECTURE                                          | 97 |

| 16.1 |                                                                     |    |

| 16.1 |                                                                     |    |

| 16.2 | BOUNDARY-SCAN INSTRUCTION SET                                       |    |

| 16.3 | TAP TEST DATA REGISTERS                                             |    |

| 16.4 | BYPASS REGISTER                                                     |    |

| 16.5 | BOUNDARY-SCAN REGISTER                                              |    |

| 16.6 | TAP CONTROLLER                                                      |    |

| 17 E | ELECTRICAL AND TIMING SPECIFICATIONS 10                             |    |

| 17.1 | MAXIMUM RATINGS 10                                                  |    |

| 17.2 | 3.3V DC SPECIFICATIONS                                              | 14 |

| 17.3 | 3.3V AC SPECIFICATIONS                                              |    |

| 17.4 | PRIMARY AND SECONDARY BUSES AT 66MHz CLOCK TIMING 10                |    |

| 17.5 | PRIMARY AND SECONDARY BUSES AT 33MHz CLOCK TIMING                   |    |

| 17.6 | POWER CONSUMPTION                                                   |    |

| 18 2 | 72-PIN PBGA PACKAGE FIGURE 10                                       | 7  |

| 18.1 | PART NUMBER ORDERING INFORMATION                                    | )7 |

## LIST OF TABLES

| TABLE 4-1  | PCI TRANSACTIONS                                           | 21  |

|------------|------------------------------------------------------------|-----|

| TABLE 4-2  | WRITE TRANSACTION FORWARDING                               | 23  |

| TABLE 4-3  | WRITE TRANSACTION DISCONNECT ADDRESS BOUNDARIES            | 26  |

|            | READ PREFETCH ADDRESS BOUNDARIES                           |     |

| TABLE 4-5  | READ TRANSACTION PREFETCHING                               | 30  |

|            | DEVICE NUMBER TO IDSEL S1_AD OR S2_AD PIN MAPPING          |     |

| TABLE 4-7  | DELAYED WRITE TARGET TERMINATION RESPONSE                  | 39  |

|            | RESPONSE TO POSTED WRITE TARGET TERMINATION                |     |

| TABLE 4-9  | RESPONSE TO DELAYED READ TARGET TERMINATION                | 40  |

| TABLE 6-1  | SUMMARY OF TRANSACTION ORDERING                            | 50  |

| TABLE 7-1  | SETTING THE PRIMARY INTERFACE DETECTED PARITY ERROR BIT    | 58  |

| TABLE 7-2  | SETTING SECONDARY INTERFACE DETECTED PARITY ERROR BIT      | 58  |

| TABLE 7-3  | SETTING PRIMARY INTERFACE DATA PARITY ERROR DETECTED BIT   | 59  |

|            | SETTING SECONDARY INTERFACE DATA PARITY ERROR DETECTED BIT |     |

| TABLE 7-5  | ASSERTION OF P_PERR#                                       | 60  |

| TABLE 7-6  | ASSERTION OF S_PERR#                                       | 62  |

|            | ASSERTION OF P_SERR# FOR DATA PARITY ERRORS                |     |

| TABLE 16-1 | 1 TAP PINS                                                 | 99  |

| TABLE 16-2 | 2 JTAG BOUNDARY REGISTER ORDER                             | 101 |

## LIST OF FIGURES

| FIGURE 9-1 SECONDARY ARBITER EXAMPLE6                | 58 |

|------------------------------------------------------|----|

| FIGURE 16-1 TEST ACCESS PORT BLOCK DIAGRAM           | 98 |

| FIGURE 17-1 PCI SIGNAL TIMING MEASUREMENT CONDITIONS | )5 |

| FIGURE 18-1 272-PIN PBGA PACKAGE 10                  | )7 |

This page intentionally left blank.

## 1 INTRODUCTION

#### **PRODUCT DESCRIPTION**

The PI7C7300D is Pericom Semiconductor's second-generation PCI-PCI Bridge and is an updated revision to the PI7C7300A. It is designed to be fully compliant with the 32bit, 66MHz implementation of the *PCI Local Bus Specification, Revision 2.2.* The PI7C7300D supports only synchronous bus transactions between devices on the Primary Bus running at 33MHz to 66MHz and the Secondary Buses operating at either 33MHz or 66MHz. The Primary and Secondary Buses can also operate in concurrent mode, resulting in added increase in system performance. Concurrent bus operation off-loads and isolates unnecessary traffic from the Primary Bus; thereby enabling a master and a target device on the same Secondary PCI Bus to communicate even while the Primary Bus is busy. In addition, the Secondary Buses have load balancing capability, allowing faster devices to be isolated away from slower devices. Among the other features supported by the PI7C7300D are: support for up to 15 devices on the Secondary Buses, Compact PCI Hot Swap (PICMG 2.1, R1.0) *Friendly* Support and Dual Addressing Cycle.

#### **PRODUCT FEATURES**

- 32-bit Primary and Two Secondary Ports run up to 66MHz

- All 3 ports compliant with the *PCI Local Bus Specification, Revision 2.2*

- Compliant with PCI-to-PCI Bridge Architecture Specification, Revision 1.1.

- All I/O and memory commands

- Type 1 to Type 0 configuration conversion

- Type 1 to Type 1 configuration forwarding

- Type 1 configuration write to special cycle conversion

- Concurrent Primary to Secondary Bus operation and independent intra-Secondary Port channel to reduce traffic on the Primary Port

- Provides internal arbitration for one set of eight secondary bus masters (S1 bus) and one set of seven (eight if Hot Swap is disabled) secondary bus masters (S2 bus)

- Programmable 2-level priority arbiter

- Disable control for use of external arbiter

- Supports posted write buffers in all directions

- Three 128 byte FIFO's for delay transactions

- Three 128 byte FIFO's for posted memory transactions

- Enhanced address decoding

- 32-bit I/O address range

- 32-bit memory-mapped I/O address range

- VGA addressing and VGA palette snooping

- ISA-aware mode for legacy support in the first 64KB of I/O address range

- Dual Addressing cycle (64-bit)

- Supports system transaction ordering rules

- Tri-state control of output buffers on secondary buses

- Compact PCI Hot Swap (PICMG 2.1, R1.0) Friendly Support

- Industrial Temperature range –40°C to 85°C

- IEEE 1149.1 JTAG interface support

- 3.3V core; 3.3V PCI I/O interface with 5V I/O tolerance

- 272-pin plastic BGA package

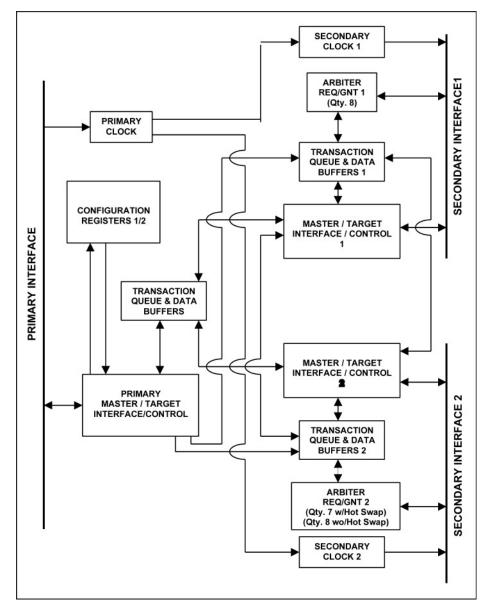

## **BLOCK DIAGRAM**

## **3** SIGNAL DEFINITIONS

## 3.1 SIGNAL TYPES

| Signal Type | Description                                                                                                                                                                       |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PI          | PCI input (3.3V, 5V tolerant)                                                                                                                                                     |  |

| PIU         | PCI input (3.3V, 5V tolerant) with weak pull-up                                                                                                                                   |  |

| PID         | PCI input (3.3V, 5V tolerant) with weak pull-down                                                                                                                                 |  |

| PO          | PCI output (3.3V)                                                                                                                                                                 |  |

| PB          | PCI tri-state bidirectional (3.3V, 5V tolerant)                                                                                                                                   |  |

| PSTS        | PCI sustained tri-state bi-directional (Active LOW signal which must be driven inactive for one cycle before being tri-stated to ensure HIGH performance on a shared signal line) |  |

| PTS         | PCI tri-state output                                                                                                                                                              |  |

| POD         | PCI output which either drives LOW (active state) or tri-state                                                                                                                    |  |

## **3.2 PRIMARY BUS INTERFACE SIGNALS**

| Name       | Pin #                                                                                                                                                                             | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P_AD[31:0] | Y7, W7, Y8, W8,<br>V8, U8, Y9, W9,<br>W10, V10, Y11,<br>V11, U11, Y12,<br>W12, V12, V16,<br>W16, Y16, W17,<br>Y17, U18, W18,<br>Y18, U19, W19,<br>Y19, U20, V20,<br>Y20, T17, R17 | PB   | <b>Primary Address/Data.</b> Multiplexed address and data<br>bus. Address is indicated by P_FRAME# assertion.<br>Write data is stable and valid when P_IRDY# is<br>asserted and read data is stable and valid when<br>P_TRDY# is asserted. Data is transferred on rising<br>clock edges when both P_IRDY# and P_TRDY# are<br>asserted. During bus idle, PI7C7300D drives P_AD to<br>a valid logic level when P_GNT# is asserted.                                                                                                                                                                                                          |

| P_CBE[3:0] | V9, U12, U16,<br>V19                                                                                                                                                              | PB   | <b>Primary Command/Byte Enables.</b> Multiplexed command field and byte enable field. During address phase, the initiator drives the transaction type on these pins. The initiator then drives the byte enables during data phases. During bus idle, PI7C7300D drives P_CBE[3:0] to a valid logic level when P_GNT# is asserted.                                                                                                                                                                                                                                                                                                          |

| P_PAR      | U15                                                                                                                                                                               | РВ   | <b>Primary Parity.</b> Parity is even across P_AD[31:0],<br>P_CBE[3:0], and P_PAR (i.e. an even number of 1's).<br>P_PAR is an input and is valid and stable one cycle<br>after the address phase (indicated by assertion of<br>P_FRAME#) for address parity. For write data phases,<br>P_PAR is an input and is valid one clock after<br>P_IRDY# is asserted. For read data phase, P_PAR is<br>an output and is valid one clock after P_TRDY# is<br>asserted. Signal P_PAR is tri-stated one cycle after the<br>P_AD lines are tri-stated. During bus idle, PI7C7300D<br>drives P_PAR to a valid logic level when P_GNT# is<br>asserted. |

| P_FRAME#   | W13                                                                                                                                                                               | PSTS | <b>Primary FRAME (Active LOW).</b> Driven by the initiator of a transaction to indicate the beginning and duration of an access. The de-assertion of P_FRAME# indicates the final data phase requested by the initiator. Before being tri-stated, it is driven to a de-asserted state for one cycle.                                                                                                                                                                                                                                                                                                                                      |

| Name      | Pin # | Туре | Description                                                      |

|-----------|-------|------|------------------------------------------------------------------|

| P_IRDY#   | V13   | PSTS | Primary IRDY (Active LOW). Driven by the                         |

|           |       |      | initiator of a transaction to indicate its ability to            |

|           |       |      | complete current data phase on the primary side. Once            |

|           |       |      | asserted in a data phase, it is not de-asserted until the        |

|           |       |      | end of the data phase. Before tri-stated, it is driven to a      |

|           |       |      | de-asserted state for one cycle.                                 |

| P TRDY#   | U13   | PSTS | Primary TRDY (Active LOW). Driven by the target                  |

| -         |       |      | of a transaction to indicate its ability to complete             |

|           |       |      | current data phase on the primary side. Once asserted            |

|           |       |      | in a data phase, it is not de-asserted until the end of the      |

|           |       |      | data phase. Before tri-stated,                                   |

|           |       |      | it is driven to a de-asserted state for one cycle.               |

| P_DEVSEL# | Y14   | PSTS | Primary Device Select (Active LOW). Asserted by                  |

| F_DEVSEL# | 114   | 1313 |                                                                  |

|           |       |      | the target indicating that the device is accepting the           |

|           |       |      | transaction. As a master, PI7C7300D waits for the                |

|           |       |      | assertion of this signal within 5 cycles of P_FRAME#             |

|           |       |      | assertion; otherwise, terminate with master abort.               |

|           |       |      | Before tri-stated, it is driven to a                             |

|           |       |      | de-asserted state for one cycle.                                 |

| P_STOP#   | W14   | PSTS | Primary STOP (Active LOW). Asserted by the target                |

|           |       |      | indicating that the target is requesting the initiator to        |

|           |       |      | stop the current transaction. Before tri-stated, it is           |

|           |       |      | driven to a de-asserted state for one cycle.                     |

| P_LOCK#   | V14   | PSTS | Primary LOCK (Active LOW). Asserted by the                       |

|           |       |      | master for multiple transactions to complete.                    |

| P_IDSEL   | Y10   | PI   | Primary ID Select. Used as a chip select line for Type           |

| _         |       |      | 0 configuration accesses to PI7C7300D configuration              |

|           |       |      | space.                                                           |

| P_PERR#   | Y15   | PSTS | Primary Parity Error (Active LOW). Asserted when                 |

|           |       |      | a data parity error is detected for data received on the         |

|           |       |      | primary interface. Before being tri-stated, it is driven         |

|           |       |      | to a de-asserted state for one cycle.                            |

| P_SERR#   | W15   | POD  | Primary System Error (Active LOW). Can be                        |

|           | W15   | TOD  | driven LOW by any device to indicate a system error              |

|           |       |      | condition. PI7C7300D drives this pin on:                         |

|           |       |      | 1                                                                |

|           |       |      | riddiebs parity error                                            |

|           |       |      | <ul> <li>Posted write data parity error on target bus</li> </ul> |

|           |       |      | <ul> <li>Secondary S1_SERR# or S2_SERR# asserted</li> </ul>      |

|           |       |      | <ul> <li>Master abort during posted write transaction</li> </ul> |

|           |       |      | <ul> <li>Target abort during posted write transaction</li> </ul> |

|           |       |      | <ul> <li>Posted write transaction discarded</li> </ul>           |

|           |       |      | <ul> <li>Delayed write request discarded</li> </ul>              |

|           |       |      | <ul> <li>Delayed read request discarded</li> </ul>               |

|           |       |      | <ul> <li>Delayed transaction master timeout</li> </ul>           |

|           |       |      | This signal requires an external pull-up resistor for            |

|           |       |      | proper operation.                                                |

| P_REQ#    | W6    | PTS  | Primary Request (Active LOW). This is asserted by                |

|           |       |      | PI7C7300D to indicate that it wants to start a                   |

|           |       |      | transaction on the primary bus. PI7C7300D de-asserts             |

|           |       |      | this pin for at least 2 PCI clock cycles before asserting        |

|           |       |      | it again.                                                        |

| P_GNT#    | U7    | PI   | Primary Grant (Active LOW). When asserted,                       |

| 0.11      | 0,    | **   | PI7C7300D can access the primary bus. During idle                |

|           |       |      | and P_GNT# asserted, PI7C7300D will drive P_AD,                  |

|           |       |      |                                                                  |

| D DEGET#  | 372   | DI   | P_CBE, and P_PAR to valid logic levels.                          |

| P_RESET#  | Y5    | PI   | Primary RESET (Active LOW).                                      |

|           |       |      | When P_RESET# is active, all PCI signals should be               |

|           |       |      | asynchronously tri-stated.                                       |

| Name    | Pin # | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P_M66EN | V18   | PI   | <b>Primary Interface 66MHz Operation.</b><br>This input is used to specify if PI7C7300D is capable of running at 66MHz. For 66MHz operation on the Primary bus, this signal should be pulled "HIGH". For 33MHz operation on the Primary bus, this signal should be pulled "LOW". In this condition, S1_M66EN and S2_M66EN will both need to be "LOW", forcing both secondary buses to run at 33MHz |

|         |       |      | also.                                                                                                                                                                                                                                                                                                                                                                                              |

3.3

## SECONDARY BUS INTERFACE SIGNALS

| Name                          | Pin #                                                                                                                                                                                                                                                                                                                                                 | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$1_AD[31:0],<br>\$2_AD[31:0] | B20, B19, C20,<br>C19, C18, D20,<br>D19, D17, E19,<br>E18, E17, F20,<br>F19, F17, G20,<br>G19, L20, L19,<br>L18, M20, M19,<br>M17, N20, N19,<br>N18, N17, P17,<br>R20, R19, R18,<br>T20, T19<br>J4, H1, H2, H3,<br>H4, G1, G3, G4,<br>F2, F3, F4, E1, E4,<br>D1, C1, B1, C5,<br>B5, D6, C6, B6,<br>A6, C7, B7, D8,<br>C8, D9, C9, B9,<br>A9, D10, C10 | PB   | Secondary Address/Data. Multiplexed address and<br>data bus. Address is indicated by S1_FRAME# or<br>S2_FRAME# assertion. Write data is stable and valid<br>when S1_IRDY# or S2_IRDY# is asserted and read<br>data is stable and valid when S1_IRDY# or S2_IRDY#<br>is asserted. Data is transferred on rising clock edges<br>when both S1_IRDY# or S2_IRDY# and S1_TRDY#<br>or S2_TRDY# are asserted. During bus idle,<br>PI7C7300D drives S1_AD or S2_AD to a valid logic<br>level when S1_GNT# or S2_GNT# is asserted<br>respectively.                                                                                                                                                                                                                                                                                                          |

| S1_CBE[3:0],                  | E20, G18, K17,                                                                                                                                                                                                                                                                                                                                        | PB   | Secondary Command/Byte Enables. Multiplexed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| S2_CBE[3:0]                   | P20<br>F1, A1, A4, A7                                                                                                                                                                                                                                                                                                                                 |      | command field and byte enable field. During address<br>phase, the initiator drives the transaction type on these<br>pins. The initiator then drives the byte enables during<br>data phases. During bus idle, PI7C7300D drives<br>S1_CBE[3:0] or S2_CBE[3:0] to a valid logic level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| S1_PAR,<br>S2_PAR             | K18,<br>B4                                                                                                                                                                                                                                                                                                                                            | PB   | when the internal grant is asserted.<br>Secondary Parity. Parity is even across S1_AD[31:0],<br>S1_CBE[3:0], and S1_PAR or S2_AD[31:0],<br>S2_CBE[3:0], and S2_PAR (i.e. an even number of<br>1's). S1_PAR or S2_PAR is an input and is valid and<br>stable one cycle after the address phase (indicated by<br>assertion of S1_FRAME# or S2_FRAME#) for address<br>parity. For write data phases, S1_PAR or S2_PAR is<br>an input and is valid one clock after S1_IRDY#<br>S2_IRDY# is asserted. For read data phase, S1_PAR<br>or S2_PAR is an output and is valid one clock after<br>S1_TRDY# or S2_TRDY# is asserted. Signal S1_PAR<br>or S2_PAR is tri-stated one cycle after the S1_AD or<br>S2_AD lines are tri-stated. During bus idle,<br>PI7C7300D drives S1_PAR or S2_PAR to a valid logic<br>level when the internal grant is asserted. |

| S1_FRAME#,<br>S2_FRAME#       | H20,<br>D2                                                                                                                                                                                                                                                                                                                                            | PSTS | Secondary FRAME (Active LOW). Driven by the initiator of a transaction to indicate the beginning and duration of an access. The de-assertion of S1_FRAME# or S2_FRAME# indicates the final data phase requested by the initiator. Before being tristated, it is driven to a de-asserted state for one cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Name                          | Pin #                                                                         | Туре | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------|-------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S1_IRDY#,<br>S2_IRDY#         | H19,<br>B2                                                                    | PSTS | Secondary IRDY (Active LOW). Driven by the initiator of a transaction to indicate its ability to complete current data phase on the secondary side. Once asserted in a data phase, it is not de-asserted until the end of the data phase. Before tri-stated, it is driven to a de-asserted state for one cycle.                                                                   |

| S1_TRDY#,<br>S2_TRDY#         | H18,<br>A2                                                                    | PSTS | <b>Secondary TRDY (Active LOW).</b> Driven by the target of a transaction to indicate its ability to complete current data phase on the secondary side. Once asserted in a data phase, it is not de-asserted until the end of the data phase. Before tri-stated, it is driven to a de-asserted state for one cycle.                                                               |

| S1_DEVSEL#,<br>S2_DEVSEL#     | J20,<br>D3                                                                    | PSTS | <b>Secondary Device Select (Active LOW).</b> Asserted by the target indicating that the device is accepting the transaction. As a master, PI7C7300D waits for the assertion of this signal within 5 cycles of S1_FRAME# or S2_FRAME# assertion; otherwise, terminate with master abort. Before tri-stated, it is driven to a deasserted state for one cycle.                      |

| S1_STOP#,<br>S2_STOP#         | J19,<br>C3                                                                    | PSTS | <b>Secondary STOP (Active LOW).</b> Asserted by the target indicating that the target is requesting the initiator to stop the current transaction. Before tristated, it is driven to a de-asserted state for one cycle.                                                                                                                                                           |

| S1_LOCK#,<br>S2_LOCK#         | J18,<br>B3                                                                    | PSTS | <b>Secondary LOCK (Active LOW).</b> Asserted by the master for multiple transactions to complete.                                                                                                                                                                                                                                                                                 |

| S1_PERR#,<br>S2_PERR#         | J17,<br>D4                                                                    | PSTS | Secondary Parity Error (Active LOW). Asserted<br>when a data parity error is detected for data received on<br>the secondary interface. Before being tri-stated, it is<br>driven to a de-asserted state for one cycle.                                                                                                                                                             |

| S1_SERR#,<br>S2_SERR#         | K20,<br>C4                                                                    | PI   | <b>Secondary System Error (Active LOW).</b> Can be driven LOW by any device to indicate a system error condition.                                                                                                                                                                                                                                                                 |

| S1_REQ#[7:0],<br>S2_REQ#[6:0] | B11, A12, D13,<br>C13, C15, A16,<br>C17, B17<br>R3, P2, P1, M2,<br>M1, K1, K3 | PIU  | <b>Secondary Request (Active LOW).</b> This is asserted<br>by an external device to indicate that it wants to start a<br>transaction on the secondary bus. The input is<br>externally pulled up through a resistor to VDD.                                                                                                                                                        |

| S1_GNT#[7:0]                  | C11, B12, B13,<br>A14, D14, B16,<br>D16, B18                                  | РО   | <b>Secondary Grant (Active LOW).</b> PI7C7300D asserts this pin to access the secondary bus. PI7C7300D deasserts this pin for at least 2 PCI clock cycles before                                                                                                                                                                                                                  |

| S2_GNT#[6:0]                  | P4, R1, N4, M3,<br>L4, L1, K2                                                 |      | asserting it again. During idle and S1_GNT# or S2-<br>GNT# asserted, PI7C7300D will drive S1_AD,<br>S1_CBE, and S1_PAR or S2_AD, S2_CBE, and<br>S2_PAR.                                                                                                                                                                                                                           |

| S1_RESET#,<br>S2_RESET#       | B10,<br>T4                                                                    | PO   | <ul> <li>Secondary RESET (Active LOW). Asserted when any of the following conditions are met:</li> <li>Signal P_RESET# is asserted.</li> <li>Secondary reset bit in bridge control register in configuration space is set.</li> <li>When asserted, all control signals are tri-stated and zeroes are driven on S1_AD, S1_CBE, and S1_PAR or S2_AD, S2_CBE, and S2_PAR.</li> </ul> |

| S1_EN,                        | W3,                                                                           | PIU  | Secondary Enable (Active HIGH). When S1_EN or                                                                                                                                                                                                                                                                                                                                     |

| S2_EN                         | W4                                                                            |      | S2_EN is inactive, secondary bus PCI S1 or PCI S2<br>will be asynchronously tri-stated.                                                                                                                                                                                                                                                                                           |

| S1_M66EN,<br>S2_M66EN         | D7,<br>W5                                                                     | PI   | Secondary Interface 66MHz Operation. This input<br>is used to specify if PI7C7300D is capable of running<br>at 66MHz on the secondary side. When HIGH, the S1<br>or S2 bus may run at 66MHz. When LOW, the S1 or<br>S2 bus may only run at 33MHz.<br>If P_M66EN is pulled LOW, both S1_M66EN and<br>S2_M66EN need to be LOW.                                                      |

| Name   | Pin # | Туре | Description                                                                                                                                                                                                                                                                                                             |

|--------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S_CFN# | Y2    | PIU  | <b>Secondary Bus Central Function Control Pin.</b> When tied LOW, it enables the internal arbiter. When tied HIGH, an external arbiter must be used. S1_REQ#[0] or S2_REQ#[0] is reconfigured to be the secondary bus grant input, and S1_GNT#[0] or S2_GNT#[0] is reconfigured to be the secondary bus request output. |

## 3.4 CLOCK SIGNALS

| Name               | Pin #                                        | Туре | Description                                                                                  |

|--------------------|----------------------------------------------|------|----------------------------------------------------------------------------------------------|

| P_CLK              | V6                                           | PI   | <b>Primary Clock Input.</b> Provides timing for all transactions on the primary interface.   |

| S1_CLKOUT<br>[7:0] | A11, C12, A13,<br>B14, B15, C16,<br>A18, A19 | PTS  | Secondary Clock Output. Provides secondary 1 clocks phase synchronous with the P_CLK.        |

| S2_CLKOUT<br>[7:0] | T3, T1, P3, N3,<br>M4, L3, L2, J1            | PTS  | <b>Secondary Clock Output.</b> Provides secondary 2 clocks phase synchronous with the P_CLK. |

## 3.5 MISCELLANEOUS SIGNALS

| Name     | Pin # | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BY_PASS  | Y4    | PI   | <b>Reserved.</b> Reserved for future use. Must be tied HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PLL_TM   | Y3    | PI   | <b>Reserved.</b> Reserved for future use. Must be tied LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| S_CLKIN  | V5    | PI   | <b>Reserved.</b> Reserved for future use. Must be tied LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SCAN_TM# | V4    | PI   | Full-Scan Test Mode Enable (Active LOW).<br>Connect HIGH for normal operation.<br>When SCAN_TM# is active, the ten scan chains will be<br>enabled. The scan clock is P_CLK. The scan input and<br>outputs are as follows:<br>S1_REQ[6], S1_REQ[5], S1_REQ[4], S1_REQ[3],<br>S1_REQ[2], S2_REQ#[6], S2_REQ#[5], S2_REQ#[4],<br>S2_REQ#[3], S2_REQ#[6], S2_REQ#[5], S2_REQ#[4],<br>S1_GNT#[5], S1_GNT#[4], S1_GNT#[6],<br>S1_GNT#[5], S2_GNT#[6], S2_GNT#[5],<br>S2_GNT#[4], S2_GNT#[3], S2_GNT#[2] |

| SCAN_EN  | U5    | PID  | <b>Full-Scan Enable Control.</b> SCAN_EN should be tied<br>LOW in normal mode. When SCAN_EN is LOW, full-<br>scan is in shift operation if SCAN_TM# is active.<br>When SCAN_EN is HIGH, full-scan is in parallel<br>operation if SCAN_TM# is active.                                                                                                                                                                                                                                              |

3.6

## COMPACT PCI HOT-SWAP SIGNALS

| Name   | Pin # | Туре | Description                                                                                                                                                                          |

|--------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOO    | U1    | PO   | Hot Swap LED. The output of this pin lights a blue LED to indicate insertion and removal ready status. If HS_EN is LOW, pin is S2_GNT#[7].                                           |

| HS_SW# | T2    | PI   | Hot Swap Switch. When driven LOW, this signal indicates that the board ejector handle indicates an insertion or impending extraction of a board. If HS_EN is LOW, pin is S2_REQ#[7]. |

| Name  | Pin # | Туре | Description                                               |

|-------|-------|------|-----------------------------------------------------------|

| HS_EN | U6    | PI   | Hot Swap Enable. To enable Hot Swap Friendly              |

|       |       |      | support, this signal should be pulled HIGH.               |

| ENUM# | R4    | POD  | Hot Swap Status Indicator. The output of ENUM#            |

|       |       |      | indicates to the system that an insertion has occurred of |

|       |       |      | that an extraction is about to occur.                     |

## 3.7 JTAG BOUNDARY SCAN SIGNALS

| Name  | Pin # | Туре | Description                                                                                                                                                               |

|-------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ТСК   | V2    | PIU  | <b>Test Clock.</b> Used to clock state information and data into and out of the PI7C7300D during boundary scan.                                                           |

| TMS   | W1    | PIU  | <b>Test Mode Select.</b> Used to control the state of the Test Access Port controller.                                                                                    |

| TDO   | V3    | PTS  | <b>Test Data Output.</b> When SCAN_EN is HIGH, it is used (in conjunction with TCK) to shift data out of the Test Access Port (TAP) in a serial bit stream.               |

| TDI   | W2    | PIU  | <b>Test Data Input.</b> When SCAN_EN is HIGH, it is used (in conjunction with TCK) to shift data and instructions into the Test Access Port (TAP) in a serial bit stream. |

| TRST# | U3    | PIU  | <b>Test Reset.</b> Active LOW signal to reset the Test Access Port (TAP) controller into an initialized state.                                                            |

### 3.8 **POWER AND GROUND**

| Name | Pin #              | Туре | Description           |

|------|--------------------|------|-----------------------|

| VDD  | B8, C14, D5, D11,  |      | 3.3V Digital Power    |

|      | D15, E2, F18, J3,  |      |                       |

|      | L17, N2, P19,      |      |                       |

|      | U10, V1, V7, V15,  |      |                       |

|      | W20                |      |                       |

| VSS  | A3, A5, A8, A10,   |      | Digital Ground        |

|      | A15, A17, A20,     |      |                       |

|      | C2, D12, D18, E3,  |      |                       |

|      | G2, G17, H17, J2,  |      |                       |

|      | J9, J10, J11, J12, |      |                       |

|      | K4, K9, K10, K11,  |      |                       |

|      | K12, K19, L9,      |      |                       |

|      | L10, L11, L12,     |      |                       |

|      | M9, M10, M11,      |      |                       |

|      | M12, M18, N1,      |      |                       |

|      | P18, R2, T18, U2,  |      |                       |

|      | U9, U14, U17,      |      |                       |

|      | V17, W11, Y6,      |      |                       |

|      | Y13                |      |                       |

| AVCC | Y1                 |      | Analog 3.3V for PLL   |

| AGND | U4                 |      | Analog Ground for PLL |

## 3.9 PI7C7300D PBGA PIN LIST

| Pin # | Name      | Туре | Pin # | Name      | Туре |

|-------|-----------|------|-------|-----------|------|

| A1    | S2_CBE[2] | PB   | A2    | S2_TRDY#  | PSTS |

| A3    | VSS       | -    | A4    | S2_CBE[1] | PB   |

| A5    | VSS       | -    | A6    | S2_AD[10] | PB   |

| Pin #      | Name                    | Туре     | Pin #      | Name              | Туре    |

|------------|-------------------------|----------|------------|-------------------|---------|

| A7         | S2_CBE[0]               | PB       | A8         | VSS               | -       |

| A9         | S2_AD[2]                | PB       | A10        | VSS               | -       |

| A11        | S1_CLKOUT[7]            | PTS      | A12        | S1_REQ#[6]        | PIU     |

| A13        | S1_CLKOUT[5]            | PTS      | A14        | S1_GNT#[4]        | PO      |

| A15        | VSS                     | -        | A16        | S1_REQ#[2]        | PIU     |

| A17        | VSS                     | -        | A18        | S1_CLKOUT[1]      | PTS     |

| A19        | S1_CLKOUT[0]            | PTS      | A20        | VSS               | -       |

| B1         | S2_AD[16]               | PB       | B2         | S2_IRDY#          | PSTS    |

| B3         | S2_LOCK#                | PSTS     | B4         | S2_PAR            | PB      |

| B5         |                         | PB       | B6         |                   | PB      |

| B7         | S2_AD[8]                | PB       | B8         | VDD               | -       |

| B9         | S2_AD[3]                | PB       | B10        | S1_RESET#         | PO      |

| B11        | S1_REQ#[7]              | PIU      | B12        |                   | PO      |

| B13        | S1_GNT#[5]              | PO       | B14        | S1_CLKOUT[4]      | PTS     |

| B15        | S1_CLKOUT[3]            | PTS      | B16        | S1_GNT#[2]        | PO      |

| B17        | S1_REQ#[0]              | PIU      | B18        | S1_GNT#[0]        | PO      |

| B19        | S1_AD[30]               | PB       | B20        | S1_AD[31]         | PB      |

| Cl         | S2_AD[17]               | PB       | C2         | VSS               | -       |

| C3         | S2_STOP#                | PSTS     | C4         | S2_SERR#          | PI      |

| C5         | S2_AD[15]               | PB       | C6         | S2_AD[12]         | PB      |

| C7         | S2_AD[13]               | PB       | C8         | S2_AD[6]          | PB      |

| C9         | S2_AD[4]                | PB       | C10        | S2_AD[0]          | PB      |

| C11        | S1 GNT#[7]              | PO       | C12        | S1_CLKOUT[6]      | PTS     |

| C13        | S1_REQ#[4]              | PIU      | C12        | VDD               | PTS     |

| C15        | S1_REQ#[3]              | PIU      | C16        | S1_CLKOUT[2]      | PTS     |

| C17        | S1_REQ#[1]              | PIU      | C18        | S1_AD[27]         | PB      |

| C19        | S1_AD[28]               | PB       | C20        | S1_AD[27]         | PB      |

| D1         | S2_AD[18]               | PB       | D2         | S2_FRAME#         | PSTS    |

| D3         | S2_AD[18]<br>S2 DEVSEL# | PSTS     | D2<br>D4   | S2_PRR#           | PSTS    |

| D5         | VDD                     | -        | D4<br>D6   | S2_AD[13]         | PB      |

| D3<br>D7   | S1_M66EN                | PI       | D0         | S2_AD[13]         | PB      |

| D7<br>D9   | S2_AD[5]                | PB       | D10        | S2_AD[7]          | PB      |

| D9<br>D11  | VDD                     | гb       | D10        | VSS               | - FD    |

| D11<br>D13 | \$1_REQ#[5]             | -<br>PIU | D12<br>D14 |                   | -<br>PO |

|            |                         | -        |            | S1_GNT#[3]        |         |

| D15<br>D17 | VDD<br>S1_AD[24]        |          | D16<br>D18 | S1_GNT#[1]<br>VSS | PO      |

| D17<br>D19 |                         | PB<br>PB | D18<br>D20 |                   | -<br>DD |

|            | S1_AD[25]               |          |            |                   | PB<br>- |

| E1         | S2_AD[20]               | PB       | E2<br>E4   | VDD               |         |

| E3         | VSS                     | -        |            | S2_AD[19]         | PB      |

| E17        | S1_AD[21]               | PB       | E18        | S1_AD[22]         | PB      |

| E19        | S1_AD[23]               | PB       | E20        | S1_CBE[3]         | PB      |

| F1         | S2_CBE[3]               | PB       | F2         | S2_AD[23]         | PB      |

| F3         | S2_AD[22]               | PB       | F4         | S2_AD[21]         | PB      |

| F17        | S1_AD[18]               | PB       | F18        | VDD               | -       |

| F19        | S1_AD[19]               | PB       | F20        | S1_AD[20]         | PB      |

| Gl         | S2_AD[26]               | PB       | G2         | VSS               | -       |

| G3         | S2_AD[25]               | PB       | G4         | S2_AD[24]         | PB      |

| G17        | VSS                     | -        | G18        | S1_CBE[2]         | PB      |

| G19        | S1_AD[16]               | PB       | G20        | S1_AD[17]         | PB      |

| H1         | S2_AD[30]               | PB       | H2         | S2_AD[29]         | PB      |

| H3         | S2_AD[28]               | PB       | H4         | S2_AD[27]         | PB      |

| H17        | VSS                     | -        | H18        | S1_TRDY#          | PSTS    |

| H19        | S1_IRDY#                | PSTS     | H20        | S1_FRAME#         | PSTS    |

| J1         | S2_CLKOUT[0]            | PTS      | J2         | VSS               | -       |

| J3         | VDD                     | -        | J4         | S2_AD[31]         | PB      |

| J9         | VSS                     | -        | J10        | VSS               | -       |

| J11        | VSS                     | -        | J12        | VSS               | -       |

| J17        | S1_PERR#                | PSTS     | J18        | S1_LOCK#          | PSTS    |

| J19        | S1_STOP#                | PSTS     | J20        | S1_DEVSEL#        | PSTS    |

| K1         | S2_REQ#[1]              | PIU      | K2         | S2_GNT#[0]        | PO      |

| Pin #      | Name              | Туре     | Pin #      | Name         | Туре       |

|------------|-------------------|----------|------------|--------------|------------|

| K3         | S2_REQ#[0]        | PIU      | K4         | VSS          | -          |

| K9         | VSS               | -        | K10        | VSS          | -          |

| K11        | VSS               | -        | K12        | VSS          | -          |

| K17        | S1_CBE[1]         | PB       | K18        | S1_PAR       | PB         |

| K19        | VSS               | -        | K20        | S1_SERR#     | PI         |

| L1         | S2_GNT#[1]        | PO       | L2         | S2_CLKOUT[1] | PTS        |

| L3         | S2_CLKOUT[2]      | PTS      | L4         | S2_GNT#[2]   | PO         |

| L9         | VSS               | -        | L10        | VSS          | -          |

| L11        | VSS               | -        | L12        | VSS          | -          |

| L17        | VDD               | -        | L18        | S1_AD[13]    | PB         |

| L19        | S1_AD[14]         | PB       | L20        | S1_AD[15]    | PB         |

| M1         | S2_REQ#[2]        | PIU      | M2         | S2_REQ#[3]   | PIU        |

| M3         | S2_GNT#[3]        | PO       | M4         | S2_CLKOUT[3] | PTS        |

| M9         | VSS               | -        | M10        | VSS          | -          |

| M11        | VSS               | -        | M12        | VSS          | -          |

| M17        | S1_AD[10]         | PB       | M18        | VSS          | -          |

| M19        | S1_AD[11]         | PB       | M20        | S1_AD[12]    | PB         |

| N1         | VSS               | -        | N2         | VDD          | -          |

| N3         | S2_CLKOUT[4]      | PTS      | N4         | S2_GNT#[4]   | PO         |

| N17        | S1_AD[6]          | PB       | N18        | S1_AD[7]     | PB         |

| N19        | S1_AD[8]          | PB       | N20        | S1_AD[9]     | PB         |

| P1         | S2_REQ#[4]        | PIU      | P2         | S2_REQ#[5]   | PIU        |

| P3         | S2_CLKOUT[5]      | PTS      | P4         | S2_GNT#[6]   | РО         |

| P17        | S1_AD[5]          | PB       | P18        | VSS          | -          |

| P19        | VDD               | -        | P20        | S1_CBE[0]    | PB         |

| R1         | S2_GNT#[5]        | РО       | R2         | VSS          | -          |

| R3         | S2_REQ#[6]        | PIU      | R4         | ENUM#        | POD        |

| R17        | P_AD[0]           | PB       | R18        | S1_AD[2]     | PB         |

| R19        | S1_AD[3]          | PB       | R20        | S1_AD[4]     | PB         |

| T1         | S2_CLKOUT[6]      | PTS      | T2         | HS_SW        | PI         |

| T3         | S2_CLKOUT[7]      | PTS      | T4         | S2_RESET#    | PO         |

| T17        | P_AD[1]           | PB       | T18        | VSS          | -          |

| T19        | S1_AD[0]          | PB       | T20        | \$1_AD[1]    | PB         |

| U1         | LOO               | PO       | U2         | VSS          | -          |

| U3         | TRST#             | PIU      | U4         | AGND         | -          |

| U5         | SCAN_EN           | PID      | U6         | HS EN        | PI         |

| U7         | P_GNT#            | PI       | U8         | P_AD[26]     | PB         |

| U9         | VSS               | -        | U10        | VDD          | -          |

| U11        | P_AD[19]          | PB       | U12        | P_CBE[2]     | PB         |

| U13        | P_TRDY#           | PB       | U14        | VSS          | -          |

| U15        | P_PAR             | PB       | U16        | P_CBE[1]     | PB         |

| U17        | VSS               | -        | U18        | P_AD[10]     | PB         |

| U19        | P_AD[7]           | PB       | U20        | P_AD[4]      | PB         |

| V1         | VDD               | -        | V2         | TCK          | PIU        |

| V3         | TDO               | PTS      | V4         | SCAN_TM#     | PI         |

| V5         | S CLKIN           | PI       | V6         | P_CLK        | PI         |

| V7         | VDD               | 1-       | V8         | P_AD[27]     | PB         |

| V9         | P_CBE[3]          | PB       | V10        | P_AD[22]     | PB         |

| V11        | P_AD[20]          | PB       | V10        | P_AD[16]     | PB         |