# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

1545 Barber Lane Milpitas, CA 95035 Telephone: 408-232-9100 FAX: 408-434-1040 Internet: http://www.diodes.com

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

A. Life support devices or systems are devices or systems which:

1. are intended to implant into the body, or

2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the

failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated

www.diodes.com

### **REVISION HISTORY**

| Date     | Revision Number | Description                                 |  |  |

|----------|-----------------|---------------------------------------------|--|--|

| 09/12/14 | 0.1             | Preliminary Datasheet                       |  |  |

| 12/09/15 | 1.0             | Updated Section 1 Feature                   |  |  |

|          |                 | Updated Section 6.3 Configuration Registers |  |  |

|          |                 | Updated Section 9 Electrical Specification  |  |  |

| 01/06/16 | 1.1             | Updated Section 9 Electrical Specification  |  |  |

|          |                 | Updated Section 11 Ordering Information     |  |  |

| 08/25/16 | 1.2             | Updated Section 4 Pin Assignment            |  |  |

|          |                 | Updated Section 11 Ordering Information     |  |  |

| 12/02/16 | 1.3             | Updated Section 4 Pin Assignment            |  |  |

|          |                 | Updated Section 9 Electrical Specification  |  |  |

### **Table of Contents**

| 1. | FEATU          | RES                                                                         | 8   |

|----|----------------|-----------------------------------------------------------------------------|-----|

| 2. | APPLIC         | ATIONS                                                                      | 8   |

| 3. | GENER          | AL DESCRIPTION                                                              | 9   |

| 4. | PIN ASS        | IGNMENT                                                                     | .11 |

| 5. | FUNCT          | IONAL DESCRIPTION                                                           | .13 |

| 5  |                | NFIGURATION SPACE                                                           |     |

| 0  | 5.1.1.         | PCI Configuration Space                                                     |     |

|    | 5.1.2.         | UART Configuration Space                                                    |     |

| 5  |                | VICE OPERATION.                                                             |     |

|    | 5.2.1.         | Configuration Access                                                        |     |

|    | 5.2.2.         | I/O Reads/Writes                                                            |     |

|    | 5.2.3.         | Memory Reads/Writes                                                         |     |

|    | 5.2.4.         | Mode Selection                                                              |     |

|    | 5.2.5.         | 450/550 Mode                                                                | .14 |

|    | 5.2.6.         | Enhanced 550 Mode                                                           | .14 |

|    | 5.2.7.         | Enhanced 950 Mode                                                           |     |

|    | 5.2.8.         | Transmit and Receive FIFOs                                                  |     |

|    | 5.2.9.         | Automated Flow Control                                                      |     |

|    | 5.2.10.        | Internal Loopback                                                           |     |

|    | 5.2.11.        | Crystal Oscillator                                                          |     |

|    | 5.2.12.        | Baud Rate Generation                                                        | .19 |

| 6. | PCI OPI        | ERATION                                                                     | .20 |

| 6  | .1. SUF        | PORTED PCI TRANSACTION                                                      | .20 |

| -  |                | JISTER TYPES                                                                |     |

| 6  |                | NFIGURATION REGISTERS                                                       |     |

| -  | 6.3.1.         | VENDOR ID REGISTER – OFFSET 00h                                             |     |

|    | 6.3.2.         | DEVICE ID REGISTER – OFFSET 00h                                             |     |

|    | 6.3.3.         | COMMAND REGISTER – OFFSET 04h                                               |     |

|    | 6.3.4.         | STATUS REGISTER – OFFSET 04h                                                |     |

|    | 6.3.5.         | REVISION ID REGISTER – OFFSET 08h                                           | .22 |

|    | 6.3.6.         | CLASS CODE REGISTER – OFFSET 08h                                            | .22 |

|    | 6.3.7.         | CACHE LINE REGISTER – OFFSET 0Ch                                            |     |

|    | <i>6.3.8</i> . | MASTER LATENCY TIMER REGISTER – OFFSET 0Ch                                  |     |

|    | 6.3.9.         | HEADER TYPE REGISTER – OFFSET 0Ch                                           |     |

|    | 6.3.10.        | BASE ADDRESS REGISTER 0 – OFFSET 10h                                        |     |

|    | 6.3.11.        | BASE ADDRESS REGISTER 1 – OFFSET 14h                                        |     |

|    | 6.3.12.        | SUBSYSTEM VENDOR REGISTER – OFFSET 2Ch                                      |     |

|    | 6.3.13.        | SUBSYSTEM ID REGISTER – OFFSET 2Ch                                          |     |

|    | 6.3.14.        | CAPABILITIES POINTER REGISTER – OFFSET 34h                                  |     |

|    | 6.3.15.        | INTERRUPT LINE REGISTER – OFFSET 3Ch                                        |     |

|    | 6.3.16.        | INTERRUPT PIN REGISTER – OFFSET 3Ch<br>EEPROM CONTROL REGISTER – OFFSET DCh |     |

|    | 6.3.17.        |                                                                             |     |

| 7. |                | EGISTER DESCRIPTION                                                         |     |

| 7  |                | GISTER TYPES                                                                |     |

| 7  |                | GISTERS IN I/O MODE                                                         |     |

|    | 7.2.1.         | RECEIVE HOLDING REGISTER – OFFSET 00h                                       | .26 |

| 7.2.2.          | TRANSMIT HOLDING REGISTER – OFFSET 00h                    | 27 |

|-----------------|-----------------------------------------------------------|----|

| 7.2.3.          | INTERRUPT ENABLE REGISTER – OFFSET 01h                    |    |

| 7.2.4.          | INTERRUPT STATUS REGISTER – OFFSET 02h                    |    |

| 7.2.5.          | FIFO CONTROL REGISTER – OFFSET 02h                        |    |

| 7.2.6.          | LINE CONTROL REGISTER – OFFSET 03h                        |    |

| 7.2.7.          | MODEM CONTROL REGISTER – OFFSET 04h                       | 20 |

| 7.2.8.          | LINE STATUS REGISTER – OFFSET 05h                         |    |

| 7.2.9.          | MODEM STATUS REGISTER – OFFSET 05/1                       |    |

| 7.2.10.         | SPECIAL FUNCTION REGISTER – OFFSET 001                    |    |

| 7.2.10.         | DIVISOR LATCH LOW REGISTER – OFFSET 00h, LCR[7] = 1       |    |

|                 |                                                           |    |

| 7.2.12.         | DIVISOR LATCH HIGH REGISTER – $OFFSET 01h$ , $LCR[7] = 1$ |    |

| <i>7.2.13</i> . | SAMPLE CLOCK REGISTER - OFFSET 02h, LCR[7] = 1            |    |

|                 | GISTERS IN MEMORY-MAPPING MODE                            |    |

| 7.3.1.          | RECEIVE HOLDING REGISTER – OFFSET 00h                     |    |

| 7.3.2.          | TRANSMIT HOLDING REGISTER – OFFSET 00h                    |    |

| <i>7.3.3</i> .  | INTERRUPT ENABLE REGISTER – OFFSET 01h                    |    |

| 7.3.4.          | INTERRUPT STATUS REGISTER – OFFSET 02h                    |    |

| 7.3.5.          | FIFO CONTROL REGISTER – OFFSET 02h                        |    |

| <i>7.3.6</i> .  | LINE CONTROL REGISTER – OFFSET 03h                        |    |

| 7.3.7.          | MODEM CONTROL REGISTER – OFFSET 04h                       | 40 |

| <i>7.3.8</i> .  | LINE STATUS REGISTER – OFFSET 05h                         | 41 |

| <i>7.3.9</i> .  | MODEM STATUS REGISTER – OFFSET 06h                        |    |

| 7.3.10.         | SPECIAL FUNCTION REGISTER – OFFSET 07h                    | 43 |

| 7.3.11.         | DIVISOR LATCH LOW REGISTER – OFFSET 08h                   |    |

| 7.3.12.         | DIVISOR LATCH HIGH REGISTER – OFFSET 09h                  |    |

| 7.3.13.         | ENHANCED FUNCTION REGISTER – OFFSET 0Ah                   |    |

| 7.3.14.         | XON SPECIAL CHARACTER 1 – OFFSET 0Bh.                     |    |

| 7.3.15.         | XON SPECIAL CHARACTER 2 – OFFSET 0Ch                      |    |

| 7.3.16.         | XOFF SPECIAL CHARACTER 1 – OFFSET 0Dh                     |    |

| 7.3.10.         | XOFF SPECIAL CHARACTER 2 – OFFSET 0Eh                     |    |

| 7.3.17.         | ADVANCE CONTROL REGISTER – OFFSET 0EH                     |    |

|                 | TRANSMIT INTERRUPT TRIGGER LEVEL – OFFSET 10h             |    |

| 7.3.19.         |                                                           |    |

| 7.3.20.         | RECEIVE INTERRUPT TRIGGER LEVEL – OFFSET 11h              |    |

| 7.3.21.         | FLOW CONTROL LOW TRIGGER LEVEL – OFFSET 12h               |    |

| 7.3.22.         | FLOW CONTROL HIGH TRIGGER LEVEL – OFFSET 13h              |    |

| 7.3.23.         | CLOCK PRESCALE REGISTER – OFFSET 14h                      |    |

| 7.3.24.         | RECEIVE FIFO DATA COUNTER – OFFSET 15h, SFR[6] = 0        |    |

| 7.3.25.         | LINE STATUS REGISTER COUNTER – OFFSET 15h, SFR[6] = 1     |    |

| 7.3.26.         | TRANSMIT FIFO DATA COUNTER – OFFSET 16h, SFR[7] = 1       | 47 |

| 7.3.27.         | SAMPLE CLOCK REGISTER – OFFSET 16h, SFR[7] = 0            | 48 |

| <i>7.3.28</i> . | GLOBAL LINE STATUS REGISTER – OFFSET 17h                  |    |

| <i>7.3.29</i> . | GLOBAL INTERRUPT ENABLE REGISTER – OFFSET 18h             | 48 |

| 7.3.30.         | GLOBAL INTERRUPT STATUS REGISTER – OFFSET 19h             | 49 |

| 7.3.31.         | TX OVERRUN REGISTER – OFFSET 1Ah                          | 49 |

| 7.3.32.         | RX OVERRUN REGISTER – OFFSET 1Bh                          | 49 |

| 7.3.33.         | INTERRUPT STATUS REGISTER – OFFSET 1Ch                    | 49 |

| 7.3.34.         | RX FIFO COUNTER – OFFSET 1Dh                              |    |

| 7.3.35.         | TX FIFO COUNTER – OFFSET 1Eh                              |    |

| 7.3.36.         | FCR MIRROR REGISTER – OFFSET 1Fh                          |    |

| 7.3.37.         | USER DEFINED TIMEOUT COUNTER REGISTER-1 – OFFSET 20h      |    |

| 7.3.38.         | USER DEFINED TIMEOUT COUNTER REGISTER-2 – OFFSET 21h      |    |

| 7.3.39.         | USER DEFINED TRIGGER LEVEL REGISTER – OFFSET 22h          |    |

| 7.3.40.         | USER DEFINED REGISTER ENABLE – OFFSET 23h                 |    |

| 7.3.40.         | TX IDLE COUNTER REGISTER– OFFSET 24h                      |    |

| 1.3.41.         | IA IDLE COUNTER REGISTER-OFFSET 2411                      |    |

|     | 7.3.42.                   | TX IDLE ENABLE REGISTER– OFFSET 25h                          | 51 |

|-----|---------------------------|--------------------------------------------------------------|----|

|     | 7.3.43.                   | SPECIAL CHARACTER 1 REGISTER- OFFSET 28h                     | 51 |

|     | 7.3.44.                   | SPECIAL CHARACTER 2 REGISTER- OFFSET 29h                     | 51 |

|     | 7.3.45.                   | SPECIAL CHARACTER 3 REGISTER- OFFSET 2Ah                     | 51 |

|     | 7.3.46.                   | SPECIAL CHARACTER 4 REGISTER– OFFSET 2Bh                     | 51 |

|     | 7.3.47.                   | SPECIAL CHARACTER ENABLE / CLEAR REGISTER- OFFSET 2Ch        | 51 |

|     | 7.3.48.                   | FLASH LSR/TX_EMPTY INTERRUPT REGISTER- OFFSET 2Dh            |    |

|     | <i>7.3.49</i> .           | IN BAND TRANSMIT FLOW CONTROL REGISTER- OFFSET 2Eh           | 52 |

|     | 7.3.50.                   | ADVANCE CONTROL REGISTER- OFFSET 2Fh                         |    |

|     | 7.3.51.                   | RECEIVE FIFO DATA REGISTERS – OFFSET 100h ~ 17Fh             |    |

|     | 7.3.52.                   | TRANSMIT FIFO DATA REGISTERS – OFFSET 100h ~ 17Fh            |    |

|     | 7. <i>3</i> . <i>53</i> . | LINE STATUS FIFO REGISTERS –OFFSET 180h ~ 1FFh               | 52 |

|     | 7.3.54.                   | GLOBAL INTERRUPT REGISTERS 0 –OFFSET 40h                     |    |

|     | 7.3.55.                   | GLOBAL INTERRUPT REGISTERS 1 –OFFSET 41h                     |    |

|     | 7.3.56.                   | GLOBAL INTERRUPT REGISTERS 2 –OFFSET 42h                     |    |

|     | 7.3.57.                   | GLOBAL INTERRUPT REGISTERS 3 –OFFSET 43h                     |    |

|     | 7.3.58.                   | TIMER CONTROL REGISTER –OFFSET 44h                           |    |

|     | 7.3.59.                   | TIMER/COUNTER LATCH LSB REGISTER –OFFSET 46h                 |    |

|     | 7.3.60.                   | TIMER/COUNTER LATCH MSB REGISTER –OFFSET 47h                 |    |

|     | 7.3.61.                   | SOFTWARE RESET REGISTER –OFFSET 4Ah                          |    |

|     | 7.3.62.                   | SLEEP MODE CONTROL REGISTER –OFFSET 4Bh                      |    |

|     | 7.3.63.                   | DEVICE REVISION REGISTER –OFFSET 4Ch                         |    |

|     | 7.3.64.                   | DEVICE IDENTIFICATION REGISTER –OFFSET 4Dh                   |    |

|     | 7.3.65.                   | SIMULTANEOUS CONFIGURATION ALL UART REGISTER –OFFSET 4Eh     |    |

|     | 7.3.66.                   | GENERALPURPOSE IO INTERRUPT MASK REGISTER –OFFSET 4Fh        |    |

|     | 7.3.67.                   | GENERALPURPOSE IO OUTPUT LEVEL CONTROL REGISTER –OFFSET 50h  |    |

|     | 7.3.68.                   | GENERALPURPOSE IO OUTPUT STATE CONTROL REGISTER –OFFSET 51h  |    |

|     | 7.3.69.                   | GENERALPURPOSE IO INPUT POLARITY SELECT REGISTER –OFFSET 52h |    |

|     | 7.3.70.                   | GENERALPURPOSE IO SELECT REGISTER –OFFSET 53h                | 56 |

| 8.  | EEPRO                     | M INTERFACE                                                  | 57 |

| 8   | 8.1. EEF                  | PROM MODE AT RESET                                           | 57 |

| -   |                           | PROM SPACE ADDRESS MAP AND DESCRIPTION                       |    |

| 9.  | ELECT                     | RICAL SPECIFICATION                                          | 58 |

| 10. | PACK                      | AGE INFORMATION                                              | 68 |

| 11. |                           | ER INFORMATION                                               |    |

### **Table of Tables**

| .14 |

|-----|

| .19 |

| .19 |

| .25 |

| .25 |

| .33 |

| .33 |

|     |

### **List of Figures**

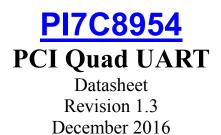

| FIGURE 3-1 PI7C8954 BLOCK DIAGRAM                                                  | 9  |

|------------------------------------------------------------------------------------|----|

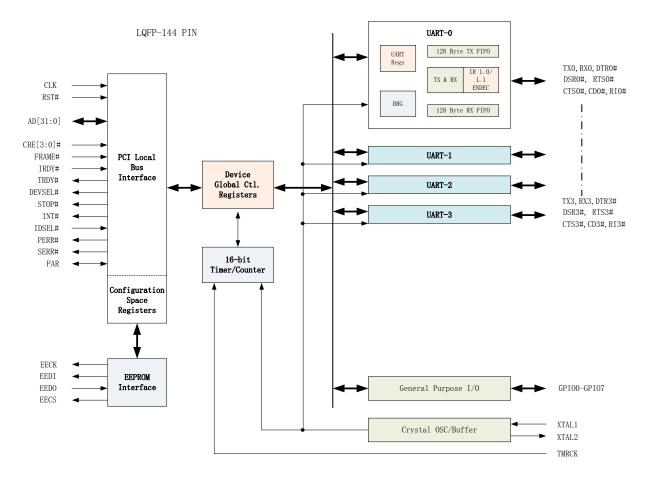

| FIGURE 3-2 PIN OUT                                                                 | 10 |

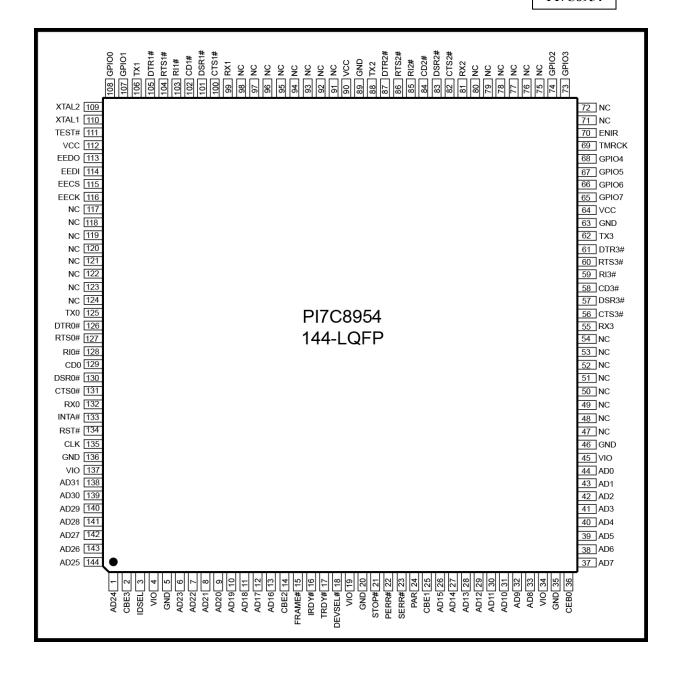

| FIGURE 5-1 TRANSMIT AND RECEIVE FIFOS                                              | 16 |

| FIGURE 5-2 INTERNAL LOOPBACK IN PI7C8954                                           | 17 |

| FIGURE 5-3 CRYSTAL OSCILLATOR AS THE CLOCK SOURCE                                  | 18 |

| FIGURE 5-4 EXTERNAL CLOCK SOURCE AS THE CLOCK SOURCE                               | 18 |

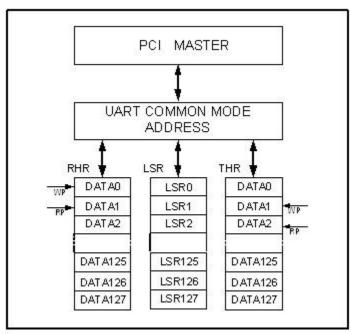

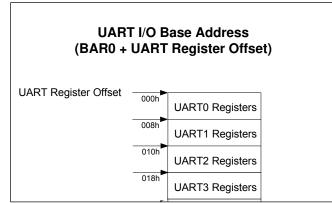

| FIGURE 7-1 UART REGISTER BLOCK ARRANGEMENT IN I/O MODE                             | 25 |

| FIGURE 7-2 UART REGISTER BLOCK ARRANGEMENT IN MEMORY MODE                          | 33 |

| FIGURE 9-1 TIMING FOR EXTERNAL CLOCK INPUT AT XTAL1 PIN                            | 62 |

| FIGURE 9-2 PCI BUS CONFIGURATION SPACE AND UART REGISTERS READ AND WRITE OPERATION | 63 |

| FIGURE 9-3 RECEIVE DATA BURST READ OPERATION                                       | 64 |

| FIGURE 9-4 TRANSMIT DATA BURST WRITE OPERATION                                     |    |

| FIGURE 9-5 5V PCI BUS CLOCK (DC TO 66MHz)                                          | 65 |

| FIGURE 9-6 3.3V PCI BUS CLOCK (DC TO 66MHZ)                                        | 66 |

| FIGURE 9-7 TRANSMIT DATA INTERRUPT AT TRIGGER LEVEL                                | 67 |

| FIGURE 9-8 RECEIVE DATA READY INTERRUPT AT TRIGGER LEVEL                           | 67 |

| FIGURE 10-1 PACKAGE OUTLINE DRAWING                                                | 69 |

|                                                                                    |    |

A Product Line of Diodes Incorporated

### **1. FEATURES**

- Four high performance 950-class UARTs

- Universal PCI Bus Buffers Auto sense 3.3V or 5V operation

- 32-bit PCI Bus 2.3 target signaling compliance

- Fully 16C550 software compatible UARTs

- 128-byte FIFO for each transmitter and receiver

- Baud rate up to 15 Mbps in asynchronous mode

- Flexible clock prescaler from 4 to 46

- Data Transfer in Byte, Word and Double-word

- Data Read/Write Burst Operation

- Automated in-band flow control using programmable Xon/Xoff in both directions

- Automated out-of-band flow control using CTS#/RTS# and/or DSR#/DTR#

- Arbitrary trigger levels for receiver and transmitter FIFO interrupts and automatic in-band and out-ofband flow control

- Global Interrupt Status and readable FIFO levels to facilitate implementation of efficient device drivers

- Detection of bad data in the receiver FIFO

- Data framing size including 5, 6, 7, 8 and 9 bits

- Infrared (IrDA 1.0/1.1) Data Encoder/Decoder

- Auto RS-485 Half-duplex Output with Control Polarity Selector

- Eight General Purpose Inputs/Outputs

- A General Purpose 16-bit Timer/Counter

- Hardware reconfiguration through Microwire compatible EEPROM

- Operations via I/O or memory mapping

- Sleep Mode with Automatic Wake-up

- Dual power operation (3.3V or 5.0V for PCI I/O and 1.8V-5.0V for UART I/O)

- Power dissipation: 0.2W typical in normal mode

- Industrial Temperature Range -40° to 85°

- 144-pin LQFP package

### 2. APPLICATIONS

- Remote Access Servers

- Network / Storage Management

- Factory Automation and Process Control

- Instrumentation

- Multi-port RS-232/ RS-422/ RS-485 Cards

- Point-of-Sale Systems (PoS)

- Industrial PC (IPC)

- Industrial Control

- Gaming Machines

- Building Automation

- Embedded Systems

| A Product Line of   |  |

|---------------------|--|

| Diodes Incorporated |  |

### 3. GENERAL DESCRIPTION

The PI7C8954 is a PCI Quad UART (Universal Asynchronous Receiver-Transmitters) I/O Bridge. It is specifically designed to meet the latest system requirements of high performance and lead (Pb) -free. The bridge can be used in a wide range of applications such as Remote Access Servers, Automation, Process Control, Instrumentation, POS, ATM and Multi-port RS232/ RS422/ RS485 Cards. The bridge supports four high performance UARTs, each of which supports Baud rate up to 15 Mbps in asynchronous mode. The UARTs support in-band and out-band auto flow control, arbitrary trigger level, I/O mapping and memory mapping, IrDA (Infrared Data Association) encoder/decoder, 8 general purpose I/O and 16-bit timer counter. The PI7C8954 is fully software compatible with 16C550 type device drivers and can be configured to fit the requirements of RS232, RS422 and RS485 applications. The EEPROM interface is provided for system implementation convenience. Some registers can be pre-programmed via hardware pin settings to facilitate system initialization. For programming flexibility, all of the default configuration registers can be overwritten by EEPROM data, such as sub-vendor and sub-system ID.

Figure 3-1 PI7C8954 Block Diagram

PERICOM PI7C8954

Figure 3-2 Pin Out

### 4. PIN ASSIGNMENT

| NAME            | PIN#            | TYPE   | DESCRIPTION                                                                                                                                                                           |  |

|-----------------|-----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PCI LOCAL BUS I |                 | T      | DCI Due most insult (active law) It most (1, DCI 1, 11, 11, 11, 11, 11, 11, 11, 11, 11,                                                                                               |  |

| RST#            | 134             | I      | PCI Bus reset input (active low). It resets the PCI local bus configuration space registers, device configuration registers and UART channel registers to the default condition.      |  |

| CLK             | 135             | Ι      | PCI Bus clock input of up to 33.34MHz.                                                                                                                                                |  |

| AD31-AD25,      | 138-144,        | I/O    | Address data lines [31:0] (bidirectional).                                                                                                                                            |  |

| AD24,           | 1,              | 1,0    |                                                                                                                                                                                       |  |

| AD23-AD16,      | 6-13            |        |                                                                                                                                                                                       |  |

| AD15-AD8,       | 26-33           |        |                                                                                                                                                                                       |  |

| AD7-AD0         | 37-44           |        |                                                                                                                                                                                       |  |

| FRAME#          | 15              | Ι      | Bus transaction cycle frame (active low). It indicates the beginning and duration of an access.                                                                                       |  |

| C/BE3#-C/BE0#   | 2,14,25,36      | Ι      | Bus Command/Byte Enable [3:0] (active low). This line is multiplexed for bus<br>Command during the address phase and Byte Enable during the data phase.                               |  |

| IRDY#           | 16              | Ι      | Initiator Ready (active low). During a write, it indicates valid data is present<br>on data bus. During a read, it indicates the master is ready to accept data.                      |  |

| TRDY#           | 17              | 0      | Target Ready (active low).                                                                                                                                                            |  |

| STOP#           | 21              | 0      | Target request to stop current transaction (active low).                                                                                                                              |  |

| IDSEL           | 3               | Ι      | Initialization device select (active high).                                                                                                                                           |  |

| DEVSEL#         | 18              | 0      | Device select to the PI7C8954 (active low).                                                                                                                                           |  |

| INTA#           | 133             | OD     | Device interrupt from PI7C8954 (open drain, active low).                                                                                                                              |  |

| PAR             | 24              | I/O    | Parity is even across AD[31:0] and C/BE[3:0]# (bidirectional, active high).                                                                                                           |  |

| PERR#           | 22              | 0      | Parity error indicator to host (active low). Optional in bus target application.                                                                                                      |  |

| SERR#           | 23              | OD     | System error indicator to host (open drain, active low). Optional in bus target application.                                                                                          |  |

| MODEM OR SERIA  | AL I/O INTERFAC | CE     |                                                                                                                                                                                       |  |

| TX0             | 125             | 0      | UART channel 0 Transmit Data or infrared transmit data. Normal TXD output idles HIGH while infrared TXD output idles LOW.                                                             |  |

| RX0             | 132             | Ι      | UART channel 0 Receive Data or infrared receive data. Normal RXD input idles HIGH. The infrared pulses typically idle LOW but can be inverted                                         |  |

| RTS0#           | 127             | 0      | internally prior the decoder by SFR[3].<br>UART channel 0 Request to Send or general purpose output (active low).                                                                     |  |

| CTS0#           | 131             | O<br>I | UART channel 0 Clear to Send of general purpose output (active low).                                                                                                                  |  |

| DTR0#           | 126             | 0      | UART channel 0 Data Terminal Ready or general purpose output (active low).                                                                                                            |  |

| DSR0#           | 130             | I      | UART channel 0 Data Terminar Ready or general purpose output (active low).                                                                                                            |  |

| CD0#            | 129             | I      | UART channel 0 Carrier Detect or general purpose input (active low).                                                                                                                  |  |

| RI0#            | 129             | I      | UART channel 0 Ring Indicator or general purpose input (active low).                                                                                                                  |  |

| TX1             | 128             | 0      | UART channel 1 Transmit Data or infrared transmit data. Normal TXD output idles HIGH while infrared TXD output idles LOW.                                                             |  |

| RX1             | 99              | Ι      | UART channel 1 Receive Data or infrared receive data. Normal RXD input idles HIGH. The infrared pulses typically idle LOW but can be inverted internally prior the decoder by SFR[3]. |  |

| RTS1#           | 104             | 0      | UART channel 1 Request to Send or general purpose output (active low).                                                                                                                |  |

| CTS1#           | 100             | Ι      | UART channel 1 Clear to Send or general purpose input (active low).                                                                                                                   |  |

| DTR1#           | 105             | 0      | UART channel 1 Data Terminal Ready or general purpose output (active low).                                                                                                            |  |

| DSR1#           | 101             | Ι      | UART channel 1 Data Set Ready or general purpose input (active low).                                                                                                                  |  |

| CD1#            | 102             | Ι      | UART channel 1 Carrier Detect or general purpose input (active low).                                                                                                                  |  |

| RI1#            | 103             | Ι      | UART channel 1 Ring Indicator or general purpose input (active low).                                                                                                                  |  |

| TX2             | 88              | 0      | UART channel 2 Transmit Data or infrared transmit data. Normal TXD output idles HIGH while infrared TXD output idles LOW.                                                             |  |

| RX2             | 81              | Ι      | UART channel 2 Receive Data or infrared receive data. Normal RXD input idles HIGH. The infrared pulses typically idle LOW but can be inverted internally prior the decoder by SFR[3]. |  |

| RTS2#           | 86              | 0      | UART channel 2 Request to Send or general purpose output (active low).                                                                                                                |  |

| CTS2#           | 82              | Ι      | UART channel 2 Clear to Send or general purpose input (active low).                                                                                                                   |  |

| DTR2#           | 87              | 0      | UART channel 2 Data Terminal Ready or general purpose output (active low).                                                                                                            |  |

| DSR2#           | 83              | Ι      | UART channel 2 Data Set Ready or general purpose input (active low).                                                                                                                  |  |

| CD2#            | 84              | Ι      | UART channel 2 Carrier Detect or general purpose input (active low).                                                                                                                  |  |

| RI2#            | 85              | Ι      | UART channel 2 Ring Indicator or general purpose input (active low).                                                                                                                  |  |

| TX3             | 62              | 0      | UART channel 3 Transmit Data or infrared transmit data. Normal TXD output                                                                                                             |  |

|                 |                 |        | idles HIGH while infrared TXD output idles LOW.                                                                                                                                       |  |

| NAME                   | PIN#            | TYPE     | DESCRIPTION                                                                                                                            |  |

|------------------------|-----------------|----------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| RX3                    | 55              | Ι        | UART channel 3 Receive Data or infrared receive data. Normal RXD input                                                                 |  |

|                        |                 |          | idles HIGH. The infrared pulses typically idle LOW but can be inverted                                                                 |  |

|                        |                 |          | internally prior the decoder by SFR[3].                                                                                                |  |

| RTS3#                  | 60              | 0        | UART channel 3 Request to Send or general purpose output (active low).                                                                 |  |

| CTS3#                  | 56              | I        | UART channel 3 Clear to Send or general purpose input (active low).                                                                    |  |

| DTR3#                  | 61              | 0        | UART channel 3 Data Terminal Ready or general purpose output (active low).                                                             |  |

| DSR3#                  | 57              | I        | UART channel 3 Data Set Ready or general purpose input (active low).                                                                   |  |

| CD3#                   | 58              | I        | UART channel 3 Carrier Detect or general purpose input (active low).                                                                   |  |

| RI3#<br>ANCILLARY SIGN | 59              | Ι        | UART channel 3 Ring Indicator or general purpose input (active low).                                                                   |  |

| GPIO0                  | 108             | I/O      | Multi-purpose input/output 0. The function of this pin is defined thru the                                                             |  |

|                        |                 |          | Configuration Register GPSEL, GPLVL, GPINV, GP3T and GPINT.                                                                            |  |

| GPIO1                  | 107             | I/O      | Multi-purpose input/output 1. The function of this pin is defined thru the Configuration Register GPSEL, GPLVL, GPINV, GP3T and GPINT. |  |

| GPIO2                  | 74              | I/O      | Multi-purpose input/output 2. The function of this pin is defined thru the Configuration Register GPSEL, GPLVL, GPINV, GP3T and GPINT. |  |

| GPIO3                  | 73              | I/O      | Multi-purpose input/output 3. The function of this pin is defined thru the                                                             |  |

| CDIO 4                 | (0)             | L/O      | Configuration Register GPSEL, GPLVL, GPINV, GP3T and GPINT.                                                                            |  |

| GPIO4                  | 68              | I/O      | Multi-purpose input/output 4. The function of this pin is defined thru the Configuration Register GPSEL, GPLVL, GPINV, GP3T and GPINT. |  |

| GPIO5                  | 67              | I/O      | Multi-purpose input/output 5. The function of this pin is defined thru the Configuration Register GPSEL, GPLVL, GPINV, GP3T and GPINT. |  |

| GPIO6                  | 66              | I/O      | Multi-purpose input/output 6. The function of this pin is defined thru the Configuration Register GPSEL, GPLVL, GPINV, GP3T and GPINT. |  |

| GPIO7/EN485#*          | 65              | I/O      | Multi-purpose input/output 7. The function of this pin is defined thru the                                                             |  |

|                        |                 |          | Configuration Register GPSEL, GPLVL, GPINV, GP3T and GPINT.                                                                            |  |

|                        |                 |          | Global Auto RS485 half-duplex direction control enable (active low). During                                                            |  |

|                        |                 |          | power up or reset, this pin is sampled and if it is a logic low, all UARTs are set                                                     |  |

|                        |                 |          | for Auto RS485 Mode. Also, the Auto RS485 bit, SFR[2], is set in all channels.                                                         |  |

|                        |                 |          | Software can override this pin thereafter and enable or disable it.                                                                    |  |

|                        |                 |          | *EN485# pin function is available when use Diodes' PCI UART driver, if use                                                             |  |

|                        |                 |          | customer own driver, they should implement this function by themselves.                                                                |  |

| EECK                   | 116             | 0        | Serial clock to EEPROM. An internal clock of CLK divide by 256 is used for                                                             |  |

|                        |                 |          | reading the vendor and sub-vendor ID and model number during power up or                                                               |  |

| EECS                   | 115             | 0        | reset.<br>Chip select to a EEPROM device like 93C46. Requires a pull-up 4.7K resistor                                                  |  |

| LLCS                   | 115             | 0        | for external sensing of EEPROM during power up.                                                                                        |  |

| EEDI                   | 114             | 0        | Write data to EEPROM device.                                                                                                           |  |

| EEDO                   | 113             | I        | Read data from EEPROM device.                                                                                                          |  |

| XTAL1                  | 110             | I        | Crystal of up to 24MHz or external clock input of up to 50MHz for data rates                                                           |  |

|                        |                 |          | up to 6.25 Mbps at 5V and 8X sampling. See AC Characterization table.                                                                  |  |

|                        |                 |          | Caution: this input is not 5V tolerant at 3.3V.                                                                                        |  |

| XTAL2                  | 109             | 0        | Crystal or buffered clock output.                                                                                                      |  |

| TMRCK                  | 69              | Ι        | 16-bit timer/counter external clock input.                                                                                             |  |

| ENIR                   | 70              | Ι        | Infrared mode enable (active high). This pin is sampled during power up,                                                               |  |

|                        |                 |          | following a hardware reset (RST#) or soft-reset (register SFRST). It can be                                                            |  |

|                        |                 |          | used to start up all 4 UARTs in the infrared mode. The sampled logic state is                                                          |  |

|                        |                 |          | transferred to MCR bit-6 in the UART. Software can override this pin thereafter                                                        |  |

| TEOT#                  | 111             | т        | and enable or disable it.                                                                                                              |  |

| TEST#<br>VCC           | 111 64, 90, 112 | I<br>PWR | Factory Test. Connect to VCC for normal operation.<br>Power supply for non-PCI signals and core logic. it can be 1.8V to 5.0V, no      |  |

| VCC                    | 04, 90, 112     | ΓWK      | matter if VIO is 3.3V or 5.0V. However VCC must equal VIO at sleep mode to                                                             |  |

|                        |                 |          | minimize the power current.                                                                                                            |  |

| VIO                    | 4, 19, 34, 45,  | PWR      | PCI bus I/O power supply - 3.3V or 5V, detected by the auto-sense circuitry of                                                         |  |

|                        | 137             | 1,010    | the PI7C8954. This power supply determines the VOH level of the PCI bus                                                                |  |

|                        | 157             |          | interface outputs. (PCI 2.3 signalling compliant at both 3.3V and 5V operation,                                                        |  |

|                        |                 |          | suitable for universal form factor add-in card application.)                                                                           |  |

| GND                    | 5, 20, 35, 46,  | PWR      | Power supply common, ground.                                                                                                           |  |

|                        | 63, 89, 136     |          |                                                                                                                                        |  |

| NC                     | 47-54, 71, 72,  |          | No Connection. These pins are reserved and used by the octal PCI UARTs                                                                 |  |

|                        | 75-80, 91-98,   |          | PI7C8958.                                                                                                                              |  |

|                        | 117-124         |          |                                                                                                                                        |  |

NOTE: Pin Type: I = Input, O = Output, I/O = Input/Output, OD = Output Open Drain

### 5. FUNCTIONAL DESCRIPTION

The PI7C8954 is an integrated solution of four high-performance 16C550 UARTs with one PCI host interface. The PCI interface allows direct access to the configuration and status registers of the UART channels.

The UARTs in the PI7C8954 support the complete register set of the 16C550-type devices. The UARTs support Baud Rates up to 15 Mbps in asynchronous mode. Each UART channel has 128-byte deep transmit and receive FIFOs. The high-speed FIFOs reduce CPU utilization and improve data throughput. In addition, the UARTs support enhanced features including automated in-band flow control using programmable Xon/Xoff in both directions, automated out-band flow control using CTS#/RTS# and/or DRS#/DTR#, and arbitrary transmit and receive trigger levels.

### **5.1. CONFIGURATION SPACE**

The PI7C8954 has two sets of registers to allow various configuration and status monitoring functions. The PCI Configuration Space Registers enable the plug-and-play and auto-configuration when the device is connected to the PCI system bus. The UART configuration and internal registers enable the general UART operation functions, status control and monitoring.

### 5.1.1. PCI Configuration Space

The PI7C8954 is recognized as a PCI endpoint, which is mapped into the configuration space as a single logical device. Each endpoint in the system, including the PI7C8954, is part of a Hierarchy Domains originated by the Host, which is a tree with a Root Port at its head in the configuration space. The device configuration registers are implemented for the user to access the functionalities provided by the PCI specification.

All PCI endpoints facilitate a PCI-compatible configuration space to maintain compatibility with PCI software configuration mechanism. PCI Local Bus Specification, Revision 3.0 allocates 256 bytes per device function. The user can access the PCI 3.0 compatible region either by conventional PCI 3.0 configuration addresses

### 5.1.2. UART Configuration Space

Through the UART registers, the user can control and monitor various functionalities of the UARTs on the PI7C8954 including FIFOs, interrupt status, line status, modem status and sample clock. Each of the UART's transmitter and receive data FIFOs can be conveniently accessed by reading and writing the registers in the UART configuration space. These registers allow flexible programming capability and versatile device operations of the PI7C8954. Each UART is accessed through an 8-byte I/O blocks. The addresses of the UART blocks are offset by the base address referred by the Base Address Register (BAR). The value of the base address is loaded from the I/O or Memory Base Address defined in the PCI configuration space.

The PI7C8954 also supports enhanced features such as Xon/Xoff, automatic flow control, Baud Rate prescaling and various status monitoring. These enhanced features are available through the memory address offset by the BAR in the PCI configuration space.

The basic features available in the registers in I/O mode are also available in the registers in memorymapping mode. Accesses to these registers are equivalent in these two modes.

The UARTs on the PI7C8954 supports operations in 16C450, 16C550 and 16C950 modes. These modes of

Page 13 of 69 www.diodes.com

operation are selected by writing the SFR, FCR and EFR registers. The PI7C8954 is backward compatible with these modes of operation.

### **5.2. DEVICE OPERATION**

The PI7C8954 is configured by the Host in the bootstrap process during system start-up. The Host performs bus scans and recognizes the device by reading vendor and device IDs. Upon successful device identification, the system then loads device-specific driver software and allocates I/O, memory and interrupt resources. The driver software allows the user to access the functions of the device by reading and writing the UART registers. The PCI interface incorporates convenient device operation and high system performance.

### 5.2.1. Configuration Access

The PI7C8954 accepts type 0 configuration read and write accesses defined in the PCI 3.0 Specification.

### 5.2.2. I/O Reads/Writes

The PCI interface of the PI7C8954 decodes incoming transaction packets. If the address is within the region assigned by the I/O Base Address Registers, the transaction is recognized as an I/O Read or Write.

### 5.2.3. Memory Reads/Writes

Similar to the I/O Read/Write, if the address of the transaction packet is within the memory range, a Memory Read/Write occurs.

### 5.2.4. Mode Selection

All of the internal UART channels in the I/O Bridge support the 16C450, 16C550, Enhanced 16C550, and Enhanced 950 UART Modes. The mode of the UART operation is selected by toggling the Special Function Register (SFR[5]) and Enhanced Function Register (EFR[4]). The FIFO depth of each mode and the mode selection is tabulated in the table below.

| Table 5-1 Mode Selection |        |        |                  |  |  |  |

|--------------------------|--------|--------|------------------|--|--|--|

| UART Mode                | SFR[5] | EFR[4] | <b>FIFO Size</b> |  |  |  |

| 450/550                  | Х      | 0      | 1/16             |  |  |  |

| Enhanced 550             | 0      | 1      | 128              |  |  |  |

| Enhanced 950             | 1      | 1      | 128              |  |  |  |

### 5.2.5. 450/550 Mode

The 450 Mode is inherently supported when 550 Mode is selected. When in the 450 Mode, the FIFOs are in the "Byte Mode", which refers to the one-byte buffer in the Transmit Holding Register and the Receive Holding Register in each of the UART channels. When in the 550 Mode, the UARTs support an increased FIFO depth of 16.

When EFR[4] is set to "0", the SFR[5] is ignored, and the 450/550 Mode is selected.

### 5.2.6. Enhanced 550 Mode

Setting the SFR[5] to "0" and EFR[4] to "1" enables the Enhanced 550 Mode. The Enhanced 550 Mode further increases FIFO depth to 128.

Page 14 of 69 www.diodes.com

### 5.2.7. Enhanced 950 Mode

128-deep FIFOs are supported in the Enhanced 950 Mode. When the Enhanced 950 Mode is enabled, the UART channels support additional features:

- Sleep mode

- Special character detection

- Automatic in-band flow control

- Automatic flow control using selectable arbitrary thresholds

- Readable status for automatic in-band and out-of-band flow control

- Flexible clock prescaler

- Programmable sample clock

- DSR/DTR automatic flow control

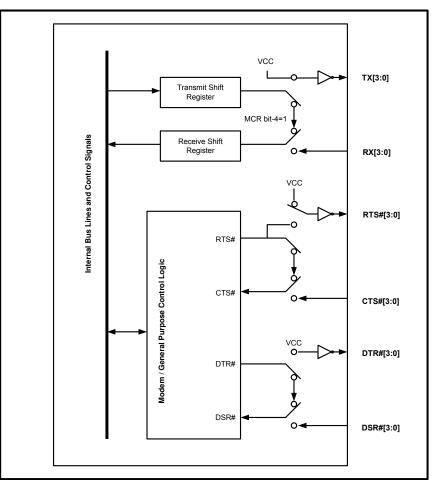

#### 5.2.8. Transmit and Receive FIFOs

Each channel of the UARTs consists of 128 bytes of transmit FIFOs and 128 bytes of receive FIFOs, namely the Transmit Holding Registers (THR) and the Receive Holding Registers (RHR). The FIFOs provide storage space for the data before they can be transmitted or processed. The THR and RHR operate simultaneously to transmit and read data.

The transmitter reads data from the THR into the Transmit Shift Register (TSR) and removes the data from top of the THR. It then converts the data into serial format with start and stop bits and parity bits if required. If the transmitter completes transmitting the data in the TSR and the THR is empty, the transmitter is in the idle state. The data that arrive most recently are written to the bottom of the THR. If the THR is full, and the user attempts to write data to the THR, a data overrun occurs and the data is lost.

The receiver writes data to the bottom of the RHR when it finishes receiving and decoding the data bits. If the RHR is full when the receiver attempts to write data to it, a data overrun occurs. Any read operation to an empty RHR is invalid.

The empty and full status of the THR and RHR can be determined by reading the empty and full flags in the Line Status Register (LSR). When the transmitter and receiver are ready to transfer data to and from the FIFOs, interrupts are raised to signal this condition. Additionally, the user can use the Receive FIFO Data Counter (RFDC) and Transmit FIFO Data Counter (TFDC) registers to determine the number of items in each FIFO.

Figure 5-1 Transmit and Receive FIFOs

### 5.2.9. Automated Flow Control

The device uses automatic in-band flow control to prevent data-overrun to the local receive FIFO and remote receive FIFO. This feature works in conjunction with the special character detection. When an XOFF condition is detected, the UART transmitter will suspend any further data transmission after the current character transmission is completed. The transmitter will resume data-transmission as soon as an XON condition is detected. The automatic in-band feature is enabled by the Enhanced Function Register (EFR). EFR[1:0] enables the in-band receive flow control, and EFR[3:2] enables the in-band transmit flow control.

The out-of-band flow control utilizes RTS# and CTS# pins to suspend and resume the data transmission and to prevent data-overrun. An asserted CTS# pin signals the UART to suspend transmission due to a full remote receive FIFO. Upon detecting an asserted CTS# pin, the UART will complete the current character transmission and enters idle mode until the CTS# pin is deserted.

The UART deasserts RTS# to signal the remote transmitter that the local receive FIFO reaches the programmed upper trigger level. When the local receive FIFO falls below the programmed lower trigger level, the RTS# is reasserted. The automatic out-of-band flow control is enabled by EFR[7:6].

### 5.2.10. Internal Loopback

The internal loopback capability of the UARTs is enabled by setting Modem Control Register bit-4 (MCR[4]) to 1. When the feature is enabled, the data from the output of the transmit shift register are looped back to the input of the receive shift register. This feature provides the users a way to perform system diagnostics by allowing the UART to receive the same data it is sending.

Figure 5-2 Internal Loopback in PI7C8954

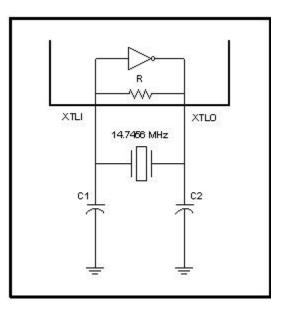

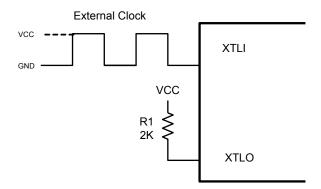

### 5.2.11. Crystal Oscillator

The PI7C8954 uses a crystal oscillator or an external clock source to provide system clock to the Baud Rate Generator. When a clock source is used, the clock signal should be connected to the XTLI pin, and a 2K pull-up resistor should be connected to the XTLO pin.

When a crystal oscillator is used, the XTLI is the input and XTLO is the output, and the crystal should be connected in parallel with two capacitors.

### 5.2.12. Baud Rate Generation

The built-in Baud Rate Generator (BRG) allows a wide range of input frequency and flexible Baud Rate generation. To obtain the desired Baud Rate, the user can set the Sample Clock Register (SCR), Divisor Latch Low Register (DLL), Divisor Latch High Register (DLH) and Clock Prescale Registers (CPRM and CPRN). The Baud Rate is generated according to the following equation:

$BaudRate = \frac{InputFrequency}{Divisor*\Pr escaler}$

The parameters in the equation above can be programmed by setting the "SCR", "DLL", "DLH", "CPRM" and "CPRN" registers according to the table below.

| Table 5-2 Badd Kate Generator Setting |                                    |  |  |  |

|---------------------------------------|------------------------------------|--|--|--|

| Setting                               | Description                        |  |  |  |

| Divisor                               | DLL + (256 * DLH)                  |  |  |  |

| Prescaler                             | $2^{M-1}$ * (SampleClock + N)      |  |  |  |

| SampleClock                           | 16-SCR, (SCR = '0h' to 'Ch')       |  |  |  |

| М                                     | CPRM, (CPRM = $(01h)$ to $(02h)$ ) |  |  |  |

| Ν                                     | CPRN, (CPRN = $(0h' to (7h'))$     |  |  |  |

#### Table 5-2 Baud Rate Generator Setting

To ensure the proper operation of the Baud Rate Generator, users should avoid setting the value '0' to Sample Clock, Divisor and Prescaler.

The following table lists some of the commonly used Baud Rates and the register settings that generate a specific Baud Rate. The examples assume an Input Clock frequency of 14.7456 Mhz. The SCR register is set to '0h', and the CPRM and CPRN registers are set to '1h' and '0h' respectively. In these examples, the Baud Rates can be generated by different combination of the DLH and DLL register values.

| Table 5-5 Sample Datu Rate Setting |     |     |  |  |  |

|------------------------------------|-----|-----|--|--|--|

| <b>Baud Rate</b>                   | DLH | DLL |  |  |  |

| 1,200                              | 3h  | 00h |  |  |  |

| 2,400                              | 1h  | 80h |  |  |  |

| 4,800                              | 0h  | C0h |  |  |  |

| 9,600                              | 0h  | 60h |  |  |  |

| 19,200                             | 0h  | 30h |  |  |  |

| 28,800                             | 0h  | 20h |  |  |  |

| 38,400                             | 0h  | 18h |  |  |  |

| 57,600                             | 0h  | 10h |  |  |  |

| 115,200                            | 0h  | 08h |  |  |  |

| 921,600                            | 0h  | 01h |  |  |  |

#### Table 5-3 Sample Baud Rate Setting

### 6. PCI OPERATION

### 6.1. SUPPORTED PCI TRANSACTION

- Configuration access: The PI7C8954 responds to type 0 configuration reads and writes if the IDSEL signal is asserted and the bus address is selecting function 0 registers. Any other configuration transaction will be ignored.

- I/O read/writes: The address is compared with the addresses reserved in the I/O Base Address Registers (BARs) to decide if the transaction should be ignored (Master abort). Only I/O byte accesses are possible. If multiple bytes is enabled during I/O transaction, only the first byte is valid and all other bytes are ignored.

- Memory reads/writes: The address is compared with the addresses reserved in the Mem Base Address Register. If the memory transaction is targeting to the registers, only first byte is valid and all other bytes are ignored and device will complete the burst transaction as disconnect-with-data. If the memory transaction is targeting to FIFOs, burst (multiple Dword) transaction is supported.

- All other cycles (64-bit, special cycles, reserved encoding etc.) are ignored.

- The PI7C8954 performs medium-speed address decoding as defined by the PCI specification. The Fast back-to-back transactions are supported.

- The PI7C8954 performs parity generation and checking on all PCI bus transactions as defined by PCI spec. If a parity error occurs during the PCI bus address phase, the device will report the error in the standard way by asserting the SERR# bus signal.

### 6.2. REGISTER TYPES

| REGISTER TYPE | DEFINITION              |

|---------------|-------------------------|

| RO            | Read Only               |

| RW            | Read / Write            |

| RWC           | Read / Write 1 to Clear |

### **6.3. CONFIGURATION REGISTERS**

The following table details the allocation of the register fields of the PCI 2.3 compatible type 0 configuration space header.

| 31 – 24  | 23 - 16            | 15 - 8                  | 7 - 0                      | BYTE OFFSET |  |  |

|----------|--------------------|-------------------------|----------------------------|-------------|--|--|

| Devi     | ce ID              | Vend                    | or ID                      | 00h         |  |  |

| Sta      | atus               | Com                     | mand                       | 04h         |  |  |

|          | Class Code         |                         | Revision ID                | 08h         |  |  |

| Reserved | Header Type        | Master Latency<br>Timer | Cache Line Size            | 0Ch         |  |  |

|          | IO BAR             | Register                |                            | 10h         |  |  |

|          | MEM BA             | R Register              |                            | 14h         |  |  |

|          | Reserved           |                         |                            |             |  |  |

| Subsy    | stem ID            | Subsystem Vendor ID     |                            | 2Ch         |  |  |

|          | Reserved           |                         |                            |             |  |  |

|          | Capability Pointer |                         |                            |             |  |  |

|          | Rese               | rved                    |                            | 38h         |  |  |

| Res      | erved              | Interrupt Pin           | Interrupt Line             | 3Ch         |  |  |

|          | Reserved           |                         |                            |             |  |  |

| EEPRO    | EEPROM Data        |                         | EEPROM Control<br>/ Status | DCh         |  |  |

|          | Rese               | rved                    |                            | E0h - FCh   |  |  |

### 6.3.1. VENDOR ID REGISTER - OFFSET 00h

| BIT  | FUNCTION  | TYPE | DESCRIPTION                                                                                                                           |

|------|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | Vendor ID | RO   | Identifies Pericom as the vendor of this I/O bridge. The default value may be changed by auto-loading from EEPROM.<br>Reset to 12D8h. |

### 6.3.2. DEVICE ID REGISTER - OFFSET 00h

| BIT   | FUNCTION  | TYPE | DESCRIPTION                                                                                                                     |

|-------|-----------|------|---------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | Device ID | RO   | Identifies this I/O bridge as the PI7C8954. The default value may be<br>changed by auto-loading from EEPROM.<br>Reset to 8954h. |

#### 6.3.3. COMMAND REGISTER - OFFSET 04h

| BIT   | FUNCTION                              | TYPE | DESCRIPTION                                                                                                                                                                                                                                                               |

|-------|---------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | I/O Space Enable                      | RW   | Controls a device's response to I/O Space accesses. A value of 0 disables the device response. A value of 1 allows the device to respond to I/O Space accesses.<br>Reset to 0b.                                                                                           |

| 1     | Memory Space<br>Enable                | RW   | Controls a device's response to Memory Space accesses. A value of<br>0 disables the device response. A value of 1 allows the device to<br>response to memory Space accesses.<br>Reset to 0b.                                                                              |

| 2     | Bus Master Enable                     | RO   | It is not implemented. Hardwired to 0b.                                                                                                                                                                                                                                   |

| 3     | Special Cycle<br>Enable               | RO   | Does not apply to PCI. Must be hardwired to 0b.                                                                                                                                                                                                                           |

| 4     | Memory Write And<br>Invalidate Enable | RO   | Does not apply to PCI. Must be hardwired to 0b.                                                                                                                                                                                                                           |

| 5     | VGA Palette Snoop<br>Enable           | RO   | Does not apply to PCI. Must be hardwired to 0b.                                                                                                                                                                                                                           |

| 6     | Parity Error<br>Response Enable       | RW   | Controls the device's response to parity errors. When the bit is set,<br>the device must take its normal action when a parity error is<br>detected. When the bit is 0, the device sets its Detected Parity Error<br>Status bit when an error is detected.<br>Reset to 0b. |

| 7     | Wait Cycle Control                    | RO   | Does not apply to PCI. Must be hardwired to 0b.                                                                                                                                                                                                                           |

| 8     | SERR# enable                          | RW   | This bit, when set, enables the assertion of SERR# when detected<br>System Error by the device.<br>Reset to 0b.                                                                                                                                                           |

| 9     | Fast Back-to-Back<br>Enable           | RO   | Does not apply to PCI. Must be hardwired to 0b.                                                                                                                                                                                                                           |

| 10    | Interrupt Disable                     | RW   | Controls the ability of the I/O bridge to generate INTx interrupt<br>Messages.<br>Reset to 0b.                                                                                                                                                                            |

| 15:11 | Reserved                              | RO   | Reset to 00000b.                                                                                                                                                                                                                                                          |

### 6.3.4. STATUS REGISTER – OFFSET 04h

| BIT   | FUNCTION          | TYPE | DESCRIPTION                                                                                   |

|-------|-------------------|------|-----------------------------------------------------------------------------------------------|

| 18:16 | Reserved          | RO   | Reset to 000b.                                                                                |

| 19    | Interrupt Status  | RO   | Indicates that an INTx interrupt Message is pending internally to the device.<br>Reset to 0b. |

| 20    | Capabilities List | RO   | RO as 0b.                                                                                     |

| BIT   | FUNCTION                     | TYPE | DESCRIPTION                             |

|-------|------------------------------|------|-----------------------------------------|

| 21    | 66MHz Capable                | RO   | Reset to 0b.                            |

| 22    | Reserved                     | RO   | Reset to 0b.                            |

| 23    | Fast Back-to-Back<br>Capable | RO   | RO as 1b.                               |

| 24    | Master Data Parity<br>Error  | RWC  | It is not implemented. Hardwired to 0b. |

| 26:25 | DEVSEL# Timing               | RO   | Reset to 01b.                           |

| 27    | Signaled Target<br>Abort     | RWC  | This bit does not apply to UART device. |

| 28    | Received Target<br>Abort     | RWC  | It is not implemented. Hardwired to 0b. |

| 29    | Received Master<br>Abort     | RWC  | Reset to 0b.                            |

| 30    | Signaled System<br>Error     | RWC  | Reset to 0b.                            |

| 31    | Detected Parity<br>Error     | RWC  | Reset to 0b.                            |

### 6.3.5. REVISION ID REGISTER - OFFSET 08h

| BIT | FUNCTION | TYPE | DESCRIPTION                                                                                                                    |

|-----|----------|------|--------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | Revision | RO   | Indicates revision number of the I/O bridge. The default value may<br>be changed by auto-loading from EEPROM.<br>Reset to 00h. |

### 6.3.6. CLASS CODE REGISTER - OFFSET 08h

| BIT   | FUNCTION        | TYPE | DESCRIPTION                                                 |

|-------|-----------------|------|-------------------------------------------------------------|

| 15:8  | Programming     | RO   | Read as 02h to indicate no programming interfaces have been |

|       | Interface       |      | defined for PCI-to-PCI bridges                              |

| 23:16 | Sub-Class Code  | RO   | Read as 00h to indicate device is PCI-to-PCI bridge         |

| 31:24 | Base Class Code | RO   | Read as 07h to indicate device is a bridge device           |

### 6.3.7. CACHE LINE REGISTER – OFFSET 0Ch

| BIT | FUNCTION        | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                 |

|-----|-----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | Cache Line Size | RW   | The cache line size register is set by the system firmware and the operating system to system cache line size. This field is implemented by PCI devices as a RW field for legacy compatibility purposes but has no impact on any PCI device functionality.<br>Reset to 00h. |

### 6.3.8. MASTER LATENCY TIMER REGISTER – OFFSET 0Ch

| BIT  | FUNCTION      | TYPE | DESCRIPTION                                      |

|------|---------------|------|--------------------------------------------------|

| 15:8 | Latency timer | RO   | Does not apply to PCI. Must be hardwired to 00h. |

#### 6.3.9. HEADER TYPE REGISTER – OFFSET 0Ch

| BIT   | FUNCTION    | TYPE | DESCRIPTION                                                                                                          |

|-------|-------------|------|----------------------------------------------------------------------------------------------------------------------|

| 23:16 | Header Type | RO   | Read as 00h to indicate that the register layout conforms to the standard PCI-to-PCI bridge layout.<br>Reset to 00h. |

| 31:24 | Reserved    | RO   | Reset to 00h                                                                                                         |

### 6.3.10. BASE ADDRESS REGISTER 0 – OFFSET 10h

| BIT  | FUNCTION       | TYPE | DESCRIPTION                                                                                                                                       |  |

|------|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:0 | Base Address 0 | RW   | Use this I/O base address to map the UART 16550 compatible<br>registers.<br>The base address can be allocated to 64 Bytes.<br>Reset to 00000001h. |  |

### 6.3.11. BASE ADDRESS REGISTER 1 – OFFSET 14h

| BIT  | FUNCTION       | TYPE | DESCRIPTION                                                                                                                                                        |  |

|------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:0 | Base Address 1 | RW   | Use this memory base address to map the UART 16550 compatible<br>and enhanced registers.<br>The base address can be allocated to 4096 Bytes.<br>Reset to 00000000h |  |

#### 6.3.12. SUBSYSTEM VENDOR REGISTER – OFFSET 2Ch

| BIT  | FUNCTION      | TYPE | DESCRIPTION                                                                                       |

|------|---------------|------|---------------------------------------------------------------------------------------------------|

| 15:0 | Sub Vendor ID | RO   | Indicates the sub-system vendor id. The default value may be changed by auto-loading from EEPROM. |

|      |               |      | Reset to 0000h.                                                                                   |

#### 6.3.13. SUBSYSTEM ID REGISTER – OFFSET 2Ch

| BIT              | FUNCTION      | TYPE  | DESCRIPTION                                                                                       |  |

|------------------|---------------|-------|---------------------------------------------------------------------------------------------------|--|

| 31:16 Sub System | Sub System ID | ID RO | Indicates the sub-system device id. The default value may be changed by auto-loading from EEPROM. |  |

|                  |               |       | Reset to 0000h.                                                                                   |  |