# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **PIC12LF1552 Memory Programming Specification**

# This document includes the programming specifications for the following device:

• PIC12LF1552

### 1.0 OVERVIEW

The device can be programmed using either the highvoltage In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) method or the low-voltage ICSP<sup>™</sup> method.

#### 1.1 Hardware Requirements

#### 1.1.1 HIGH-VOLTAGE ICSP PROGRAMMING

In High-Voltage ICSP<sup>™</sup> mode, this device requires two programmable power supplies: one for VDD and one for the MCLR/VPP pin.

#### 1.1.2 LOW-VOLTAGE ICSP PROGRAMMING

In Low-Voltage ICSP<sup>™</sup> mode, this device can be programmed using <u>a single</u> VDD source in the operating range. The MCLR/VPP pin does not have to be brought to a different voltage, but can instead be left at the normal operating voltage.

#### 1.1.2.1 Single-Supply ICSP Programming

The LVP bit in Configuration Word 2 enables singlesupply (low-voltage) ICSP programming. The LVP bit defaults to a '1' (enabled) from the factory. The LVP bit may only be programmed to '0' by entering the High-Voltage ICSP mode, where the MCLR/VPP pin is raised to VIHH. Once the LVP bit is programmed to a '0', only the High-Voltage ICSP mode is available and only the High-Voltage ICSP mode can be used to program the device.

Note 1: The High-Voltage ICSP mode is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR/ VPP pin.

> 2: While in Low-Voltage ICSP mode, MCLR is always enabled, regardless of the MCLRE bit, and the port pin can no longer be used as a general purpose input.

### 1.2 Pin Utilization

Five pins are needed for ICSP<sup>TM</sup> programming. The pins are listed in Table 1-1.

#### TABLE 1-1:PIN DESCRIPTIONS DURING PROGRAMMING

| Din Nama     | During Programming  |                  | 9 Programming                                |

|--------------|---------------------|------------------|----------------------------------------------|

| Pin Name     | Function            | Pin Type         | Pin Description                              |

| RA1          | ICSPCLK             | I                | Clock Input – Schmitt Trigger Input          |

| RA0          | ICSPDAT             | I/O              | Data Input/Output – Schmitt Trigger Input    |

| MCLR/Vpp/RA3 | Program/Verify mode | P <sup>(1)</sup> | Program Mode Select/Programming Power Supply |

| Vdd          | Vdd                 | Р                | Power Supply                                 |

| Vss          | Vss                 | Р                | Ground                                       |

Legend: I = Input, O = Output, P = Power

**Note 1:** The programming high voltage is internally generated. To activate the Program/Verify mode, high voltage needs to be applied to MCLR input. Since the MCLR is used for a level source, MCLR does not draw any significant current.

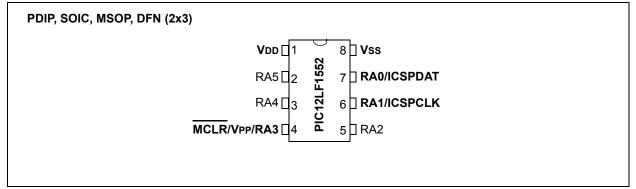

## 2.0 DEVICE PINOUTS

The pin diagram is shown in Figure 2-1. The pins that are required for programming are listed in Table 1-1 and shown in bold lettering in the pin diagram.

#### FIGURE 2-1: 8-PIN PDIP, SOIC, MSOP, DFN DIAGRAM FOR PIC12LF1552

### 3.0 MEMORY MAP

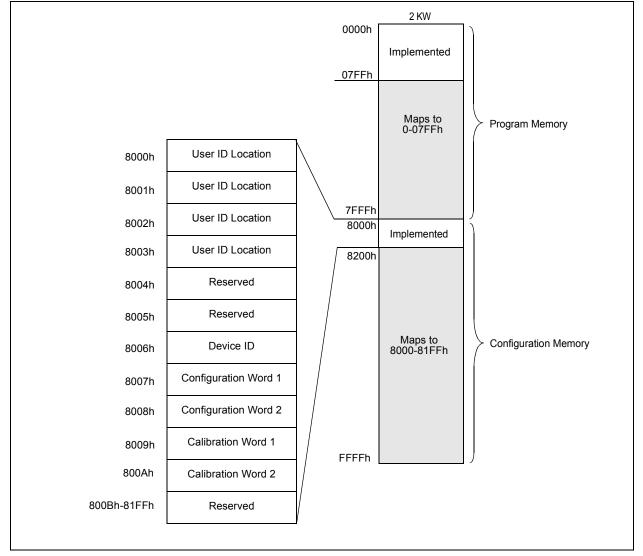

The memory is broken into two sections: program memory and configuration memory.

FIGURE 3-1: PIC12LF1552 PROGRAM MEMORY MAPPING

#### 3.1 User ID Location

A user may store identification information (user ID) in four designated locations. The user ID locations are mapped to 8000h-8003h. Each location is 14 bits in length. Code protection has no effect on these memory locations. Each location may be read with code protection enabled or disabled.

Note: MPLAB<sup>®</sup> IDE only displays the seven Least Significant bits (LSb) of each user ID location, the upper bits are not read. It is recommended that only the seven LSbs be used if MPLAB IDE is the primary tool used to read these addresses.

#### 3.2 Device ID

The device ID word is located at 8006h. This location is read-only and cannot be erased or modified.

#### **REGISTER 3-1:** DEVICE ID: DEVICE ID REGISTER<sup>(1)</sup>

|                |      | R      | R                | R    | R    | R                  | R     |

|----------------|------|--------|------------------|------|------|--------------------|-------|

|                |      | DEV8   | DEV7             | DEV6 | DEV5 | DEV4               | DEV3  |

|                |      | bit 13 |                  |      |      |                    | bit 8 |

|                |      |        |                  |      |      |                    |       |

| R              | R    | R      | R                | R    | R    | R                  | R     |

| DEV2           | DEV1 | DEV0   | REV4             | REV3 | REV2 | REV1               | REV0  |

| bit 7          |      |        |                  |      |      |                    | bit 0 |

|                |      |        |                  |      |      |                    |       |

| Legend:        |      |        |                  |      |      |                    |       |

| R = Readable b | it   |        | '1' = Bit is set |      |      | '0' = Bit is clear | red   |

bit 13-5 **DEV<8:0>:** Device ID bits

These bits are used to identify the part number.

bit 4-0 **REV<4:0>:** Revision ID bits

These bits are used to identify the revision.

**Note 1:** This location cannot be written.

#### TABLE 3-1:DEVICE ID VALUES

| DEVICE      | DEVICE II     | O VALUES |

|-------------|---------------|----------|

| DEVICE      | DEV           | REV      |

| PIC12LF1552 | 0010 1011 110 | x xxxx   |

#### 3.3 Configuration Words

There are two Configuration Words, Configuration Word 1 (8007h) and Configuration Word 2 (8008h). The individual bits within these Configuration Words are used to enable or disable device functions such as the Brown-out Reset, code protection and Power-up Timer.

#### 3.4 Calibration Words

The internal calibration values are factory calibrated and stored in Calibration Words 1 and 2 (8009h, 800Ah).

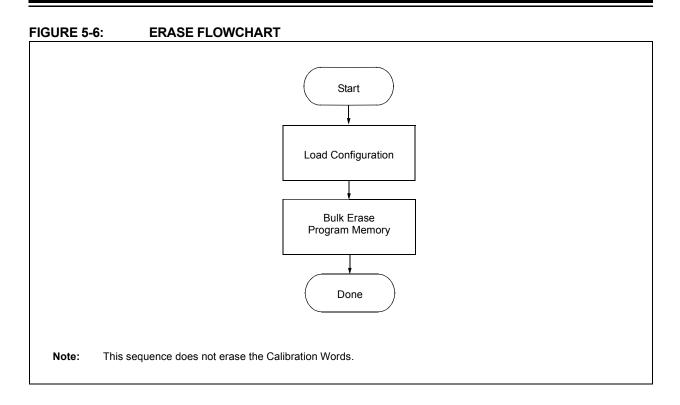

The Calibration Words do not participate in erase operations. The device can be erased without affecting the Calibration Words.

| REGISTER 3-2: CONFIGURATION WORD T | REGISTER 3-2: | <b>CONFIGURATION WORD 1</b> |

|------------------------------------|---------------|-----------------------------|

|------------------------------------|---------------|-----------------------------|

|                      |                                                                                        | U-1                                                                                                               | U-1                                                                          | R/P-1                                         | R/P-1             | R/P-1             | U-1 <sup>(3)</sup> |

|----------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------|-------------------|-------------------|--------------------|

|                      |                                                                                        | _                                                                                                                 | —                                                                            | CLKOUTEN                                      | BORE              | N<1:0>            | _                  |

|                      |                                                                                        | bit 13                                                                                                            |                                                                              |                                               |                   |                   | bit                |

| R/P-1                | R/P-1                                                                                  | R/P-1                                                                                                             | R/P-1                                                                        | R/P-1                                         | U-1               | R/P-1             | R/P-1              |

|                      | MCLRE                                                                                  | PWRTE                                                                                                             |                                                                              | TE<1:0>                                       |                   | FOSC              |                    |

| bit 7                | MOLINE                                                                                 | TWICIE                                                                                                            |                                                                              |                                               |                   | 1000              | bit                |

| Legend:              |                                                                                        |                                                                                                                   |                                                                              |                                               |                   |                   |                    |

| R = Readable         | e bit                                                                                  | P = Programm                                                                                                      | able bit                                                                     | U = Unimplemer                                | nted bit, read as | '1'               |                    |

| '0' = Bit is cle     | ared                                                                                   | '1' = Bit is set                                                                                                  |                                                                              | -n = Value when                               | blank or after B  | ulk Erase         |                    |

| bit 13-12            | Unimplement                                                                            | ed: Read as '1'                                                                                                   |                                                                              |                                               |                   |                   |                    |

| bit 11               | CLKOUTEN: C<br>1 = CLKOUT                                                              | lock Out Enable b                                                                                                 | d. I/O or oscillato                                                          | r function on CLKOU                           | T pin.            |                   |                    |

| bit 10-9             | When enabled,<br>11 = Brown-ou<br>10 = Brown-ou<br>01 = Brown-ou                       | t Reset enabled. S<br>t Reset enabled w                                                                           | Voltage (VBOR) is<br>PBOREN bit is ig<br>hile running and o<br>by the SBOREN | disabled in Sleep. SB<br>bit in the BORCON re | OREN bit is igno  | Ũ                 | er.                |

| bit 8 <sup>(3)</sup> | Unimplemented: Read as '1'                                                             |                                                                                                                   |                                                                              |                                               |                   |                   |                    |

| bit 7                | Ũ                                                                                      | ection bit <sup>(2)</sup><br>emory code protec<br>emory code protec                                               |                                                                              |                                               |                   |                   |                    |

| bit 6                | <u>If LVP bit = 1</u> :<br>This bit is i<br><u>If LVP bit = 0</u> :<br>1 = <u>MCLR</u> | VPP pin function is                                                                                               | MCLR; Weak pul                                                               | I-up enabled.<br>R internally disabled;       | Weak pull-up und  | er control of WPU | A register.        |

| bit 5                |                                                                                        | r-up Timer Enable<br>sabled                                                                                       |                                                                              | ,, <b>,</b> ,                                 |                   |                   |                    |

| bit 4-3              | 11 = WDT ena<br>10 = WDT ena<br>01 = WDT con                                           | Vatchdog Timer Er<br>abled. SWDTEN is<br>abled while running<br>ttrolled by the SWI<br>abled. SWDTEN is           | ignored.<br>and disabled in<br>DTEN bit in the W                             | Sleep. SWDTEN is iç<br>DTCON register         | gnored.           |                   |                    |

| bit 2                | Unimplement                                                                            | ed: Read as '1'                                                                                                   |                                                                              |                                               |                   |                   |                    |

| bit 1-0              | 11 = ECH: E<br>10 = ECM: E<br>01 = ECL: E                                              | escillator Selection<br>External Clock, Hig<br>External Clock, Me<br>External Clock, Low<br>C oscillator: I/O fun | h-Power mode: c<br>dium-Power mod<br>⁄-Power mode: or                        | e: on CLKIN pin<br>n CLKIN pin                |                   |                   |                    |

| <b>2</b> : 1         | Enabling Brown-out                                                                     | Reset does not au<br>memory will be era                                                                           | tomatically enab<br>ased when the co                                         | le Power-up Timer.<br>de protection is turne  | ed off.           |                   |                    |

**3:** This bit should be maintained as '1' when programmed.

### REGISTER 3-3: CONFIGURATION WORD 2

|                                       |                                                                                                                                                 | R/P-1                                                           | U-1                              | R/P-1                                     | R/P-1 | R/P-1 | U-1   |  |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------|-------------------------------------------|-------|-------|-------|--|--|

|                                       | LVP — <u>LPBOR</u> BORV STVREN —                                                                                                                |                                                                 |                                  |                                           |       |       |       |  |  |

|                                       |                                                                                                                                                 | bit 13                                                          |                                  | ·                                         | •     |       | bit 8 |  |  |

| U-1                                   | U-1                                                                                                                                             | U-1                                                             | U-1                              | U-1                                       | U-1   | R/P-1 | R/P-1 |  |  |

| _                                     |                                                                                                                                                 | _                                                               | _                                | _                                         | _     | WRT<  | :1:0> |  |  |

| bit 7                                 |                                                                                                                                                 |                                                                 |                                  |                                           |       |       | bit ( |  |  |

|                                       |                                                                                                                                                 |                                                                 |                                  |                                           |       |       |       |  |  |

| Legend:                               |                                                                                                                                                 |                                                                 |                                  |                                           |       |       |       |  |  |

| R = Readable bit P = Programmable bit |                                                                                                                                                 |                                                                 | U = Unimpleme                    | nted bit, read as                         | s '1' |       |       |  |  |

| '0' = Bit is cle                      | cleared '1' = Bit is set                                                                                                                        |                                                                 |                                  | -n = Value when blank or after Bulk Erase |       |       |       |  |  |

| bit 12<br>bit 11                      | Unimplemented: Read as '1'<br><b>LPBOR:</b> Low-Power BOR bit<br>1 = Low-Power BOR is disabled<br>0 = Low-Power BOR is enabled                  |                                                                 |                                  |                                           |       |       |       |  |  |

| bit 10                                | BORV: Brown-out Reset Voltage Selection bit<br>1 = Brown-out Reset Voltage (VBOR) set to 1.9V<br>0 = Brown-out Reset Voltage (VBOR) set to 2.7V |                                                                 |                                  |                                           |       |       |       |  |  |

| bit 9                                 | STVREN: Sta<br>1 = Stack Ove                                                                                                                    | ck Overflow/Under<br>erflow or Underflow<br>erflow or Underflow | flow Reset Ena<br>will cause a R | able bit<br>leset                         |       |       |       |  |  |

| bit 8-2                               | Unimplemente                                                                                                                                    | ed: Read as '1'                                                 |                                  |                                           |       |       |       |  |  |

| bit 1-0                               | 11 = Write pr<br>10 = 000h to                                                                                                                   | 1FFh write-protect<br>3FFh write-protect                        | ed, 200h to 7F                   | Fh may be modifie                         |       |       |       |  |  |

Note 1: The LVP bit cannot be programmed to '0' when Programming mode is entered via LVP.

### 4.0 PROGRAM/VERIFY MODE

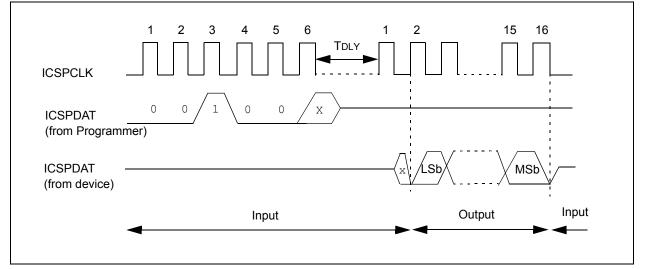

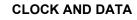

In Program/Verify mode, the program memory and the configuration memory can be accessed and programmed in serial fashion. ICSPDAT and ICSPCLK are used for the data and the clock, respectively. All commands and data words are transmitted LSb first. Data changes on the rising edge of the ICSPCLK and latched on the falling edge. In Program/Verify mode, both the ICSPDAT and ICSPCLK are Schmitt Trigger inputs. The sequence that enters the device into Program/Verify mode places all other logic into the Reset state. Upon entering Program/Verify mode, all I/Os are automatically configured as high-impedance inputs and the address is cleared.

#### 4.1 High-Voltage Program/Verify Mode Entry and Exit

There are two different methods of entering Program/ Verify mode via high voltage:

- VPP First entry mode

- VDD First entry mode

#### 4.1.1 VPP – FIRST ENTRY MODE

To enter Program/Verify mode via the VPP-first method the following sequence must be followed:

- 1. Hold ICSPCLK and ICSPDAT low. All other pins should be unpowered.

- 2. Raise the voltage on MCLR from 0V to VIHH.

- 3. Raise the voltage on VDD from 0V to the desired operating voltage.

The VPP-first entry prevents the device from executing code prior to entering Program/Verify mode. For example, the device will execute code when Configuration Word 1 has MCLR disabled (MCLRE = 0), the Power-up Timer is disabled (PWRTE = 0), the internal oscillator is selected (FOSC = 100), and ICSPCLK and ICSPDAT pins are driven by the user application. Since this may prevent entry, VPP-first entry mode is strongly recommended. See the timing diagram in Figure 8-2.

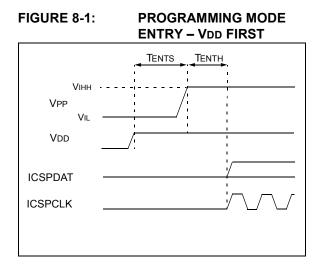

#### 4.1.2 VDD – FIRST ENTRY MODE

To enter Program/Verify mode via the VDD-first method the following sequence must be followed:

- 1. Hold ICSPCLK and ICSPDAT low.

- 2. Raise the voltage on VDD from 0V to the desired operating voltage.

- 3. Raise the voltage on MCLR from VDD or below to VIHH.

The VDD-first method is useful when programming the device when VDD is already applied, for it is not necessary to disconnect VDD to enter Program/Verify mode. See the timing diagram in Figure 8-1.

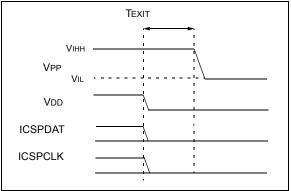

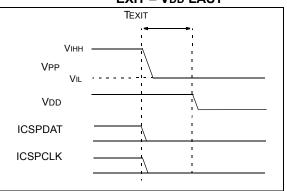

#### 4.1.3 PROGRAM/VERIFY MODE EXIT

To exit Program/Verify mode take  $\overline{\text{MCLR}}$  to VDD or lower (VIL). See Figures 8-3 and 8-4.

#### 4.2 Low-Voltage Programming (LVP) Mode

The Low-Voltage Programming mode allows the device to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Word 2 register is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'. This can only be done while in the High-Voltage Entry mode.

Entry into the Low-Voltage ICSP Program/Verify modes requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

The key sequence is a specific 32-bit pattern, '0100 1101 0100 0011 0100 1000 0101 0000' (more easily remembered as MCHP in ASCII). The device will enter Program/Verify mode only if the sequence is valid. The Least Significant bit of the Least Significant nibble must be shifted in first.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

For low-voltage programming timing, see Figure 8-8 and Figure 8-9.

Exiting <u>Program/Verify</u> mode is done by no longer driving MCLR to VIL. See Figure 8-8 and Figure 8-9.

**Note:** To enter LVP mode, the LSB of the Least Significant nibble must be shifted in first. This differs from entering the key sequence on other parts.

### 4.3 **Program/Verify Commands**

The device implements ten programming commands; each six bits in length. The commands are summarized in Table 4-1.

Commands that have data associated with them are specified to have a minimum delay of TDLY between the command and the data. After this delay 16 clocks are required to either clock in or clock out the 14-bit data word. The first clock is for the Start bit and the last clock is for the Stop bit.

#### TABLE 4-1:COMMAND MAPPING

| Command                            |   |      |        | Маррі | ing  |   |     | Data/Note        |

|------------------------------------|---|------|--------|-------|------|---|-----|------------------|

| Command                            |   | Bina | ary (M | Sb I  | LSb) |   | Hex |                  |

| Load Configuration                 | Х | 0    | 0      | 0     | 0    | 0 | 00h | 0, data (14), 0  |

| Load Data For Program Memory       | Х | 0    | 0      | 0     | 1    | 0 | 02h | 0, data (14), 0  |

| Read Data From Program Memory      | Х | 0    | 0      | 1     | 0    | 0 | 04h | 0, data (14), 0  |

| Increment Address                  | Х | 0    | 0      | 1     | 1    | 0 | 06h | —                |

| Reset Address                      | Х | 1    | 0      | 1     | 1    | 0 | 16h | —                |

| Begin Internally Timed Programming | х | 0    | 1      | 0     | 0    | 0 | 08h | —                |

| Begin Externally Timed Programming | Х | 1    | 1      | 0     | 0    | 0 | 18h | —                |

| End Externally Timed Programming   | Х | 0    | 1      | 0     | 1    | 0 | 0Ah | —                |

| Bulk Erase Program Memory          | х | 0    | 1      | 0     | 0    | 1 | 09h | Internally Timed |

| Row Erase Program Memory           | х | 1    | 0      | 0     | 0    | 1 | 11h | Internally Timed |

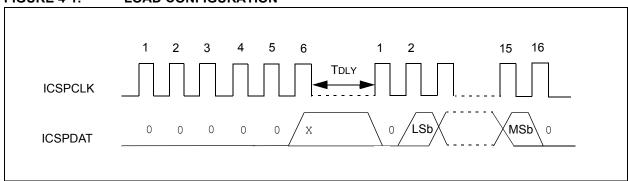

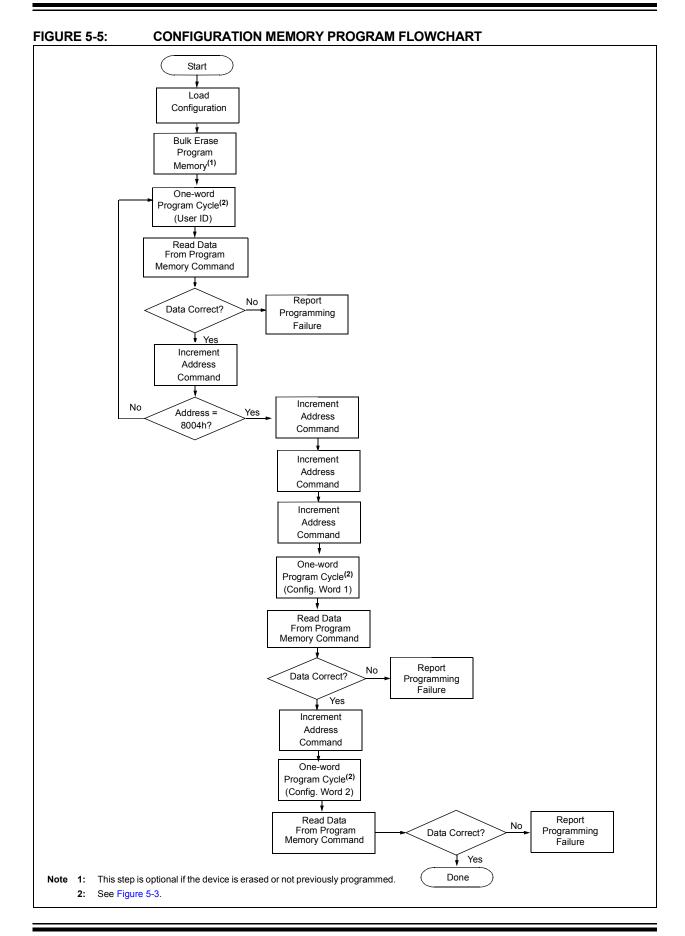

#### 4.3.1 LOAD CONFIGURATION

The Load Configuration command is used to access the configuration memory (user ID locations, Configuration Words, Calibration Words). The Load Configuration command sets the address to 8000h and loads the data latches with one word of data (see Figure 4-1).

After issuing the Load Configuration command, use the Increment Address command until the proper address to be programmed is reached. The address is then programmed by issuing either the Begin Internally Timed Programming or Begin Externally Timed Programming command.

| or Calibration Word will have no effect on<br>the targeted word. |  | Externally timed writes are not supported<br>for Configuration and Calibration bits. Any<br>externally timed write to the Configuration<br>or Calibration Word will have no effect on<br>the targeted word. |

|------------------------------------------------------------------|--|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------|--|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

The only way to get back to the program memory (address 0) is to exit Program/Verify mode or issue the Reset Address command after the configuration memory has been accessed by the Load Configuration command.

#### FIGURE 4-1: LOAD CONFIGURATION

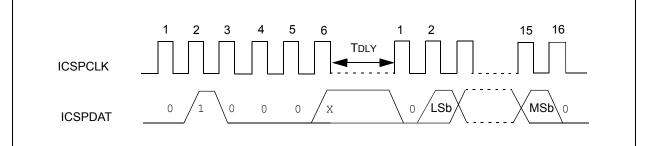

# 4.3.2 LOAD DATA FOR PROGRAM MEMORY

The Load Data for Program Memory command is used to load one 14-bit word into the data latches. The word programs into program memory after the Begin Internally Timed Programming or Begin Externally Timed Programming command is issued (see Figure 4-2).

#### FIGURE 4-2: LOAD DATA FOR PROGRAM MEMORY

# 4.3.3 READ DATA FROM PROGRAM MEMORY

The Read Data from Program Memory command will transmit data bits out of the program memory map currently accessed, starting with the second rising edge of the clock input. The ICSPDAT pin will go into Output mode on the first falling clock edge, and it will revert to Input mode (high-impedance) after the 16th falling edge of the clock. If the program memory is code-protected  $(\overline{CP})$ , the data will be read as zeros (see Figure 4-3).

#### FIGURE 4-3: READ DATA FROM PROGRAM MEMORY

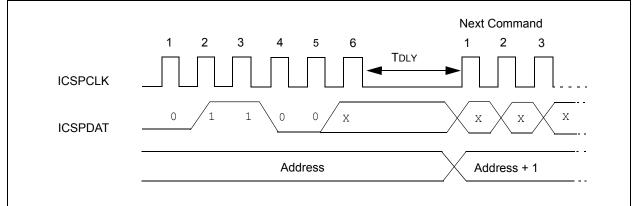

#### 4.3.4 INCREMENT ADDRESS

The address is incremented when this command is received. It is not possible to decrement the address. To reset this counter, the user must use the Reset Address command or exit Program/Verify mode and reenter it. If the address is incremented from address 7FFFh, it will wrap-around to location 0000h. If the address is incremented from FFFFh, it will wrap-around to location 8000h.

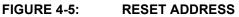

#### 4.3.5 RESET ADDRESS

The Reset Address command will reset the address to 0000h, regardless of the current value. The address is used in program memory or the configuration memory.

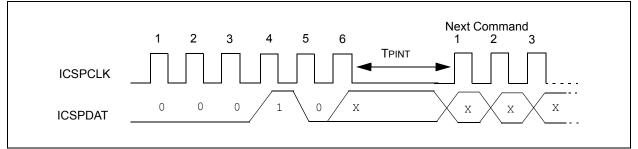

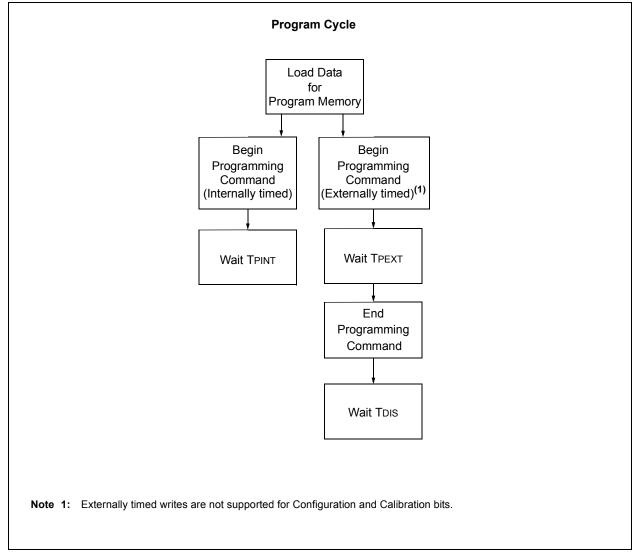

#### 4.3.6 BEGIN INTERNALLY TIMED PROGRAMMING

A Load Configuration or Load Data for Program Memory command must be given before every Begin Programming command. Programming of the addressed memory will begin after this command is received. An internal timing mechanism executes the write. The user must allow for the program cycle time, TPINT, for the programming to complete.

The End Externally Timed Programming command is not needed when the Begin Internally Timed Programming is used to start the programming.

The program memory address that is being programmed is not erased prior to being programmed.

#### FIGURE 4-6: BEGIN INTERNALLY TIMED PROGRAMMING

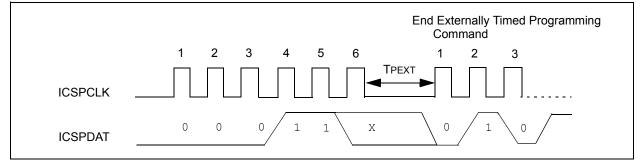

#### 4.3.7 BEGIN EXTERNALLY TIMED PROGRAMMING

A Load Configuration or Load Data for Program Memory command must be given before every Begin Programming command. Programming of the addressed memory will begin after this command is received. To complete the programming, the End Externally Timed Programming command must be sent in the specified time window defined by TPEXT (see Figure 4-7).

Externally timed writes are not supported for Configuration and Calibration bits. Any externally timed write to the Configuration or Calibration Word will have no effect on the targeted word.

#### FIGURE 4-7: BEGIN EXTERNALLY TIMED PROGRAMMING

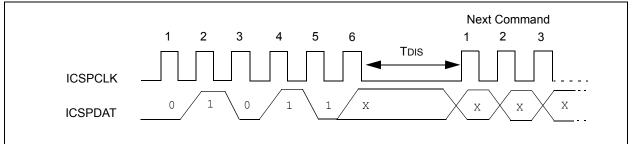

# 4.3.8 END EXTERNALLY TIMED PROGRAMMING

This command is required after a Begin Externally Timed Programming command is given. This command must be sent within the time window specified by TPEXT, after the Begin Externally Timed Programming command is sent.

After sending the End Externally Timed Programming command, an additional delay (TDIS) is required before sending the next command. This delay is longer than the delay ordinarily required between other commands (see Figure 4-8).

#### FIGURE 4-8: END EXTERNALLY TIMED PROGRAMMING

#### 4.3.9 BULK ERASE PROGRAM MEMORY

The Bulk Erase Program Memory command performs two different functions dependent on the current state of the address.

Address 0000h-7FFFh:

Program Memory is erased Configuration Words are erased

#### Address 8000h-8008h:

Program Memory is erased

Configuration Words are erased

User ID Locations are erased

A Bulk Erase Program Memory command should not be issued when the address is greater than 8008h.

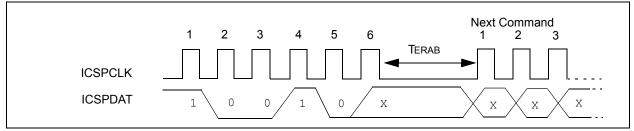

#### FIGURE 4-9: BULK ERASE PROGRAM MEMORY

After receiving the Bulk Erase Program Memory command, the erase will not complete until the time interval, TERAB, has expired.

Note: The code protection Configuration bit  $\overline{(CP)}$  has no effect on the Bulk Erase Program Memory command.

#### 4.3.10 ROW ERASE PROGRAM MEMORY

The Row Erase Program Memory command will erase an individual row. Refer to Table 4-2 for row sizes of the device and the PC bits used to address them. If the program memory is code-protected, the Row Erase Program Memory command will be ignored. When the address is 8000h-8008h, the Row Erase Program Memory command will only erase the user ID locations, regardless of the setting of the  $\overline{CP}$  Configuration bit.

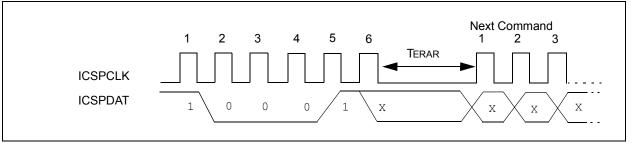

After receiving the Row Erase Program Memory command, the erase will not complete until the time interval, TERAR, has expired.

#### TABLE 4-2:PROGRAMMING ROW SIZE AND LATCHES

| Device      | PC     | Row Size | Number of Latches |

|-------------|--------|----------|-------------------|

| PIC12LF1552 | <15:4> | 16       | 16                |

#### FIGURE 4-10: ROW ERASE PROGRAM MEMORY

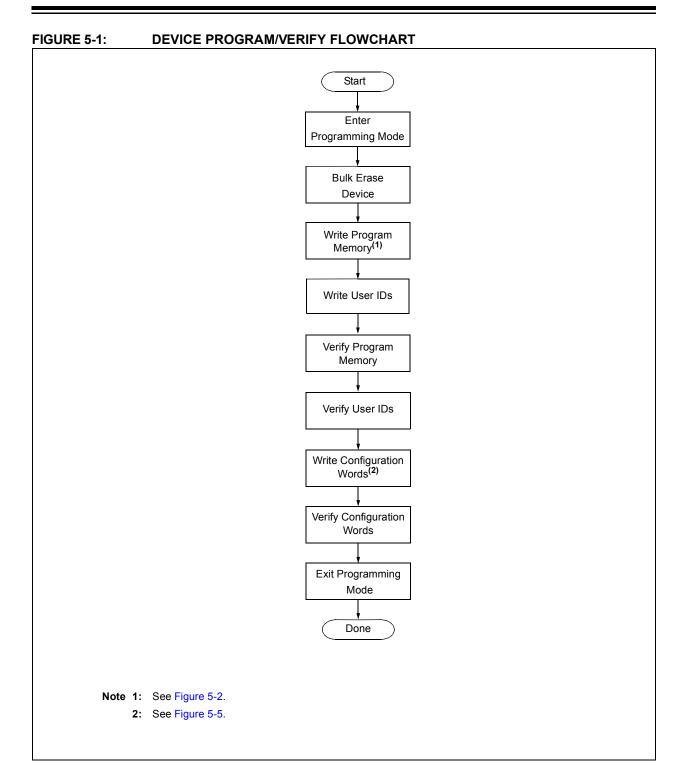

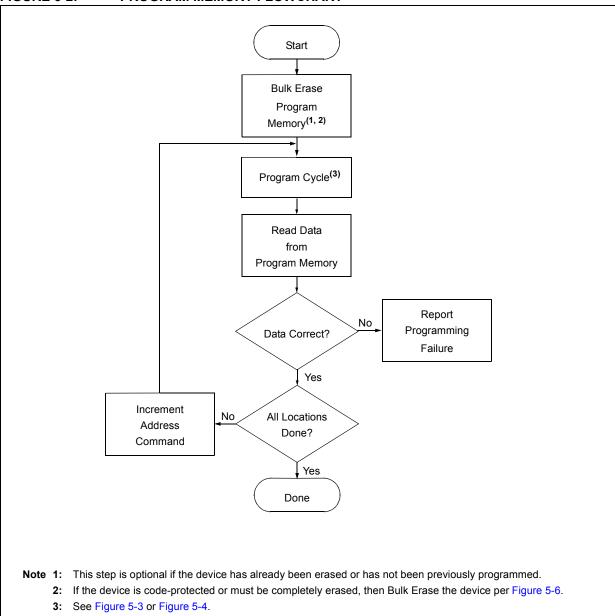

## 5.0 PROGRAMMING ALGORITHMS

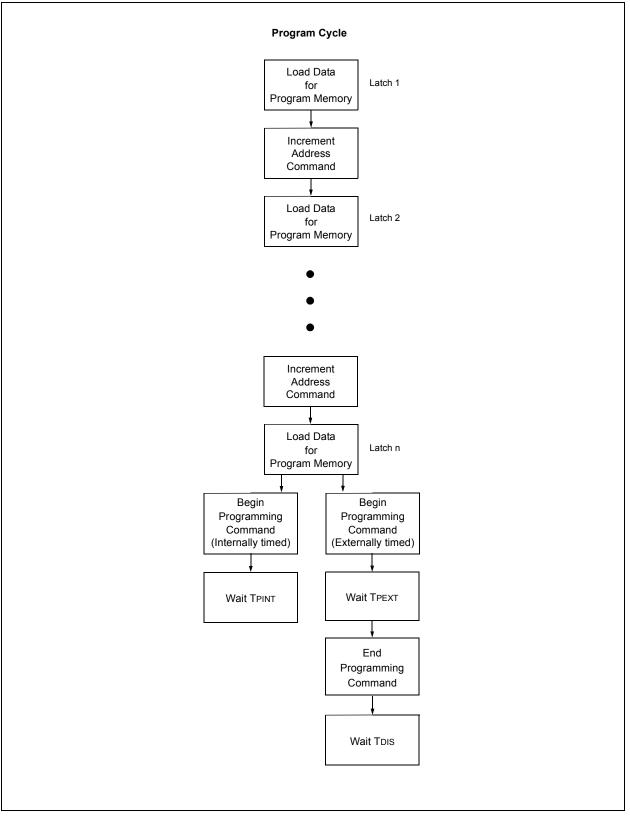

The device uses internal latches to temporarily store the 14-bit words used for programming. Refer to Table 4-2 for specific latch information. The data latches allow the user to write the program words with a single Begin Externally Timed Programming or Begin Internally Timed Programming command. The Load Program Data or the Load Configuration command is used to load a single data latch. The data latch will hold the data until the Begin Externally Timed Programming or Begin Internally Timed Programming command is given.

The data latches are aligned with the LSbs of the address. The PC's address at the time the Begin Externally Timed Programming or Begin Internally Timed Programming command is given will determine which location(s) in memory are written. Writes cannot cross the physical boundary. For example, attempting to write from address 0002h-0009h will result in data being written to 0008h-000Fh.

If more than the maximum number of data latches are written without a Begin Externally Timed Programming or Begin Internally Timed Programming command, the data in the data latches will be overwritten. The following figures show the recommended flowcharts for programming.

© 2012 Microchip Technology Inc.

DS41642A-page 15

## 6.0 CODE PROTECTION

Code protection is controlled using the  $\overline{CP}$  bit in Configuration Word 1. When code protection is enabled, all program memory locations (0000h-7FFFh) read as '0'. Further programming is disabled for the program memory (0000h-7FFFh).

The user ID locations and Configuration Words can be programmed and read out regardless of the code protection settings.

### 6.1 **Program Memory**

Code protection is enabled by programming the  $\overline{CP}$  bit in Configuration Word 1 register to '0'.

The only way to disable code protection is to use the Bulk Erase Program Memory command.

# 7.0 HEX FILE USAGE

In the hex file there are two bytes per program word stored in the Intel<sup>®</sup> INHX32 hex format. Data is stored LSB first, MSB second. Because there are two bytes per word, the addresses in the hex file are 2x the address in program memory. (Example: Configuration Word 1 is stored at 8007h. In the hex file this will be referenced as 1000Eh-1000Fh).

### 7.1 Configuration Word

To allow portability of code, it is strongly recommended that the programmer is able to read the Configuration Words and user ID locations from the hex file. If the Configuration Words information was not present in the hex file, a simple warning message may be issued. Similarly, while saving a hex file, Configuration Words and user ID information should be included.

### 7.2 Device ID and Revision

If a device ID is present in the hex file at 1000Ch-1000Dh (8006h on the part), the programmer should verify the device ID (excluding the revision) against the value read from the part. On a mismatch condition the programmer should generate a warning message.

#### 7.3 Checksum Computation

The checksum is calculated by two different methods dependent on the setting of the  $\overline{CP}$  Configuration bit.

#### TABLE 7-1: CONFIGURATION WORD MASK VALUES

| Device      | Config. Word<br>1 Mask | Config. Word<br>2 Mask |

|-------------|------------------------|------------------------|

| PIC12LF1552 | 0EFBh                  | 2E03h                  |

#### 7.3.1 PROGRAM CODE PROTECTION DISABLED

With the program code protection disabled, the checksum is computed by reading the contents of the program memory locations and adding up the program memory data starting at address 0000h, up to the maximum user addressable location. Any Carry bit exceeding 16 bits are ignored. Additionally, the relevant bits of the Configuration Words are added to the checksum. All unimplemented Configuration bits are masked to '0'.

#### EXAMPLE 7-1: CHECKSUM COMPUTED WITH PROGRAM CODE PROTECTION DISABLED (CP = 1), PIC12LF1552, 00AAh AT FIRST AND LAST ADDRESS

| PIC12LF1 | 1552 Sum of Memory addresses 0000h-07FFh                                                                                                                                                                                                              | 7956h <sup>(1)</sup>                                | l |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---|--|--|--|

|          | Configuration Word 1                                                                                                                                                                                                                                  | 3FFFh <sup>(2)</sup>                                |   |  |  |  |

|          | Configuration Word 1 mask 0EFBh <sup>(3)</sup>                                                                                                                                                                                                        |                                                     |   |  |  |  |

|          | Configuration Word 2                                                                                                                                                                                                                                  | 3FFFh <sup>(4)</sup>                                |   |  |  |  |

|          | Configuration Word 2 mask                                                                                                                                                                                                                             | 2E03h <sup>(5)</sup>                                | l |  |  |  |

|          | Checksum = 7956h + (3FFFh and 0EFBh) + (3FF                                                                                                                                                                                                           | Fh and 2E03h) <sup>(6)</sup>                        | l |  |  |  |

|          | = 7956h + 0EFBh + 2E03h                                                                                                                                                                                                                               |                                                     | l |  |  |  |

|          | = B654h                                                                                                                                                                                                                                               |                                                     |   |  |  |  |

| Note 1:  | is 800h) subtracting 2h which yields 7FEh, then multiplying it by the blank memory value of 0x3FFF to get the sum of 1FF 7802h. Then, truncate to 16 bits the value of 7802h. Now add 00AAh (00AAh + 00AAh) to 7802h to get the final value of B654h. |                                                     |   |  |  |  |

| 2:       | 2: This value is obtained by making all bits of the Configuration Word 1 a '1', then converting it to hex, thus having a value of 3FFFh.                                                                                                              |                                                     |   |  |  |  |

| 3:       | <b>3:</b> This value is obtained by making all used bits of the Configuration Word 1 a '1', then converting it to hex, thus having a value of 0EFBh.                                                                                                  |                                                     |   |  |  |  |

| 4:       | This value is obtained by making all bits of the Configure having a value of 3FFFh.                                                                                                                                                                   | ation Word 2 a '1', then converting it to hex, thus |   |  |  |  |

| 5:       | 5                                                                                                                                                                                                                                                     |                                                     |   |  |  |  |

<sup>6:</sup> This value is obtained by ANDing the Configuration Word value with the Configuration Word Mask Value and adding it to the sum of memory addresses: (3FFFh and 0EFBh) + (3FFFh and 2E03h) + 7956h = B654h. Then, truncate to 16 bits, thus having a final value of B654h.

#### 7.3.2 PROGRAM CODE PROTECTION ENABLED

With the program code protection enabled, the checksum is computed in the following manner: The Least Significant nibble of each user ID is used to create a 16-bit value. The masked value of user ID location 8000h is the Most Significant nibble. This sum of user IDs is summed with the Configuration Words (all unimplemented Configuration bits are masked to '0').

| EXAMPLE 7-2: | CHECKSUM COMPUTED WITH PROGRAM CODE PROTECTION ENABLED |

|--------------|--------------------------------------------------------|

|              | (CP = 0), PIC12LF1552, 00AAh AT FIRST AND LAST ADDRESS |

| PIC12LF         | 1552 Configuration Word 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3F7Fh <sup>(1)</sup>                                                                                                                                                                    |  |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                 | Configuration Word 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | mask 0E7Bh <sup>(2)</sup>                                                                                                                                                               |  |  |  |  |  |

|                 | Configuration Word 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3FFFh <sup>(3)</sup>                                                                                                                                                                    |  |  |  |  |  |

|                 | Configuration Word 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | mask 2E03h <sup>(4)</sup>                                                                                                                                                               |  |  |  |  |  |

|                 | User ID (8000h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 000Eh <sup>(5)</sup>                                                                                                                                                                    |  |  |  |  |  |

| User ID (8001h) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0008h <sup>(5)</sup>                                                                                                                                                                    |  |  |  |  |  |

|                 | User ID (8002h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0005h <sup>(5)</sup>                                                                                                                                                                    |  |  |  |  |  |

|                 | User ID (8003h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0008h <sup>(5)</sup>                                                                                                                                                                    |  |  |  |  |  |

|                 | Sum of User IDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | = (000Eh and 000Fh) << 12 + (0008h and 000Fh) << 8 +                                                                                                                                    |  |  |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (0005h and 000Fh) << 4 + (0008h and 000Fh) <sup>(6)</sup>                                                                                                                               |  |  |  |  |  |

|                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | = E000h + 0800h + 0050h + 0008h                                                                                                                                                         |  |  |  |  |  |

|                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | = E858h                                                                                                                                                                                 |  |  |  |  |  |

|                 | Checksum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | = (3F7Fh and 0E7Bh) + (3FFFh and 2E03h) + Sum of User IDs <sup>(7)</sup>                                                                                                                |  |  |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | = 0E7Bh +2E03h + E858h                                                                                                                                                                  |  |  |  |  |  |

|                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | = 24D6h                                                                                                                                                                                 |  |  |  |  |  |

| Note 1:         | This value is obtained by making all bits of the Configuration Word 1 a '1', but the code-protect bit is '0' (thus, enabled), then converting it to hex, thus having a value of 3F7Fh.                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                         |  |  |  |  |  |

| 2:              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | his value is obtained by making all used bits of the Configuration Word 1 a '1', but the code-protect bit '0' (thus, enabled), then converting it to hex, thus having a value of 0E7Bh. |  |  |  |  |  |

| 3:              | This value is obtained by making all bits of the Configuration Word 2 a '1', then converting it to hex, thus having a value of 3FFFh.                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                         |  |  |  |  |  |

| 4:              | This value is obtained by making all used bits of the Configuration Word 2 a '1', then converting it to hex, thus having a value of 2E03h.                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                         |  |  |  |  |  |

| 5:              | These values are picked at random for this example; they could be any 16-bit value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                         |  |  |  |  |  |

| 6:              | In order to calculate the sum of user IDs, take the 16-bit value of the first user ID location (000Eh), AND the address to (000Fh), thus masking the MSB. This gives you the value 000Eh, then shift left 12 bits, giving you E000h. Do the same procedure for the 16-bit value of the second user ID location (0008h), except shift left 8 bits. Also, do the same for the third user ID location (0005h), except shift left 4 bits. For the fourth user ID location do not shift. Finally, add up all four user ID values to get the final sum of user IDs of E858h. |                                                                                                                                                                                         |  |  |  |  |  |

| 7:              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ng the Configuration Word value with the Configuration Word Mask Value<br>er IDs: (3F7Fh AND 0E7Bh) + (3FFFh AND 2E03h) + E858h = 24D6h.                                                |  |  |  |  |  |

## 8.0 ELECTRICAL SPECIFICATIONS

Refer to the device specific data sheet for absolute maximum ratings.

#### TABLE 8-1: AC/DC CHARACTERISTICS TIMING REQUIREMENTS FOR PROGRAM/VERIFY MODE

| AC/DC CHARACTERISTICS |                                                                                                    |              | Standard Operating Conditions<br>Production tested at 25°C |          |          |                                                                            |  |

|-----------------------|----------------------------------------------------------------------------------------------------|--------------|------------------------------------------------------------|----------|----------|----------------------------------------------------------------------------|--|

| Sym.                  | Characteristics                                                                                    | Min.         | Тур.                                                       | Max.     | Units    | Conditions/Comments                                                        |  |

|                       | Supply Voltag                                                                                      | es and Curre | nts                                                        |          |          |                                                                            |  |

| Vdd                   | VDD                                                                                                |              |                                                            |          |          | T                                                                          |  |

|                       | Read/Write and Row Erase operations                                                                | VDDMIN       | -                                                          | VDDMAX   | V        |                                                                            |  |

|                       | Bulk Erase operations                                                                              | 2.7          |                                                            | VDDMAX   | V        |                                                                            |  |

| Iddi                  | Current on VDD, Idle                                                                               | —            | —                                                          | 1.0      | mA       |                                                                            |  |

| IDDP                  | Current on VDD, Programming                                                                        | —            | —                                                          | 3.0      | mA       |                                                                            |  |

|                       | Vpp                                                                                                | -            |                                                            | -        |          |                                                                            |  |

| IPP                   | Current on MCLR/VPP                                                                                | —            | -                                                          | 600      | μA       |                                                                            |  |

| Vінн                  | High voltage on MCLR/VPP for<br>Program/Verify mode entry                                          | 8.0          | _                                                          | 9.0      | V        |                                                                            |  |

| TVHHR                 | MCLR rise time (VIL to VIHH) for<br>Program/Verify mode entry                                      | _            | _                                                          | 1.0      | μs       |                                                                            |  |

|                       | I/O pins                                                                                           |              |                                                            |          |          |                                                                            |  |

| VIH                   | (ICSPCLK, ICSPDAT, MCLR/VPP) input high level                                                      | 0.8 VDD      | _                                                          | _        | V        |                                                                            |  |

| VIL                   | (ICSPCLK, ICSPDAT, MCLR/VPP) input low level                                                       | _            | _                                                          | 0.2 VDD  | V        |                                                                            |  |

| Vон                   | ICSPDAT output high level                                                                          | VDD-0.7      | _                                                          | _        | v        | IOH = 3.5 mA, VDD = 5V<br>IOH = 3 mA, VDD = 3.3V<br>IOH = 2 mA, VDD = 1.8V |  |

| Vol                   | ICSPDAT output low level                                                                           | _            | _                                                          | 0.6      | V        | IOH = 8 mA, VDD = 5V<br>IOH = 6 mA, VDD = 3.3V<br>IOH = 3 mA, VDD = 1.8V   |  |

|                       | Programming M                                                                                      | ode Entry an | d Exit                                                     | -        |          |                                                                            |  |

| Tents                 | Programing mode entry setup time: ICSPCLK,<br>ICSPDAT setup time before VDD or MCLR↑               | 100          | —                                                          | —        | ns       |                                                                            |  |

| Tenth                 | Programing mode entry hold time: ICSPCLK,<br>ICSPDAT hold time after VDD or MCLR↑                  | 250          | —                                                          | —        | μs       |                                                                            |  |

|                       |                                                                                                    | gram/Verify  |                                                            |          |          |                                                                            |  |

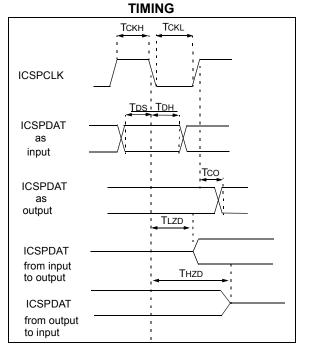

| TCKL                  | Clock Low Pulse Width                                                                              | 100          | —                                                          | —        | ns       |                                                                            |  |

| Тскн                  | Clock High Pulse Width                                                                             | 100          | -                                                          | —        | ns       |                                                                            |  |

| TDS                   | Data in setup time before clock↓                                                                   | 100          |                                                            | _        | ns       |                                                                            |  |

| Трн                   | Data in hold time after clock↓                                                                     | 100          | _                                                          |          | ns       |                                                                            |  |

| Тсо                   | Clock↑ to data out valid (during a<br>Read Data command)                                           | 0            | —                                                          | 80       | ns       |                                                                            |  |

| Tlzd                  | Clock↓ to data low-impedance (during a Read Data command)                                          | 0            | —                                                          | 80       | ns       |                                                                            |  |

| Thzd                  | Clock↓ to data high-impedance (during a Read Data command)                                         | 0            | —                                                          | 80       | ns       |                                                                            |  |

| TDLY                  | Data input not driven to next clock input (delay required between command/data or command/command) | 1.0          |                                                            | _        | μS       |                                                                            |  |

| Terab                 | Bulk Erase cycle time                                                                              |              |                                                            | 5        | ms       |                                                                            |  |

| Terar                 | Row Erase cycle time                                                                               | -            | -                                                          | 2.5      | ms       |                                                                            |  |

| TPINT                 | Internally timed programming operation time                                                        | _            |                                                            | 2.5<br>5 | ms<br>ms | Program memory<br>Configuration Words                                      |  |

| TPEXT                 | Externally timed programming pulse                                                                 | 1.0          | —                                                          | 2.1      | ms       | Note 1                                                                     |  |

| TDIS                  | Time delay from program to compare<br>(HV discharge time)                                          | 300          | _                                                          | _        | μs       |                                                                            |  |

| TEXIT                 | Time delay when exiting Program/Verify mode                                                        | 1            | -                                                          | _        | μS       |                                                                            |  |

Note 1: Externally timed writes are not supported for Configuration and Calibration bits.

### 8.1 AC Timing Diagrams

FIGURE 8-2: PROGRAMMING MODE ENTRY – VPP FIRST

FIGURE 8-3: PROGRAMMING MODE EXIT – VPP LAST

#### FIGURE 8-4:

#### PROGRAMMING MODE EXIT – VDD LAST

FIGURE 8-5:

© 2012 Microchip Technology Inc.