Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 8-Bit CMOS Microcontrollers with A/D Converter and Capture/Compare/PWM

#### **Devices included in this Data Sheet:**

PIC16C712

PIC16C716

#### **Microcontroller Core Features:**

- · High-performance RISC CPU

- · Only 35 single-word instructions to learn

- All single-cycle instructions except for program branches which are two cycle

- Operating speed: DC 20 MHz clock input DC – 200 ns instruction cycle

| Device    | Program<br>Memory | Data Memory |  |  |

|-----------|-------------------|-------------|--|--|

| PIC16C712 | 1K                | 128         |  |  |

| PIC16C716 | 2K                | 128         |  |  |

- Interrupt capability (up to 7 internal/external interrupt sources)

- · Eight-level deep hardware stack

- · Direct, Indirect and Relative Addressing modes

- · Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- Brown-out detection circuitry for Brown-out Reset (BOR)

- Programmable code-protection

- · Power-saving Sleep mode

- Selectable oscillator options

- Low-power, high-speed CMOS EPROM technology

- · Fully static design

- In-Circuit Serial Programming™ (ICSP™)

- · Wide operating voltage range: 2.5V to 5.5V

- · High Sink/Source Current 25/25 mA

- Commercial, Industrial and Extended temperature ranges

- Low-power consumption:

- < 2 mA @ 5V, 4 MHz

- 22.5 μA, typical @ 3V, 32 kHz

- < 1 μA, typical standby current

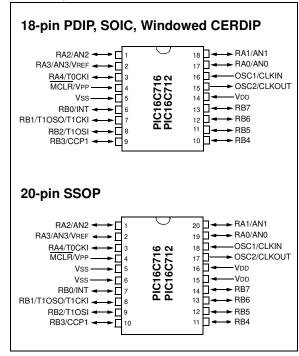

#### Pin Diagrams

#### **Peripheral Features:**

- Timer0: 8-bit timer/counter with 8-bit prescaler

- Timer1: 16-bit timer/counter with prescaler can be incremented during Sleep via external crystal/clock

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- · Capture, Compare, PWM module

- Capture is 16-bit, max. resolution is 12.5 ns, Compare is 16-bit, max. resolution is 200 ns, PWM maximum resolution is 10-bit

- · 8-bit multi-channel Analog-to-Digital converter

| Key Features<br>PIC <sup>®</sup> Mid-Range Reference Manual (DS33023) | PIC16C712            | PIC16C716            |

|-----------------------------------------------------------------------|----------------------|----------------------|

| Operating Frequency                                                   | DC – 20 MHz          | DC – 20 MHz          |

| Resets (and Delays)                                                   | POR, BOR (PWRT, OST) | POR, BOR (PWRT, OST) |

| Program Memory (14-bit words)                                         | 1K                   | 2K                   |

| Data Memory (bytes)                                                   | 128                  | 128                  |

| Interrupts                                                            | 7                    | 7                    |

| I/O Ports                                                             | Ports A,B            | Ports A,B            |

| Timers                                                                | 3                    | 3                    |

| Capture/Compare/PWM modules                                           | 1                    | 1                    |

| 8-bit Analog-to-Digital Module                                        | 4 input channels     | 4 input channels     |

#### PIC16C7XX FAMILY OF DEVICES

|             |                                                                               | PIC16C710                           | PIC16C71            | PIC16C711                           | PIC16C712                           | PIC16C715                           | PIC16C716                           | PIC16C72A                  | PIC16C73B                      |

|-------------|-------------------------------------------------------------------------------|-------------------------------------|---------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|----------------------------|--------------------------------|

| Clock       | Maximum Frequency of Operation (MHz)                                          | 20                                  | 20                  | 20                                  | 20                                  | 20                                  | 20                                  | 20                         | 20                             |

| Memory      | EPROM Program<br>Memory<br>(x14 words)                                        | 512                                 | 1K                  | 1K                                  | 1K                                  | 2K                                  | 2K                                  | 2K                         | 4K                             |

|             | Data Memory (bytes)                                                           | 36                                  | 36                  | 68                                  | 128                                 | 128                                 | 128                                 | 128                        | 192                            |

|             | Timer Module(s)                                                               | TMR0                                | TMR0                | TMR0                                | TMR0<br>TMR1<br>TMR2                | TMR0                                | TMR0<br>TMR1<br>TMR2                | TMR0<br>TMR1<br>TMR2       | TMR0<br>TMR1<br>TMR2           |

| Peripherals | Capture/Compare/<br>PWM Module(s)                                             | _                                   | _                   | _                                   | 1                                   | _                                   | 1                                   | 1                          | 2                              |

|             | Serial Port(s)<br>(SPI <sup>TM</sup> /I <sup>2</sup> C <sup>TM</sup> , USART) | _                                   | _                   | _                                   | _                                   | _                                   | _                                   | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C,<br>USART |

|             | A/D Converter (8-bit)<br>Channels                                             | 4                                   | 4                   | 4                                   | 4                                   | 4                                   | 4                                   | 5                          | 5                              |

|             | Interrupt Sources                                                             | 4                                   | 4                   | 4                                   | 7                                   | 4                                   | 7                                   | 8                          | 11                             |

|             | I/O Pins                                                                      | 13                                  | 13                  | 13                                  | 13                                  | 13                                  | 13                                  | 22                         | 22                             |

|             | Voltage Range (Volts)                                                         | 2.5-6.0                             | 3.0-6.0             | 2.5-6.0                             | 2.5-5.5                             | 2.5-5.5                             | 2.5-5.5                             | 2.5-5.5                    | 2.5-5.5                        |

| Features    | In-Circuit Serial<br>Programming™                                             | Yes                                 | Yes                 | Yes                                 | Yes                                 | Yes                                 | Yes                                 | Yes                        | Yes                            |

|             | Brown-out Reset                                                               | Yes                                 | _                   | Yes                                 | Yes                                 | Yes                                 | Yes                                 | Yes                        | Yes                            |

|             | Packages                                                                      | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC           |

#### **Table of Contents**

| 1.0   | Device Overview                          | 5     |

|-------|------------------------------------------|-------|

| 2.0   | Device Overview                          | 9     |

| 3.0   | I/O Ports                                | 21    |

| 4.0   | Timer0 Module                            | 29    |

| 5.0   | Timer1 Module                            | 31    |

| 6.0   | Timer2 Module                            |       |

| 7.0   | Capture/Compare/PWM (CCP) Module(s)      | 39    |

| 8.0   | Analog-to-Digital Converter (A/D) Module |       |

| 9.0   | Special Features of the CPU              |       |

| 10.0  | Instruction Set Summary                  | 67    |

| 11.0  | Development Support                      |       |

| 12.0  | Electrical Characteristics               | 73    |

| 13.0  | Packaging Information                    | 89    |

| Revis | ion History                              | 95    |

|       | ersion Considerations                    |       |

| Migra | tion from Base-line to Mid-Range Devices | 95    |

| Index |                                          | 97    |

| On-L  | ne Support                               | . 101 |

|       | er Response                              |       |

| PIC1  | 6C712/716 Product Identification System  | . 103 |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

**NOTES:**

#### 1.0 DEVICE OVERVIEW

This document contains device-specific information. Additional information may be found in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip web site. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

There are two devices (PIC16C712, PIC16C716) covered by this data sheet.

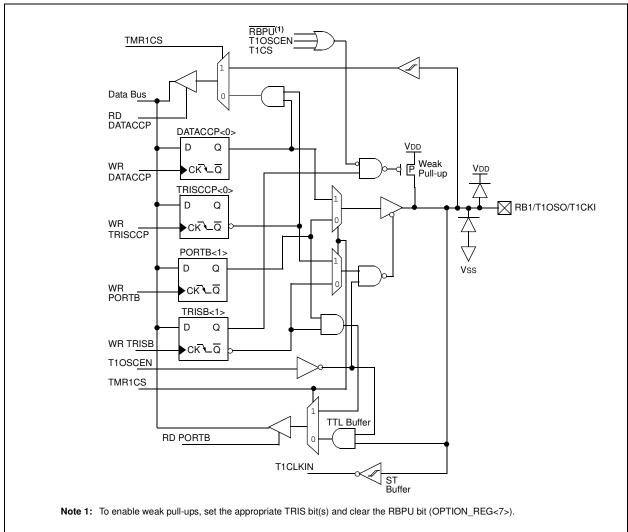

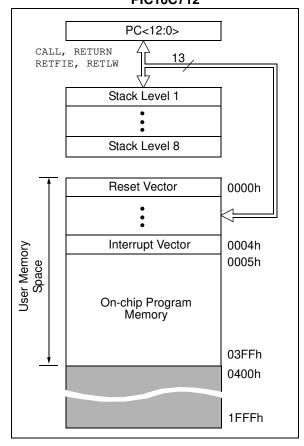

Figure 1-1 is the block diagram for both devices. The pinouts are listed in Table 1-1.

FIGURE 1-1: PIC16C712/716 BLOCK DIAGRAM

TABLE 1-1: PIC16C712/716 PINOUT DESCRIPTION

| Pin                     | PIC16C    | 712/716 | Pin      | Buffer        |                                                                                                                        |

|-------------------------|-----------|---------|----------|---------------|------------------------------------------------------------------------------------------------------------------------|

| Name                    | DIP, SOIC | SSOP    | Туре     | Туре          | Description                                                                                                            |

| MCLR/VPP<br>MCLR<br>VPP | 4         | 4       | l<br>P   | ST            | Master clear (Reset) input. This pin is an active low Reset to the device. Programming voltage input                   |

| OSC1/CLKIN              | 16        | 18      | '        |               | 1 Togramming voltage input                                                                                             |

| OSC1                    | 10        | 10      | I        | ST            | Oscillator crystal input or external clock source input. ST buffer when config-                                        |

| CLKIN                   |           |         | I        | CMOS          | ured in RC mode. CMOS otherwise. External clock source input.                                                          |

| OSC2/CLKOUT<br>OSC2     | 15        | 17      | 0        | _             | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator                                      |

| CLKOUT                  |           |         | 0        | _             | mode. In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

|                         |           |         |          |               | PORTA is a bidirectional I/O port.                                                                                     |

| RA0/AN0<br>RA0<br>AN0   | 17        | 19      | I/O<br>I | TTL<br>Analog | Digital I/O<br>Analog input 0                                                                                          |

| RA1/AN1                 | 18        | 20      |          |               | D. 1. 1.1.0                                                                                                            |

| RA1<br>AN1              |           |         | I/O      | TTL<br>Analog | Digital I/O Analog input 1                                                                                             |

| RA2/AN2<br>RA2          | 1         | 1       | I/O      | TTL           |                                                                                                                        |

| AN2                     |           |         | 1/0      | Analog        | Digital I/O<br>Analog input 2                                                                                          |

| RA3/AN3/VREF            | 2         | 2       |          |               |                                                                                                                        |

| RA3<br>AN3              |           |         | I/O<br>I | TTL<br>Analog | Digital I/O<br>Analog input 3                                                                                          |

| VREF                    |           |         | i        | Analog        | A/D Reference Voltage input.                                                                                           |

| RA4/T0CKI               | 3         | 3       |          |               |                                                                                                                        |

| RA4                     |           |         | I/O      | ST/OD         | Digital I/O. Open drain when configured as output.                                                                     |

| T0CKI                   |           |         | 1        | ST            | Timer0 external clock input                                                                                            |

ST = Schmitt Trigger input with CMOS levels

OD = Open drain output

SM = SMBus compatible input. An external resistor is required if this pin is used as an output

$I = input & O = output \\ P = Power & L = LCD Driver$

TABLE 1-1: PIC16C712/716 PINOUT DESCRIPTION (CONTINUED)

| Pin                       | PIC16C    | 712/716 | Pin        | Buffer    |                                                                                                               |

|---------------------------|-----------|---------|------------|-----------|---------------------------------------------------------------------------------------------------------------|

| Name                      | DIP, SOIC | SSOP    | Туре       | Туре      | Description                                                                                                   |

|                           |           |         |            |           | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs. |

| RB0/INT<br>RB0<br>INT     | 6         | 7       | I/O<br>I   | TTL<br>ST | Digital I/O<br>External Interrupt                                                                             |

| RB1/T1OSO/T1CKI<br>RB1    | 7         | 8       |            |           |                                                                                                               |

| T1OSO                     |           |         | I/O<br>O   | TTL<br>—  | Digital I/O<br>Timer1 oscillator output. Connects to                                                          |

| T1CKI                     |           |         | I          | ST        | crystal in oscillator mode.<br>Timer1 external clock input.                                                   |

| RB2/T1OSI<br>RB2<br>T1OSI | 8         | 9       | I/O<br>I   | TTL<br>—  | Digital I/O Timer1 oscillator input. Connects to crystal in oscillator mode.                                  |

| RB3/CCP1<br>RB3<br>CCP1   | 9         | 10      | I/O<br>I/O | TTL<br>ST | Digital I/O Capture1 input, Compare1 output, PWM1 output.                                                     |

| RB4                       | 10        | 12      | I/O        | TTL       | Digital I/O<br>Interrupt on change pin.                                                                       |

| RB5                       | 11        | 12      | I/O        | TTL       | Digital I/O<br>Interrupt on change pin.                                                                       |

| RB6                       | 12        | 13      | I/O        | TTL       | Digital I/O<br>Interrupt on change pin.                                                                       |

|                           |           |         | 1          | ST        | ICSP programming clock.                                                                                       |

| RB7                       | 13        | 14      | I/O<br>I/O | TTL<br>ST | Digital I/O Interrupt on change pin. ICSP programming data.                                                   |

| Vss                       | 5         | 5, 6    | P          | _         | Ground reference for logic and I/O pins.                                                                      |

| VDD                       | 14        | 15, 16  | Р          | _         | Positive supply for logic and I/O pins.                                                                       |

ST = Schmitt Trigger input with CMOS levels

OD = Open drain output

SM = SMBus compatible input. An external resistor is required if this pin is used as an output

NPU = N-channel pull-up

PU = Weak internal pull-up

No-P diode = No P-diode to VDD AN = Analog input or output

**NOTES:**

#### 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these PIC<sup>®</sup> microcontroller devices. Each block (Program Memory and Data Memory) has its own bus so that concurrent access can occur.

Additional information on device memory may be found in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

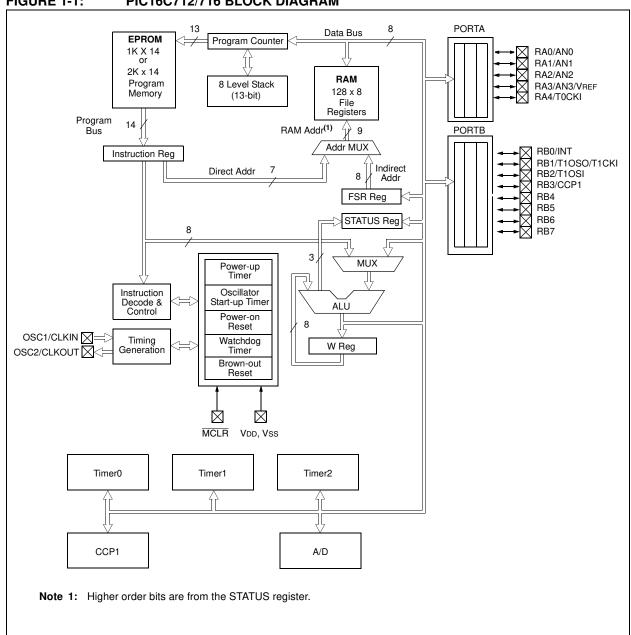

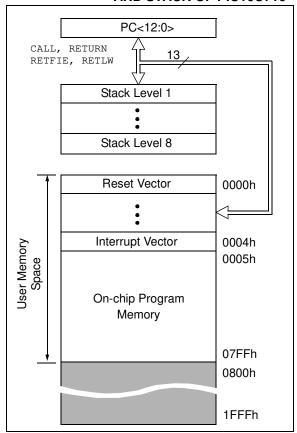

#### 2.1 Program Memory Organization

The PIC16C712/716 has a 13-bit Program Counter (PC) capable of addressing an 8K x 14 program memory space. PIC16C712 has 1K x 14 words of program memory and PIC16C716 has 2K x 14 words of program memory. Accessing a location above the physically implemented address will cause a wraparound.

The Reset vector is at 0000h and the interrupt vector is at 0004h.

FIGURE 2-1: PROGRAM MEMORY MAP AND STACK OF THE PIC16C712

FIGURE 2-2: PROGRAM MEMORY MAP

AND STACK OF PIC16C716

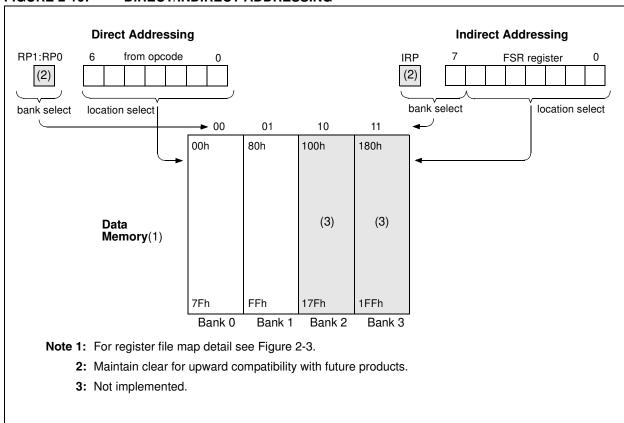

#### 2.2 **Data Memory Organization**

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

RP1<sup>(1)</sup> RP0

(STATUS<6:5>)

- $= 00 \rightarrow Bank 0$

- $= 01 \rightarrow Bank 1$

- = 10 → Bank 2 (not implemented)

- = 11 → Bank 3 (not implemented)

Note 1: Maintain this bit clear to ensure upward compatibility with future products.

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some "high use" Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

#### GENERAL PURPOSE REGISTER 2.2.1 **FILE**

The register file can be accessed either directly, or indirectly through the File Select Register FSR (see Section 2.5 "Indirect Addressing, INDF and FSR Registers").

FIGURE 2-3: **REGISTER FILE MAP**

| JRE 2-3:     | RE                   | GISTER FIL          | EWAP    |  |  |  |  |  |  |

|--------------|----------------------|---------------------|---------|--|--|--|--|--|--|

| File         |                      |                     | File    |  |  |  |  |  |  |

| Address      |                      |                     | Address |  |  |  |  |  |  |

| 00h          | INDF <sup>(1)</sup>  | INDF <sup>(1)</sup> | 80h     |  |  |  |  |  |  |

| 01h          | TMR0                 | OPTION_REG          | 81h     |  |  |  |  |  |  |

| 02h          | PCL                  | PCL                 | 82h     |  |  |  |  |  |  |

| 03h          | STATUS               | STATUS              | 83h     |  |  |  |  |  |  |

| 04h          | FSR                  | FSR                 | 84h     |  |  |  |  |  |  |

| 05h          | PORTA                | TRISA               | 85h     |  |  |  |  |  |  |

| 06h          | PORTB                | TRISB               | 86h     |  |  |  |  |  |  |

| 07h          | DATACCP              | TRISCCP             | 87h     |  |  |  |  |  |  |

| 08h          |                      |                     | 88h     |  |  |  |  |  |  |

| 09h          |                      |                     | 89h     |  |  |  |  |  |  |

| 0Ah          | PCLATH               | PCLATH              | 8Ah     |  |  |  |  |  |  |

| 0Bh          | INTCON               | INTCON              | 8Bh     |  |  |  |  |  |  |

| 0Ch          | PIR1                 | PIE1                | 8Ch     |  |  |  |  |  |  |

| 0Dh          |                      |                     | 8Dh     |  |  |  |  |  |  |

| 0Eh          | TMR1L                | PCON                | 8Eh     |  |  |  |  |  |  |

| 0Fh          | TMR1H                |                     | 8Fh     |  |  |  |  |  |  |

| 10h          | T1CON                |                     | 90h     |  |  |  |  |  |  |

| 11h          | TMR2                 |                     | 91h     |  |  |  |  |  |  |

| 12h          | T2CON                | PR2                 | 92h     |  |  |  |  |  |  |

| 13h          |                      |                     | 93h     |  |  |  |  |  |  |

| 14h          |                      |                     | 94h     |  |  |  |  |  |  |

| 15h          | CCPR1L               |                     | 95h     |  |  |  |  |  |  |

| 16h          | CCPR1H               |                     | 96h     |  |  |  |  |  |  |

| 17h          | CCP1CON              |                     | 97h     |  |  |  |  |  |  |

| 18h          |                      |                     | 98h     |  |  |  |  |  |  |

| 19h          |                      |                     | 99h     |  |  |  |  |  |  |

| 1Ah          |                      |                     | 9Ah     |  |  |  |  |  |  |

| 1Bh          |                      |                     | 9Bh     |  |  |  |  |  |  |

| 1Ch          |                      |                     | 9Ch     |  |  |  |  |  |  |

| 1Dh          |                      |                     | 9Dh     |  |  |  |  |  |  |

| 1Eh          | ADRES                |                     | 9Eh     |  |  |  |  |  |  |

| 1Fh          | ADCON0               | ADCON1              | 9Fh     |  |  |  |  |  |  |

| 20h          | 71000110             | General             | A0h     |  |  |  |  |  |  |

| 2011         |                      | Purpose             | 71011   |  |  |  |  |  |  |

|              | General              | Registers           | BFh     |  |  |  |  |  |  |

|              | Purpose<br>Registers | 32 Bytes            |         |  |  |  |  |  |  |

|              | 96 Bytes             |                     | C0h     |  |  |  |  |  |  |

| ]            | •                    |                     |         |  |  |  |  |  |  |

| 7Fh          |                      |                     | FFh     |  |  |  |  |  |  |

|              | Bank 0               | Bank 1              |         |  |  |  |  |  |  |

|              |                      | ata memory loc      | ations, |  |  |  |  |  |  |

| read as '0'. |                      |                     |         |  |  |  |  |  |  |

| te 1: Not    | a physical re        | aictor              |         |  |  |  |  |  |  |

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is give in Table 2-1. The Special Function Registers can be classified into two sets; core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in that peripheral feature section.

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY

| Oth   TMR0   Timer0 Module's Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Addr    | Name                    | Bit 7              | Bit 6              | Bit 5         | Bit 4           | Bit 3         | Bit 2           | Bit 1         | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets (4) |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------|--------------------|--------------------|---------------|-----------------|---------------|-----------------|---------------|---------|--------------------------|-------------------------------------|

| Oth   TMR0   Timer0 Module's Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Bank 0  |                         |                    |                    |               |                 |               |                 |               |         |                          |                                     |

| O2h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 00h     | INDF <sup>(1)</sup>     | Addressing         | this location      | uses conten   | ts of FSR to ac | ddress data r | nemory (not     | a physical re | gister) | 0000 0000                | 0000 0000                           |

| O3h   STATUS <sup>(1)</sup>   IRP <sup>(4)</sup>   RPI <sup>(4)</sup>   RPO   TO   PD   Z   DC   C   rr01 1xxx   rr00 q of points   C   PORTA   Indirect Data Memory Address Pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 01h     | TMR0                    | Timer0 Mod         | lule's Registe     |               | xxxx xxxx       | uuuu uuuu     |                 |               |         |                          |                                     |

| 04h   FSR <sup>(1)</sup>   Indirect Data Memory Address Pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 02h     | PCL <sup>(1)</sup>      | Program Co         | ounter's (PC)      |               | 0000 0000       | 0000 0000     |                 |               |         |                          |                                     |

| OSh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 03h     | STATUS <sup>(1)</sup>   | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup> | RP0           | TO              | PD            | Z               | DC            | С       | rr01 1xxx                | rr0q quuu                           |

| 06h         PORTB(5,6)         PORTB Data Latch when written: PORTB pins when read         xxxx xxxx xxxx xxxx xxxx xxxx xxxx xx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 04h     | FSR <sup>(1)</sup>      | Indirect Data      | a Memory Ad        | ddress Pointe | er              | •             | •               |               |         | xxxx xxxx                | uuuu uuuu                           |

| 07h         DATACCP         _(7)         _(7)         _(7)         _(7)         _(7)         _(7)         DCCP         _(7)         DT1CK         xxxxx xxxx         xxxxx         xxxx                                                                                                 | 05h     | PORTA <sup>(5,6)</sup>  | _                  | _                  | (7)           | PORTA Data      | Latch when v  | written: POR    | TA pins wher  | n read  | xx xxxx                  | xu uuuu                             |

| 08h-09h         —         Unimplemented         —         Write Buffer for the upper 5 bits of the Program Counter         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —                                                                                                                                                                                                        | 06h     | PORTB <sup>(5,6)</sup>  | PORTB Dat          | a Latch whe        | n written: PC | RTB pins whe    | n read        |                 |               |         | xxxx xxxx                | uuuu uuuu                           |

| OAh         PCLATH <sup>(1,2)</sup> —         —         Write Buffer for the upper 5 bits of the Program Counter        0 0000        0 0000           0Bh         INTCON <sup>(1)</sup> GIE         PEIE         TOIE         INTE         RBIE         TOIF         INTF         RBIF         0000 0000 0000 0000 0000 0000 0000 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 07h     | DATACCP                 | (7)                | (7)                | (7)           | (7)             | (7)           | DCCP            | (7)           | DT1CK   | xxxx xxxx                | xxxx xuxu                           |

| OBh         INTCON(1)         GIE         PEIE         TOIE         INTE         RBIE         TOIF         INTF         RBIF         0000 000x 0000 000x 0000 0000 0000 000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 08h-09h | _                       | Unimpleme          | nted               |               |                 |               |                 |               |         | -                        | -                                   |

| OCh         PIR1         —         ADIF         —         —         CCP1IF         TMR2IF         TMR1IF         —         —         COP1IF           0Dh         —         Unimplemented         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         — <td>0Ah</td> <td>PCLATH<sup>(1,2)</sup></td> <td>_</td> <td>_</td> <td>_</td> <td>Write Buffer fo</td> <td>or the upper</td> <td>5 bits of the F</td> <td>Program Cou</td> <td>ınter</td> <td>0 0000</td> <td>0 0000</td> | 0Ah     | PCLATH <sup>(1,2)</sup> | _                  | _                  | _             | Write Buffer fo | or the upper  | 5 bits of the F | Program Cou   | ınter   | 0 0000                   | 0 0000                              |

| ODh         —         Unimplemented         —         —           0Eh         TMR1L         Holding Register for the Least Significant Byte of the 16-bit TMR1 Register         xxxx xxxx uuuu u           0Fh         TMR1H         Holding Register for the Most Significant Byte of the 16-bit TMR1 Register         xxxx xxxx uuuu u           10h         T1CON         —         —         T1CKPS1         T1CKPS0         T1OSCEN         T1SYNC         TMR1CS         TMR1ON         —00 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0Bh     | INTCON <sup>(1)</sup>   | GIE                | PEIE               | T0IE          | INTE            | RBIE          | T0IF            | INTF          | RBIF    | 0000 000x                | 0000 000u                           |

| 0Eh         TMR1L         Holding Register for the Least Significant Byte of the 16-bit TMR1 Register         xxxx xxxx uuuu u           0Fh         TMR1H         Holding Register for the Most Significant Byte of the 16-bit TMR1 Register         xxxx xxxx uuuu u           10h         T1CON         —         T1CKPS1         T1CKPS0         T1OSCEN         T1SYNC         TMR1CS         TMR1ON         —00 0000         —0000         —0000         —0000         —0000         —0000         —0000         0000         —0000         0000         —0000         0000         —0000         0000         —0000         0000         —0000         0000         —0000         0000         —0000         0000         —0000         0000         —0000         0000         —0000         0000         —0000         0000         —0000         0000         —0000         0000         —0000         0000         —0000         0000         —0000         0000         —0000         0000         —0000         0000         —0000         —0000         —0000         —0000         —0000         —0000         —0000         —0000         —0000         —0000         —0000         —0000         —0000         —0000         —0000         —0000         —0000         —0000         —0000         —                         | 0Ch     | PIR1                    | _                  | ADIF               | _             | _               | _             | CCP1IF          | TMR2IF        | TMR1IF  | -0 0000                  | -0 0000                             |

| 0Fh         TMR1H         Holding Register for the Most Significant Byte of the 16-bit TMR1 Register         xxxx xxxx uuuu u           10h         T1CON         —         T1CKPS1         T1CKPS0         T1OSCEN         T1SYNC         TMR1CS         TMR1ON         -00         0000         -uu u           11h         TMR2         Timer2 Module's Register         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         00                                                                      | 0Dh     | ı                       | Unimplemen         | nted               |               |                 |               |                 |               |         | -                        | _                                   |

| 10h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0Eh     | TMR1L                   | Holding Reg        | gister for the     | Least Signifi | cant Byte of th | e 16-bit TMF  | R1 Register     |               |         | xxxx xxxx                | uuuu uuuu                           |

| 11h         TMR2         Timer2 Module's Register         0000 0000 0000 0000 0000 0000 0000 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0Fh     | TMR1H                   | Holding Reg        | gister for the     | Most Signific | ant Byte of the | e 16-bit TMR  | 1 Register      |               |         | xxxx xxxx                | uuuu uuuu                           |

| 12h         T2CON         —         TOUTPS3         TOUTPS2         TOUTPS1         TOUTPS0         TMR2ON         T2CKPS1         T2CKPS0         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000         -000         0000                                                                                          | 10h     | T1CON                   |                    | _                  | T1CKPS1       | T1CKPS0         | T10SCEN       | T1SYNC          | TMR1CS        | TMR10N  | 00 0000                  | uu uuuu                             |

| 13h-14h         15h         CCPR1L         Capture/Compare/PWM Register1 (LSB)         xxxxx xxxxx         uuuu u           16h         CCPR1H         Capture/Compare/PWM Register1 (MSB)         xxxx xxxx         uuuu u           17h         CCP1CON         —         DC1B1         DC1B0         CCP1M3         CCP1M2         CCP1M1         CCP1M0        00         0000        00         18h-1Dh         —         Unimplemented         —         —         —         —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11h     | TMR2                    | Timer2 Mod         | lule's Registe     | er            |                 |               |                 |               |         | 0000 0000                | 0000 0000                           |

| 15h         CCPR1L         Capture/Compare/PWM Register1 (LSB)         xxxx xxxx uuuu t           16h         CCPR1H         Capture/Compare/PWM Register1 (MSB)         xxxx xxxx uuuu t           17h         CCP1CON         —         DC1B1         DC1B0         CCP1M3         CCP1M2         CCP1M1         CCP1M0        00 0000        00 000           18h-1Dh         —         Unimplemented         —         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12h     | T2CON                   | _                  | TOUTPS3            | TOUTPS2       | TOUTPS1         | TOUTPS0       | TMR2ON          | T2CKPS1       | T2CKPS0 | -000 0000                | -000 0000                           |

| 16h         CCPR1H         Capture/Compare/PWM Register1 (MSB)         xxxx xxxx         uuuu 1           17h         CCP1CON         —         DC1B1         DC1B0         CCP1M3         CCP1M2         CCP1M1         CCP1M0        00         0000        00         0         0         18h-1Dh         —         Unimplemented         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —                                                                                                                                                                                              | 13h-14h |                         |                    |                    |               |                 |               |                 |               |         |                          |                                     |

| 17h         CCP1CON         —         DC1B1         DC1B0         CCP1M3         CCP1M2         CCP1M1         CCP1M0        00 0000        00 0           18h-1Dh         —         Unimplemented         —         —         —         —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15h     | CCPR1L                  | Capture/Co         | mpare/PWM          | Register1 (L  | .SB)            |               |                 |               |         | xxxx xxxx                | uuuu uuuu                           |

| 18h-1Dh — Unimplemented — —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16h     | CCPR1H                  | Capture/Co         | mpare/PWM          | Register1 (N  | MSB)            |               |                 |               |         | xxxx xxxx                | uuuu uuuu                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17h     | CCP1CON                 | _                  | _                  | DC1B1         | DC1B0           | CCP1M3        | CCP1M2          | CCP1M1        | CCP1M0  | 00 0000                  | 00 0000                             |

| 1Eh ADRES A/D Result Register xxxx xxxx uuuu u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18h-1Dh | _                       | Unimplemen         | nted               |               | -               | -             |                 |               |         |                          |                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1Eh     | ADRES                   | A/D Result I       | Register           |               | xxxx xxxx       | uuuu uuuu     |                 |               |         |                          |                                     |

| 1Fh ADCON0 ADCS1 ADCS0 CHS2 CHS1 CHS0 GO/DONE — ADON 0000 00-0 0000 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1Fh     | ADCON0                  | ADCS1              | ADCS0              | CHS2          | CHS1            | CHS0          | GO/DONE         | _             | ADON    | 0000 00-0                | 0000 00-0                           |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, — = unimplemented, read as '0', Shaded locations are unimplemented, read as '0'.

- Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8> whose contents are transferred to the upper byte of the program counter.

- 3: Other (non Power-up) Resets include: external Reset through MCLR and the Watchdog Timer Reset.

- 4: The IRP and RP1 bits are reserved. Always maintain these bits clear.

- 5: On any device Reset, these pins are configured as inputs.

- 6: This is the value that will be in the port output latch.

- 7: Reserved bits; Do Not Use.

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr    | Name                    | Bit 7                                   | Bit 6                         | Bit 5        | Bit 4           | Bit 3         | Bit 2           | Bit 1         | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets (4) |

|---------|-------------------------|-----------------------------------------|-------------------------------|--------------|-----------------|---------------|-----------------|---------------|---------|--------------------------|-------------------------------------|

| Bank 1  |                         |                                         |                               |              |                 |               |                 |               |         |                          |                                     |

| 80h     | INDF <sup>(1)</sup>     | Addressing                              | this location                 | uses conten  | ts of FSR to ac | ddress data r | nemory (not     | a physical re | gister) | 0000 0000                | 0000 0000                           |

| 81h     | OPTION_<br>REG          | RBPU                                    | INTEDG                        | T0CS         | T0SE            | PSA           | PS2             | PS1           | PS0     | 1111 1111                | 1111 1111                           |

| 82h     | PCL <sup>(1)</sup>      | Program Co                              | ounter's (PC)                 | Least Signif | ficant Byte     |               |                 |               |         | 0000 0000                | 0000 0000                           |

| 83h     | STATUS <sup>(1)</sup>   | IRP <sup>(4)</sup>                      | RP1 <sup>(4)</sup>            | RP0          | TO              | PD            | Z               | DC            | С       | rr01 1xxx                | rr0q quuu                           |

| 84h     | FSR <sup>(1)</sup>      | Indirect Data                           | a Memory Ad                   |              | xxxx xxxx       | uuuu uuuu     |                 |               |         |                          |                                     |

| 85h     | TRISA                   | — — — — — PORTA Data Direction Register |                               |              |                 |               |                 |               |         |                          | x1 1111                             |

| 86h     | TRISB                   | PORTB Dat                               | PORTB Data Direction Register |              |                 |               |                 |               |         |                          |                                     |

| 87h     | TRISCCP                 | (7)                                     | _(7)                          |              |                 |               |                 |               |         |                          | xxxx x1x1                           |

| 88h-89h | _                       | Unimpleme                               | nted                          |              |                 |               |                 |               |         | -                        | -                                   |

| 8Ah     | PCLATH <sup>(1,2)</sup> | _                                       | _                             | _            | Write Buffer fo | or the upper  | 5 bits of the F | Program Cou   | inter   | 0 0000                   | 0 0000                              |

| 8Bh     | INTCON <sup>(1)</sup>   | GIE                                     | PEIE                          | T0IE         | INTE            | RBIE          | T0IF            | INTF          | RBIF    | 0000 000x                | 0000 000u                           |

| 8Ch     | PIE1                    | _                                       | ADIE                          | _            | _               | _             | CCP1IE          | TMR2IE        | TMR1IE  | -0000                    | -0000                               |

| 8Dh     | _                       | Unimpleme                               | nted                          |              |                 |               |                 |               |         | -                        | -                                   |

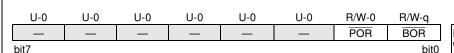

| 8Eh     | PCON                    | _                                       | _                             | _            | _               | _             | _               | POR           | BOR     | qq                       | uu                                  |

| 8Fh-91h | _                       | Unimpleme                               | nted                          |              | _               | -             |                 |               |         |                          |                                     |

| 92h     | PR2                     | Timer2 Peri                             |                               | 1111 1111    | 1111 1111       |               |                 |               |         |                          |                                     |

| 93h-9Eh | _                       | Unimpleme                               | nted                          |              |                 |               |                 |               |         | -                        | -                                   |

| 9Fh     | ADCON1                  | _                                       | _                             | _            | _               | _             | PCFG2           | PCFG1         | PCFG0   | 000                      | 000                                 |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, — = unimplemented, read as '0', Shaded locations are unimplemented, read as '0'.

- Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8> whose contents are transferred to the upper byte of the program counter.

- 3: Other (non Power-up) Resets include: external Reset through MCLR and the Watchdog Timer Reset.

- 4: The IRP and RP1 bits are reserved. Always maintain these bits clear.

- 5: On any device Reset, these pins are configured as inputs.

- 6: This is the value that will be in the port output latch.

- 7: Reserved bits; Do Not Use.

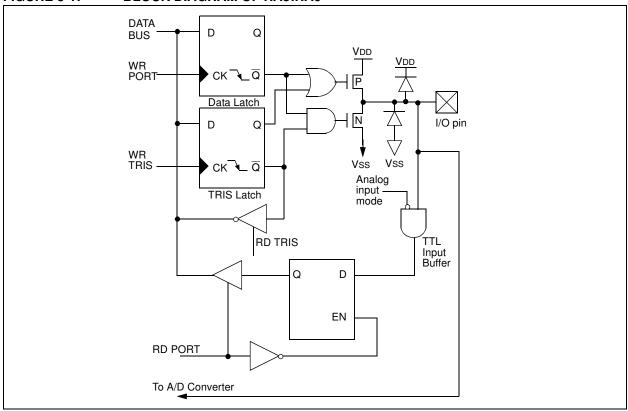

#### 2.2.2.1 Status Register

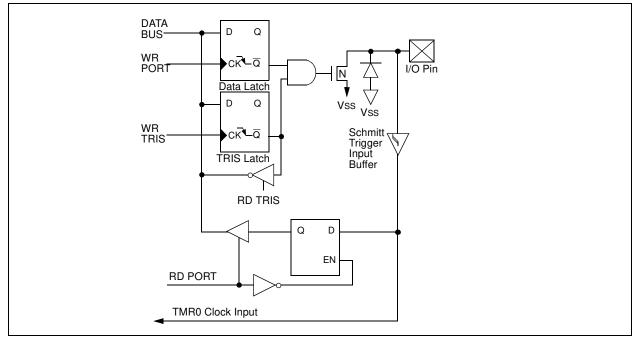

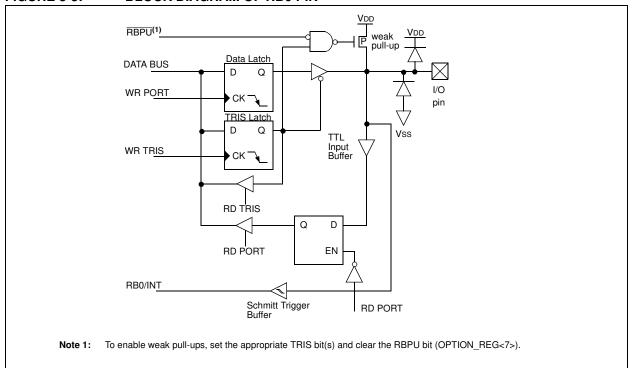

The STATUS register, shown in Figure 2-4, contains the arithmetic status of the ALU, the Reset status and the bank select bits for data memory.