Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## Full-Featured 28/40/44-Pin Microcontrollers

### **Description**

PIC16(L)F18854 microcontrollers feature Analog, Core Independent Peripherals and Communication Peripherals, combined with eXtreme Low-Power (XLP) technology for a wide range of general purpose and low-power applications. The family will feature the CRC/SCAN, Hardware Limit Timer (HLT) and Windowed Watchdog Timer (WWDT) to support customers looking to add safety to their application. Additionally, this family includes up to 7 KB of Flash memory, along with a 10-bit ADC with Computation (ADC<sup>2</sup>) extensions for automated signal analysis to reduce the complexity of the application.

#### **Core Features**

- · C Compiler Optimized RISC Architecture

- Only 49 Instructions

- · Operating Speed:

- DC 32 MHz clock input

- 125 ns minimum instruction cycle

- · Interrupt Capability

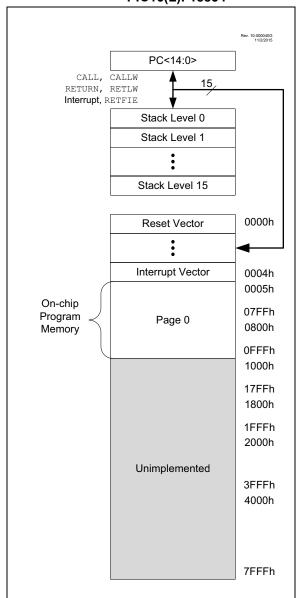

- 16-Level Deep Hardware Stack

- Three 8-Bit Timers (TMR2/4/6) with Hardware Limit Timer (HLT) Extensions

- Four 16-Bit Timers (TMR0/1/3/5)

- · Low-Current Power-on Reset (POR)

- Configurable Power-up Timer (PWRTE)

- · Brown-out Reset (BOR) with Fast Recovery

- · Low-Power BOR (LPBOR) Option

- Windowed Watchdog Timer (WWDT):

- Variable prescaler selection

- Variable window size selection

- All sources configurable in hardware or software

- · Programmable Code Protection

#### Memory

- Up to 7 KB Flash Program Memory

- · Up to 512B Data SRAM

- · 256B of EEPROM

- Direct, Indirect and Relative Addressing modes

### **Operating Characteristics**

- · Operating Voltage Range:

- 1.8V to 3.6V (PIC16LF18854)

- 2.3V to 5.5V (PIC16F18854)

- · Temperature Range:

- Industrial: -40°C to 85°C

- Extended: -40°C to 125°C

### **Power-Saving Functionality**

- DOZE mode: Ability to run the CPU core slower than the system clock

- IDLE mode: Ability to halt CPU core while internal peripherals continue operating

- Sleep mode: Lowest Power Consumption

- · Peripheral Module Disable (PMD):

- Ability to disable hardware module to minimize power consumption of unused peripherals

### eXtreme Low-Power (XLP) Features

- Sleep mode: 50 nA @ 1.8V, typical

- · Watchdog Timer: 500 nA @ 1.8V, typical

- Secondary Oscillator: 500 nA @ 32 kHz

- Operating Current:

- 8 μA @ 32 kHz, 1.8V, typical

- 32  $\mu$ A/MHz @ 1.8V, typical

## **Digital Peripherals**

- · Four Configurable Logic Cells (CLC):

- Integrated combinational and sequential logic

- Three Complementary Waveform Generators (CWG):

- Rising and falling edge dead-band control

- Full-bridge, half-bridge, 1-channel drive

- Multiple signal sources

- Five Capture/Compare/PWM (CCP) module:

- 16-bit resolution for Capture/Compare modes

- 10-bit resolution for PWM mode

- 10-bit PWM:

- Two 10-bit PWMs

- · Numerically Controlled Oscillator (NCO):

- Generates true linear frequency control and increased frequency resolution

- Input Clock: 0 Hz <  $F_{NCO}$  < 32 MHz

- Resolution: F<sub>NCO</sub>/220

- Two Signal Measurement Timers (SMT):

- 24-bit Signal Measurement Timer

- Up to 12 different Acquisition modes

### **Digital Peripherals (Cont.)**

- · Cyclical Redundancy Check (CRC/SCAN):

- 16-bit CRC

- Scans memory for NVM integrity

- · Communication:

- EUSART, RS-232, RS-485, LIN compatible

- Two SPI

- Two I<sup>2</sup>C, SMBus, PMBus™ compatible

- Up to 25 I/O Pins:

- Individually programmable pull-ups

- Slew rate control

- Interrupt-on-change with edge-select

- Input level selection control (ST or TTL)

- Digital open-drain enable

- Current mode enable

- · Peripheral Pin Select (PPS):

- Enables pin mapping of digital I/O

- Data Signal Modulator (DSM)

- Modulates a carrier signal with digital data to create custom carrier synchronized output waveforms

### **Analog Peripherals**

- Analog-to-Digital Converter with Computation (ADC<sup>2</sup>):

- 10-bit with up to 24 external channels

- Automated post-processing

- Automates math functions on input signals: averaging, filter calculations, oversampling and threshold comparison

- Operates in Sleep

- · Two Comparators (COMP):

- Fixed Voltage Reference at (non) inverting input(s)

- Comparator outputs externally accessible

- 5-Bit Digital-to-Analog Converter (DAC):

- 5-bit resolution, rail-to-rail

- Positive Reference Selection

- Unbuffered I/O pin output

- Internal connections to ADCs and comparators

- · Voltage Reference:

- Fixed Voltage Reference with 1.024V, 2.048V and 4.096V output levels

#### Flexible Oscillator Structure

- · High-Precision Internal Oscillator:

- Software selectable frequency range up to 32 MHz, ±1% typical

- x2/x4 PLL with Internal and External Sources

- Low-Power Internal 32 kHz Oscillator (LFINTOSC)

- External 32 kHz Crystal Oscillator (SOSC)

- · External Oscillator Block with:

- Three crystal/resonator modes up to 20 MHz

- Three external clock modes up to 20 MHz

- · Fail-Safe Clock Monitor:

- Allows for safe shutdown if peripheral clock stops

- Oscillator Start-up Timer (OST)

- Ensures stability of crystal oscillator resources

## PIC16(L)F188XX Family Types

| Device         | Data Sheet Index | Program Flash<br>Memory (Words) | Program Flash<br>Memory (KB) | EEPROM<br>(bytes) | Data SRAM<br>(bytes) | I/O Pins <sup>(1)</sup> | 10-Bit ADC <sup>2</sup> (ch) | 5-Bit DAC | Comparator | 8-Bit (with HLT)/<br>16-Bit Timers | SMT | Windowed<br>Watchdog Timer | CRC and Memory Scan | CCP/10-Bit PWM | Zero-Cross Detect | CWG | NCO | CLC | DSM | EUSART/I <sup>2</sup> C/SPI | Peripheral Pin Select | Peripheral Module<br>Disable |

|----------------|------------------|---------------------------------|------------------------------|-------------------|----------------------|-------------------------|------------------------------|-----------|------------|------------------------------------|-----|----------------------------|---------------------|----------------|-------------------|-----|-----|-----|-----|-----------------------------|-----------------------|------------------------------|

| PIC16(L)F18854 | (1)              | 4096                            | 7                            | 256               | 512                  | 25                      | 24                           | 1         | 2          | 3/4                                | 2   | Υ                          | Υ                   | 5/2            | Υ                 | 3   | 1   | 4   | 1   | 1/2                         | Υ                     | Υ                            |

| PIC16(L)F18855 | (2)              | 8192                            | 14                           | 256               | 1024                 | 25                      | 24                           | 1         | 2          | 3/4                                | 2   | Υ                          | Υ                   | 5/2            | Υ                 | 3   | 1   | 4   | 1   | 1/2                         | Υ                     | Υ                            |

| PIC16(L)F18856 | (3)              | 16384                           | 28                           | 256               | 2048                 | 25                      | 24                           | 1         | 2          | 3/4                                | 2   | Υ                          | Υ                   | 5/2            | Υ                 | 3   | 1   | 4   | 1   | 1/2                         | Υ                     | Υ                            |

| PIC16(L)F18857 | (4)              | 32768                           | 56                           | 256               | 4096                 | 25                      | 24                           | 1         | 2          | 3/4                                | 2   | Υ                          | Υ                   | 5/2            | Υ                 | 3   | 1   | 4   | 1   | 1/2                         | Υ                     | Υ                            |

| PIC16(L)F18875 | (2)              | 8192                            | 14                           | 256               | 1024                 | 36                      | 35                           | 1         | 2          | 3/4                                | 2   | Υ                          | Υ                   | 5/2            | Υ                 | 3   | 1   | 4   | 1   | 1/2                         | Υ                     | Υ                            |

| PIC16(L)F18876 | (3)              | 16384                           | 28                           | 256               | 2048                 | 36                      | 35                           | 1         | 2          | 3/4                                | 2   | Υ                          | Υ                   | 5/2            | Υ                 | 3   | 1   | 4   | 1   | 1/2                         | Υ                     | Υ                            |

| PIC16(L)F18877 | (4)              | 32768                           | 56                           | 256               | 4096                 | 36                      | 35                           | 1         | 2          | 3/4                                | 2   | Υ                          | Υ                   | 5/2            | Υ                 | 3   | 1   | 4   | 1   | 1/2                         | Υ                     | Υ                            |

Note 1: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document)

DS40001826 PIC16(L)F18854 Data Sheet, 28-Pin, Full-Featured 8-bit Microcontrollers

DS40001802 PIC16(L)F18855/75 Data Sheet, 28/40-Pin, Full-Featured 8-bit Microcontrollers

DS40001824 PIC16(L)F18856/76 Data Sheet, 28/40-Pin, Full-Featured 8-bit Microcontrollers

DS40001825 PIC16(L)F18857/77 Data Sheet, 28/40-Pin, Full-Featured 8-bit Microcontrollers

**Note:** For other small form-factor package availability and marking information, please visit <a href="http://www.microchip.com/packaging">http://www.microchip.com/packaging</a> or contact your local sales office.

© 2016 Microchip Technology Inc. Preliminary DS40001826A-page 3

TABLE 1: PACKAGES

| Packages       | (S)PDIP | SOIC | SSOP | QFN<br>(6x6) | UQFN<br>(4x4) | TQFP | QFN<br>(8x8) | UQFN<br>(5x5) |

|----------------|---------|------|------|--------------|---------------|------|--------------|---------------|

| PIC16(L)F18854 | •       | •    | •    | •            | •             |      |              |               |

**Note:** Pin details are subject to change.

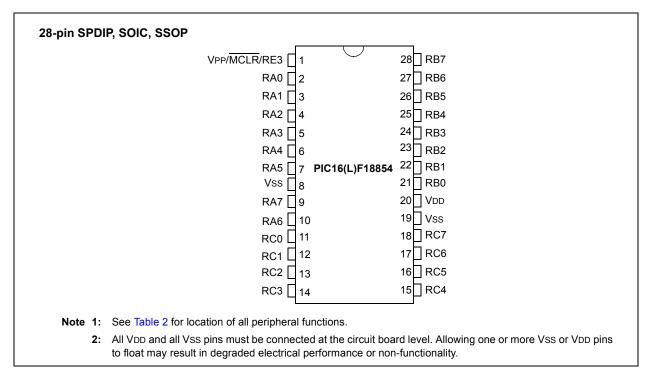

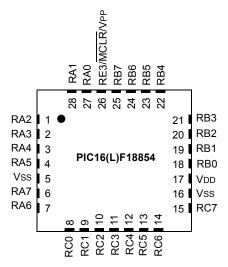

### **PIN DIAGRAMS**

28-pin QFN (6x6), UQFN (4x4)

- Note 1: See Table 2 for location of all peripheral functions.

- 2: All VDD and all VSS pins must be connected at the circuit board level. Allowing one or more VSS or VDD pins to float may result in degraded electrical performance or non-functionality.

- 3: The bottom pad of the QFN/UQFN package should be connected to Vss at the circuit board level.

© 2016 Microchip Technology Inc. Preliminary DS40001826A-page 5

DS40001826A-page 6

## **PIN ALLOCATION TABLES**

## TABLE 2: 28-PIN ALLOCATION TABLE (PIC16(L)F18854)

| 0/1 | 28-Pin SPDIP/SOIC/SSOP | 28-Pin (U)QFN | ADC                           | Voltage Reference | DAC      | Comparators      | Zero-Cross Detect | MSSP (SPI/I <sup>2</sup> C)                  | EUSART | DSM                   | Timers/SMT                                   | CCP and PWM         | CWG                   | פרכ                   | NCO | Clock Reference (CLKR) | Interrupt-on-Change         | Basic          |

|-----|------------------------|---------------|-------------------------------|-------------------|----------|------------------|-------------------|----------------------------------------------|--------|-----------------------|----------------------------------------------|---------------------|-----------------------|-----------------------|-----|------------------------|-----------------------------|----------------|

| RA0 | 2                      | 27            | ANA0                          | _                 | _        | C1IN0-<br>C2IN0- | _                 | _                                            | _      | _                     | _                                            | _                   | _                     | CLCIN0 <sup>(1)</sup> | -   | _                      | IOCA0                       | _              |

| RA1 | 3                      | 28            | ANA1                          | _                 | _        | C1IN1-<br>C2IN1- | _                 | _                                            | _      | _                     | _                                            | -                   | _                     | CLCIN1 <sup>(1)</sup> |     | _                      | IOCA1                       | _              |

| RA2 | 4                      | 1             | ANA2                          | VREF-             | DAC1OUT1 | C1IN0+<br>C2IN0+ | _                 | _                                            | _      | _                     | _                                            | -                   | _                     | _                     | -   | _                      | IOCA2                       | _              |

| RA3 | 5                      | 2             | ANA3                          | VREF+             | _        | C1IN1+           | _                 | _                                            | _      | MDCARL <sup>(1)</sup> | _                                            | _                   | _                     | _                     | _   | _                      | IOCA3                       | _              |

| RA4 | 6                      | 3             | ANA4                          | _                 | _        | _                | _                 | _                                            | _      | MDCARH <sup>(1)</sup> | T0CKI <sup>(1)</sup>                         | CCP5 <sup>(1)</sup> | _                     |                       | _   | _                      | IOCA4                       | _              |

| RA5 | 7                      | 4             | ANA5                          | _                 | _        | _                | _                 | SS1 <sup>(1)</sup>                           | _      | MDSRC <sup>(1)</sup>  | _                                            |                     | _                     | _                     | _   | _                      | IOCA5                       | _              |

| RA6 | 10                     | 7             | ANA6                          | _                 | _        | _                | -                 | _                                            | _      | _                     | _                                            | _                   | _                     | _                     | 1   | _                      | IOCA6                       | OSC2<br>CLKOUT |

| RA7 | 9                      | 6             | ANA7                          | _                 | _        | _                | _                 | _                                            | _      | _                     | _                                            | -                   | _                     | -                     |     | _                      | IOCA7                       | OSC1<br>CLKIN  |

| RB0 | 21                     | 18            | ANB0                          | _                 | _        | C2IN1+           | ZCD               | SS2 <sup>(1)</sup>                           | _      | _                     | _                                            | CCP4 <sup>(1)</sup> | CWG1IN <sup>(1)</sup> | _                     | _   | _                      | INT <sup>(1)</sup><br>IOCB0 | _              |

| RB1 | 22                     | 19            | ANB1                          | _                 | _        | C1IN3-<br>C2IN3- | _                 | SCL2 <sup>(3,4)</sup><br>SCK2 <sup>(1)</sup> | _      | _                     | _                                            | _                   | CWG2IN <sup>(1)</sup> | _                     | -   | _                      | IOCB1                       | _              |

| RB2 | 23                     | 20            | ANB2                          | _                 | _        | _                | _                 | SDA2 <sup>(3,4)</sup><br>SDI2 <sup>(1)</sup> | _      | _                     | _                                            | _                   | CWG3IN <sup>(1)</sup> | _                     | -   | _                      | IOCB2                       | _              |

| RB3 | 24                     | 21            | ANB3                          | _                 | _        | C1IN2-<br>C2IN2- | _                 | _                                            | _      | _                     | _                                            | _                   | _                     | _                     | _   | _                      | IOCB3                       | _              |

| RB4 | 25                     | 22            | ANB4<br>ADCACT <sup>(1)</sup> | _                 | _        | _                | _                 | _                                            | _      | -                     | T5G <sup>(1)</sup><br>SMTWIN2 <sup>(1)</sup> | _                   | _                     | _                     |     | _                      | IOCB4                       | _              |

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTX pins. Refer to Table 13-1 for details on which port pins may be used for this signal.

<sup>2:</sup> All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTX pin options as described in Table 13-3.

<sup>3:</sup> This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

<sup>4:</sup> These pins are configured for I<sup>2</sup>C logic levels.; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMbus input buffer thresholds.

TABLE 2: 28-PIN ALLOCATION TABLE (PIC16(L)F18854) (CONTINUED)

| O/I | 28-Pin SPDIP/SOIC/SSOP | 28-Pin (U)QFN | ADC  | Voltage Reference | DAC      | Comparators | Zero-Cross Detect | MSSP (SPI/I <sup>2</sup> C)                  | EUSART                                 | DSM | Timers/SMT                                                                          | CCP and PWM         | CWG | CLC                   | OON | Clock Reference (CLKR) | Interrupt-on-Change | Basic       |

|-----|------------------------|---------------|------|-------------------|----------|-------------|-------------------|----------------------------------------------|----------------------------------------|-----|-------------------------------------------------------------------------------------|---------------------|-----|-----------------------|-----|------------------------|---------------------|-------------|

| RB5 | 26                     | 23            | ANB5 | _                 | _        | _           | _                 | _                                            | _                                      |     | T1G <sup>(1)</sup><br>SMTSIG2 <sup>(1)</sup>                                        | CCP3 <sup>(1)</sup> | _   | _                     | _   | _                      | IOCB5               | _           |

| RB6 | 27                     | 24            | ANB6 | _                 | _        | _           | _                 | _                                            | _                                      | _   | _                                                                                   | _                   | _   | CLCIN2 <sup>(1)</sup> | _   | _                      | IOCB6               | ICSPCLK     |

| RB7 | 28                     | 25            | ANB7 | _                 | DAC1OUT2 | _           | _                 | _                                            | _                                      | _   | T6IN <sup>(1)</sup>                                                                 | _                   | _   | CLCIN3 <sup>(1)</sup> | _   | _                      | IOCB7               | ICSPDAT     |

| RC0 | 11                     | 8             | ANC0 | _                 | _        | _           | _                 | _                                            | _                                      | _   | T1CKI <sup>(1)</sup> T3CKI <sup>(1)</sup> T3G <sup>(1)</sup> SMTWIN1 <sup>(1)</sup> | _                   | _   | _                     | _   | -                      | IOCC0               | sosco       |

| RC1 | 12                     | 9             | ANC1 | _                 | _        | _           | _                 | _                                            | _                                      | l   | SMTSIG1 <sup>(1)</sup>                                                              | CCP2 <sup>(1)</sup> | _   | _                     | _   |                        | IOCC1               | SOSCI       |

| RC2 | 13                     | 10            | ANC2 | _                 |          | _           | _                 | _                                            | _                                      | -   | T5CKI <sup>(1)</sup>                                                                | CCP1 <sup>(1)</sup> | _   | _                     | -   | _                      | IOCC2               | _           |

| RC3 | 14                     | 11            | ANC3 | _                 | _        | _           | _                 | SCL1 <sup>(3,4)</sup><br>SCK1 <sup>(1)</sup> | _                                      | _   | T2IN <sup>(1)</sup>                                                                 | _                   | _   | _                     | _   | _                      | IOCC3               | _           |

| RC4 | 15                     | 12            | ANC4 | _                 | _        | _           | _                 | SDA1 <sup>(3,4)</sup><br>SDI1 <sup>(1)</sup> | _                                      | _   | _                                                                                   | _                   | _   | _                     | _   | _                      | IOCC4               | _           |

| RC5 | 16                     | 13            | ANC5 | _                 | _        | _           | _                 | _                                            | _                                      | _   | T4IN <sup>(1)</sup>                                                                 | _                   | _   | _                     | _   | _                      | IOCC5               | _           |

| RC6 | 17                     | 14            | ANC6 | _                 | _        | _           | _                 | _                                            | CK(3)                                  | _   | _                                                                                   | _                   | _   | _                     | _   | _                      | IOCC6               | _           |

| RC7 | 18                     | 15            | ANC7 | _                 | _        | _           | _                 | _                                            | RX <sup>(1)</sup><br>DT <sup>(3)</sup> | _   | _                                                                                   | _                   | _   | _                     | _   | _                      | IOCC7               | _           |

| RE3 | 1                      | 26            |      | _                 | _        |             | _                 | _                                            | _                                      | _   | _                                                                                   |                     | _   | _                     | 1   | _                      | IOCE3               | MCLR<br>VPP |

| VDD | 20                     | 17            | _    | _                 | _        | _           | _                 | _                                            | _                                      | _   | _                                                                                   | _                   | _   | _                     | _   | _                      | _                   | _           |

| Vss | 8,<br>19               | 5,<br>16      | _    | _                 | _        | _           | _                 | _                                            | _                                      | _   | _                                                                                   | _                   | _   | _                     | _   | _                      | _                   | _           |

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTX pins. Refer to Table 13-1 for details on which port pins may be used for this signal.

<sup>2:</sup> All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTX pin options as described in Table 13-3.

<sup>3:</sup> This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

<sup>4:</sup> These pins are configured for I<sup>2</sup>C logic levels.; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMbus input buffer thresholds.

Note

TABLE 2: 28-PIN ALLOCATION TABLE (PIC16(L)F18854) (CONTINUED)

| O/I                | 28-Pin SPDIP/SOIC/SSOP | 28-Pin (U)QFN | ADC              | Voltage Reference | DAC | Comparators    | Zero-Cross Detect | MSSP (SPIII <sup>2</sup> C)  | EUSART                                        | DSM | Timers/SMT | CCP and PWM                                                | CWG                                                                                                      | כרכ                                      | NCO | Clock Reference (CLKR) | Interrupt-on-Change | Basic |

|--------------------|------------------------|---------------|------------------|-------------------|-----|----------------|-------------------|------------------------------|-----------------------------------------------|-----|------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------|-----|------------------------|---------------------|-------|

| OUT <sup>(2)</sup> |                        |               | ADGRDA<br>ADGRDB | 1                 | _   | C1OUT<br>C2OUT | I                 | SDO1<br>SCK1<br>SDO2<br>SCK2 | TX/<br>CK <sup>(3)</sup><br>DT <sup>(3)</sup> | DSM | TMR0       | CCP1<br>CCP2<br>CCP3<br>CCP4<br>CCP5<br>PWM6OUT<br>PWM7OUT | CWG1A<br>CWG1B<br>CWG1C<br>CWG1D<br>CWG2A<br>CWG2B<br>CWG2C<br>CWG2D<br>CWG3A<br>CWG3B<br>CWG3C<br>CWG3D | CLC1OUT<br>CLC2OUT<br>CLC3OUT<br>CLC4OUT | NCO | CLKR                   |                     | _     |

PIC16(L)F18854

1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTX pins. Refer to Table 13-1 for details on which port pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTX pin options as described in Table 13-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels.; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMbus input buffer thresholds.

## **Table of Contents**

| 1.0  | Device Overview                                                           | 11  |

|------|---------------------------------------------------------------------------|-----|

| 2.0  | Enhanced Mid-Range CPU                                                    | 21  |

| 3.0  | Memory Organization                                                       | 23  |

| 4.0  | Device Configuration                                                      | 73  |

| 5.0  | Resets                                                                    | 82  |

| 3.0  | Oscillator Module (with Fail-Safe Clock Monitor)                          | 91  |

| 7.0  | Interrupts                                                                | 109 |

| 3.0  | Power-Saving Operation Modes                                              | 135 |

| 9.0  | Windowed Watchdog Timer (WWDT)                                            | 142 |

| 10.0 |                                                                           |     |

| 11.0 | Cyclic Redundancy Check (CRC) Module                                      | 168 |

| 12.0 | I/O Ports                                                                 | 180 |

| 13.0 | Peripheral Pin Select (PPS) Module                                        | 208 |

| 14.0 | Peripheral Module Disable                                                 | 218 |

| 15.0 | Interrupt-On-Change                                                       | 225 |

| 16.0 | Fixed Voltage Reference (FVR)                                             | 233 |

| 17.0 | Temperature Indicator Module                                              | 237 |

| 18.0 | Comparator Module                                                         | 239 |

| 19.0 | Pulse-Width Modulation (PWM)                                              | 249 |

| 20.0 | Complementary Waveform Generator (CWG) Module                             | 256 |

| 21.0 | Zero-Cross Detection (ZCD) Module                                         | 280 |

| 22.0 | Configurable Logic Cell (CLC)                                             | 285 |

| 23.0 | Analog-to-Digital Converter With Computation (ADC2) Module                | 302 |

| 24.0 | Numerically Controlled Oscillator (NCO) Module                            | 341 |

| 25.0 | 5-Bit Digital-to-Analog Converter (DAC1) Module                           | 351 |

| 26.0 | Data Signal Modulator (DSM) Module                                        | 356 |

| 27.0 | Timer0 Module                                                             |     |

| 28.0 | Timer1/3/5 Module with Gate Control                                       | 375 |

| 29.0 | Timer2/4/6 Module                                                         | 388 |

| 30.0 | Capture/Compare/PWM Modules                                               | 411 |

|      | Master Synchronous Serial Port (MSSP) Modules                             |     |

| 32.0 | Signal Measurement Timer (SMT)                                            | 475 |

| 33.0 | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | 520 |

|      | Reference Clock Output Module                                             |     |

| 35.0 | In-Circuit Serial Programming™ (ICSP™)                                    | 552 |

| 36.0 | Instruction Set Summary                                                   | 554 |

| 37.0 | Electrical Specifications                                                 | 568 |

| 38.0 | DC and AC Characteristics Graphs and Charts                               | 597 |

| 39.0 | Development Support                                                       | 598 |

| 40.0 | Packaging Information                                                     | 602 |

| Data | a Sheet Revision History                                                  | 616 |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

## 1.0 DEVICE OVERVIEW

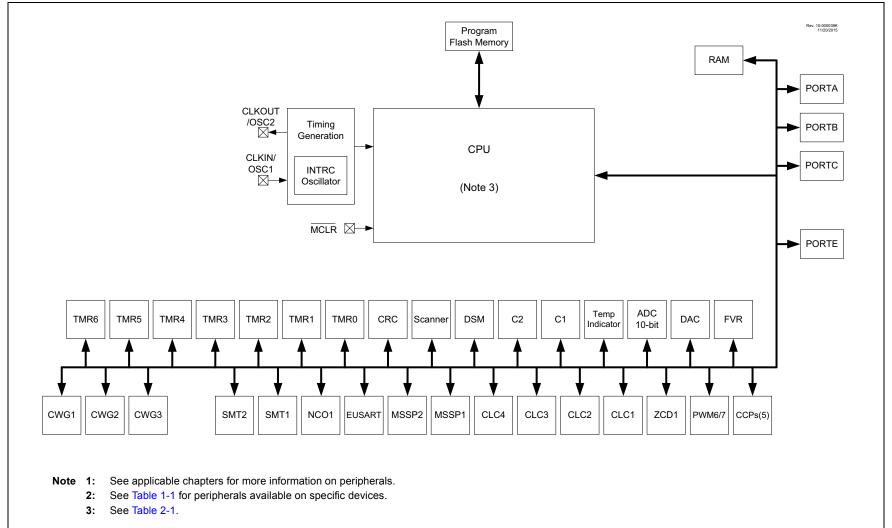

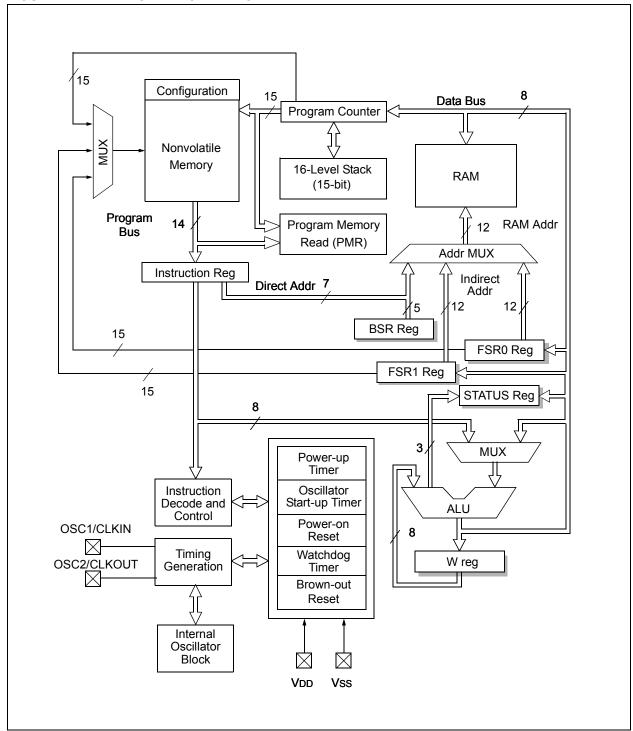

The PIC16(L)F18854 are described within this data sheet. The PIC16(L)F18854 devices are available in 28-pin SPDIP, SSOP, SOIC, and UQFN packages. Figure 1-1 shows a block diagram of the PIC16(L)F18854 devices. Table 1-2 shows the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| Peripheral                                                      |                          | PIC16(L)F18854 |

|-----------------------------------------------------------------|--------------------------|----------------|

| Analog-to-Digital Converter with Computation                    | tion (ADC <sup>2</sup> ) | •              |

| Cyclic Redundancy Check (CRC)                                   |                          | •              |

| Digital-to-Analog Converter (DAC)                               |                          | •              |

| Fixed Voltage Reference (FVR)                                   |                          | •              |

| Enhanced Universal Synchronous/Asynchr<br>Transmitter (EUSART1) | onous Receiver/          | •              |

| Digital Signal Modulator (DSM)                                  |                          | •              |

| Numerically Controlled Oscillator (NCO1)                        |                          | •              |

| Temperature Indicator                                           |                          | •              |

| Zero-Cross Detect (ZCD)                                         |                          | •              |

| Capture/Compare/PWM (CCP/ECCP) Mod                              |                          |                |

|                                                                 | CCP1                     | •              |

|                                                                 | CCP2<br>CCP3             | •              |

|                                                                 | CCP4                     | •              |

|                                                                 | CCP4                     | •              |

| Comparators                                                     | 30.0                     |                |

|                                                                 | C1                       | •              |

|                                                                 | C2                       | •              |

| Configurable Logic Cell (CLC)                                   |                          |                |

|                                                                 | CLC1                     | •              |

|                                                                 | CLC2                     | •              |

|                                                                 | CLC3                     | •              |

|                                                                 | CLC4                     | •              |

| Complementary Waveform Generator (CWC                           | r e                      |                |

|                                                                 | CWG1                     | •              |

|                                                                 | CWG2                     | •              |

| Martin Ourahamana Out I Day                                     | CWG3                     | •              |

| Master Synchronous Serial Ports                                 | Meena                    | _              |

|                                                                 | MSSP1<br>MSSP2           | •              |

| Pulse-Width Modulator (PWM)                                     | IVISSP2                  | _              |

| i disc viidii ivioddiatoi (i vvivi)                             | PWM6                     | •              |

|                                                                 | PWM7                     |                |

| Signal Measure Timer (SMT)                                      | 1                        |                |

| /                                                               |                          |                |

|                                                                 | SMT1                     | •              |

TABLE 1-1: DEVICE PERIPHERAL SUMMARY (CONTINUED)

| Peripheral |        | PIC16(L)F18854 |

|------------|--------|----------------|

| Timers     |        |                |

|            | Timer0 | •              |

|            | Timer1 | •              |

|            | Timer2 | •              |

|            | Timer3 | •              |

|            | Timer4 | •              |

|            | Timer5 | •              |

|            | Timer6 | •              |

## 1.1 Register and Bit naming conventions

#### 1.1.1 REGISTER NAMES

When there are multiple instances of the same peripheral in a device, the peripheral control registers will be depicted as the concatenation of a peripheral identifier, peripheral instance, and control identifier. The control registers section will show just one instance of all the register names with an 'x' in the place of the peripheral instance number. This naming convention may also be applied to peripherals when there is only one instance of that peripheral in the device to maintain compatibility with other devices in the family that contain more than one.

#### 1.1.2 BIT NAMES

There are two variants for bit names:

- · Short name: Bit function abbreviation

- Long name: Peripheral abbreviation + short name

#### 1.1.2.1 Short Bit Names

Short bit names are an abbreviation for the bit function. For example, some peripherals are enabled with the EN bit. The bit names shown in the registers are the short name variant.

Short bit names are useful when accessing bits in C programs. The general format for accessing bits by the short name is RegisterNamebits. ShortName. For example, the enable bit, EN, in the COG1CON0 register can be set in C programs with the instruction COG1CON0bits.EN = 1.

Short names are generally not useful in assembly programs because the same name may be used by different peripherals in different bit positions. When this occurs, during the include file generation, all instances of that short bit name are appended with an underscore plus the name of the register in which the bit resides to avoid naming contentions.

### 1.1.2.2 Long Bit Names

Long bit names are constructed by adding a peripheral abbreviation prefix to the short name. The prefix is unique to the peripheral thereby making every long bit name unique. The long bit name for the COG1 enable bit is the COG1 prefix, G1, appended with the enable bit short name, EN, resulting in the unique bit name G1EN.

Long bit names are useful in both C and assembly programs. For example, in C the COG1CON0 enable bit can be set with the G1EN = 1 instruction. In assembly, this bit can be set with the BSF COG1CON0, G1EN instruction.

#### 1.1.2.3 Bit Fields

Bit fields are two or more adjacent bits in the same register. Bit fields adhere only to the short bit naming convention. For example, the three Least Significant bits of the COG1CON0 register contain the mode control bits. The short name for this field is MD. There is no long bit name variant. Bit field access is only possible in C programs. The following example demonstrates a C program instruction for setting the COG1 to the Push-Pull mode:

```

COG1CON0bits.MD = 0x5;

```

Individual bits in a bit field can also be accessed with long and short bit names. Each bit is the field name appended with the number of the bit position within the field. For example, the Most Significant mode bit has the short bit name MD2 and the long bit name is G1MD2. The following two examples demonstrate assembly program sequences for setting the COG1 to Push-Pull mode:

#### Example 1:

```

MOVLW ~(1<<G1MD1)

ANDWF COG1CON0,F

MOVLW 1<<G1MD2 | 1<<G1MD0

IORWF COG1CON0,F

```

#### Example 2:

BSF COG1CON0, G1MD2 BCF COG1CON0, G1MD1 BSF COG1CON0, G1MD0

## 1.1.3 REGISTER AND BIT NAMING EXCEPTIONS

### 1.1.3.1 Status, Interrupt, and Mirror Bits

Status, interrupt enables, interrupt flags, and mirror bits are contained in registers that span more than one peripheral. In these cases, the bit name shown is unique so there is no prefix or short name variant.

## 1.1.3.2 Legacy Peripherals

There are some peripherals that do not strictly adhere to these naming conventions. Peripherals that have existed for many years and are present in almost every device are the exceptions. These exceptions were necessary to limit the adverse impact of the new conventions on legacy code. Peripherals that do adhere to the new convention will include a table in the registers section indicating the long name prefix for each peripheral instance. Peripherals that fall into the exception category will not have this table. These peripherals include, but are not limited to, the following:

- EUSART

- MSSP

© 2016 Microchip Technology Inc.

FIGURE 1-1: PIC16(L)F18854 BLOCK DIAGRAM

PIC16F18854 PINOUT DESCRIPTION **TABLE 1-2:**

| Name                                                                                 | Function              | Input<br>Type | Output Type | Description                                                         |

|--------------------------------------------------------------------------------------|-----------------------|---------------|-------------|---------------------------------------------------------------------|

| RA0/ANA0/C1IN0-/C2IN0-/CLCIN0 <sup>(1)</sup> /<br>IOCA0                              | RA0                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                |

| IOCAU                                                                                | ANA0                  | AN            | _           | ADC Channel A0 input.                                               |

|                                                                                      | C1IN0-                | AN            | _           | Comparator negative input.                                          |

|                                                                                      | C2IN0-                | AN            | _           | Comparator negative input.                                          |

|                                                                                      | CLCINO <sup>(1)</sup> | TTL/ST        | _           | Configurable Logic Cell source input.                               |

|                                                                                      | IOCA0                 | TTL/ST        | _           | Interrupt-on-change input.                                          |

| RA1/ANA1/C1IN1-/C2IN1-/CLCIN1 <sup>(1)</sup> /                                       | RA1                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                |

| IOCA1                                                                                | ANA1                  | AN            | _           | ADC Channel A1 input.                                               |

|                                                                                      | C1IN1-                | AN            | _           | Comparator negative input.                                          |

|                                                                                      | C2IN1-                | AN            | _           | Comparator negative input.                                          |

|                                                                                      | CLCIN1 <sup>(1)</sup> | TTL/ST        | _           | Configurable Logic Cell source input.                               |

|                                                                                      | IOCA1                 | TTL/ST        | _           | Interrupt-on-change input.                                          |

| RA2/ANA2/C1IN0+/C2IN0+/VREF-/                                                        | RA2                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                |

| DAC1OUT1/IOCA2                                                                       | ANA2                  | AN            | _           | ADC Channel A2 input.                                               |

|                                                                                      | C1IN0+                | AN            | _           | Comparator positive input.                                          |

|                                                                                      | C2IN0+                | AN            | _           | Comparator positive input.                                          |

|                                                                                      | VREF-                 | AN            | _           | External ADC and/or DAC negative reference input.                   |

|                                                                                      | DAC1OUT1              | _             | AN          | Digital-to-Analog Converter output.                                 |

|                                                                                      | IOCA2                 | TTL/ST        | _           | Interrupt-on-change input.                                          |

| RA3/ANA3/C1IN1+/VREF+/MDCARL <sup>(1)</sup> /                                        | RA3                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                |

| IOCAS                                                                                | ANA3                  | AN            | _           | ADC Channel A3 input.                                               |

|                                                                                      | C1IN1+                | AN            | _           | Comparator positive input.                                          |

|                                                                                      | VREF+                 | AN            | _           | External ADC and/or DAC positive reference input.                   |

|                                                                                      | MDCARL <sup>(1)</sup> | TTL/ST        | _           | Modular Carrier input 1.                                            |

|                                                                                      | IOCA3                 | TTL/ST        | _           | Interrupt-on-change input.                                          |

| RA4/ANA4/MDCARH <sup>(1)</sup> /T0CKI <sup>(1)</sup> /<br>CCP5 <sup>(1)</sup> /IOCA4 | RA4                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                |

| CCP5\*'/IOCA4                                                                        | ANA4                  | AN            | _           | ADC Channel A4 input.                                               |

|                                                                                      | MDCARH <sup>(1)</sup> | TTL/ST        | _           | Modular Carrier input 2.                                            |

|                                                                                      | T0CKI <sup>(1)</sup>  | TTL/ST        | _           | Timer0 clock input.                                                 |

|                                                                                      | CCP5 <sup>(1)</sup>   | TTL/ST        | CMOS/OD     | Capture/compare/PWM5 (default input location for capture function). |

|                                                                                      | IOCA4                 | TTL/ST        | _           | Interrupt-on-change input.                                          |

Legend: AN = Analog input or output CMOS = CMOS compatible input or output = Open-Drain

OD I<sup>2</sup>C TTL = TTL compatible input ST Schmitt Trigger input with CMOS levels = Schmitt Trigger input with I<sup>2</sup>C HV = High Voltage XTAL = Crystal levels

Note This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 13-1 for details on which PORT pins may be used for this signal.

All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 13-3.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and 3: PPS output registers.

These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

**TABLE 1-2:** PIC16F18854 PINOUT DESCRIPTION (CONTINUED)

| Name                                                                                                              | Function              | Input<br>Type              | Output Type | Description                                                                                 |

|-------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------|-------------|---------------------------------------------------------------------------------------------|

| RA5/ANA5/SS1 <sup>(1)</sup> /MDSRC <sup>(1)</sup> /IOCA5                                                          | RA5                   | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                        |

|                                                                                                                   | ANA5                  | AN                         | _           | ADC Channel A5 input.                                                                       |

|                                                                                                                   | SS1 <sup>(1)</sup>    | TTL/ST                     | _           | MSSP1 SPI slave select input.                                                               |

|                                                                                                                   | MDSRC <sup>(1)</sup>  | TTL/ST                     | _           | Modulator Source input.                                                                     |

|                                                                                                                   | IOCA5                 | TTL/ST                     | _           | Interrupt-on-change input.                                                                  |

| RA6/ANA6/OSC2/CLKOUT/IOCA6                                                                                        | RA6                   | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                        |

|                                                                                                                   | ANA6                  | AN                         | _           | ADC Channel A6 input.                                                                       |

|                                                                                                                   | OSC2                  | _                          | XTAL        | External Crystal/Resonator (LP, XT, HS modes) driver output.                                |

|                                                                                                                   | CLKOUT                | _                          | CMOS/OD     | Fosc/4 digital output (in non-crystal/resonator modes).                                     |

|                                                                                                                   | IOCA6                 | TTL/ST                     | _           | Interrupt-on-change input.                                                                  |

| RA7/ANA7/OSC1/CLKIN/IOCA7                                                                                         | RA7                   | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                        |

|                                                                                                                   | ANA7                  | AN                         | _           | ADC Channel A7 input.                                                                       |

|                                                                                                                   | OSC1                  | XTAL                       | _           | External Crystal/Resonator (LP, XT, HS modes) driver input.                                 |

|                                                                                                                   | CLKIN                 | TTL/ST                     | _           | External digital clock input.                                                               |

|                                                                                                                   | IOCA7                 | TTL/ST                     | _           | Interrupt-on-change input.                                                                  |

| RB0/ANB0/C2IN1+/ZCD/SS2 <sup>(1)</sup> /<br>CCP4 <sup>(1)</sup> /CWG1IN <sup>(1)</sup> /INT <sup>(1)</sup> /IOCB0 | RB0                   | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                        |

| CCP4(*//CWGTIN(*//INTX*//IOCBU                                                                                    | ANB0                  | AN                         | _           | ADC Channel B0 input.                                                                       |

|                                                                                                                   | C2IN1+                | AN                         | _           | Comparator positive input.                                                                  |

|                                                                                                                   | ZCD                   | AN                         | AN          | Zero-cross detect input pin (with constant current sink/source).                            |

|                                                                                                                   | SS2 <sup>(1)</sup>    | TTL/ST                     | _           | MSSP2 SPI slave select input.                                                               |

|                                                                                                                   | CCP4 <sup>(1)</sup>   | TTL/ST                     | CMOS/OD     | Capture/compare/PWM4 (default input location for capture function).                         |

|                                                                                                                   | CWG1IN <sup>(1)</sup> | TTL/ST                     | _           | Complementary Waveform Generator 1 input.                                                   |

|                                                                                                                   | INT <sup>(1)</sup>    | TTL/ST                     | _           | External interrupt request input.                                                           |

|                                                                                                                   | IOCB0                 | TTL/ST                     | _           | Interrupt-on-change input.                                                                  |

| RB1/ANB1/C1IN3-/C2IN3-/SCL2 <sup>(3,4)</sup> /<br>SCK2 <sup>(1)</sup> /CWG2IN <sup>(1)</sup> /IOCB1               | RB1                   | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                        |

| SORZY YOWGZINY YIOODT                                                                                             | ANB1                  | AN                         | _           | ADC Channel B1 input.                                                                       |

|                                                                                                                   | C1IN3-                | AN                         | _           | Comparator negative input.                                                                  |

|                                                                                                                   | C2IN3-                | AN                         | _           | Comparator negative input.                                                                  |

|                                                                                                                   | SCL2 <sup>(3,4)</sup> | I <sup>2</sup> C/<br>SMBus | OD          | MSSP2 I <sup>2</sup> C clock input/output.                                                  |

|                                                                                                                   | SCK2 <sup>(1)</sup>   | TTL/ST                     | CMOS/OD     | MSSP2 SPI serial clock (default input location, SCK2 is a PPS remappable input and output). |

|                                                                                                                   | CWG2IN <sup>(1)</sup> | TTL/ST                     | _           | Complementary Waveform Generator 2 input.                                                   |

|                                                                                                                   | IOCB1                 | TTL/ST                     | _           | Interrupt-on-change input.                                                                  |

**Legend:** AN = Analog input or output

CMOS = CMOS compatible input or output

= Open-Drain

TTL = TTL compatible input = High Voltage

ST = Schmitt Trigger input with CMOS levels I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C

Note

= Crystal levels XTAL

- This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx 1: pins. Refer to Table 13-1 for details on which PORT pins may be used for this signal.

- All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 13-3.

- This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and 3: PPS output registers.

- These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

TABLE 1-2: PIC16F18854 PINOUT DESCRIPTION (CONTINUED)

| Name                                                                                  | Function               | Input<br>Type              | Output Type | Description                                                         |

|---------------------------------------------------------------------------------------|------------------------|----------------------------|-------------|---------------------------------------------------------------------|

| RB2/ANB2/SDA2 <sup>(3,4)</sup> /SDI2 <sup>(1)</sup> /<br>CWG3IN <sup>(1)</sup> /IOCB2 | RB2                    | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                |

| CWG3IN 7/IOCB2                                                                        | ANB2                   | AN                         | _           | ADC Channel B2 input.                                               |

|                                                                                       | SDA2 <sup>(3,4)</sup>  | I <sup>2</sup> C/<br>SMBus | OD          | MSSP2 I <sup>2</sup> C serial data input/output.                    |

|                                                                                       | SDI2 <sup>(1)</sup>    | TTL/ST                     | _           | MSSP2 SPI serial data input.                                        |

|                                                                                       | CWG3IN <sup>(1)</sup>  | TTL/ST                     | _           | Complementary Waveform Generator 3 input.                           |

|                                                                                       | IOCB2                  | TTL/ST                     | _           | Interrupt-on-change input.                                          |

| RB3/ANB3/C1IN2-/C2IN2-/IOCB3                                                          | RB3                    | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                |

|                                                                                       | ANB3                   | AN                         | _           | ADC Channel B3 input.                                               |

|                                                                                       | C1IN2-                 | AN                         | _           | Comparator negative input.                                          |

|                                                                                       | C2IN2-                 | AN                         | _           | Comparator negative input.                                          |

|                                                                                       | IOCB3                  | TTL/ST                     | _           | Interrupt-on-change input.                                          |

| RB4/ANB4/ADCACT <sup>(1)</sup> /T5G <sup>(1)</sup> /<br>SMTWIN2 <sup>(1)</sup> /IOCB4 | RB4                    | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                |

| SMTWINZ***/IOCB4                                                                      | ANB4                   | AN                         | _           | ADC Channel B4 input.                                               |

|                                                                                       | ADCACT <sup>(1)</sup>  | TTL/ST                     | _           | ADC Auto-Conversion Trigger input.                                  |

|                                                                                       | T5G <sup>(1)</sup>     | TTL/ST                     | _           | Timer5 gate input.                                                  |

|                                                                                       | SMTWIN2 <sup>(1)</sup> | TTL/ST                     | _           | Signal Measurement Timer 2 (SMT2) window input.                     |

|                                                                                       | IOCB4                  | TTL/ST                     | _           | Interrupt-on-change input.                                          |

| RB5/ANB5/T1G <sup>(1)</sup> /SMTSIG2 <sup>(1)</sup> /<br>CCP3 <sup>(1)</sup> /IOCB5   | RB5                    | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                |

| CCP3(*//IOCB5                                                                         | ANB5                   | AN                         | _           | ADC Channel B5 input.                                               |

|                                                                                       | T1G <sup>(1)</sup>     | TTL/ST                     | _           | Timer1 gate input.                                                  |

|                                                                                       | SMTSIG2 <sup>(1)</sup> | TTL/ST                     | _           | Signal Measurement Timer 2 (SMT2) signal input.                     |

|                                                                                       | CCP3 <sup>(1)</sup>    | TTL/ST                     | CMOS/OD     | Capture/compare/PWM3 (default input location for capture function). |

|                                                                                       | IOCB5                  | TTL/ST                     | _           | Interrupt-on-change input.                                          |

| RB6/ANB6/CLCIN2 <sup>(1)</sup> /IOCB6/ICSPCLK                                         | RB6                    | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                |

|                                                                                       | ANB6                   | AN                         | _           | ADC Channel B6 input.                                               |

|                                                                                       | CLCIN2 <sup>(1)</sup>  | TTL/ST                     | _           | Configurable Logic Cell source input.                               |

|                                                                                       | IOCB6                  | TTL/ST                     | _           | Interrupt-on-change input.                                          |

|                                                                                       | ICSPCLK                | ST                         | _           | In-Circuit Serial Programming™ and debugging clock input.           |

Legend:

AN

= Analog input or output

CMOS

= CMOS compatible input or output

OD

= Open-Drain

TTL

= TTL compatible input

ST

= Schmitt Trigger input with CMOS levels

I²C

= Schmitt Trigger input with I²C

HV

= High Voltage

XTAL

= Crystal levels

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 13-1 for details on which PORT pins may be used for this signal.

<sup>2:</sup> All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 13-3.

<sup>3:</sup> This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

<sup>4:</sup> These pins are configured for 1<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the 1<sup>2</sup>C specific or SMBus input buffer thresholds.

TABLE 1-2: PIC16F18854 PINOUT DESCRIPTION (CONTINUED)

| Name                                                                                                | Function               | Input<br>Type              | Output Type | Description                                                                                       |

|-----------------------------------------------------------------------------------------------------|------------------------|----------------------------|-------------|---------------------------------------------------------------------------------------------------|

| RB7/ANB7/DAC1OUT2/T6IN <sup>(1)</sup> /<br>CLCIN3 <sup>(1)</sup> /IOCB7/ICSPDAT                     | RB7                    | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                              |

| CECINS. //IOCB//ICSPDAI                                                                             | ANB7                   | AN                         | _           | ADC Channel B7 input.                                                                             |

|                                                                                                     | DAC1OUT2               | _                          | AN          | Digital-to-Analog Converter output.                                                               |

|                                                                                                     | T6IN <sup>(1)</sup>    | TTL/ST                     | _           | Timer6 external digital clock input.                                                              |

|                                                                                                     | CLCIN3 <sup>(1)</sup>  | TTL/ST                     | _           | Configurable Logic Cell source input.                                                             |

|                                                                                                     | IOCB7                  | TTL/ST                     | _           | Interrupt-on-change input.                                                                        |

|                                                                                                     | ICSPDAT                | ST                         | CMOS        | In-Circuit Serial Programming™ and debugging data input/output.                                   |

| RC0/ANC0/T1CKI(1)/T3CKI <sup>(1)</sup> /T3G <sup>(1)</sup> /<br>SMTWIN1 <sup>(1)</sup> /IOCC0/SOSCO | RC0                    | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                              |

| SMTWINT MOCCO/SOSCO                                                                                 | ANC0                   | AN                         | _           | ADC Channel C0 input.                                                                             |

|                                                                                                     | T1CKI <sup>(1)</sup>   | TTL/ST                     | _           | Timer1 external digital clock input.                                                              |

|                                                                                                     | T3CKI <sup>(1)</sup>   | TTL/ST                     | _           | Timer3 external digital clock input.                                                              |

|                                                                                                     | T3G <sup>(1)</sup>     | TTL/ST                     | _           | Timer3 gate input.                                                                                |

|                                                                                                     | SMTWIN1 <sup>(1)</sup> | TTL/ST                     | _           | Signal Measurement Timer1 (SMT1) input.                                                           |

|                                                                                                     | IOCC0                  | TTL/ST                     | _           | Interrupt-on-change input.                                                                        |

|                                                                                                     | SOSCO                  | _                          | AN          | 32.768 kHz secondary oscillator crystal driver output.                                            |

| RC1/ANC1/SMTSIG1 <sup>(1)</sup> /CCP2 <sup>(1)</sup> /                                              | RC1                    | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                              |

| IOCC1/SOSCI                                                                                         | ANC1                   | AN                         | _           | ADC Channel C1 input.                                                                             |

|                                                                                                     | SMTSIG1 <sup>(1)</sup> | TTL/ST                     | _           | Signal Measurement Timer1 (SMT1) signal input.                                                    |