# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# PIC16F527

## 20-Pin, 8-Bit Flash Microcontroller

#### **Processor Features:**

- · Interrupt Capability

- PIC16F527 Operating Speed:

- DC 20 MHz Crystal oscillator

- DC 200 ns Instruction cycle

- High-Endurance Program and Flash Data Memory Cells:

- 1024 x 12 user execution memory

- 64 x 8 self-writable data memory

- 100,000 write program memory endurance

- 1,000,000 write Flash data memory endurance

- Program and Flash data retention: >40 years

- General Purpose Registers (SRAM):

- 68 x 8 for PIC16F527

- Only 36 Single-Word Instructions to Learn:

- Added RETURN and RETFIE instructions

- Added MOVLB instruction

- All Instructions are Single-Cycle except for Program Branches which are Two-Cycle

- Four-Level Deep Hardware Stack

- Direct, Indirect and Relative Addressing modes for Data and Instructions

#### **Peripheral Features:**

- · Device Features:

- One Input-only pin

- 17 I/Os

- Individual direction control

- High-current source/sink

- 8-Bit Real-Time Clock/Counter (TMR0) with 8-Bit Programmable Prescaler

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two External Pin Connections

- Analog Comparator (CMP):

- Two analog comparators

- Absolute and programmable references

- Analog-to-Digital Converter (ADC):

- 8-bit resolution

- Eight external input channels

- One internal channel to convert comparator

- 0.6V reference input

- Operational Amplifiers (op amps):

- Two operational amplifiers

- Fully-accessible visibility

#### eXtreme Low-Power (XLP) Features

- Sleep mode 50 nA @ 2.0V, typical

- Watchdog Timer (WDT): 500 nA @ 2.0V, typical

#### **Microcontroller Features:**

- Brown-out Reset (BOR)

- Power-on Reset (POR)

- Device Reset Timer (DRT)

- Watchdog Timer (WDT) with a Dedicated RC Oscillator

- Programmable Code Protection (CP)

- Power-Saving Sleep mode with Wake-up on Change Feature

- Selectable Oscillator Options:

- INTOSC: Precision 4 or 8 MHz internal oscillator

- EXTRC: Low-cost external RC oscillator

- LP: Power-saving, low-frequency crystal

- XT: Standard crystal/resonator

- HS: High-speed crystal/resonator

- EC: High-speed external clock

- · Variety of Packaging Options:

- 20-Lead PDIP, SOIC, SSOP, QFN, UQFN

#### **CMOS Technology:**

- Low-Power, High-Speed CMOS Flash Technology

- Fully-Static Design

- Wide Operating Voltage and Temperature Range:

- Industrial: 2.0V to 5.5V

- Extended: 2.0V to 5.5V

- Operating Current:

- 170 uA @ 2V, 4 MHz, typical

- 15 uA @ 2V, 32 kHz, typical

- Standby Current:

- 100 nA @ 2V, typical

#### TABLE 1:PIC16F527 AND PIC16F570 FAMILY TYPES

| Device    | Data Sheet Index | I/O Pins <sup>(1)</sup> | Flash | Data EE (B) | SRAM (B) | 8-Bit ADC<br>Channels | Op Amp | Comparator | 8-Bit Timers | BOR | Stack Levels | Interrupts | 8 MHz Int. Osc. | Interrupt-on-Change<br>Pins | Weak Pull-up Pins | ХГР |

|-----------|------------------|-------------------------|-------|-------------|----------|-----------------------|--------|------------|--------------|-----|--------------|------------|-----------------|-----------------------------|-------------------|-----|

| PIC16F527 | (1)              | 18                      | 1 KW  | 64          | 68       | 8                     | 2      | 2          | 1            | Y   | 4            | Y          | Y               | 4                           | 4                 | Y   |

| PIC16F570 | (2)              | 25                      | 2 KW  | 64          | 132      | 8                     | 2      | 2          | 1            | Υ   | 4            | Y          | Y               | 8                           | 8                 | Υ   |

**Note 1:** One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

1: DS40001652 PIC16F527 Data Sheet, 20-Pin, 8-bit Flash Microcontroller.

2: DS40001684 PIC16F570 Data Sheet, 28-Pin, 8-bit Flash Microcontroller.

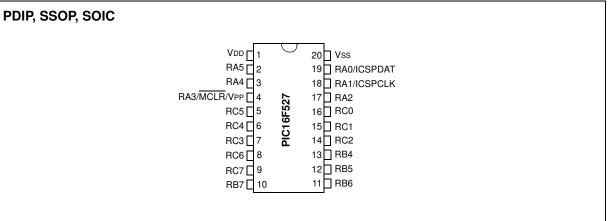

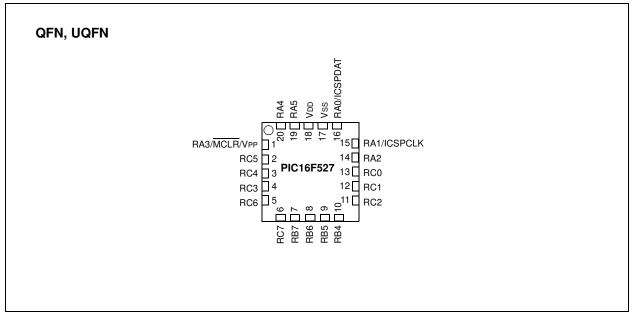

#### FIGURE 1: 20-PIN DIAGRAM FOR PIC16F527

FIGURE 2: 20-PIN DIAGRAM FOR PIC16F527

TABLE 2: 20-PIN ALLOCATION TABLE

|     |                       |                 |        |            | i          |           |        | -      | 1               | 1       | 1           |         |                     |

|-----|-----------------------|-----------------|--------|------------|------------|-----------|--------|--------|-----------------|---------|-------------|---------|---------------------|

| 0/1 | 20-Pin PDIP/SOIC/SSOP | 20-Pin QFN/UQFN | Analog | Oscillator | Comparator | Reference | Timers | Op Amp | Clock Reference | ICSPTM  | Basic       | Pull-up | Interrupt-on-Change |

| RA0 | 19                    | 16              | AN0    |            | C1IN+      | —         |        | —      | —               | ICSPDAT | —           | Υ       | Y                   |

| RA1 | 18                    | 15              | AN1    | _          | C1IN-      | CVREF     | _      | _      | _               | ICSPCLK | —           | Υ       | Y                   |

| RA2 | 17                    | 14              | AN2    |            | C1OUT      | _         | TOCKI  | _      | _               | _       |             |         | _                   |

| RA3 | 4                     | 1               |        |            | —          | _         |        | —      | —               | —       | MCLR<br>VPP | Y       | Y                   |

| RA4 | 3                     | 20              | AN3    | OSC2       | _          | _         |        | _      | CLKOUT          | _       | —           | Υ       | Y                   |

| RA5 | 2                     | 19              | _      | OSC1       | _          | _         |        | _      | CLKIN           | —       | —           |         | —                   |

| RB4 | 13                    | 10              | _      | _          | —          | —         | _      | OP2-   | —               | —       | —           | _       | _                   |

| RB5 | 12                    | 9               |        | _          | —          | —         | —      | OP2+   | —               | —       | —           |         | —                   |

| RB6 | 11                    | 8               |        |            | _          | —         |        | _      | _               | _       | —           | _       | —                   |

| RB7 | 10                    | 7               |        | _          | —          | —         | _      |        | —               | —       |             | —       | —                   |

| RC0 | 16                    | 13              | AN4    | _          | C2IN+      | —         | _      | —      | —               | —       |             | —       | —                   |

| RC1 | 15                    | 12              | AN5    |            | C2IN-      | —         |        |        | —               | —       | —           | —       | —                   |

| RC2 | 14                    | 11              | AN6    | —          | —          | —         | —      | OP2    | —               | —       | —           | —       | —                   |

| RC3 | 7                     | 4               | AN7    | —          | —          | —         | —      | OP1    | —               | —       | —           | _       | —                   |

| RC4 | 6                     | 3               |        | _          | C2OUT      |           |        |        |                 |         | —           | -       | —                   |

| RC5 | 5                     | 2               | —      | —          | —          | —         | —      | —      | —               | —       | —           | —       | —                   |

| RC6 | 8                     | 5               |        |            | —          |           |        | OP1-   |                 | —       | —           | —       | —                   |

| RC7 | 9                     | 6               |        | —          | —          | —         | —      | OP1+   |                 |         | —           | —       | —                   |

| VDD | 1                     | 18              | _      | _          | —          | —         | _      | —      | —               | —       | —           | —       | —                   |

| Vss | 20                    | 17              | _      | —          | —          | —         | —      |        |                 | —       | _           |         | —                   |

#### **Table of Contents**

| 1.0   | General Description                               | 5   |

|-------|---------------------------------------------------|-----|

| 2.0   | General Description<br>PIC16F527 Device Varieties | . 6 |

| 3.0   | Architectural Overview                            | 7   |

| 4.0   | Memory Organization                               | 12  |

| 5.0   | Self-Writable Flash Data Memory Control           | 22  |

| 6.0   | I/O Port<br>Timer0 Module and TMR0 Register       | 26  |

| 7.0   | Timer0 Module and TMR0 Register                   | 31  |

| 8.0   | Special Features of the CPU                       | 36  |

| 9.0   | Analog-to-Digital (A/D) Converter                 | 54  |

| 10.0  | Comparator(s)                                     | 59  |

| 11.0  | Comparator(s)                                     | 64  |

| 12.0  | Operational Amplifier (OPA) Module                | 66  |

| 13.0  | Operational Amplifier (OPA) Module                | 68  |

| 14.0  | Development Support                               | 76  |

| 15.0  | Development Support                               | 80  |

| 16.0  | DC and AC Characteristics Graphs and Charts       | 98  |

| 17.0  | Packaging Information                             | 12  |

| The M | Aicrochip Website                                 | 30  |

| Custo | omer Change Notification Service                  | 30  |

| Custo | omer Support                                      | 30  |

| Produ | omer Change Notification Service                  | 31  |

|       |                                                   |     |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

## 1.0 GENERAL DESCRIPTION

The PIC16F527 device from Microchip Technology is a low-cost, high-performance, 8-bit, fully-static, Flashbased CMOS microcontroller. It employs a RISC architecture with only 36 single-word/single-cycle instructions. All instructions are single cycle except for program branches, which take two cycles. The PIC16F527 device delivers performance an order of magnitude higher than its competitors in the same price category. The 12-bit wide instructions are highly symmetrical, resulting in a typical 2:1 code compression over other 8-bit microcontrollers in its class. The easy-to-use and easy to remember instruction set reduces development time significantly.

The PIC16F527 product is equipped with special features that reduce system cost and power requirements. The Power-on Reset (POR) and Device Reset Timer (DRT) eliminate the need for external Reset circuitry. There are several oscillator configurations to choose from, including INTRC Internal Oscillator mode and the power-saving LP (Low-Power) Oscillator mode. Power-Saving Sleep mode, Watchdog Timer and code protection features improve system cost, power and reliability.

The PIC16F527 device is available in the cost-effective Flash programmable version, which is suitable for production in any volume. The customer can take full advantage of Microchip's price leadership in Flash programmable microcontrollers, while benefiting from the Flash programmable flexibility.

The PIC16F527 product is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a 'C' compiler, a low-cost development programmer and a full-featured programmer. All the tools are supported on IBM<sup>®</sup> PC and compatible machines.

#### 1.1 Applications

The PIC16F527 device fits in applications ranging from personal care appliances and security systems to lowpower remote transmitters/receivers. The Flash technology makes customizing application programs (transmitter codes, appliance settings, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages, for through hole or surface mounting, make these microcontrollers perfect for applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16F527 device very versatile, even in areas where no microcontroller use has been considered before (e.g., timer functions, logic and PLDs in larger systems and coprocessor applications).

PIC16F527

| Clock       | Maximum Frequency of Operation (MHz)        | 20                                 |  |  |  |  |

|-------------|---------------------------------------------|------------------------------------|--|--|--|--|

| Memory      | Flash Program Memory                        | 1024                               |  |  |  |  |

|             | SRAM Data Memory (bytes)                    | 68                                 |  |  |  |  |

|             | Flash Data Memory (bytes)                   | 64                                 |  |  |  |  |

| Peripherals | Timer Module(s)                             | TMR0                               |  |  |  |  |

|             | Wake-up from Sleep on Pin Change            | Yes                                |  |  |  |  |

| eatures     | I/O Pins                                    | 17                                 |  |  |  |  |

|             | Input Pins                                  | 1                                  |  |  |  |  |

|             | Internal Pull-ups                           | Yes                                |  |  |  |  |

|             | In-Circuit Serial Programming <sup>TM</sup> | Yes                                |  |  |  |  |

|             | Number of Instructions                      | 36                                 |  |  |  |  |

|             | Packages                                    | 20-pin PDIP, SOIC, SSOP, QFN, UQFN |  |  |  |  |

|             | Interrupts                                  | Yes                                |  |  |  |  |

#### TABLE 1-1:FEATURES AND MEMORY OF PIC16F527

## 2.0 PIC16F527 DEVICE VARIETIES

A variety of packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in this section. When placing orders, please use the PIC16F527 Product Identification System at the back of this data sheet to specify the correct part number.

#### 2.1 Quick Turn Programming (QTP) Devices

Microchip offers a QTP programming service for factory production orders. This service is made available for users who choose not to program medium-to-high quantity units and whose code patterns have stabilized. The devices are identical to the Flash devices but with all Flash locations and fuse options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

#### 2.2 Serialized Quick Turn Programming<sup>SM</sup> (SQTP<sup>SM</sup>) Devices

Microchip offers a unique programming service, where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number, which can serve as an entry code, password or ID number.

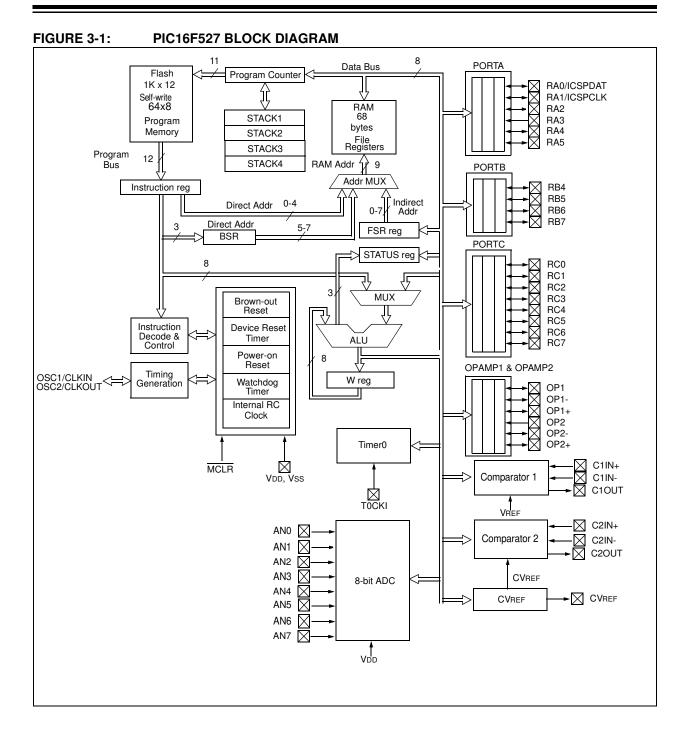

## 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16F527 device can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16F527 device uses a Harvard architecture in which program and data are accessed on separate buses. This improves bandwidth over traditional von Neumann architectures where program and data are fetched on the same bus. Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 12 bits wide, making it possible to have all single-word instructions. A 12-bit wide program memory access bus fetches a 12-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions execute in a single cycle (200 ns @ 20 MHz, 1 µs @ 4 MHz) except for program branches.

Table 3-1 below lists memory supported by the PIC16F527 device.

TABLE 3-1: PIC16F527 MEMORY

| Device    | Program<br>Memory | Data Memory     |                  |  |  |  |

|-----------|-------------------|-----------------|------------------|--|--|--|

| Device    | Flash<br>(words)  | SRAM<br>(bytes) | Flash<br>(bytes) |  |  |  |

| PIC16F527 | 1024              | 68              | 64               |  |  |  |

The PIC16F527 device can directly or indirectly address its register files and data memory. All Special Function Registers (SFR), including the PC, are mapped in the data memory. The PIC16F527 device has a highly orthogonal (symmetrical) instruction set that makes it possible to carry out any operation, on any register, using any Addressing mode. This symmetrical nature and lack of "special optimal situations" make programming with the PIC16F527 device simple, yet efficient. In addition, the learning curve is reduced significantly.

The PIC16F527 device contains an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is eight bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, one operand is typically the W (working) register. The other operand is either a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC) and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBWF and ADDWF instructions for examples.

A simplified block diagram is shown in Figure 3-2, with the corresponding device pins described in Table 3-2.

## PIC16F527

| Name                            | Function | Input Type | Output Type | Description                                                                                                                                                                                                                                                      |

|---------------------------------|----------|------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RA0/AN0/C1IN+/ICSPDAT           | RA0      | TTL        | CMOS        | Bidirectional I/O pin. It can be software<br>programmed for internal weak pull-up and<br>wake-up from Sleep on pin change.                                                                                                                                       |

|                                 | ICSPDAT  | ST         | CMOS        | ICSP™ mode Schmitt Trigger.                                                                                                                                                                                                                                      |

|                                 | C1IN+    | AN         | —           | Comparator 1 input.                                                                                                                                                                                                                                              |

|                                 | AN0      | AN         | —           | ADC channel input.                                                                                                                                                                                                                                               |

| RA1/AN1/C1IN-/CVREF/<br>ICSPCLK | RA1      | TTL        | CMOS        | Bidirectional I/O pin. It can be software<br>programmed for internal weak pull-up and<br>wake-up from Sleep on pin change.                                                                                                                                       |

|                                 | ICSPCLK  | ST         | _           | ICSP™ mode Schmitt Trigger.                                                                                                                                                                                                                                      |

|                                 | C1IN-    | AN         | _           | Comparator 1 input.                                                                                                                                                                                                                                              |

|                                 | CVREF    | _          | AN          | Programmable Voltage Reference output.                                                                                                                                                                                                                           |

|                                 | AN1      | AN         | —           | ADC channel input.                                                                                                                                                                                                                                               |

| RA2/AN2/C1OUT/T0CKI             | RA2      | TTL        | CMOS        | Bidirectional I/O port.                                                                                                                                                                                                                                          |

|                                 | C1OUT    | —          | CMOS        | Comparator 1 output.                                                                                                                                                                                                                                             |

|                                 | AN2      | AN         | _           | ADC channel input.                                                                                                                                                                                                                                               |

|                                 | TOCKI    | ST         | _           | Timer0 Schmitt Trigger input pin.                                                                                                                                                                                                                                |

| RA3/MCLR/VPP                    | RA3      | TTL        | _           | Standard TTL input with weak pull-up.                                                                                                                                                                                                                            |

|                                 | MCLR     | ST         | _           | Master Clear (Reset). When configured as MCLR, this pin is an active-low Reset to the device. Voltage on MCLR/VPP must not exceed VDD during normal device operation or the device will enter Programming mode. Weak pull-up is always on if configured as MCLR. |

|                                 | Vpp      | HV         | _           | Test mode high-voltage pin.                                                                                                                                                                                                                                      |

| RA4/AN3/OSC2/CLKOUT             | RA4      | TTL        | CMOS        | Bidirectional I/O pin. It can be software<br>programmed for internal weak pull-up and<br>wake-up from Sleep on pin change.                                                                                                                                       |

|                                 | OSC2     | —          | XTAL        | Oscillator crystal output. Connections to crystal or resonator in Crystal Oscillator mode (XT, HS and LP modes only, PORTB in other modes).                                                                                                                      |

|                                 | CLKOUT   | —          | CMOS        | EXTRC/INTRC CLKOUT pin (Fosc/4).                                                                                                                                                                                                                                 |

|                                 | AN3      | AN         | —           | ADC channel input.                                                                                                                                                                                                                                               |

| RA5/OSC1/CLKIN                  | RA5      | TTL        | CMOS        | Bidirectional I/O port.                                                                                                                                                                                                                                          |

|                                 | OSC1     | XTAL       | —           | XTAL oscillator input pin.                                                                                                                                                                                                                                       |

|                                 | CLKIN    | ST         | —           | EXTRC Schmitt Trigger input.                                                                                                                                                                                                                                     |

| RB4/OP2-                        | RB4      | TTL        | CMOS        | Bidirectional I/O port.                                                                                                                                                                                                                                          |

|                                 | OP2-     | AN         | —           | Op amp 2 inverting input.                                                                                                                                                                                                                                        |

| RB5/OP2+                        | RB5      | TTL        | CMOS        | Bidirectional I/O port.                                                                                                                                                                                                                                          |

|                                 | OP2+     | AN         | _           | Op amp 2 non-inverting input.                                                                                                                                                                                                                                    |

| RB6                             | RB6      | TTL        | CMOS        | Bidirectional I/O port.                                                                                                                                                                                                                                          |

| RB7                             | RB7      | TTL        | CMOS        | Bidirectional I/O port.                                                                                                                                                                                                                                          |

| RC0/AN4/C2IN+                   | RC0      | ST         | CMOS        | Bidirectional I/O port.                                                                                                                                                                                                                                          |

|                                 | AN4      | AN         | —           | ADC channel input.                                                                                                                                                                                                                                               |

|                                 | C2IN+    | AN         | _           | Comparator 2 input.                                                                                                                                                                                                                                              |

| RC1/AN5/C2IN-                   | RC1      | ST         | CMOS        | Bidirectional I/O port.                                                                                                                                                                                                                                          |

|                                 | AN5      | AN         | _           | ADC channel input.                                                                                                                                                                                                                                               |

|                                 | C2IN-    | AN         | 1           | Comparator 2 input.                                                                                                                                                                                                                                              |

Legend: I = Input, O = Output, I/O = Input/Output, P = Power, — = Not Used, TTL = TTL input, ST = Schmitt Trigger input, HV = High Voltage, AN = Analog Voltage

| Name        | Function | Input Type | Output Type | Description                              |  |  |

|-------------|----------|------------|-------------|------------------------------------------|--|--|

| RC2/AN6/OP2 | RC2      | ST         | CMOS        | Bidirectional I/O port.                  |  |  |

|             | AN6      | AN         | —           | ADC channel input.                       |  |  |

|             | OP2      | —          | AN          | Op amp 2 output.                         |  |  |

| RC3/AN7/OP1 | RC3      | ST         | CMOS        | Bidirectional I/O port.                  |  |  |

|             | AN7      | AN         | —           | ADC channel input.                       |  |  |

|             | OP1      | —          | AN          | Op amp 1 output.                         |  |  |

| RC4/C2OUT   | RC4      | ST         | CMOS        | Bidirectional I/O port.                  |  |  |

|             | C2OUT    | —          | CMOS        | Comparator 2 output.                     |  |  |

| RC5         | RC5      | ST         | CMOS        | Bidirectional I/O port.                  |  |  |

| RC6/OP1-    | RC6      | ST         | CMOS        | Bidirectional I/O port.                  |  |  |

|             | OP1-     | AN         | —           | Op amp 1 inverting input.                |  |  |

| RC7/OP1+    | RC7      | ST         | CMOS        | Bidirectional I/O port.                  |  |  |

|             | OP1+     | AN         | —           | Op amp 1 non-inverting input.            |  |  |

| Vdd         | Vdd      | —          | Р           | Positive supply for logic and I/O pins.  |  |  |

| Vss         | Vss      |            | Р           | Ground reference for logic and I/O pins. |  |  |

#### TABLE 3-2:PIC16F527 PINOUT DESCRIPTION (CONTINUED)

Legend: I = Input, O = Output, I/O = Input/Output, P = Power, — = Not Used, TTL = TTL input, ST = Schmitt Trigger input, HV = High Voltage, AN = Analog Voltage

#### 3.1 **Clocking Scheme/Instruction** Cycle

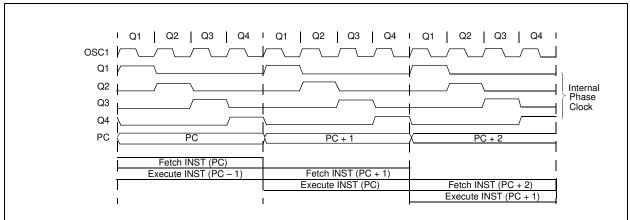

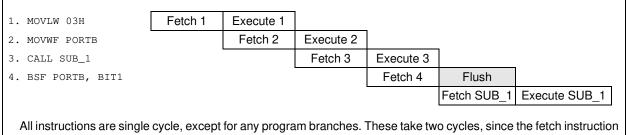

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the PC is incremented every Q1 and the instruction is fetched from program memory and latched into the instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2 and Example 3-1.

#### 3.2 Instruction Flow/Pipelining

An instruction cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the PC to change (e.g., GOTO or an interrupt), then two cycles are required to complete the instruction (see Example 3-1).

A fetch cycle begins with the PC incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### **FIGURE 3-2: CLOCK/INSTRUCTION CYCLE**

#### **INSTRUCTION PIPELINE FLOW** EXAMPLE 3-1:

is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

## 4.0 MEMORY ORGANIZATION

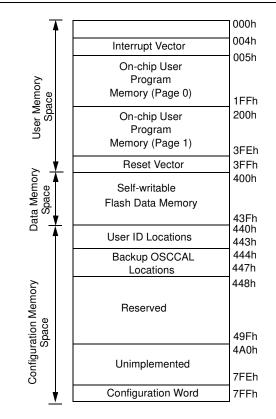

The PIC16F527 memories are organized into program memory and data memory (SRAM). The self-writable portion of the program memory called self-writable Flash data memory is located at addresses 400h-43Fh. All program mode commands that work on the normal Flash memory, work on the Flash data memory. This includes bulk erase, row/column/cycling toggles, Load and Read data commands (Refer to Section 5.0 "Self-Writable Flash Data Memory Control" for more details). For devices with more than 512 bytes of program memory, a paging scheme is used. Program memory pages are accessed using one STATUS register bit. For the PIC16F527, with data memory register files of more than 32 registers, a banking scheme is used. Data memory banks are accessed using the File Select Register (FSR).

#### 4.1 Program Memory Organization for PIC16F527

The PIC16F527 device has an 11-bit Program Counter (PC) capable of addressing a 2K x 12 program memory space. Program memory is partitioned into user memory, data memory and configuration memory spaces.

The user memory space is the on-chip user program memory. As shown in Figure 4-1, it extends from 0x000 to 0x3FF and partitions into pages, including an Interrupt vector at address 0x004 and a Reset vector at address 0x3FF.

The data memory space is the self-writable Flash data memory block and is located at addresses PC = 400h-43Fh. All program mode commands that work on the normal Flash memory, work on the Flash data memory block. This includes bulk erase, Load and Read data commands.

The configuration memory space extends from 0x440 to 0x7FF. Locations from 0x448 through 0x49F are reserved. The user ID locations extend from 0x440 through 0x443. The Backup OSCCAL locations extend from 0x444 through 0x447. The Configuration Word is physically located at 0x7FF.

Refer to *"PIC16F527 Memory Programming Specification"* (DS41640) for more details.

#### FIGURE 4-1: MEMORY MAP

#### 4.2 Data Memory (SRAM and SFRs)

Data memory is composed of registers or bytes of SRAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: Special Function Registers (SFR) and General Purpose Registers (GPR).

The Special Function Registers are registers used by the CPU and peripheral functions for controlling desired operations of the PIC16F527. See Section 4.3 "STATUS Register" for details.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The General Purpose Register file is accessed directly or indirectly. See **Section 4.8** "**Direct and Indirect Addressing**".

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral functions to control the operation of the device (see Section 4.3 "STATUS Register").

The Special Function Registers can be classified into two sets. The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

| BSR<1:0>          | → 00                            | 01                              | 10                                           | 11                              |

|-------------------|---------------------------------|---------------------------------|----------------------------------------------|---------------------------------|

| File Address      | - 00                            | 20h                             | 40h                                          | 60h                             |

|                   | INDF <sup>(1)</sup>             | INDF <sup>(1)</sup>             | INDF <sup>(1)</sup>                          | INDF <sup>(1)</sup>             |

| V 01h             | TMR0                            | EECON                           | TMR0                                         | IW                              |

| 02h               | PCL                             | PCL                             | PCL                                          | PCL                             |

| 03h               | STATUS                          | STATUS                          | STATUS                                       | STATUS                          |

| 04h               | FSR                             | FSR                             | FSR                                          | FSR                             |

| 05h               | OSCCAL                          | EEDATA                          | OSCCAL                                       | INTCON1                         |

| 06h               | PORTA                           | EEADR                           | PORTA                                        | ISTATUS                         |

| 07h               | PORTB                           | CM1CON0                         | PORTB                                        | IFSR                            |

| 08h               | PORTC                           | CM2CON0                         | PORTC                                        | IBSR                            |

| 09h               | ADCON0                          | VRCON                           | ADCON0                                       | OPACON                          |

| 0Ah               | ADRES                           | ANSEL                           | ADRES                                        | ANSEL                           |

| 0Bh               | INTCON0                         | INTCON0                         | INTCON0                                      | INTCON0                         |

| 0Ch               | General<br>Purpose<br>Registers |                                 | 4Ch<br>esses map back to<br>esses in Bank 0. | 6Ch                             |

| 0Fh               | C C                             | 2Fh                             | 4Fh                                          | 6Fh                             |

| 10h               |                                 | 30h                             | 50h                                          | 70h                             |

|                   | General<br>Purpose<br>Registers | General<br>Purpose<br>Registers | General<br>Purpose<br>Registers              | General<br>Purpose<br>Registers |

| 1Fh               |                                 | 3Fh                             | 5Fh                                          | 7Fh                             |

|                   | Bank 0                          | Bank 1                          | Bank 2                                       | Bank 3                          |

| Note 1: Not a phy | vsical register. See            | Section 4.8 "Direc              | t and Indirect Add                           | ressing".                       |

#### FIGURE 4-2: PIC16F527 REGISTER FILE MAP

| Address | Name                  | Bit 7         | Bit 6             | Bit 5      | Bit 4         | Bit 3       | Bit 2       | Bit 1   | Bit 0 | Value on<br>POR/BOR | Value on all<br>other Resets |

|---------|-----------------------|---------------|-------------------|------------|---------------|-------------|-------------|---------|-------|---------------------|------------------------------|

| Bank 0  |                       |               |                   |            |               |             |             |         |       |                     |                              |

| N/A     | W <sup>(2)</sup>      | Working Regi  | ister (W)         |            |               |             |             |         |       | xxxx xxxx           | XXXX XXXX                    |

| N/A     | TRIS                  | I/O Control R | egisters (TRIS    | A, TRISB,  | TRISC)        |             |             |         |       | 1111 1111           | 1111 1111                    |

| N/A     | OPTION                | Contains cont | trol bits to conf | igure Time | r0 and Time   | 0/WDT pre   | escaler     |         |       | 1111 1111           | 1111 1111                    |

| N/A     | BSR <sup>(2)</sup>    | _             | _                 | _          | _             | _           | _           | BSR1    | BSR0  | 000                 | 0uu                          |

| 00h     | INDF                  | Uses contents | s of FSR to ad    | dress data | memory (no    | t a physica | I register) |         |       | XXXX XXXX           | uuuu uuuu                    |

| 01h     | TMR0                  | Timer0 modu   | le Register       |            |               |             |             |         |       | XXXX XXXX           | uuuu uuuu                    |

| 02h     | PCL <sup>(1)</sup>    | Low-order eig | ght bits of PC    |            |               |             |             |         |       | 1111 1111           | 1111 1111                    |

| 03h     | STATUS <sup>(2)</sup> | Reserved      | Reserved          | PA0        | TO            | PD          | Z           | DC      | С     | -001 1xxx           | -00q qqqq                    |

| 04h     | FSR <sup>(2)</sup>    | _             | Indirect data     | memory a   | ddress pointe | er          |             |         |       | 0xxx xxxx           | Ouuu uuuu                    |

| 05h     | OSCCAL                | CAL6          | CAL5              | CAL4       | CAL3          | CAL2        | CAL1        | CAL0    | —     | 1111 111-           | uuuu uuu-                    |

| 06h     | PORTA                 | _             | _                 | RA5        | RA4           | RA3         | RA2         | RA1     | RA0   | xx xxxx             | uu uuuu                      |

| 07h     | PORTB                 | RB7           | RB6               | RB5        | RB4           | _           | _           | _       | _     | xxxx                | uuuu                         |

| 08h     | PORTC                 | RC7           | RC6               | RC5        | RC4           | RC3         | RC2         | RC1     | RC0   | xxxx xxxx           | uuuu uuuu                    |

| 09h     | ADCON0                | ADCS1         | ADCS0             | CHS3       | CHS2          | CHS1        | CHS0        | GO/DONE | ADON  | 1111 1100           | 1111 1100                    |

| 0Ah     | ADRES                 | ADC Convers   | sion Result       | •          | •             |             |             |         |       | XXXX XXXX           | uuuu uuuu                    |

| 0Bh     | INTCON0               | ADIF          | CWIF              | T0IF       | RAIF          | _           | _           | —       | GIE   | 00000               | 00000                        |

| Bank 1  |                       |               |                   |            |               |             |             |         |       |                     |                              |

| N/A     | W <sup>(2)</sup>      | Working Regi  | ister (W)         |            |               |             |             |         |       | XXXX XXXX           | XXXX XXXX                    |

| N/A     | TRIS                  | I/O Control R | egisters (TRIS    | A, TRISB,  | TRISC)        |             |             |         |       | 1111 1111           | 1111 1111                    |

| N/A     | OPTION                | Contains cont | trol bits to conf | igure Time | r0 and Time   | 0/WDT pre   | escaler     |         |       | 1111 1111           | 1111 1111                    |

| N/A     | BSR <sup>(2)</sup>    | _             | _                 | —          | —             | —           | _           | BSR1    | BSR0  | 000                 | 0uu                          |

| 20h     | INDF                  | Uses contents | s of FSR to ad    | dress data | memory (no    | t a physica | l register) |         |       | XXXX XXXX           | uuuu uuuu                    |

| 21h     | EECON                 | _             | _                 |            | FREE          | WRERR       | WREN        | WR      | RD    | 0 0000              | 0 0000                       |

| 22h     | PCL <sup>(1)</sup>    | Low-order eig | ght bits of PC    |            |               |             |             |         |       | 1111 1111           | 1111 1111                    |

| 23h     | STATUS <sup>(2)</sup> | Reserved      | Reserved          | PA0        | TO            | PD          | Z           | DC      | С     | -001 1xxx           | -00q qqqq                    |

| 24h     | FSR <sup>(2)</sup>    | _             | Indirect data     | memory a   | ddress pointe | er          |             |         |       | 0xxx xxxx           | Ouuu uuuu                    |

| 25h     | EEDATA                | Self Read/Wr  | ite Data          |            |               |             |             |         |       | XXXX XXXX           | uuuu uuuu                    |

| 26h     | EEADR                 | —             | _                 | Self Read  | d/Write Addre | ess         |             |         |       | xx xxxx             | uu uuuu                      |

| 27h     | CM1CON0               | C1OUT         | C10UTEN           | C1POL      | C1T0CS        | C1ON        | C1NREF      | C1PREF  | C1WU  | 1111 1111           | quuu uuuu                    |

| 28h     | CM2CON0               | C2OUT         | C2OUTEN           | C2POL      | C2PREF2       | C2ON        | C2NREF      | C2PREF1 | C2WU  | 1111 1111           | quuu uuuu                    |

| 29h     | VRCON                 | VREN          | VROE              | VRR        | —             | VR3         | VR2         | VR1     | VR0   | 001- 0000           | uuu- uuuu                    |

| 2Ah     | ANSEL                 | ANS7          | ANS6              | ANS5       | ANS4          | ANS3        | ANS2        | ANS1    | ANS0  | 1111 1111           | 1111 1111                    |

|         | INTCON0               | ADIF          | CWIF              | T0IF       | RAIF          |             |             |         | GIE   | 00000               | 00000                        |

#### TABLE 4-1: SPECIAL FUNCTION REGISTER SUMMARY

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0' (if applicable), q = value depends on condition.

Shaded cells = unimplemented or unused

Note 1: The upper byte of the Program Counter is not directly accessible. See Section 4.6 "Program Counter" for an explanation of how to access these bits.

Registers are implemented as two physical registers. When executing from within an ISR, a secondary register is used at the same logical location. Both registers are persistent. See Section 8.11 "Interrupts".

3: These registers show the contents of the registers in the other context: ISR or main line code. See Section 8.11 "Interrupts".

| Address | Name                   | Bit 7         | Bit 6             | Bit 5      | Bit 4         | Bit 3       | Bit 2        | Bit 1   | Bit 0  | Value on<br>POR/BOR | Value on all<br>other Resets |

|---------|------------------------|---------------|-------------------|------------|---------------|-------------|--------------|---------|--------|---------------------|------------------------------|

| Bank 2  |                        |               |                   |            |               |             |              |         |        |                     |                              |

| N/A     | W <sup>(2)</sup>       | Working Regi  | ister (W)         |            | XXXX XXXX     | XXXX XXXX   |              |         |        |                     |                              |

| N/A     | TRIS                   | I/O Control R | egisters (TRIS    | A, TRISB,  | TRISC)        |             |              |         |        | 1111 1111           | 1111 1111                    |

| N/A     | OPTION                 | Contains con  | trol bits to conf | igure Time | r0 and Time   | r0/WDT pre  | escaler      |         |        | 1111 1111           | 1111 1111                    |

| N/A     | BSR <sup>(2)</sup>     | —             | —                 | _          | -             | -           |              | BSR1    | BSR0   | 000                 | 0uu                          |

| 40h     | INDF                   | Uses content  | s of FSR to add   | dress data | memory (no    | t a physica | al register) |         |        | XXXX XXXX           | uuuu uuuu                    |

| 41h     | TMR0                   | Timer0 modu   | le Register       |            |               |             |              |         |        | XXXX XXXX           | uuuu uuuu                    |

| 42h     | PCL <sup>(1)</sup>     | Low-order eig | ght bits of PC    |            |               |             |              |         |        | 1111 1111           | 1111 1111                    |

| 43h     | STATUS <sup>(2)</sup>  | Reserved      | Reserved          | PA0        | TO            | PD          | z            | DC      | С      | -001 1xxx           | -00q qqqq                    |

| 44h     | FSR <sup>(2)</sup>     | _             | Indirect data     | memory ad  | ddress pointe | er          |              | •       |        | 0xxx xxxx           | Ouuu uuuu                    |

| 45h     | OSCCAL                 | CAL6          | CAL5              | CAL4       | CAL3          | CAL2        | CAL1         | CAL0    | _      | 1111 111-           | uuuu uuu-                    |

| 46h     | PORTA                  | _             | _                 | RA5        | RA4           | RA3         | RA2          | RA1     | RA0    | xx xxxx             | uu uuuu                      |

| 47h     | PORTB                  | RB7           | RB6               | RB5        | RB4           | _           | _            | _       | _      | xxxx                | uuuu                         |

| 48h     | PORTC                  | RC7           | RC6               | RC5        | RC4           | RC3         | RC2          | RC1     | RC0    | XXXX XXXX           | uuuu uuuu                    |

| 49h     | ADCON0                 | ADCS1         | ADCS0             | CHS3       | CHS2          | CHS1        | CHS0         | GO/DONE | ADON   | 1111 1100           | 1111 1100                    |

| 4Ah     | ADRES                  | ADC Convers   | sion Result       |            |               |             |              |         |        | xxxx xxxx           | uuuu uuuu                    |

| 4Bh     | INTCON0                | ADIF          | CWIF              | T0IF       | RAIF          | —           | —            | —       | GIE    | 00000               | 00000                        |

| Bank 3  |                        |               |                   |            |               |             |              |         |        |                     |                              |

| N/A     | W <sup>(2)</sup>       | Working Regi  | ister (W)         |            |               |             |              |         |        | xxxx xxxx           | XXXX XXXX                    |

| N/A     | TRIS                   | I/O Control R | egisters (TRIS    | A, TRISB,  | TRISC)        |             |              |         |        | 1111 1111           | 1111 1111                    |

| N/A     | OPTION                 | Contains con  | trol bits to conf | igure Time | r0 and Time   | r0/WDT pre  | escaler      |         |        | 1111 1111           | 1111 1111                    |

| N/A     | BSR <sup>(2)</sup>     | _             | —                 | _          | —             | _           |              | BSR1    | BSR0   | 000                 | 0uu                          |

| 60h     | INDF                   | Uses content  | s of FSR to add   | dress data | memory (no    | t a physica | al register) |         |        | xxxx xxxx           | uuuu uuuu                    |

| 61h     | IW <sup>(3)</sup>      | Interrupt Wor | king Register. (  | Addresse   | d also as W ı | egister wh  | en within IS | SR)     |        | XXXX XXXX           | XXXX XXXX                    |

| 62h     | PCL <sup>(1)</sup>     | Low-order eig | ght bits of PC    |            |               |             |              |         |        | 1111 1111           | 1111 1111                    |

| 63h     | STATUS <sup>(2)</sup>  | Reserved      | Reserved          | PA0        | TO            | PD          | Z            | DC      | С      | -001 1xxx           | -00q qqqq                    |

| 64h     | FSR <sup>(2)</sup>     | _             | Indirect data     | memory a   | ddress pointe | er          |              |         |        | 0xxx xxxx           | Ouuu uuuu                    |

| 65h     | INTCON1                | ADIE          | CWIE              | T0IE       | RAIE          | —           | —            | —       | WUR    | 00000               | 00000                        |

| 66h     | ISTATUS <sup>(3)</sup> | Reserved      | Reserved          | PA0        | TO            | PD          | Z            | DC      | С      | -xxx xxxx           | -00q qqqq                    |

| 67h     | IFSR <sup>(3)</sup>    | _             | Indirect data     | memory a   | ddress pointe | er          |              | •       | •      | 0xxx xxxx           | Ouuu uuuu                    |

| 68h     | IBSR <sup>(3)</sup>    | _             | _                 | _          | _             | _           | _            | BSR1    | BSR0   | 0xx                 | 0uu                          |

| 69h     | OPACON                 | _             | _                 | —          | —             | —           | —            | OPA2ON  | OPA1ON | 00                  | 00                           |

| 6Bh     | INTCON0                | ADIF          | CWIF              | T0IF       | RAIF          | —           | —            | —       | GIE    | 00000               | 00000                        |

| 1       |                        | n u = unchano |                   |            |               |             | · ·          |         |        | 1                   | 1                            |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0' (if applicable), q = value depends on condition.

Shaded cells = unimplemented or unused

Note 1: The upper byte of the Program Counter is not directly accessible. See Section 4.6 "Program Counter" for an explanation of how to access these bits.

2: Registers are implemented as two physical registers. When executing from within an ISR, a secondary register is used at the same logical location. Both registers are persistent. See Section 8.11 "Interrupts".

3: These registers show the contents of the registers in the other context: ISR or main line code. See Section 8.11 "Interrupts".

#### 4.3 STATUS Register

This register contains the arithmetic status of the ALU, the Reset status and the page preselect bit.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS, will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

Therefore, it is recommended that only BCF, BSF and MOVWF instructions be used to alter the STATUS register. These instructions do not affect the Z, DC or C bits from the STATUS register. For other instructions which do affect Status bits, see Section 13.0 "Instruction Set Summary".

#### REGISTER 4-1: STATUS: STATUS REGISTER

| R-0           | R-0                                                           | R/W-0                                           | R-1            | R-1              | R/W-x             | R/W-x           | R/W-x |

|---------------|---------------------------------------------------------------|-------------------------------------------------|----------------|------------------|-------------------|-----------------|-------|

| Reserved      | Reserved                                                      | PA0                                             | TO             | PD               | Z                 | DC              | С     |

| bit 7         |                                                               |                                                 |                |                  |                   |                 | bit 0 |

|               |                                                               |                                                 |                |                  |                   |                 |       |

| Legend:       |                                                               |                                                 |                |                  |                   |                 |       |

| R = Readable  | e bit                                                         | W = Writable k                                  | bit            |                  | mented bit, rea   | d as '0'        |       |

| -n = Value at | POR                                                           | '1' = Bit is set                                |                | '0' = Bit is cle | eared             | x = Bit is unkr | nown  |

|               |                                                               |                                                 |                |                  |                   |                 |       |

| bit 7-6       | Reserved: Re                                                  |                                                 |                |                  |                   |                 |       |

| bit 5         |                                                               | n Page Preseled                                 | ct bit         |                  |                   |                 |       |

|               | 1 = Page 1 (2<br>0 = Page 0 (0                                |                                                 |                |                  |                   |                 |       |

| bit 4         | TO: Time-Out                                                  | ,                                               |                |                  |                   |                 |       |

|               |                                                               | er-up, CLRWDT                                   | instruction, o | or SLEEP instru  | iction            |                 |       |

|               | 0 = A WDT tir                                                 | me-out occurred                                 | k              |                  |                   |                 |       |

| bit 3         | PD: Power-Do                                                  |                                                 |                |                  |                   |                 |       |

|               |                                                               | er-up or by the<br>tion of the SLEE             |                |                  |                   |                 |       |

| bit 2         | <b>Z</b> : Zero bit                                           |                                                 |                |                  |                   |                 |       |

| Dit 2         |                                                               | t of an arithmeti                               | c or logic op  | eration is zero  |                   |                 |       |

|               | 0 = The result                                                | t of an arithmeti                               | c or logic op  | eration is not z | ero               |                 |       |

| bit 1         | DC: Digit carry/borrow bit (for ADDWF and SUBWF instructions) |                                                 |                |                  |                   |                 |       |

|               |                                                               | om the 4th low-                                 |                |                  |                   |                 |       |

|               | 0 = A carry fro                                               | om the 4th low-                                 | order bit of t | he result did no | ot occur          |                 |       |

|               |                                                               | from the 4th low<br>from the 4th low            |                |                  |                   |                 |       |

| bit 0         | •                                                             | <b>ow bit (for</b> ADDW<br>WF: RRF <b>or</b> RI |                | nd RRF, RLF ins  | tructions)        |                 |       |

|               | 1 = A  carry of                                               |                                                 | porrow did n   |                  | bit with LSb or I | MSb, respective | ły    |

#### 4.4 **OPTION Register**

The OPTION register is a 8-bit wide, write-only register, which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the <code>OPTION</code> instruction, the contents of the W register will be transferred to the <code>OPTION</code> register. A Reset sets the <code>OPTION</code> <7:0> bits.

# **Note:** If TRIS bit is set to '0', the wake-up on change and pull-up functions are disabled for that pin (i.e., note that TRIS overrides Option control of RAPU and RAWU).

#### REGISTER 4-2: OPTION: OPTION REGISTER

| W-1                 | W-1  | W-1                 | W-1  | W-1 | W-1 | W-1 | W-1   |

|---------------------|------|---------------------|------|-----|-----|-----|-------|

| RAWU <sup>(2)</sup> | RAPU | T0CS <sup>(1)</sup> | T0SE | PSA | PS2 | PS1 | PS0   |

| bit 7               | •    |                     |      |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | <b>RAWU:</b> Enable PORTA Interrupt Flag on Pin Change bit <sup>(2)</sup><br>1 = Disabled<br>0 = Enabled                                                   |                                   |                                  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------|--|--|--|

| bit 6   | <b>RAPU:</b> Enable PORTA Weak Pull-Ups bit<br>1 = Disabled<br>0 = Enabled                                                                                 |                                   |                                  |  |  |  |

| bit 5   | <b>TOCS:</b> Timer0 Clock Source Select bit <sup>(1)</sup><br>1 = Transition on TOCKI pin<br>0 = Internal instruction cycle clock (CLKOUT)                 |                                   |                                  |  |  |  |

| bit 4   | <b>TOSE:</b> Timer0 Source Edge Select bit<br>1 = Increment on high-to-low transition on T0CKI pin<br>0 = Increment on low-to-high transition on T0CKI pin |                                   |                                  |  |  |  |

| bit 3   | <ul> <li>PSA: Prescaler Assignment bit</li> <li>1 = Prescaler assigned to the WDT</li> <li>0 = Prescaler assigned to Timer0</li> </ul>                     |                                   |                                  |  |  |  |

| bit 2-0 | PS<2:0>: Prescaler                                                                                                                                         | Rate Select b                     | pits                             |  |  |  |

|         | Bit Value                                                                                                                                                  | Timer0 Rate                       | WDT Rate                         |  |  |  |

|         | 000<br>001<br>010<br>011<br>100                                                                                                                            | 1:2<br>1:4<br>1:8<br>1:16<br>1:32 | 1:1<br>1:2<br>1:4<br>1:8<br>1:16 |  |  |  |

|         | 100                                                                                                                                                        | 1:64                              | 1:32                             |  |  |  |

**Note 1:** If the TOCS bit is set to '1', it will override the TRIS function on the TOCKI pin.

1:128

1:256

110

111

2: The RAWU bit of the OPTION register must be cleared to enable the RAIF function in the INTCON0 register.

1:64

1 : 128

#### 4.5 OSCCAL Register

The Oscillator Calibration (OSCCAL) register is used to calibrate the 8 MHz internal oscillator macro. It contains seven bits of calibration that uses a two's complement scheme for controlling the oscillator speed. See Register 4-3 for details.

#### REGISTER 4-3: OSCCAL: OSCILLATOR CALIBRATION REGISTER

| R/W-1 | U-0   |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CAL6  | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | —     |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

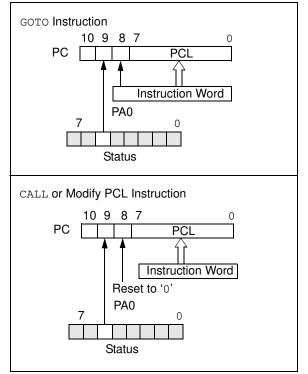

#### 4.6 Program Counter

As a program instruction is executed, the Program Counter (PC) will contain the address of the next program instruction to be executed. The PC value is increased by one every instruction cycle, unless an instruction changes the PC.

For a GOTO instruction, bits <8:0> of the PC are provided by the GOTO instruction word. The Program Counter (PCL) is mapped to PC<7:0>. Bit 5 of the STATUS register provides page information to bit 9 of the PC (see Figure 4-3).

For a CALL instruction, or any instruction where the PCL is the destination, bits <7:0> of the PC again are provided by the instruction word. However, PC<8> does not come from the instruction word, but is always cleared (see Figure 4-3).

Instructions where the PCL is the destination, or modify PCL instructions, include MOVWF PCL, ADDWF PCL and BSF PCL, 5.

| Note: | Because bit 8 of the PC is cleared in the CALL instruction or any modify PCL                                                  |

|-------|-------------------------------------------------------------------------------------------------------------------------------|

|       | instruction, all subroutine calls or com-<br>puted jumps are limited to the first 256<br>locations of any program memory page |

|       | (512 words long).                                                                                                             |

#### FIGURE 4-3: LOADING OF PC BRANCH INSTRUCTIONS

#### 4.6.1 EFFECTS OF RESET

The PC is set upon a Reset, which means that the PC addresses the last location in the last page (i.e., the oscillator calibration instruction). After executing MOVLW XX, the PC will roll over to location 00h and begin executing user code.

The STATUS register page preselect bits are cleared upon a Reset, which means that page 0 is pre-selected.

Therefore, upon a Reset, a GOTO instruction will automatically cause the program to jump to page 0 until the value of the page bits is altered.

#### 4.7 Stack

The PIC16F527 device has a 4-deep, 12-bit wide hardware PUSH/POP stack.

A CALL instruction or an interrupt will PUSH the current PC value, incremented by one, into Stack Level 1. If there was a previous value in the Stack 1 location, it will be pushed into the Stack 2 location. This process will be continued throughout the remaining stack locations populated with values. If more than four sequential CALLs are executed, only the most recent four return addresses are stored.

A RETLW, RETURN or RETFIE instruction will POP the contents of Stack Level 1 into the PC. If there was a previous value in the Stack 2 location, it will be copied into the Stack Level 1 location. This process will be continued throughout the remaining stack locations populated with values. If more than four sequential RETLWS are executed, the stack will be filled with the address previously stored in Stack Level 4. Note that the W register will be loaded with the literal value specified in the instruction. This is particularly useful for the implementation of data look-up tables within the program memory.

Note 1: There are no Status bits to indicate Stack Overflows or Stack Underflow conditions.

2: There are no instruction mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETFIE and RETLW instructions.

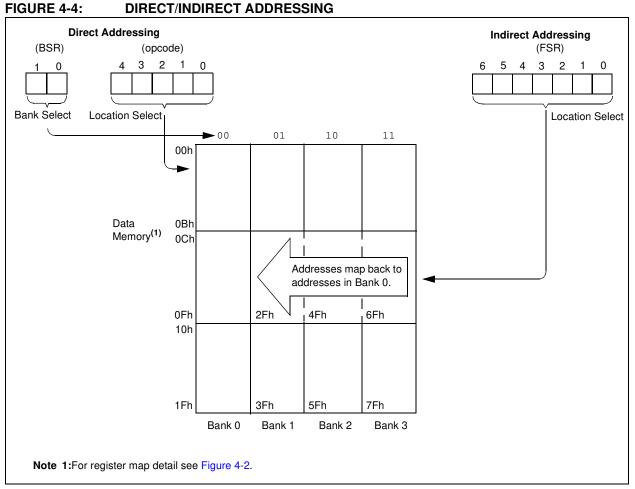

#### 4.8 Direct and Indirect Addressing

#### 4.8.1 DIRECT DATA ADDRESSING: BSR REGISTER

Traditional data memory addressing is performed in the Direct Addressing mode. In Direct Addressing, the Bank Select Register bits BSR<1:0>, in the new BSR register, are used to select the data memory bank. The address location within that bank comes directly from the opcode being executed.

BSR<1:0> are the bank select bits and are used to select the bank to be addressed (00 = Bank 0, 01 = Bank 1, 10 = Bank 2, 11 = Bank 3).

A new instruction supports the addition of the BSR register, called the MOVLB instruction. See Section 13.0 "Instruction Set Summary" for more information.

#### 4.8.2 INDIRECT DATA ADDRESSING: INDF AND FSR REGISTERS

The INDF Register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR Register (FSR is a *pointer*). This is indirect addressing.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF Register indirectly results in a no-operation (although Status bits may be affected).

The FSR is an 8-bit wide register. It is used in conjunction with the INDF Register to indirectly address the data memory area.

The FSR<6:0> bits are used to select data memory addresses 00h to 1Fh.

FSR<7> is unimplemented and read as '0'.

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 4-1.

#### EXAMPLE 4-1: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT   | MOVLW<br>MOVWF<br>CLRF<br>INCF | 0x10<br>FSR<br>INDF<br>FSR,F | <pre>;initialize pointer ;to RAM ;clear INDF ;register ;inc pointer</pre> |

|--------|--------------------------------|------------------------------|---------------------------------------------------------------------------|

|        | BTFSC<br>GOTO                  | FSR <b>,</b> 4<br>NEXT       | ;all done?<br>;NO, clear next                                             |

| CONTIN | IUE                            |                              |                                                                           |

|        | :                              |                              | ;YES, continue                                                            |