# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# PIC16F684 Data Sheet

14-Pin, Flash-Based 8-Bit CMOS Microcontrollers with nanoWatt Technology

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC, and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Linear Active Thermistor, Migratable Memory, MXDEV, MXLAB, PS logo, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2007, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and water fabrication facilities in Chandler and Tempe, Arizona, Gresham, Oregon and Mountain View, California. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# **PIC16F684**

# 14-Pin Flash-Based, 8-Bit CMOS Microcontrollers with nanoWatt Technology

#### **High-Performance RISC CPU:**

- · Only 35 instructions to learn:

- All single-cycle instructions except branches

- Operating speed:

- DC 20 MHz oscillator/clock input

- DC 200 ns instruction cycle

- · Interrupt capability

- 8-level deep hardware stack

- Direct, Indirect and Relative Addressing modes

#### **Special Microcontroller Features:**

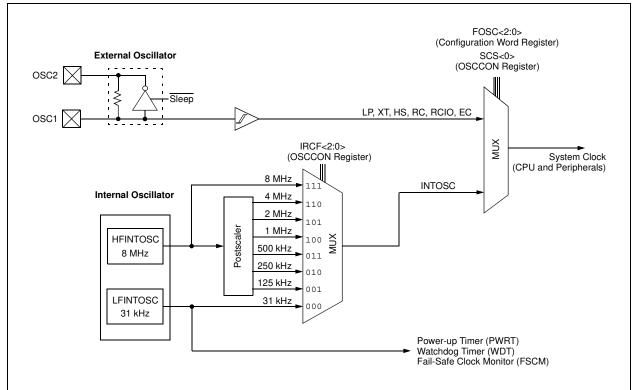

- Precision Internal Oscillator:

- Factory calibrated to ±1%, typical

- Software selectable frequency range of

- 8 MHz to 125 kHz

- Software tunable

- Two-Speed Start-up mode

- Crystal fail detect for critical applications

- Clock mode switching during operation for power savings

- · Software Selectable 31 kHz Internal Oscillator

- · Power-Saving Sleep mode

- Wide operating voltage range (2.0V-5.5V)

- · Industrial and Extended Temperature range

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR) with software control option

- Enhanced low-current Watchdog Timer (WDT) with on-chip oscillator (software selectable nominal 268 seconds with full prescaler) with software enable

- Multiplexed Master Clear with pull-up/input pin

- · Programmable code protection

- High Endurance Flash/EEPROM cell:

- 100,000 write Flash endurance

- 1,000,000 write EEPROM endurance

- Flash/Data EEPROM retention: > 40 years

#### Low-Power Features:

- · Standby Current:

- 50 nA @ 2.0V, typical

- Operating Current:

- 11 μA @ 32 kHz, 2.0V, typical

- 220 μA @ 4 MHz, 2.0V, typical

- Watchdog Timer Current:

- 1 μA @ 2.0V, typical

#### **Peripheral Features:**

- 12 I/O pins with individual direction control:

- High current source/sink for direct LED drive

- Interrupt-on-change pin

- Individually programmable weak pull-ups

- Ultra Low-Power Wake-Up (ULPWU)

- Analog Comparator module with:

- Two analog comparators

- Programmable on-chip voltage reference (CVREF) module (% of VDD)

- Comparator inputs and outputs externally accessible

- A/D Converter:

- 10-bit resolution and 8 channels

- Timer0: 8-bit timer/counter with 8-bit programmable prescaler

- Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Timer1 Gate (count enable)

- Option to use OSC1 and OSC2 in LP mode as Timer1 oscillator if INTOSC mode selected

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- Enhanced Capture, Compare, PWM module:

- 16-bit Capture, max resolution 12.5 ns

- Compare, max resolution 200 ns

- 10-bit PWM with 1, 2 or 4 output channels, programmable "dead time", max frequency 20 kHz

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via two pins

| Device    | Program<br>Memory | Data Memory     |                   | 1/0 | 10-bit A/D | Comparators | Timers   |  |

|-----------|-------------------|-----------------|-------------------|-----|------------|-------------|----------|--|

| Device    | Flash<br>(words)  | SRAM<br>(bytes) | EEPROM<br>(bytes) | 1/0 | (ch)       | Comparators | 8/16-bit |  |

| PIC16F684 | 2048              | 128             | 256               | 12  | 8          | 2           | 2/1      |  |

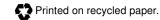

# 14-Pin Diagram (PDIP, SOIC, TSSOP)

TABLE 1: DUAL IN-LINE PIN SUMMARY

| I/O                | Pin | Analog   | Comparators | Timer | ССР      | Interrupts | Pull-ups         | Basic         |

|--------------------|-----|----------|-------------|-------|----------|------------|------------------|---------------|

| RA0                | 13  | AN0      | C1IN+       | —     | _        | IOC        | Y                | ICSPDAT/ULPWU |

| RA1                | 12  | AN1/VREF | C1IN-       | —     | _        | IOC        | Y                | ICSPCLK       |

| RA2                | 11  | AN2      | C1OUT       | T0CKI | _        | INT/IOC    | Y                | —             |

| RA3 <sup>(1)</sup> | 4   | _        | _           | _     | _        | IOC        | Y <sup>(2)</sup> | MCLR/Vpp      |

| RA4                | 3   | AN3      | —           | T1G   | —        | IOC        | Y                | OSC2/CLKOUT   |

| RA5                | 2   |          | —           | T1CKI | _        | IOC        | Y                | OSC1/CLKIN    |

| RC0                | 10  | AN4      | C2IN+       | _     | _        | —          | —                | —             |

| RC1                | 9   | AN5      | C2IN-       | —     | _        | —          | —                | —             |

| RC2                | 8   | AN6      | —           | _     | P1D      | —          | —                | —             |

| RC3                | 7   | AN7      | —           | _     | P1C      | —          | —                | —             |

| RC4                | 6   | _        | C2OUT       |       | P1B      | —          | —                | —             |

| RC5                | 5   | _        | —           | _     | CCP1/P1A | _          | —                | —             |

| _                  | 1   | _        | —           |       |          | _          | —                | Vdd           |

| —                  | 14  | _        | —           |       |          | _          | —                | Vss           |

Note 1: Input only.

2: Only when pin is configured for external MCLR.

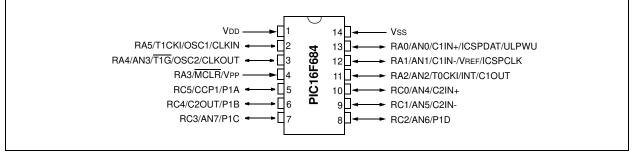

#### 16-Pin Diagram (QFN)

#### TABLE 2: QFN PIN SUMMARY

| I/O                | Pin | Analog   | Comparators | Timers       | ССР      | Interrupts | Pull-ups         | Basic         |

|--------------------|-----|----------|-------------|--------------|----------|------------|------------------|---------------|

| RA0                | 12  | AN0      | C1IN+       |              | _        | IOC        | Y                | ICSPDAT/ULPWU |

| RA1                | 11  | AN1/VREF | C1IN-       | —            | _        | IOC        | Y                | ICSPCLK       |

| RA2                | 10  | AN2      | C1OUT       | <b>T0CKI</b> | _        | INT/IOC    | Y                | —             |

| RA3 <sup>(1)</sup> | 3   | _        | —           | _            |          | IOC        | Y <sup>(2)</sup> | MCLR/VPP      |

| RA4                | 2   | AN3      | —           | T1G          | _        | IOC        | Y                | OSC2/CLKOUT   |

| RA5                | 1   |          | —           | T1CKI        | _        | IOC        | Y                | OSC1/CLKIN    |

| RC0                | 9   | AN4      | C2IN+       | —            | _        | _          | —                | —             |

| RC1                | 8   | AN5      | C2IN-       | —            | _        |            | —                | —             |

| RC2                | 7   | AN6      | —           |              | P1D      |            | —                | —             |

| RC3                | 6   | AN7      | —           | —            | P1C      |            | _                | —             |

| RC4                | 5   | —        | C2OUT       | —            | P1B      | -          | —                | —             |

| RC5                | 4   |          | —           | _            | CCP1/P1A |            | —                | —             |

|                    | 16  | _        | —           |              | _        | _          | —                | Vdd           |

| —                  | 13  | _        |             | _            | _        | _          |                  | Vss           |

Note 1: Input only.

2: Only when pin is configured for external MCLR.

#### **Table of Contents**

| 1.0   | Device Overview                                                        | 5    |

|-------|------------------------------------------------------------------------|------|

| 2.0   | Memory Organization                                                    | 7    |

| 3.0   | Oscillator Module (With Fail-Safe Clock Monitor)                       | . 19 |

| 4.0   | I/O Ports                                                              | . 31 |

| 5.0   | Timer0 Module                                                          |      |

| 6.0   | Timer1 Module with Gate Control                                        |      |

| 7.0   | Timer2 Module                                                          | . 53 |

| 8.0   | Comparator Module                                                      | . 55 |

| 9.0   | Analog-to-Digital Converter (ADC) Module                               | . 65 |

| 10.0  | Data EEPROM Memory                                                     |      |

| 11.0  | Enhanced Capture/Compare/PWM (With Auto-Shutdown and Dead Band) Module |      |

| 12.0  | Special Features of the CPU                                            |      |

| 13.0  | Instruction Set Summary                                                |      |

| 14.0  | Development Support                                                    |      |

| 15.0  | Electrical Specifications                                              |      |

|       | DC and AC Characteristics Graphs and Tables                            |      |

|       | Packaging Information                                                  |      |

|       | ndix A: Data Sheet Revision History                                    |      |

|       | ndix B: Migrating from other PIC® Devices                              |      |

|       | · · · · · · · · · · · · · · · · · · ·                                  |      |

|       | licrochip Web Site                                                     |      |

|       | mer Change Notification Service                                        |      |

|       | mer Support                                                            |      |

|       | er Response                                                            |      |

| Produ | ct Identification System                                               | 189  |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### 1.0 **DEVICE OVERVIEW**

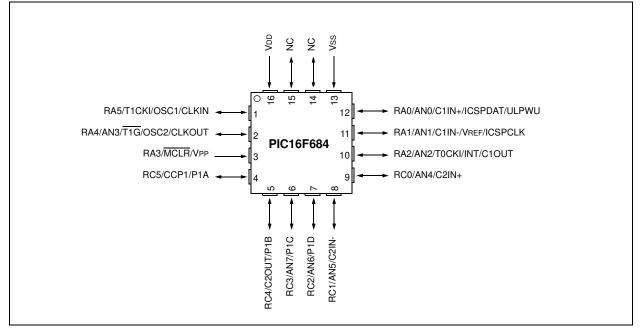

The PIC16F684 is covered by this data sheet. It is available in 14-pin PDIP, SOIC, TSSOP and 16-pin QFN packages. Figure 1-1 shows a block diagram of the PIC16F684 device. Table 1-1 shows the pinout description.

FIGURE 1-1: PIC16F684 BLOCK DIAGRAM

#### TABLE 1-1: PIC16F684 PINOUT DESCRIPTION

| Name                                | Function | Input<br>Type | Output<br>Type | Description                                          |

|-------------------------------------|----------|---------------|----------------|------------------------------------------------------|

| RA0/AN0/C1IN+/ICSPDAT/ULPWU         | RA0      | TTL           | CMOS           | PORTA I/O with prog. pull-up and interrupt-on-change |

|                                     | AN0      | AN            | —              | A/D Channel 0 input                                  |

|                                     | C1IN+    | AN            |                | Comparator 1 non-inverting input                     |

|                                     | ICSPDAT  | TTL           | CMOS           | Serial Programming Data I/O                          |

|                                     | ULPWU    | AN            | —              | Ultra Low-Power Wake-Up input                        |

| RA1/AN1/C1IN-/VREF/ICSPCLK          | RA1      | TTL           | CMOS           | PORTA I/O with prog. pull-up and interrupt-on-chang  |

|                                     | AN1      | AN            | _              | A/D Channel 1 input                                  |

|                                     | C1IN-    | AN            | —              | Comparator 1 inverting input                         |

|                                     | VREF     | AN            | —              | External Voltage Reference for A/D                   |

|                                     | ICSPCLK  | ST            |                | Serial Programming Clock                             |

| RA2/AN2/T0CKI/INT/C1OUT             | RA2      | ST            | CMOS           | PORTA I/O with prog. pull-up and interrupt-on-change |

|                                     | AN2      | AN            |                | A/D Channel 2 input                                  |

|                                     | TOCKI    | ST            |                | Timer0 clock input                                   |

|                                     | INT      | ST            | _              | External Interrupt                                   |

|                                     | C1OUT    | _             | CMOS           | Comparator 1 output                                  |

| RA3/MCLR/VPP                        | RA3      | TTL           |                | PORTA input with interrupt-on-change                 |

|                                     | MCLR     | ST            | _              | Master Clear w/internal pull-up                      |

|                                     | VPP      | HV            |                | Programming voltage                                  |

| RA4/AN3/T1G/OSC2/CLKOUT             | RA4      |               | CMOS           | PORTA I/O with prog. pull-up and interrupt-on-chang  |

| RA4/AN3/TTG/OSC2/CEROUT             |          |               | CIVIOS         |                                                      |

|                                     | AN3      | AN            |                | A/D Channel 3 input                                  |

|                                     | TIG      | ST            |                | Timer1 gate (count enable)                           |

|                                     | OSC2     |               | XTAL           | Crystal/Resonator                                    |

|                                     | CLKOUT   |               | CMOS           | Fosc/4 output                                        |

| RA5/T1CKI/OSC1/CLKIN                | RA5      | TTL           | CMOS           | PORTA I/O with prog. pull-up and interrupt-on-chang  |

|                                     | T1CKI    | ST            | —              | Timer1 clock                                         |

|                                     | OSC1     | XTAL          | —              | Crystal/Resonator                                    |

|                                     | CLKIN    | ST            | —              | External clock input/RC oscillator connection        |

| RC0/AN4/C2IN+                       | RC0      | TTL           | CMOS           | PORTC I/O                                            |

|                                     | AN4      | AN            | —              | A/D Channel 4 input                                  |

|                                     | C2IN+    | AN            | —              | Comparator 2 non-inverting input                     |

| RC1/AN5/C2IN-                       | RC1      | TTL           | CMOS           | PORTC I/O                                            |

|                                     | AN5      | AN            | _              | A/D Channel 5 input                                  |

|                                     | C2IN-    | AN            | —              | Comparator 2 inverting input                         |

| RC2/AN6/P1D                         | RC2      | TTL           | CMOS           | PORTC I/O                                            |

|                                     | AN6      | AN            | _              | A/D Channel 6 input                                  |

|                                     | P1D      | —             | CMOS           | PWM output                                           |

| RC3/AN7/P1C                         | RC3      | TTL           | CMOS           | PORTC I/O                                            |

|                                     | AN7      | AN            |                | A/D Channel 7 input                                  |

|                                     | P1C      | —             | CMOS           | PWM output                                           |

| RC4/C2OUT/P1B                       | RC4      | TTL           | CMOS           | PORTC I/O                                            |

|                                     | C2OUT    | _             | CMOS           | Comparator 2 output                                  |

|                                     | P1B      |               | CMOS           | PWM output                                           |

| RC5/CCP1/P1A                        | RC5      | TTL           | CMOS           | PORTC I/O                                            |

|                                     | CCP1     | ST            | CMOS           | Capture input/Compare output                         |

|                                     | P1A      | _             | CMOS           | PWM output                                           |

| VDD                                 | VDD      | Power         | _              | Positive supply                                      |

| Vss                                 | VSS      | Power         |                | Ground reference                                     |

| Legend: AN = Analog input or output |          |               |                | DS compatible input or output HV = High Voltage      |

# 2.0 MEMORY ORGANIZATION

#### 2.1 Program Memory Organization

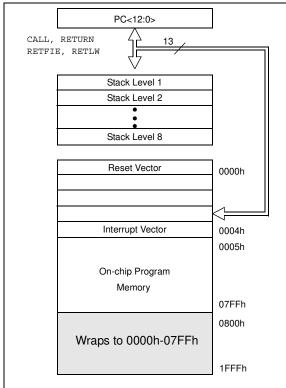

The PIC16F684 has a 13-bit program counter capable of addressing an  $8k \times 14$  program memory space. Only the first  $2k \times 14$  (0000h-07FFh) for the PIC16F684 is physically implemented. Accessing a location above these boundaries will cause a wrap around within the first  $2k \times 14$  space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 2-1).

#### FIGURE 2-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16F684

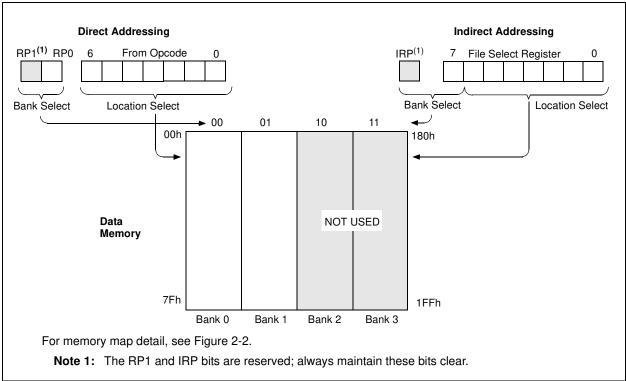

### 2.2 Data Memory Organization

The data memory (see Figure 2-2) is partitioned into two banks, which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR). The Special Function Registers are located in the first 32 locations of each bank. Register locations 20h-7Fh in Bank 0 and A0h-BFh in Bank 1 are General Purpose Registers, implemented as static RAM. Register locations F0h-FFh in Bank 1 point to addresses 70h-7Fh in Bank 0. All other RAM is unimplemented and returns '0' when read. The RP0 bit of the STATUS register is the bank select bit.

#### RP0

- $0 \rightarrow \text{Bank 0 is selected}$

- $1 \rightarrow \text{Bank 1 is selected}$

Note: The IRP and RP1 bits of the STATUS register are reserved and should always be maintained as '0's.

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 128 x 8 in the PIC16F684. Each register is accessed, either directly or indirectly, through the File Select Register (FSR) (see Section 2.4 "Indirect Addressing, INDF and FSR Registers").

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (see Table 2-1). These registers are static RAM.

The special registers can be classified into two sets: core and peripheral. The Special Function Registers associated with the "core" are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

#### FIGURE 2-2: DATA MEMORY MAP OF THE PIC16F684

| Indirect Addr. <sup>(1)</sup> | 00h       | Indirect Addr. <sup>(1)</sup> | 80       |

|-------------------------------|-----------|-------------------------------|----------|

| TMR0                          | 01h       | OPTION REG                    | 81       |

| PCL                           | 02h       | PCL                           | 82       |

| STATUS                        | 03h       | STATUS                        | 83       |

| FSR                           | 04h       | FSR                           | 84       |

| PORTA                         | 05h       | TRISA                         | 85       |

| 10111/                        | 05h       | THOM                          | 86       |

| PORTC                         | 07h       | TRISC                         | 87       |

| Tonto                         |           | 11100                         | 88       |

|                               | 08h       |                               |          |

|                               | 09h       |                               | 89       |

| PCLATH<br>INTCON              | 0Ah       | PCLATH                        | 8A       |

|                               | 0Bh       | INTCON<br>PIE1                | 8B       |

| PIR1                          | 0Ch       | PIET                          | 80       |

| THE                           | 0Dh       | Baan                          | 8D       |

| TMR1L                         | 0Eh       | PCON                          | 8E       |

| TMR1H                         | 0Fh       | OSCCON                        | 8F       |

| T1CON                         | 10h       | OSCTUNE                       | 90       |

| TMR2                          | 11h       | ANSEL                         | 91       |

| T2CON                         | 12h       | PR2                           | 92       |

| CCPR1L                        | 13h       |                               | 93       |

| CCPR1H                        | 14h       |                               | 94       |

| CCP1CON                       | 15h       | WPUA                          | 95       |

| PWM1CON                       | 16h       | IOCA                          | 96       |

| ECCPAS                        | 17h       |                               | 97       |

| WDTCON                        | 18h       |                               | 98       |

| CMCON0                        | 19h       | VRCON                         | 99       |

| CMCON1                        | 1Ah       | EEDAT                         | 9A       |

|                               | 1Bh       | EEADR                         | 9B       |

|                               | 1Ch       | EECON1                        | 90       |

|                               | 1Dh       | EECON2 <sup>(1)</sup>         | 90       |

| ADRESH                        | 1Eh       | ADRESL                        | 9E       |

| ADCON0                        | 1Fh       | ADCON1                        | 9F       |

|                               | 20h       | General                       | A0       |

|                               |           | Purpose<br>Registers          |          |

| General                       |           | 32 Bytes                      | BF       |

| Purpose                       |           |                               |          |

| Registers                     |           |                               |          |

| 96 Bytes                      |           |                               |          |

|                               |           |                               |          |

|                               |           |                               |          |

|                               |           |                               |          |

|                               |           |                               |          |

|                               | 6Fh       |                               |          |

|                               | 70        |                               | F0       |

|                               | 76<br>7Fh | Accesses 70h-7Fh              | FF       |

| Bank 0                        |           | Bank 1                        | <u> </u> |

| Addr   | Name                 | Bit 7              | Bit 6              | Bit 5           | Bit 4          | Bit 3            | Bit 2           | Bit 1         | Bit 0   | Value on<br>POR, BOR | Page     |

|--------|----------------------|--------------------|--------------------|-----------------|----------------|------------------|-----------------|---------------|---------|----------------------|----------|

| Bank 0 |                      |                    |                    |                 |                |                  |                 |               |         |                      |          |

| 00h    | INDF                 | Addressing         | this location (    | uses contents   | s of FSR to a  | ddress data r    | memory (not     | a physical re | gister) | xxxx xxxx            | 19, 104  |

| 01h    | TMR0                 | Timer0 Mod         | ule's Registe      | r               |                |                  |                 |               |         | xxxx xxxx            | 43, 104  |

| 02h    | PCL                  | ě                  | unter's (PC)       | Least Signific  | cant Byte      | -                | -               | -             | -       | 0000 0000            | 19, 104  |

| 03h    | STATUS               | IRP <sup>(1)</sup> | RP1 <sup>(1)</sup> | RP0             | TO             | PD               | Z               | DC            | С       | 0001 1xxx            | 13, 104  |

| 04h    | FSR                  | Indirect Data      | a Memory Ad        | dress Pointe    | r              | -                | -               | -             | -       | xxxx xxxx            | 19, 104  |

| 05h    | PORTA <sup>(2)</sup> | -                  | —                  | RA5             | RA4            | RA3              | RA2             | RA1           | RA0     | x0 x000              | 31, 104  |

| 06h    | —                    | Unimplemer         | nted               |                 |                |                  |                 |               |         | —                    | —        |

| 07h    | PORTC <sup>(2)</sup> |                    | —                  | RC5             | RC4            | RC3              | RC2             | RC1           | RC0     | xx 0000              | 40, 104  |

| 08h    | _                    | Unimplemen         | nted               |                 |                |                  |                 |               |         | —                    | —        |

| 09h    | _                    | Unimplemen         | nted               |                 |                |                  |                 |               |         | _                    | —        |

| 0Ah    | PCLATH               | _                  | _                  | _               | Write          | e Buffer for up  | oper 5 bits of  | Program Co    | unter   | 0 0000               | 19, 104  |

| 0Bh    | INTCON               | GIE                | PEIE               | T0IE            | INTE           | RAIE             | T0IF            | INTF          | RAIF    | 0000 0000            | 15, 104  |

| 0Ch    | PIR1                 | EEIF               | ADIF               | CCP1IF          | C2IF           | C1IF             | OSFIF           | TMR2IF        | TMR1IF  | 0000 0000            | 17, 104  |

| 0Dh    | _                    | Unimplemer         | nted               |                 |                |                  |                 |               |         | —                    | —        |

| 0Eh    | TMR1L                | Holding Reg        | jister for the I   | _east Signific  | ant Byte of th | ne 16-bit TMF    | R1 Register     |               |         | xxxx xxxx            | 47, 104  |

| 0Fh    | TMR1H                | Holding Reg        | ister for the I    | Most Significa  | ant Byte of th | e 16-bit TMR     | 1 Register      |               |         | xxxx xxxx            | 47, 104  |

| 10h    | T1CON                | T1GINV             | TMR1GE             | T1CKPS1         | T1CKPS0        | T1OSCEN          | T1SYNC          | TMR1CS        | TMR10N  | 0000 0000            | 50, 104  |

| 11h    | TMR2                 | Timer2 Mod         | ule Register       |                 |                | •                | •               | •             | •       | 0000 0000            | 53, 104  |

| 12h    | T2CON                |                    | TOUTPS3            | TOUTPS2         | TOUTPS1        | TOUTPS0          | TMR2ON          | T2CKPS1       | T2CKPS0 | -000 0000            | 54, 104  |

| 13h    | CCPR1L               | Capture/Cor        | mpare/PWM          | Register 1 Lo   | ow Byte        | •                | •               | •             | •       | XXXX XXXX            | 80, 104  |

| 14h    | CCPR1H               | Capture/Cor        | mpare/PWM          | Register 1 Hi   | gh Byte        |                  |                 |               |         | XXXX XXXX            | 80, 104  |

| 15h    | CCP1CON              | P1M1               | P1M0               | DC1B1           | DC1B0          | CCP1M3           | CCP1M2          | CCP1M1        | CCP1M0  | 0000 0000            | 79, 104  |

| 16h    | PWM1CON              | PRSEN              | PDC6               | PDC5            | PDC4           | PDC3             | PDC2            | PDC1          | PDC0    | 0000 0000            | 96, 104  |

| 17h    | ECCPAS               | ECCPASE            | ECCPAS2            | ECCPAS1         | ECCPAS0        | PSSAC1           | PSSAC0          | PSSBD1        | PSSBD0  | 0000 0000            | 93, 104  |

| 18h    | WDTCON               | —                  | —                  |                 | WDTPS3         | WDTPS2           | WDTPS1          | WDTPS0        | SWDTEN  | 0 1000               | 111, 104 |

| 19h    | CMCON0               | C2OUT              | C1OUT              | C2INV           | C1INV          | CIS              | CM2             | CM1           | CM0     | 0000 0000            | 61, 104  |

| 1Ah    | CMCON1               | —                  | —                  | —               | —              | —                | —               | T1GSS         | C2SYNC  | 10                   | 62, 104  |

| 1Bh    | _                    | Unimplemer         | nted               |                 |                |                  |                 |               |         | _                    | —        |

| 1Ch    | _                    | Unimplemer         | nted               |                 |                |                  |                 |               |         | _                    | —        |

| 1Dh    | _                    | Unimplemer         | nted               |                 |                |                  |                 |               |         | _                    | —        |

| 1Eh    | ADRESH               | Most Signific      | cant 8 bits of     | the left shifte | d A/D result   | or 2 bits of rig | ght shifted res | sult          |         | xxxx xxxx            | 71, 104  |

| 1Fh    | ADCON0               | ADFM               | VCFG               | _               | CHS2           | CHS1             | CHS0            | GO/DONE       | ADON    | 00-0 0000            | 70, 104  |

| TABLE 2-1: | PIC16F684 SPECIAL FUNCTION REGISTERS SUMMARY BANK 0 |

|------------|-----------------------------------------------------|

|            |                                                     |

Legend: Note 1:

– = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented IRP and RP1 bits are reserved, always maintain these bits clear.

Port pins with analog functions controlled by the ANSEL register will read '0' immediately after a Reset even though the data latches are either undefined (POR) or unchanged (other Resets). 2:

| Addr   | Name                | Bit 7              | Bit 6              | Bit 5            | Bit 4         | Bit 3               | Bit 2           | Bit 1         | Bit 0     | Value on<br>POR, BOR | Page    |

|--------|---------------------|--------------------|--------------------|------------------|---------------|---------------------|-----------------|---------------|-----------|----------------------|---------|

| Bank 1 |                     |                    |                    |                  |               |                     |                 |               |           |                      |         |

| 80h    | INDF                | Addressing         | this location      | uses content     | ts of FSR to  | address data        | a memory (no    | ot a physical | register) | xxxx xxxx            | 19, 104 |

| 81h    | OPTION_REG          | RAPU               | INTEDG             | TOCS             | T0SE          | PSA                 | PS2             | PS1           | PS0       | 1111 1111            | 14, 104 |

| 82h    | PCL                 | Program Co         | ounter's (PC)      | Least Signif     | icant Byte    |                     |                 |               |           | 0000 0000            | 19, 104 |

| 83h    | STATUS              | IRP <sup>(1)</sup> | RP1 <sup>(1)</sup> | RP0              | TO            | PD                  | Z               | DC            | С         | 0001 1xxx            | 13, 104 |

| 84h    | FSR                 | Indirect Dat       | a Memory Ad        | dress Pointe     | er            |                     |                 |               |           | xxxx xxxx            | 19, 104 |

| 85h    | TRISA               | _                  | _                  | TRISA5           | TRISA4        | TRISA3              | TRISA2          | TRISA1        | TRISA0    | 11 1111              | 31, 104 |

| 86h    |                     | Unimpleme          | nted               |                  |               |                     |                 |               |           | -                    | _       |

| 87h    | TRISC               | _                  | _                  | TRISC5           | TRISC4        | TRISC3              | TRISC2          | TRISC1        | TRISC0    | 11 1111              | 40, 104 |

| 88h    |                     | Unimpleme          | nted               |                  |               |                     |                 |               |           | _                    | _       |

| 89h    | —                   | Unimpleme          | nted               |                  |               |                     |                 |               |           | —                    | _       |

| 8Ah    | PCLATH              | _                  |                    |                  | Write         | e Buffer for u      | pper 5 bits of  | Program Co    | ounter    | 0 0000               | 19, 104 |

| 8Bh    | INTCON              | GIE                | PEIE               | T0IE             | INTE          | RAIE                | T0IF            | INTF          | RAIF      | 0000 0000            | 15, 104 |

| 8Ch    | PIE1                | EEIE               | ADIE               | CCP1IE           | C2IE          | C1IE                | OSFIE           | TMR2IE        | TMR1IE    | 0000 0000            | 16, 104 |

| 8Dh    |                     | Unimpleme          | nted               |                  |               |                     |                 |               |           | _                    | _       |

| 8Eh    | PCON                | _                  | _                  | ULPWUE           | SBOREN        | _                   | _               | POR           | BOR       | 01qq                 | 18, 104 |

| 8Fh    | OSCCON              | _                  | IRCF2              | IRCF1            | IRCF0         | OSTS <sup>(2)</sup> | HTS             | LTS           | SCS       | -110 x000            | 20, 104 |

| 90h    | OSCTUNE             | _                  |                    |                  | TUN4          | TUN3                | TUN2            | TUN1          | TUN0      | 0 0000               | 24, 105 |

| 91h    | ANSEL               | ANS7               | ANS6               | ANS5             | ANS4          | ANS3                | ANS2            | ANS1          | ANS0      | 1111 1111            | 32, 105 |

| 92h    | PR2                 | Timer2 Mod         | lule Period R      | egister          |               |                     |                 |               |           | 1111 1111            | 53, 105 |

| 93h    | _                   | Unimpleme          | nted               |                  |               |                     |                 |               |           | -                    | _       |

| 94h    |                     | Unimpleme          | nted               |                  |               |                     |                 |               |           | -                    | —       |

| 95h    | WPUA <sup>(3)</sup> |                    |                    | WPUA5            | WPUA4         |                     | WPUA2           | WPUA1         | WPUA0     | 11 -111              | 33, 105 |

| 96h    | IOCA                |                    |                    | IOCA5            | IOCA4         | IOCA3               | IOCA2           | IOCA1         | IOCA0     | 00 0000              | 33, 105 |

| 97h    | _                   | Unimpleme          | nted               |                  |               |                     |                 |               |           | -                    | _       |

| 98h    |                     | Unimpleme          | nted               |                  |               |                     |                 |               |           | -                    | _       |

| 99h    | VRCON               | VREN               | _                  | VRR              | —             | VR3                 | VR2             | VR1           | VR0       | 0-0- 0000            | 63, 105 |

| 9Ah    | EEDAT               | EEDAT7             | EEDAT6             | EEDAT5           | EEDAT4        | EEDAT3              | EEDAT2          | EEDAT1        | EEDAT0    | 0000 0000            | 75, 105 |

| 9Bh    | EEADR               | EEADR7             | EEADR6             | EEADR5           | EEADR4        | EEADR3              | EEADR2          | EEADR1        | EEADR0    | 0000 0000            | 75, 105 |

| 9Ch    | EECON1              | —                  | —                  | —                |               | WRERR               | WREN            | WR            | RD        | x000                 | 76, 105 |

| 9Dh    | EECON2              | EEPROM C           | Control Regist     | ter 2 (not a p   | hysical regis | iter)               |                 |               |           |                      | 76, 105 |

| 9Eh    | ADRESL              | Least Signif       | icant 2 bits o     | f the left shift | ted result or | 8 bits of the       | right shifted ı | result        |           | xxxx xxxx            | 71, 105 |

| 9Fh    | ADCON1              | _                  | ADCS2              | ADCS1            | ADCS0         | _                   | _               | _             | _         | -000                 | 70, 105 |

#### TABLE 2-2: PIC16F684 SPECIAL FUNCTION REGISTERS SUMMARY BANK 1

Legend: -= Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

**Note 1:** IRP and RP1 bits are reserved, always maintain these bits clear.

2: OSTS bit of the OSCCON register reset to '0' with Dual Speed Start-up and LP, HS or XT selected as the oscillator.

3: RA3 pull-up is enabled when MCLRE is '1' in the Configuration Word register.

#### 2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

- the bank select bits for data memory (SRAM)

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS, will clear the upper three bits and set the Z bit. This leaves the STATUS register as `000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits, see Section 13.0 "Instruction Set Summary".

- Note 1: Bits IRP and RP1 of the STATUS register are not used by the PIC16F684 and should be maintained as clear. Use of these bits is not recommended, since this may affect upward compatibility with future products.

- 2: The <u>C</u> and <u>DC</u> bits operate as a Borrow and <u>Digit</u> Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

# REGISTER 2-1: STATUS: STATUS REGISTER

| Reserved | Reserved | R/W-0 | R-1 | R-1 | R/W-x | R/W-x | R/W-x |

|----------|----------|-------|-----|-----|-------|-------|-------|

| IRP      | RP1      | RP0   | TO  | PD  | Z     | DC    | С     |

| bit 7    |          |       |     |     |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | <b>IRP:</b> This bit is reserved and should be maintained as '0'                                                   |

|---------|--------------------------------------------------------------------------------------------------------------------|

| bit 6   | <b>RP1:</b> This bit is reserved and should be maintained as '0'                                                   |

| bit 5   | <b>RP0:</b> Register Bank Select bit (used for direct addressing)                                                  |

|         | 1 = Bank 1 (80h – FFh)                                                                                             |

|         | 0 = Bank 0 (00h - 7Fh)                                                                                             |

| bit 4   | TO: Time-out bit                                                                                                   |

|         | 1 = After power-up, CLRWDT instruction or SLEEP instruction                                                        |

|         | 0 = A WDT time-out occurred                                                                                        |

| bit 3   | PD: Power-down bit                                                                                                 |

|         | 1 = After power-up or by the CLRWDT instruction                                                                    |

|         | 0 = By execution of the SLEEP instruction                                                                          |

| bit 2   | <b>Z:</b> Zero bit                                                                                                 |

|         | 1 = The result of an arithmetic or logic operation is zero                                                         |

|         | 0 = The result of an arithmetic or logic operation is not zero                                                     |

| bit 1   | <b>DC:</b> Digit Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions), For Borrow, the polarity is reversed. |

|         | 1 = A carry-out from the 4th low-order bit of the result occurred                                                  |

|         | 0 = No carry-out from the 4th low-order bit of the result                                                          |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions)                                       |

|         | 1 = A carry-out from the Most Significant bit of the result occurred                                               |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                                              |

| Note 1: | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the sec-         |

**Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register.

#### 2.2.2.2 OPTION Register

The OPTION register is a readable and writable register, which contains various control bits to configure:

- Timer0/WDT prescaler

- External RA2/INT interrupt

- Timer0

- Weak pull-ups on PORTA

Note: To achieve a 1:1 prescaler assignment for Timer0, assign the prescaler to the WDT by setting PSA bit to '1' of the OPTION register. See Section 5.1.3 "Software Programmable Prescaler".

#### REGISTER 2-2: OPTION\_REG: OPTION REGISTER

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RAPU  | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | RAPU: PORTA Pull-up Enable bit                                 |

|---------|----------------------------------------------------------------|

|         | 1 = PORTA pull-ups are disabled                                |

|         | 0 = PORTA pull-ups are enabled by individual PORT latch values |

| bit 6   | INTEDG: Interrupt Edge Select bit                              |

|         | 1 = Interrupt on rising edge of RA2/INT pin                    |

|         | 0 = Interrupt on falling edge of RA2/INT pin                   |

| bit 5   | TOCS: Timer0 Clock Source Select bit                           |

|         | 1 = Transition on RA2/T0CKI pin                                |

|         | 0 = Internal instruction cycle clock (FOSC/4)                  |

| bit 4   | TOSE: Timer0 Source Edge Select bit                            |

|         | 1 = Increment on high-to-low transition on RA2/T0CKI pin       |

|         | 0 = Increment on low-to-high transition on RA2/T0CKI pin       |

| bit 3   | PSA: Prescaler Assignment bit                                  |

|         | 1 = Prescaler is assigned to the WDT                           |

|         | 0 = Prescaler is assigned to the Timer0 module                 |

| bit 2-0 | PS<2:0>: Prescaler Rate Select bits                            |

|         | BIT VALUE TIMER0 RATE WDT RATE                                 |

|         | 000 1:2 1:1                                                    |

|         | 001 1:4 1:2                                                    |

1:8

1:16

1:32

1:64

1:128

1:256

1:4

1:8

1:16

1:32 1:64

1:128

010

011 100

101

110

111

#### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, PORTA change and external RA2/INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GIE   | PEIE  | T0IE  | INTE  | RAIE  | T0IF  | INTF  | RAIF  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | <b>GIE:</b> Global Interrupt Enable bit<br>1 = Enables all unmasked interrupts<br>0 = Disables all interrupts                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <b>PEIE:</b> Peripheral Interrupt Enable bit<br>1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts                                                         |

| bit 5 | <b>TolE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt<br>0 = Disables the Timer0 interrupt                                                                       |

| bit 4 | INTE: RA2/INT External Interrupt Enable bit<br>1 = Enables the RA2/INT external interrupt<br>0 = Disables the RA2/INT external interrupt                                                         |

| bit 3 | <b>RAIE:</b> PORTA Change Interrupt Enable bit <sup>(1)</sup><br>1 = Enables the PORTA change interrupt<br>0 = Disables the PORTA change interrupt                                               |

| bit 2 | <b>TOIF:</b> Timer0 Overflow Interrupt Flag bit <sup>(2)</sup><br>1 = Timer0 register has overflowed (must be cleared in software)<br>0 = Timer0 register did not overflow                       |

| bit 1 | INTF: RA2/INT External Interrupt Flag bit<br>1 = The RA2/INT external interrupt occurred (must be cleared in software)<br>0 = The RA2/INT external interrupt did not occur                       |

| bit 0 | <b>RAIF:</b> PORTA Change Interrupt Flag bit<br>1 = When at least one of the PORTA <5:0> pins changed state (must be cleared in software)<br>0 = None of the PORTA <5:0> pins have changed state |

|       |                                                                                                                                                                                                  |

- Note 1: IOCA register must also be enabled.

- 2: T0IF bit is set when TMR0 rolls over. TMR0 is unchanged on Reset and should be initialized before clearing T0IF bit.

# PIC16F684

#### 2.2.2.4 PIE1 Register

The PIE1 register contains the peripheral interrupt enable bits, as shown in Register 2-4.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

| R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  |

|-------|-------|--------|-------|-------|-------|--------|--------|

| EEIE  | ADIE  | CCP1IE | C2IE  | C1IE  | OSFIE | TMR2IE | TMR1IE |

| bit 7 |       |        |       |       |       |        | bit 0  |

| Legend:         |                                                                                                |                      |                    |

|-----------------|------------------------------------------------------------------------------------------------|----------------------|--------------------|

| R = Readable    | bit W = Writable bit                                                                           | U = Unimplemented bi | t, read as '0'     |

| -n = Value at F | POR '1' = Bit is set                                                                           | '0' = Bit is cleared | x = Bit is unknown |

|                 |                                                                                                |                      |                    |

| bit 7           | EEIE: EE Write Complete Interru                                                                | •                    |                    |

|                 | <ul><li>1 = Enables the EE write complete</li><li>0 = Disables the EE write complete</li></ul> |                      |                    |

| bit 6           | ADIE: A/D Converter (ADC) Inte                                                                 | errupt Enable bit    |                    |

|                 | <ul> <li>1 = Enables the ADC interrupt</li> <li>0 = Disables the ADC interrupt</li> </ul>      |                      |                    |

| bit 5           | <b>CCP1IE:</b> CCP1 Interrupt Enable                                                           | bit                  |                    |

|                 | 1 = Enables the CCP1 interrupt                                                                 |                      |                    |

|                 | 0 = Disables the CCP1 interrupt                                                                |                      |                    |

| bit 4 C         | C2IE: Comparator 2 Interrupt En                                                                | hable bit            |                    |

|                 | 1 = Enables the Comparator 2 in                                                                | nterrupt             |                    |

|                 | 0 = Disables the Comparator 2 in                                                               | nterrupt             |                    |

| bit 3           | C1IE: Comparator 1 Interrupt En                                                                | hable bit            |                    |

|                 | 1 = Enables the Comparator 1 in                                                                |                      |                    |

|                 | 0 = Disables the Comparator 1 in                                                               | •                    |                    |

| bit 2           | <b>OSFIE:</b> Oscillator Fail Interrupt E                                                      |                      |                    |

|                 | 1 = Enables the oscillator fail inte                                                           | •                    |                    |

|                 | 0 = Disables the oscillator fail int                                                           | •                    |                    |

| bit 1           | TMR2IE: Timer2 to PR2 Match I                                                                  | •                    |                    |

|                 | <ul> <li>1 = Enables the Timer2 to PR2 r</li> <li>0 = Disables the Timer2 to PR2</li> </ul>    | •                    |                    |

| bit 0           |                                                                                                | · ·                  |                    |

|                 | <b>TMR1IE:</b> Timer1 Overflow Interr                                                          | •                    |                    |

|                 | <ul> <li>1 = Enables the Timer1 overflow</li> <li>0 = Disables the Timer1 overflow</li> </ul>  | / interrupt          |                    |

#### 2.2.2.5 PIR1 Register

The PIR1 register contains the peripheral interrupt flag bits, as shown in Register 2-5.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  |

|-------|-------|--------|-------|-------|-------|--------|--------|

| EEIF  | ADIF  | CCP1IF | C2IF  | C1IF  | OSFIF | TMR2IF | TMR1IF |

| bit 7 |       |        |       |       |       |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7 | <b>EEIF:</b> EEPROM Write Operation Interrupt Flag bit<br>1 = The write operation completed (must be cleared in software)<br>0 = The write operation has not completed or has not been started                                                                                                                                                                          |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <ul> <li>ADIF: A/D Interrupt Flag bit</li> <li>1 = A/D conversion complete</li> <li>0 = A/D conversion has not completed or has not been started</li> </ul>                                                                                                                                                                                                             |

| bit 5 | CCP1IF: CCP1 Interrupt Flag bit<br><u>Capture mod</u> e:<br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred<br><u>Compare mode</u> :<br>1 = A TMR1 register compare match occurred (must be cleared in software)<br>0 = No TMR1 register compare match occurred<br><u>PWM mode</u> :<br>Unused in this mode |

| bit 4 | <b>C2IF:</b> Comparator 2 Interrupt Flag bit<br>1 = Comparator 2 output has changed (must be cleared in software)<br>0 = Comparator 2 output has not changed                                                                                                                                                                                                            |

| bit 3 | <b>C1IF:</b> Comparator 1 Interrupt Flag bit<br>1 = Comparator 1 output has changed (must be cleared in software)<br>0 = Comparator 1 output has not changed                                                                                                                                                                                                            |

| bit 2 | <b>OSFIF:</b> Oscillator Fail Interrupt Flag bit<br>1 = System oscillator failed, clock input has changed to INTOSC (must be cleared in software)<br>0 = System clock operating                                                                                                                                                                                         |

| bit 1 | <b>TMR2IF:</b> Timer2 to PR2 Match Interrupt Flag bit<br>1 = Timer2 to PR2 match occurred (must be cleared in software)<br>0 = Timer2 to PR2 match has not occurred                                                                                                                                                                                                     |

| bit 0 | <b>TMR1IF:</b> Timer1 Overflow Interrupt Flag bit<br>1 = Timer1 register overflowed (must be cleared in software)<br>0 = Timer1 has not overflowed                                                                                                                                                                                                                      |

#### 2.2.2.6 PCON Register

The Power Control (PCON) register (see Table 12-2) contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON register also controls the Ultra Low-Power Wake-up and software enable of the BOR.

The PCON register bits are shown in Register 2-6.

#### REGISTER 2-6: PCON: POWER CONTROL REGISTER

| U-0   | U-0 | R/W-0  | R/W-1  | U-0 | U-0 | R/W-0 | R/W-x |

|-------|-----|--------|--------|-----|-----|-------|-------|

| —     | —   | ULPWUE | SBOREN | -   | —   | POR   | BOR   |

| bit 7 |     |        |        |     |     |       | bit 0 |

| Legend:                               |                                                                                                                                                                    |                                                                                                       |                                                   |                    |  |  |  |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------|--|--|--|

| R = Readable bit                      |                                                                                                                                                                    | W = Writable bit                                                                                      | = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value                            | at POR                                                                                                                                                             | '1' = Bit is set                                                                                      | '0' = Bit is cleared                              | x = Bit is unknown |  |  |  |

|                                       |                                                                                                                                                                    |                                                                                                       |                                                   |                    |  |  |  |

| bit 7-6                               | Unimple                                                                                                                                                            | mented: Read as '0'                                                                                   |                                                   |                    |  |  |  |

| bit 5                                 | ULPWUE                                                                                                                                                             | E: Ultra Low-Power Wake-Up                                                                            | o Enable bit                                      |                    |  |  |  |

|                                       |                                                                                                                                                                    | <ul> <li>1 = Ultra Low-Power Wake-up enabled</li> <li>0 = Ultra Low-Power Wake-up disabled</li> </ul> |                                                   |                    |  |  |  |

| bit 4                                 | SBOREN                                                                                                                                                             | I: Software BOR Enable bit <sup>(*</sup>                                                              | 1)                                                |                    |  |  |  |

|                                       | 1 = BOR enabled<br>0 = BOR disabled                                                                                                                                |                                                                                                       |                                                   |                    |  |  |  |

| bit 3-2                               | Unimple                                                                                                                                                            | Unimplemented: Read as '0'                                                                            |                                                   |                    |  |  |  |

| bit 1                                 | POR: Po                                                                                                                                                            | POR: Power-on Reset Status bit                                                                        |                                                   |                    |  |  |  |

|                                       | <ul> <li>1 = No Power-on Reset occurred</li> <li>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)</li> </ul>                  |                                                                                                       |                                                   |                    |  |  |  |

| bit 0 BOR: Brown-out Reset Status bit |                                                                                                                                                                    |                                                                                                       |                                                   |                    |  |  |  |

|                                       | <ul> <li>1 = No Brown-out Reset occurred</li> <li>0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out R occurs)</li> </ul> |                                                                                                       |                                                   |                    |  |  |  |

**Note 1:** BOREN<1:0> = 01 in the Configuration Word register for this bit to control the  $\overline{\text{BOR}}$ .

## 2.3 PCL and PCLATH

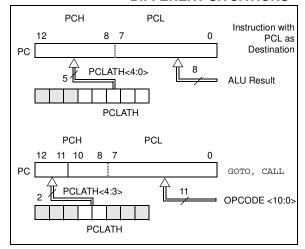

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-3 shows the two situations for the loading of the PC. The upper example in Figure 2-3 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 2-3 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-3: LOADING OF PC IN DIFFERENT SITUATIONS

#### 2.3.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<12:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by first writing the desired upper 5 bits to the PCLATH register. Then, when the lower 8 bits are written to the PCL register, all 13 bits of the program counter will change to the values contained in the PCLATH register.

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). Care should be exercised when jumping into a look-up table or program branch table (computed GOTO) by modifying the PCL register. Assuming that PCLATH is set to the table start address, if the table length is greater than 255 instructions or if the lower 8 bits of the memory address rolls over from 0xFF to 0x00 in the middle of the table, then PCLATH must be incremented for each address rollover that occurs between the table beginning and the target location within the table.

For more information refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

## 2.3.2 STACK

The PIC16F684 Family has an 8-level x 13-bit wide hardware stack (see Figure 2-1). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

| Note 1: | There are no Status bits to indicate stack overflow or stack underflow conditions.                                                                                                                   |  |  |  |  |