Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### 8-Bit CMOS Microcontrollers with A/D Converter

#### Devices included in this data sheet:

- PIC16C72

- PIC16C74A

- PIC16C73

- PIC16C76

- PIC16C73A

- PIC16C77

- PIC16C74

### **PIC16C7X Microcontroller Core Features:**

- · High-performance RISC CPU

- · Only 35 single word instructions to learn

- All single cycle instructions except for program branches which are two cycle

- Operating speed: DC 20 MHz clock input DC - 200 ns instruction cycle

- Up to 8K x 14 words of Program Memory, up to 368 x 8 bytes of Data Memory (RAM)

- · Interrupt capability

- · Eight level deep hardware stack

- · Direct, indirect, and relative addressing modes

- · Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- · Programmable code-protection

- · Power saving SLEEP mode

- · Selectable oscillator options

- Low-power, high-speed CMOS EPROM technology

- · Fully static design

- Wide operating voltage range: 2.5V to 6.0V

- · High Sink/Source Current 25/25 mA

- Commercial, Industrial and Extended temperature ranges

- · Low-power consumption:

- < 2 mA @ 5V, 4 MHz

- 15 μA typical @ 3V, 32 kHz

- < 1 µA typical standby current

### **PIC16C7X Peripheral Features:**

- Timer0: 8-bit timer/counter with 8-bit prescaler

- Timer1: 16-bit timer/counter with prescaler, can be incremented during sleep via external crystal/clock

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- · Capture, Compare, PWM module(s)

- Capture is 16-bit, max. resolution is 12.5 ns, Compare is 16-bit, max. resolution is 200 ns, PWM max. resolution is 10-bit

- 8-bit multichannel analog-to-digital converter

- Synchronous Serial Port (SSP) with SPI<sup>™</sup> and I<sup>2</sup>C<sup>™</sup>

- Universal Synchronous Asynchronous Receiver Transmitter (USART/SCI)

- Parallel Slave Port (PSP) 8-bits wide, with external RD, WR and CS controls

- Brown-out detection circuitry for Brown-out Reset (BOR)

| PIC16C7X Features             | 72                   | 73                             | 73A                            | 74                             | 74 <b>A</b>                    | 76                             | 77                             |

|-------------------------------|----------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|

| Program Memory (EPROM) x 14   | 2K                   | 4K                             | 4K                             | 4K                             | 4K                             | 8K                             | 8K                             |

| Data Memory (Bytes) x 8       | 128                  | 192                            | 192                            | 192                            | 192                            | 368                            | 368                            |

| I/O Pins                      | 22                   | 22                             | 22                             | 33                             | 33                             | 22                             | 33                             |

| Parallel Slave Port           | _                    | _                              | _                              | Yes                            | Yes                            | _                              | Yes                            |

| Capture/Compare/PWM Modules   | 1                    | 2                              | 2                              | 2                              | 2                              | 2                              | 2                              |

| Timer Modules                 | 3                    | 3                              | 3                              | 3                              | 3                              | 3                              | 3                              |

| A/D Channels                  | 5                    | 5                              | 5                              | 8                              | 8                              | 5                              | 8                              |

| Serial Communication          | SPI/I <sup>2</sup> C | SPI/I <sup>2</sup> C,<br>USART |

| In-Circuit Serial Programming | Yes                  | Yes                            | Yes                            | Yes                            | Yes                            | Yes                            | Yes                            |

| Brown-out Reset               | Yes                  | _                              | Yes                            | _                              | Yes                            | Yes                            | Yes                            |

| Interrupt Sources             | 8                    | 11                             | 11                             | 12                             | 12                             | 11                             | 12                             |

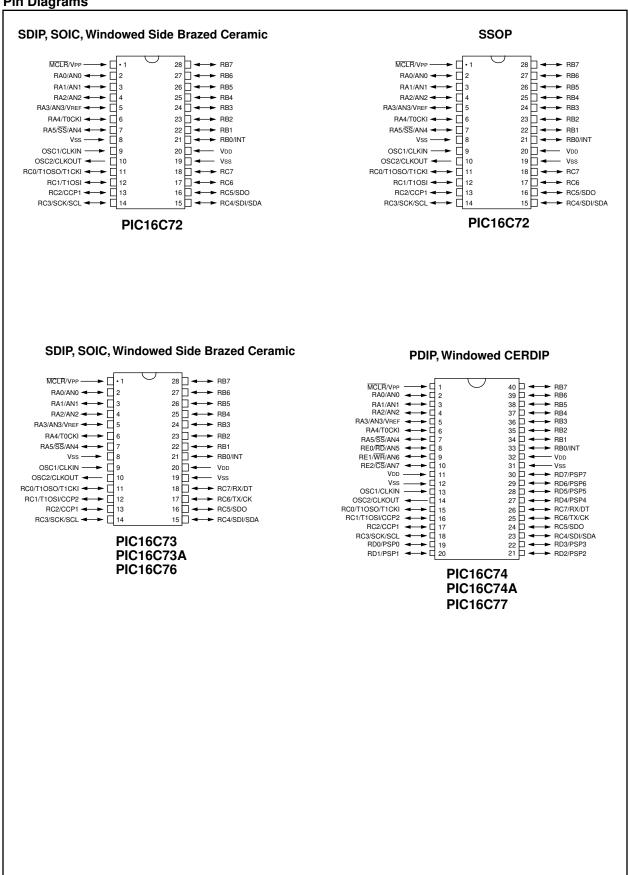

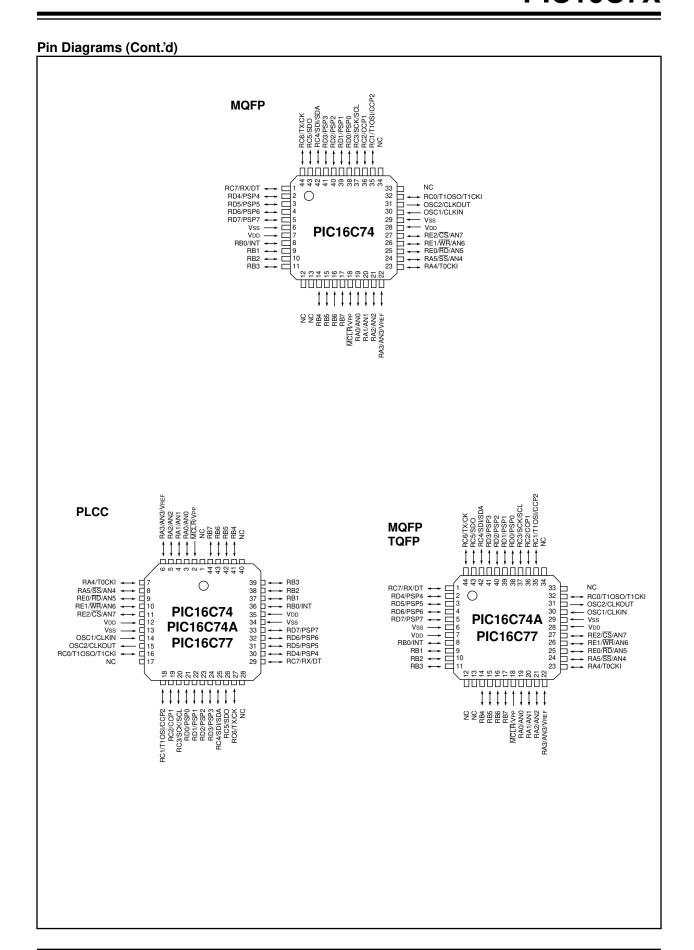

### **Pin Diagrams**

#### **Table of Contents**

| 1.0 General Description                                              | 5   |

|----------------------------------------------------------------------|-----|

| 2.0 PIC16C7X Device Varieties                                        | 7   |

| 3.0 Architectural Overview                                           | 9   |

| 4.0 Memory Organization                                              | 19  |

| 5.0 I/O Ports                                                        | 43  |

| 6.0 Overview of Timer Modules                                        | 57  |

| 7.0 Timer0 Module                                                    | 59  |

| 8.0 Timer1 Module                                                    | 65  |

| 9.0 Timer2 Module                                                    | 69  |

| 10.0 Capture/Compare/PWM Module(s)                                   | 71  |

| 11.0 Synchronous Serial Port (SSP) Module                            | 77  |

| 12.0 Universal Synchronous Asynchronous Receiver Transmitter (USART) | 99  |

| 13.0 Analog-to-Digital Converter (A/D) Module                        | 117 |

| 14.0 Special Features of the CPU                                     | 129 |

| 15.0 Instruction Set Summary                                         | 147 |

| 16.0 Development Support                                             |     |

| 17.0 Electrical Characteristics for PIC16C72                         | 167 |

| 18.0 Electrical Characteristics for PIC16C73/74                      |     |

| 19.0 Electrical Characteristics for PIC16C73A/74A                    | _   |

| 20.0 Electrical Characteristics for PIC16C76/77                      | 219 |

| 21.0 DC and AC Characteristics Graphs and Tables                     | 241 |

| 22.0 Packaging Information                                           | 251 |

| Appendix A:                                                          | 263 |

| Appendix B: Compatibility                                            | 263 |

| Appendix C: What's New                                               |     |

| Appendix D: What's Changed                                           |     |

| Appendix E: PIC16/17 Microcontrollers                                |     |

| Pin Compatibility                                                    | 271 |

| Index                                                                | 273 |

| List of Examples                                                     | 279 |

| List of Figures                                                      | 280 |

| List of Tables                                                       | 283 |

| Reader Response                                                      | 286 |

| PIC16C7X Product Identification System                               | 287 |

For register and module descriptions in this data sheet, device legends show which devices apply to those sections. As an example, the legend below would mean that the following section applies only to the PIC16C72, PIC16C73A and PIC16C74A devices.

Applicable Devices

72 73 73A 74 74A 76 77

### To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent an exceptional amount of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

### 1.0 GENERAL DESCRIPTION

The PIC16C7X is a family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with integrated analog-to-digital (A/D) converters, in the PIC16CXX mid-range family.

All PIC16/17 microcontrollers employ an advanced RISC architecture. The PIC16CXX microcontroller family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches which require two cycles. A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The **PIC16C72** has 128 bytes of RAM and 22 I/O pins. In addition several peripheral features are available including: three timer/counters, one Capture/Compare/PWM module and one serial port. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. Also a 5-channel high-speed 8-bit A/D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

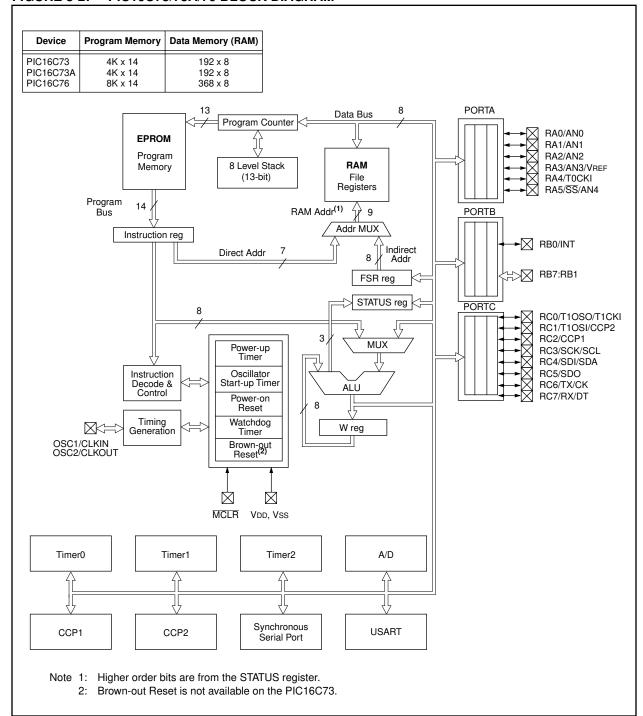

The PIC16C73/73A devices have 192 bytes of RAM, while the PIC16C76 has 368 byes of RAM. Each device has 22 I/O pins. In addition, several peripheral features are available including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. The Universal Synchronous Asynchronous Receiver Transmitter (USART) is also known as the Serial Communications Interface or SCI. Also a 5-channel high-speed 8-bit A/ D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The **PIC16C74/74A** devices have 192 bytes of RAM, while the **PIC16C77** has 368 bytes of RAM. Each device has 33 I/O pins. In addition several peripheral features are available including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. The Universal Synchronous Asynchronous Receiver Transmitter (USART) is also known as the Serial Communications Interface or SCI. An 8-bit Parallel Slave Port is provided. Also an 8-channel high-speed

8-bit A/D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The PIC16C7X family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) feature provides a power saving mode. The user can wake up the chip from SLEEP through several external and internal interrupts and resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lockup.

A UV erasable CERDIP packaged version is ideal for code development while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume.

The PIC16C7X family fits perfectly in applications ranging from security and remote sensors to appliance control and automotive. The EPROM technology makes customization of application programs (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16C7X very versatile even in areas where no microcontroller use has been considered before (e.g. timer functions, serial communication, capture and compare, PWM functions and coprocessor applications).

### 1.1 Family and Upward Compatibility

Users familiar with the PIC16C5X microcontroller family will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for the PIC16C5X can be easily ported to the PIC16CXX family of devices (Appendix B).

#### 1.2 <u>Development Support</u>

PIC16C7X devices are supported by the complete line of Microchip Development tools.

Please refer to Section 16.0 for more details about Microchip's development tools.

TABLE 1-1: PIC16C7XX FAMILY OF DEVCES

|             |                                                 | PIC16C710                           | PIC16C71            | PIC16C711                           | PIC16C715                           | PIC16C72                   | PIC16CR72 <sup>(1)</sup>   |

|-------------|-------------------------------------------------|-------------------------------------|---------------------|-------------------------------------|-------------------------------------|----------------------------|----------------------------|

| Clock       | Maximum Frequency of Operation (MHz)            | 20                                  | 20                  | 20                                  | 20                                  | 20                         | 20                         |

|             | EPROM Program Memory (x14 words)                | 512                                 | 1K                  | 1K                                  | 2K                                  | 2K                         | _                          |

| Memory      | ROM Program Memory<br>(14K words)               | _                                   | _                   | _                                   | _                                   | _                          | 2K                         |

|             | Data Memory (bytes)                             | 36                                  | 36                  | 68                                  | 128                                 | 128                        | 128                        |

|             | Timer Module(s)                                 | TMR0                                | TMR0                | TMR0                                | TMR0                                | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2     |

| Peripherals | Capture/Compare/<br>PWM Module(s)               | _                                   | _                   | _                                   | _                                   | 1                          | 1                          |

|             | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | _                                   | _                   | _                                   | _                                   | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C       |

|             | Parallel Slave Port                             | _                                   | _                   | _                                   | _                                   | _                          | _                          |

|             | A/D Converter (8-bit) Channels                  | 4                                   | 4                   | 4                                   | 4                                   | 5                          | 5                          |

|             | Interrupt Sources                               | 4                                   | 4                   | 4                                   | 4                                   | 8                          | 8                          |

|             | I/O Pins                                        | 13                                  | 13                  | 13                                  | 13                                  | 22                         | 22                         |

|             | Voltage Range (Volts)                           | 3.0-6.0                             | 3.0-6.0             | 3.0-6.0                             | 3.0-5.5                             | 2.5-6.0                    | 3.0-5.5                    |

| Features    | In-Circuit Serial Programming                   | Yes                                 | Yes                 | Yes                                 | Yes                                 | Yes                        | Yes                        |

|             | Brown-out Reset                                 | Yes                                 | _                   | Yes                                 | Yes                                 | Yes                        | Yes                        |

|             | Packages                                        | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC, SSOP |

|             |                                               | PIC16C73A                   | PIC16C74A                                 | PIC16C76                    | PIC16C77                                  |

|-------------|-----------------------------------------------|-----------------------------|-------------------------------------------|-----------------------------|-------------------------------------------|

| Clock       | Maximum Frequency of Operation (MHz)          | 20                          | 20                                        | 20                          | 20                                        |

| Memory      | EPROM Program Memory (x14 words)              | 4K                          | 4K                                        | 8K                          | 8K                                        |

|             | Data Memory (bytes)                           | 192                         | 192                                       | 368                         | 368                                       |

|             | Timer Module(s)                               | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    |

| Peripherals | Capture/Compare/PWM Mod-<br>ule(s)            | 2                           | 2                                         | 2                           | 2                                         |

|             | Serial Port(s) (SPI/I <sup>2</sup> C, US-ART) | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               |

|             | Parallel Slave Port                           | _                           | Yes                                       | _                           | Yes                                       |

|             | A/D Converter (8-bit) Channels                | 5                           | 8                                         | 5                           | 8                                         |

|             | Interrupt Sources                             | 11                          | 12                                        | 11                          | 12                                        |

|             | I/O Pins                                      | 22                          | 33                                        | 22                          | 33                                        |

|             | Voltage Range (Volts)                         | 2.5-6.0                     | 2.5-6.0                                   | 2.5-6.0                     | 2.5-6.0                                   |

| Features    | In-Circuit Serial Programming                 | Yes                         | Yes                                       | Yes                         | Yes                                       |

|             | Brown-out Reset                               | Yes                         | Yes                                       | Yes                         | Yes                                       |

|             | Packages                                      | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C7XX Family devices use serial programming with clock pin RB6 and data pin RB7.

Note 1: Please contact your local Microchip sales office for availability of these devices.

### 2.0 PIC16C7X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C7X Product Identification System section at the end of this data sheet. When placing orders, please use that page of the data sheet to specify the correct part number.

For the PIC16C7X family, there are two device "types" as indicated in the device number:

- C, as in PIC16C74. These devices have EPROM type memory and operate over the standard voltage range.

- LC, as in PIC16LC74. These devices have EPROM type memory and operate over an extended voltage range.

### 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART® Plus and PRO MATE® II programmers both support programming of the PIC16C7X.

### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

# 2.3 Quick-Turnaround-Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

### 2.4 <u>Serialized Quick-Turnaround</u> Production (SQTPSM) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random, or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password, or ID number.

**NOTES:**

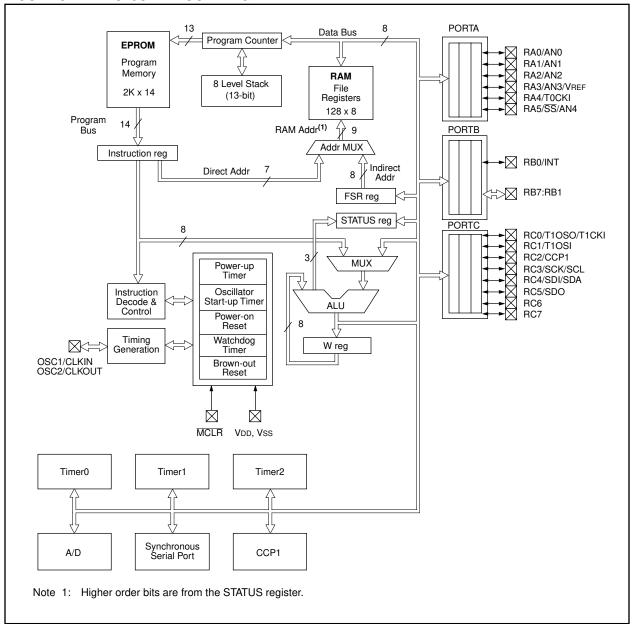

### 3.0 ARCHITECTURAL OVERVIEW

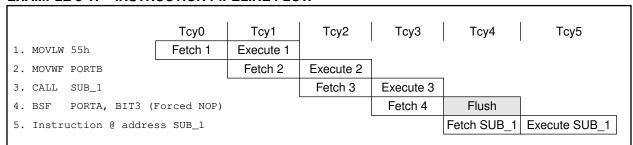

The high performance of the PIC16CXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXX uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture in which program and data are fetched from the same memory using the same bus. Separating program and data buses further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

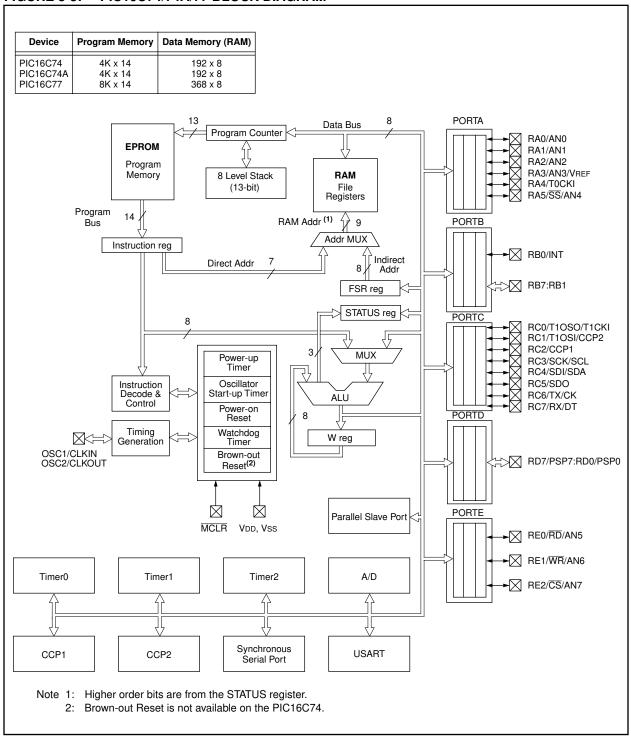

The table below lists program memory (EPROM) and data memory (RAM) for each PIC16C7X device.

| Device    | Program<br>Memory | Data Memory |

|-----------|-------------------|-------------|

| PIC16C72  | 2K x 14           | 128 x 8     |

| PIC16C73  | 4K x 14           | 192 x 8     |

| PIC16C73A | 4K x 14           | 192 x 8     |

| PIC16C74  | 4K x 14           | 192 x 8     |

| PIC16C74A | 4K x 14           | 192 x 8     |

| PIC16C76  | 8K x 14           | 368 x 8     |

| PIC16C77  | 8K x 14           | 386 x 8     |

The PIC16CXX can directly or indirectly address its register files or data memory. All special function registers, including the program counter, are mapped in the data memory. The PIC16CXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16CXX simple yet efficient. In addition, the learning curve is reduced significantly.

PIC16CXX devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between the data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow bit and a digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

FIGURE 3-1: PIC16C72 BLOCK DIAGRAM

FIGURE 3-2: PIC16C73/73A/76 BLOCK DIAGRAM

FIGURE 3-3: PIC16C74/74A/77 BLOCK DIAGRAM

**TABLE 3-1: PIC16C72 PINOUT DESCRIPTION**

| Pin Name        | DIP<br>Pin# | SSOP<br>Pin# | SOIC<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                                  |

|-----------------|-------------|--------------|--------------|---------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN      | 9           | 9            | 9            | ı             | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                        |

| OSC2/CLKOUT     | 10          | 10           | 10           | 0             | _                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/VPP        | 1           | 1            | 1            | I/P           | ST                     | Master clear (reset) input or programming voltage input. This pin is an active low reset to the device.                                                                                                      |

|                 |             |              |              |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                          |

| RA0/AN0         | 2           | 2            | 2            | I/O           | TTL                    | RA0 can also be analog input0                                                                                                                                                                                |

| RA1/AN1         | 3           | 3            | 3            | I/O           | TTL                    | RA1 can also be analog input1                                                                                                                                                                                |

| RA2/AN2         | 4           | 4            | 4            | I/O           | TTL                    | RA2 can also be analog input2                                                                                                                                                                                |

| RA3/AN3/VREF    | 5           | 5            | 5            | I/O           | TTL                    | RA3 can also be analog input3 or analog reference voltage                                                                                                                                                    |

| RA4/T0CKI       | 6           | 6            | 6            | I/O           | ST                     | RA4 can also be the clock input to the Timer0 module. Output is open drain type.                                                                                                                             |

| RA5/SS/AN4      | 7           | 7            | 7            | I/O           | TTL                    | RA5 can also be analog input4 or the slave select for the synchronous serial port.                                                                                                                           |

|                 |             |              |              |               |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                                |

| RB0/INT         | 21          | 21           | 21           | I/O           | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                                  |

| RB1             | 22          | 22           | 22           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB2             | 23          | 23           | 23           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB3             | 24          | 24           | 24           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB4             | 25          | 25           | 25           | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |

| RB5             | 26          | 26           | 26           | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |

| RB6             | 27          | 27           | 27           | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming clock.                                                                                                                                                           |

| RB7             | 28          | 28           | 28           | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming data.                                                                                                                                                            |

|                 |             |              |              |               |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                          |

| RC0/T1OSO/T1CKI | 11          | 11           | 11           | I/O           | ST                     | RC0 can also be the Timer1 oscillator output or Timer1 clock input.                                                                                                                                          |

| RC1/T1OSI       | 12          | 12           | 12           | I/O           | ST                     | RC1 can also be the Timer1 oscillator input.                                                                                                                                                                 |

| RC2/CCP1        | 13          | 13           | 13           | I/O           | ST                     | RC2 can also be the Capture1 input/Compare1 output/PWM1 output.                                                                                                                                              |

| RC3/SCK/SCL     | 14          | 14           | 14           | I/O           | ST                     | RC3 can also be the synchronous serial clock input/output for both SPI and I <sup>2</sup> C modes.                                                                                                           |

| RC4/SDI/SDA     | 15          | 15           | 15           | I/O           | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                                                                                              |

| RC5/SDO         | 16          | 16           | 16           | I/O           | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                 |

| RC6             | 17          | 17           | 17           | I/O           | ST                     | , , ,                                                                                                                                                                                                        |

| RC7             | 18          | 18           | 18           | I/O           | ST                     |                                                                                                                                                                                                              |

| Vss             | 8, 19       | 8, 19        | 8, 19        | Р             | _                      | Ground reference for logic and I/O pins.                                                                                                                                                                     |

| VDD             | 20          | 20           | 20           | Р             | _                      | Positive supply for logic and I/O pins.                                                                                                                                                                      |

| Lagandi Linniit |             | L            | _            | 1/0 :         | nnut/autaut            | D. nower                                                                                                                                                                                                     |

Legend: I = input

O = output

I/O = input/output

P = power

TTL = TTL input — = Not used ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

TABLE 3-2: PIC16C73/73A/76 PINOUT DESCRIPTION

| Pin Name        | DIP<br>Pin# | SOIC<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                                  |

|-----------------|-------------|--------------|---------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN      | 9           | 9            | I             | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                        |

| OSC2/CLKOUT     | 10          | 10           | 0             | _                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/VPP        | 1           | 1            | I/P           | ST                     | Master clear (reset) input or programming voltage input. This pin is an active low reset to the device.                                                                                                      |

|                 |             |              |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                          |

| RA0/AN0         | 2           | 2            | I/O           | TTL                    | RA0 can also be analog input0                                                                                                                                                                                |

| RA1/AN1         | 3           | 3            | I/O           | TTL                    | RA1 can also be analog input1                                                                                                                                                                                |

| RA2/AN2         | 4           | 4            | I/O           | TTL                    | RA2 can also be analog input2                                                                                                                                                                                |

| RA3/AN3/VREF    | 5           | 5            | I/O           | TTL                    | RA3 can also be analog input3 or analog reference voltage                                                                                                                                                    |

| RA4/T0CKI       | 6           | 6            | I/O           | ST                     | RA4 can also be the clock input to the Timer0 module.                                                                                                                                                        |

|                 |             |              |               |                        | Output is open drain type.                                                                                                                                                                                   |

| RA5/SS/AN4      | 7           | 7            | I/O           | TTL                    | RA5 can also be analog input4 or the slave select for the synchronous serial port.                                                                                                                           |

|                 |             |              |               |                        | PORTB is a bi-directional I/O port. PORTB can be software                                                                                                                                                    |

|                 |             |              |               |                        | programmed for internal weak pull-up on all inputs.                                                                                                                                                          |

| RB0/INT         | 21          | 21           | I/O           | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                                  |

| RB1             | 22          | 22           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB2             | 23          | 23           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB3             | 24          | 24           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB4             | 25          | 25           | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |

| RB5             | 26          | 26           | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |

| RB6             | 27          | 27           | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming clock.                                                                                                                                                           |

| RB7             | 28          | 28           | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming data.                                                                                                                                                            |

|                 |             |              |               |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                          |

| RC0/T1OSO/T1CKI | 11          | 11           | I/O           | ST                     | RC0 can also be the Timer1 oscillator output or Timer1 clock input.                                                                                                                                          |

| RC1/T1OSI/CCP2  | 12          | 12           | I/O           | ST                     | RC1 can also be the Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output.                                                                                                                   |

| RC2/CCP1        | 13          | 13           | I/O           | ST                     | RC2 can also be the Capture1 input/Compare1 output/PWM1 output.                                                                                                                                              |

| RC3/SCK/SCL     | 14          | 14           | I/O           | ST                     | RC3 can also be the synchronous serial clock input/output for both SPI and I <sup>2</sup> C modes.                                                                                                           |

| RC4/SDI/SDA     | 15          | 15           | I/O           | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                                                                                              |

| RC5/SDO         | 16          | 16           | I/O           | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                 |

| RC6/TX/CK       | 17          | 17           | I/O           | ST                     | RC6 can also be the USART Asynchronous Transmit or Synchronous Clock.                                                                                                                                        |

| RC7/RX/DT       | 18          | 18           | I/O           | ST                     | RC7 can also be the USART Asynchronous Receive or Synchronous Data.                                                                                                                                          |

| Vss             | 8, 19       | 8, 19        | Р             | _                      | Ground reference for logic and I/O pins.                                                                                                                                                                     |

| VDD             | 20          | 20           | Р             | <u> </u>               | Positive supply for logic and I/O pins.                                                                                                                                                                      |

|                 | 0 0.14      |              | 1/0           | innut/outnut           | D nower                                                                                                                                                                                                      |

Legend: I = input O =

O = output

I/O = input/output

P = power

- = Not used TTL = TTL input ST = Schmitt Trigger input Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

**TABLE 3-3:** PIC16C74/74A/77 PINOUT DESCRIPTION

| Pin Name     | DIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                              |

|--------------|-------------|--------------|-------------|---------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN   | 13          | 14           | 30          | ı             | ST/CMOS <sup>(4)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                    |

| OSC2/CLKOUT  | 14          | 15           | 31          | 0             | _                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/VPP     | 1           | 2            | 18          | I/P           | ST                     | Master clear (reset) input or programming voltage input. This pin is an active low reset to the device.                                                                                                  |

|              |             |              |             |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                      |

| RA0/AN0      | 2           | 3            | 19          | I/O           | TTL                    | RA0 can also be analog input0                                                                                                                                                                            |

| RA1/AN1      | 3           | 4            | 20          | I/O           | TTL                    | RA1 can also be analog input1                                                                                                                                                                            |

| RA2/AN2      | 4           | 5            | 21          | I/O           | TTL                    | RA2 can also be analog input2                                                                                                                                                                            |

| RA3/AN3/VREF | 5           | 6            | 22          | I/O           | TTL                    | RA3 can also be analog input3 or analog reference voltage                                                                                                                                                |

| RA4/T0CKI    | 6           | 7            | 23          | I/O           | ST                     | RA4 can also be the clock input to the Timer0 timer/ counter. Output is open drain type.                                                                                                                 |

| RA5/SS/AN4   | 7           | 8            | 24          | I/O           | TTL                    | RA5 can also be analog input4 or the slave select for the synchronous serial port.                                                                                                                       |

|              |             |              |             |               |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                            |

| RB0/INT      | 33          | 36           | 8           | I/O           | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                              |

| RB1          | 34          | 37           | 9           | I/O           | TTL                    |                                                                                                                                                                                                          |

| RB2          | 35          | 38           | 10          | I/O           | TTL                    |                                                                                                                                                                                                          |

| RB3          | 36          | 39           | 11          | I/O           | TTL                    |                                                                                                                                                                                                          |

| RB4          | 37          | 41           | 14          | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                 |

| RB5          | 38          | 42           | 15          | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                 |

| RB6          | 39          | 43           | 16          | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming clock.                                                                                                                                                       |

| RB7          | 40          | 44           | 17          | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming data.                                                                                                                                                        |

Legend: I = input O = output

— = Not used

I/O = input/output

P = power

TTL = TTL input ST = Schmitt Trigger input

- Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

- 2: This buffer is a Schmitt Trigger input when used in serial programming mode. 3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

- 4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

TABLE 3-3: PIC16C74/74A/77 PINOUT DESCRIPTION (Cont.'d)

| Pin Name        | DIP<br>Pin# | PLCC<br>Pin#   | QFP<br>Pin#     | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                         |

|-----------------|-------------|----------------|-----------------|---------------|-----------------------|-----------------------------------------------------------------------------------------------------|

|                 |             |                |                 |               |                       | PORTC is a bi-directional I/O port.                                                                 |

| RC0/T1OSO/T1CKI | 15          | 16             | 32              | I/O           | ST                    | RC0 can also be the Timer1 oscillator output or a Timer1 clock input.                               |

| RC1/T1OSI/CCP2  | 16          | 18             | 35              | I/O           | ST                    | RC1 can also be the Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output.          |

| RC2/CCP1        | 17          | 19             | 36              | I/O           | ST                    | RC2 can also be the Capture1 input/Compare1 output/PWM1 output.                                     |

| RC3/SCK/SCL     | 18          | 20             | 37              | I/O           | ST                    | RC3 can also be the synchronous serial clock input/output for both SPI and I <sup>2</sup> C modes.  |

| RC4/SDI/SDA     | 23          | 25             | 42              | I/O           | ST                    | RC4 can also be the SPI Data In (SPI mode) or data I/O ( $I^2$ C mode).                             |

| RC5/SDO         | 24          | 26             | 43              | I/O           | ST                    | RC5 can also be the SPI Data Out (SPI mode).                                                        |

| RC6/TX/CK       | 25          | 27             | 44              | I/O           | ST                    | RC6 can also be the USART Asynchronous Transmit or Synchronous Clock.                               |

| RC7/RX/DT       | 26          | 29             | 1               | I/O           | ST                    | RC7 can also be the USART Asynchronous Receive or Synchronous Data.                                 |

|                 |             |                |                 |               |                       | PORTD is a bi-directional I/O port or parallel slave port when interfacing to a microprocessor bus. |

| RD0/PSP0        | 19          | 21             | 38              | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |

| RD1/PSP1        | 20          | 22             | 39              | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |

| RD2/PSP2        | 21          | 23             | 40              | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |

| RD3/PSP3        | 22          | 24             | 41              | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |

| RD4/PSP4        | 27          | 30             | 2               | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |

| RD5/PSP5        | 28          | 31             | 3               | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |

| RD6/PSP6        | 29          | 32             | 4               | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |

| RD7/PSP7        | 30          | 33             | 5               | I/O           | ST/TTL <sup>(3)</sup> |                                                                                                     |

|                 |             |                |                 |               |                       | PORTE is a bi-directional I/O port.                                                                 |

| RE0/RD/AN5      | 8           | 9              | 25              | I/O           | ST/TTL <sup>(3)</sup> | RE0 can also be read control for the parallel slave port, or analog input5.                         |

| RE1/WR/AN6      | 9           | 10             | 26              | I/O           | ST/TTL <sup>(3)</sup> | RE1 can also be write control for the parallel slave port, or analog input6.                        |

| RE2/CS/AN7      | 10          | 11             | 27              | I/O           | ST/TTL <sup>(3)</sup> | RE2 can also be select control for the parallel slave port, or analog input7.                       |

| Vss             | 12,31       | 13,34          | 6,29            | Р             | _                     | Ground reference for logic and I/O pins.                                                            |

| VDD             | 11,32       | 12,35          | 7,28            | Р             | _                     | Positive supply for logic and I/O pins.                                                             |

| NC              | _           | 1,17,28,<br>40 | 12,13,<br>33,34 |               | _                     | These pins are not internally connected. These pins should be left unconnected.                     |

Legend: I = input

O = output

— = Not used

I/O = input/output TTL = TTL input

= input/output P = power

ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

- 2: This buffer is a Schmitt Trigger input when used in serial programming mode.

- 3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

- 4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

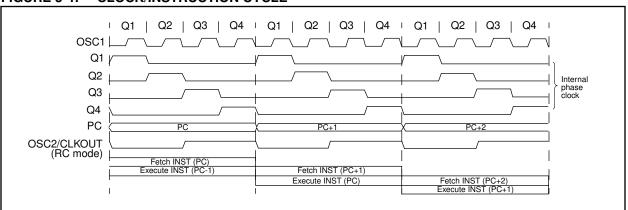

### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-4.

### 3.2 <u>Instruction Flow/Pipelining</u>

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g. GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### **EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW**

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

**NOTES:**

### 4.0 MEMORY ORGANIZATION

**Applicable Devices** 72 | 73 | 73 A | 74 | 74 A | 76 | 77

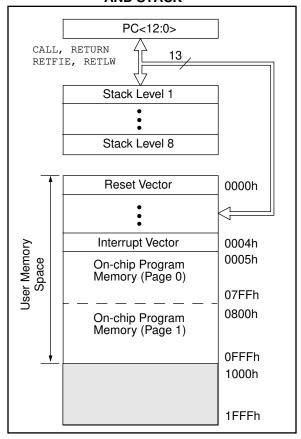

### 4.1 **Program Memory Organization**

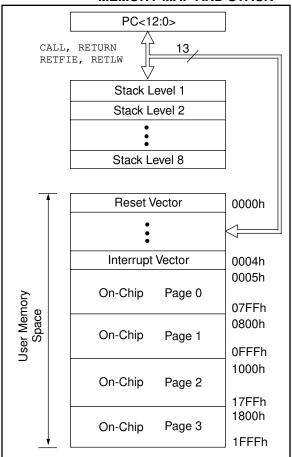

The PIC16C7X family has a 13-bit program counter capable of addressing an 8K x 14 program memory space. The amount of program memory available to each device is listed below:

| Device    | Program<br>Memory | Address Range |  |

|-----------|-------------------|---------------|--|

| PIC16C72  | 2K x 14           | 0000h-07FFh   |  |

| PIC16C73  | 4K x 14           | 0000h-0FFFh   |  |

| PIC16C73A | 4K x 14           | 0000h-0FFFh   |  |

| PIC16C74  | 4K x 14           | 0000h-0FFFh   |  |

| PIC16C74A | 4K x 14           | 0000h-0FFFh   |  |

| PIC16C76  | 8K x 14           | 0000h-1FFFh   |  |

| PIC16C77  | 8K x 14           | 0000h-1FFFh   |  |

For those devices with less than 8K program memory, accessing a location above the physically implemented address will cause a wraparound.

The reset vector is at 0000h and the interrupt vector is at 0004h.

FIGURE 4-1: PIC16C72 PROGRAM MEMORY MAP AND STACK

FIGURE 4-2: PIC16C73/73A/74/74A

PROGRAM MEMORY MAP

AND STACK

FIGURE 4-3: PIC16C76/77 PROGRAM MEMORY MAP AND STACK

### 4.2 <u>Data Memory Organization</u>

**Applicable Devices** 72 | 73 | 73 | 74 | 74 | 76 | 77 |

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

RP1:RP0 (STATUS<6:5>)

- $= 00 \rightarrow Bank0$

- =  $01 \rightarrow Bank1$

- =  $10 \rightarrow Bank2$

- =  $11 \rightarrow Bank3$

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain special function registers. Some "high use" special function registers from one bank may be mirrored in another bank for code reduction and quicker access.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR (Section 4.5).

FIGURE 4-4: PIC16C72 REGISTER FILE MAP

| F               | IVIZI                |                     |                 |  |  |  |  |  |

|-----------------|----------------------|---------------------|-----------------|--|--|--|--|--|

| File<br>Address | 3                    |                     | File<br>Address |  |  |  |  |  |

| 00h             | INDF <sup>(1)</sup>  | INDF <sup>(1)</sup> | 80h             |  |  |  |  |  |

| 01h             | TMR0                 | OPTION              | 81h             |  |  |  |  |  |

| 02h             | PCL                  | PCL                 | 82h             |  |  |  |  |  |

| 03h             | STATUS               | STATUS              | 83h             |  |  |  |  |  |

| 04h             | FSR                  | FSR                 | 84h             |  |  |  |  |  |

| 05h             | PORTA                | TRISA               | 85h             |  |  |  |  |  |

| 06h             | PORTB                | TRISB               | 86h             |  |  |  |  |  |

| 07h             | PORTC                | TRISC               | 87h             |  |  |  |  |  |

| 08h             |                      |                     | 88h             |  |  |  |  |  |

| 09h             |                      |                     | 89h             |  |  |  |  |  |

| 0Ah             | PCLATH               | PCLATH              | -<br>8Ah        |  |  |  |  |  |

| 0Bh             | INTCON               | INTCON              | -<br>8Bh        |  |  |  |  |  |

| 0Ch             | PIR1                 | PIE1                | 8Ch             |  |  |  |  |  |

| 0Dh             |                      |                     | 8Dh             |  |  |  |  |  |

| 0Eh             | TMR1L                | PCON                | 8Eh             |  |  |  |  |  |

| 0Fh             | TMR1H                |                     | 8Fh             |  |  |  |  |  |

| 10h             | T1CON                |                     | 90h             |  |  |  |  |  |

| 11h             | TMR2                 |                     | 91h             |  |  |  |  |  |

| 12h             | T2CON                | PR2                 | 92h             |  |  |  |  |  |

| 13h             | SSPBUF               | SSPADD              | 93h             |  |  |  |  |  |

| 14h             | SSPCON               | SSPSTAT             | 94h             |  |  |  |  |  |

| 15h             | CCPR1L               |                     | 95h             |  |  |  |  |  |

| 16h             | CCPR1H               |                     | 96h             |  |  |  |  |  |

| 17h             | CCP1CON              |                     | 97h             |  |  |  |  |  |

| 18h             |                      |                     | 98h             |  |  |  |  |  |

| 19h             |                      |                     | 99h             |  |  |  |  |  |

| 1Ah             |                      |                     | 9Ah             |  |  |  |  |  |

| 1Bh             |                      |                     | 9Bh             |  |  |  |  |  |

| 1Ch             |                      |                     | 9Ch             |  |  |  |  |  |

| 1Dh             |                      |                     | 9Dh             |  |  |  |  |  |

| 1Eh             | ADRES                |                     | 9Eh             |  |  |  |  |  |

| 1Fh             | ADCON0               | ADCON1              | 9Fh             |  |  |  |  |  |

| 20h             |                      |                     | A0h             |  |  |  |  |  |

|                 | General              | General             | 7.011           |  |  |  |  |  |

|                 | Purpose<br>Register  | Purpose<br>Register |                 |  |  |  |  |  |

|                 | i togisto.           | riogistoi           | BFh             |  |  |  |  |  |

|                 |                      |                     | C0h             |  |  |  |  |  |

|                 |                      |                     |                 |  |  |  |  |  |

|                 |                      |                     |                 |  |  |  |  |  |

|                 |                      |                     | _               |  |  |  |  |  |

| 7Fh             |                      |                     | FFh             |  |  |  |  |  |

| Bank 0 Bank 1   |                      |                     |                 |  |  |  |  |  |

|                 |                      |                     |                 |  |  |  |  |  |

|                 | Inimplemented data   | a memory location   | s, read as      |  |  |  |  |  |

| '0'             |                      |                     |                 |  |  |  |  |  |

| Note 1:         | Not a physical regis | sier.               |                 |  |  |  |  |  |

| 1               |                      |                     |                 |  |  |  |  |  |

FIGURE 4-5: PIC16C73/73A/74/74A REGISTER FILE MAP

| REGISTER FILE WAP                            |                      |                      |                 |  |  |  |  |  |  |

|----------------------------------------------|----------------------|----------------------|-----------------|--|--|--|--|--|--|

| File<br>Addres                               | ss                   |                      | File<br>Address |  |  |  |  |  |  |

| 00h                                          | INDF <sup>(1)</sup>  | INDF <sup>(1)</sup>  | 80h             |  |  |  |  |  |  |

| 01h                                          | TMR0                 | OPTION               | 81h             |  |  |  |  |  |  |

| 02h                                          | PCL                  | PCL                  | 82h             |  |  |  |  |  |  |

| 02h                                          | STATUS               | STATUS               | 83h             |  |  |  |  |  |  |

| 03h                                          | FSR                  | FSR                  | 84h             |  |  |  |  |  |  |

| -                                            | PORTA                | TRISA                | 85h             |  |  |  |  |  |  |

| 05h                                          |                      |                      |                 |  |  |  |  |  |  |

| 06h                                          | PORTB                | TRISB                | 86h             |  |  |  |  |  |  |

| 07h                                          | PORTC                | TRISC                | 87h             |  |  |  |  |  |  |

| 08h                                          | PORTD <sup>(2)</sup> | TRISD <sup>(2)</sup> | 88h             |  |  |  |  |  |  |

| 09h                                          | PORTE <sup>(2)</sup> | TRISE <sup>(2)</sup> | 89h             |  |  |  |  |  |  |

| 0Ah                                          | PCLATH               | PCLATH               | 8Ah             |  |  |  |  |  |  |

| 0Bh                                          | INTCON               | INTCON               | _ 8Bh           |  |  |  |  |  |  |

| 0Ch                                          | PIR1                 | PIE1                 | 8Ch             |  |  |  |  |  |  |

| 0Dh                                          | PIR2                 | PIE2                 | 8Dh             |  |  |  |  |  |  |

| 0Eh                                          | TMR1L                | PCON                 | 8Eh             |  |  |  |  |  |  |

| 0Fh                                          | TMR1H                |                      | 8Fh             |  |  |  |  |  |  |

| 10h                                          | T1CON                |                      | 90h             |  |  |  |  |  |  |

| 11h                                          | TMR2                 |                      | 91h             |  |  |  |  |  |  |

| 12h                                          | T2CON                | PR2                  | 92h             |  |  |  |  |  |  |

| 13h                                          | SSPBUF               | SSPADD               | 93h             |  |  |  |  |  |  |

| 14h                                          | SSPCON               | SSPSTAT              | 94h             |  |  |  |  |  |  |

| 15h                                          | CCPR1L               |                      | 95h             |  |  |  |  |  |  |

| 16h                                          | CCPR1H               |                      | 96h             |  |  |  |  |  |  |

| 17h                                          | CCP1CON              |                      | 97h             |  |  |  |  |  |  |

| 18h                                          | RCSTA                | TXSTA                | 98h             |  |  |  |  |  |  |

| 19h                                          | TXREG                | SPBRG                | 99h             |  |  |  |  |  |  |

| 1Ah                                          | RCREG                | OI BITG              | 9Ah             |  |  |  |  |  |  |

| 1Bh                                          | CCPR2L               |                      | 9Bh             |  |  |  |  |  |  |

| 1Ch                                          | CCPR2H               |                      | 9Ch             |  |  |  |  |  |  |

| 1Dh                                          |                      |                      | 9Dh             |  |  |  |  |  |  |

|                                              | CCP2CON              |                      | _               |  |  |  |  |  |  |

| 1Eh                                          | ADRES                | 400014               | 9Eh             |  |  |  |  |  |  |

| 1Fh                                          | ADCON0               | ADCON1               | 9Fh             |  |  |  |  |  |  |