# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 28/40/44-Pin, Low-Power, High-Performance Microcontrollers with XLP Technology

# Description

PIC18(L)F26/45/46K40 microcontrollers feature Analog, Core Independent Peripherals and Communication Peripherals, combined with eXtreme Low-Power (XLP) technology for a wide range of general purpose and low-power applications. These 28/40/44-pin devices are equipped with a 10-bit ADC with Computation (ADCC) automating Capacitive Voltage Divider (CVD) techniques for advanced touch sensing, averaging, filtering, oversampling and performing automatic threshold comparisons. They also offer a set of Core Independent Peripherals such as Complementary Waveform Generator (CWG), Windowed Watchdog Timer (WWDT), Cyclic Redundancy Check (CRC)/ Memory Scan, Zero-Cross Detect (ZCD) and Peripheral Pin Select (PPS), providing for increased design flexibility and lower system cost.

# **Core Features**

- C Compiler Optimized RISC Architecture

- Operating Speed:

- DC 64 MHz clock input

- 62.5 ns minimum instruction cycle

- Programmable 2-Level Interrupt Priority

- 31-Level Deep Hardware Stack

- Three 8-Bit Timers (TMR2/4/6) with Hardware Limit Timer (HLT)

- Four 16-Bit Timers (TMR0/1/3/5)

- Low-Current Power-on Reset (POR)

- Power-up Timer (PWRT)

- Brown-out Reset (BOR)

- Low-Power BOR (LPBOR) Option

- Programmable Code Protection

- Windowed Watchdog Timer (WWDT):

- Timer monitoring of overflow and underflow events

- Variable prescaler selection

- Variable window size selection

- All sources configurable in hardware or software

### Memory

- Up to 64K bytes Program Flash Memory

- Up to 3728 Bytes Data SRAM Memory

- Up to 1024 Bytes Data EEPROM

- Direct, Indirect and Relative Addressing modes

### **Operating Characteristics**

- Operating Voltage Ranges:

- 1.8V to 3.6V (PIC18LF2x/4xK40)

- 2.3V to 5.5V (PIC18F2x/4xK40)

- Temperature Range:

- Industrial: -40°C to 85°C

- Extended: -40°C to 125°C

# **Power-Saving Operation Modes**

- Doze: CPU and Peripherals Running at Different Cycle Rates (typically CPU is lower)

- Idle: CPU Halted While Peripherals Operate

- Sleep: Lowest Power Consumption

- Peripheral Module Disable (PMD):

- Ability to selectively disable hardware module to minimize active power consumption of unused peripherals

### eXtreme Low-Power (XLP) Features

- Sleep mode: 50 nA @ 1.8V, typical

- Windowed Watchdog Timer: 500 nA @ 1.8V, typical

- Secondary Oscillator: 500 nA @ 32 kHz

- · Operating Current:

- 8 uA @ 32 kHz, 1.8V, typical

- 32 uA/MHz @ 1.8V, typical

### **Digital Peripherals**

- Complementary Waveform Generator (CWG):

- Rising and falling edge dead-band control

- Full-bridge, half-bridge, 1-channel driveMultiple signal sources

- Capture/Compare/PWM (CCP) modules:

- Two CCPs

- 16-bit resolution for Capture/Compare modes

- 10-bit resolution for PWM mode

- 10-Bit Pulse-Width Modulators (PWM):

Two 10-bit PWMs

- Serial Communications:

- Two Enhanced USART (EUSART) with Auto-Baud Detect, Auto-wake-up on Start. RS-232, RS-485, LIN compatible

- SPI

- I<sup>2</sup>C, SMBus and PMBus™ compatible

- Up to 35 I/O Pins and One Input Pin:

- Individually programmable pull-ups

- Slew rate control

- Interrupt-on-change on all pins

- Input level selection control

# **Digital Peripherals (Continued)**

- Programmable CRC with Memory Scan:

- Reliable data/program memory monitoring for Fail-Safe operation (e.g., Class B)

- Calculate CRC over any portion of Flash or EEPROM

- High-speed or background operation

- Hardware Limit Timer (TMR2/4/6+HLT):

- Hardware monitoring and Fault detection

- Peripheral Pin Select (PPS):

- Enables pin mapping of digital I/O

- Data Signal Modulator (DSM)

# **Analog Peripherals**

- 10-Bit Analog-to-Digital Converter with Computation (ADC<sup>2</sup>):

- 35 external channels

- Conversion available during Sleep

- Four internal analog channels

- Internal and external trigger options

- Automated math functions on input signals:

- averaging, filter calculations, oversampling and threshold comparison

- Hardware Capacitive Voltage Divider (CVD) Support:

- 8-bit precharge timer

- Adjustable sample and hold capacitor array

- Guard ring digital output drive

- Zero-Cross Detect (ZCD):

- Detect when AC signal on pin crosses ground

- 5-Bit Digital-to-Analog Converter (DAC):

- Output available externally

- Programmable 5-bit voltage (% of VDD)

- Internal connections to comparators, Fixed Voltage Reference and ADC

- Two Comparators (CMP):

- Four external inputs

- External output via PPS

- Fixed Voltage Reference (FVR) module:

- 1.024V, 2.048V and 4.096V output levels

### **Clocking Structure**

- High-Precision Internal Oscillator Block (HFINTOSC):

- Selectable frequency range up to 64 MHz

±1% at calibration

- 32 kHz Low-Power Internal Oscillator (LFINTOSC)

- External 32 kHz Crystal Oscillator (SOSC)

- External Oscillator Block:

- Three crystal/resonator modes

- 4x PLL with external sources

- Fail-Safe Clock Monitor:

- Allows for safe shutdown if peripheral clock stops

- Oscillator Start-up Timer (OST)

### **Programming/Debug Features**

- In-Circuit Debug Integrated On-Chip

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

- In-Circuit Debug (ICD) with Three Breakpoints via Two Pins

# PIC18(L)F26/45/46K40

### PIC18(L)F2x/4xK40 Family Types

| Device         | Data Sheet Index | Program Memory Flash<br>(bytes) | Data SRAM<br>(bytes) | Data EEPROM<br>(bytes) | I/O Pins | 16-bit Timers | Comparators | 10-bit ADC <sup>2</sup> with<br>Computation (ch) | 5-bit DAC | Zero-Cross Detect | CCP/10-bit PWM | CWG | 8-bit TMR with HLT | Windowed Watchdog<br>Timer | <b>CRC</b> with Memory Scan | EUSART | I <sup>2</sup> C/SPI | PPS | Peripheral Module Disable | Temperature Indicator | Debug <sup>(1)</sup> |

|----------------|------------------|---------------------------------|----------------------|------------------------|----------|---------------|-------------|--------------------------------------------------|-----------|-------------------|----------------|-----|--------------------|----------------------------|-----------------------------|--------|----------------------|-----|---------------------------|-----------------------|----------------------|

| PIC18(L)F24K40 | (1)              | 16k                             | 1024                 | 256                    | 25       | 4             | 2           | 24                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Y                           | 1      | 1                    | Y   | Y                         | Y                     | I                    |

| PIC18(L)F25K40 | (1)              | 32k                             | 2048                 | 256                    | 25       | 4             | 2           | 24                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Y                           | 1      | 1                    | Υ   | Y                         | Y                     | Ι                    |

| PIC18(L)F26K40 | (2)              | 64k                             | 3728                 | 1024                   | 25       | 4             | 2           | 24                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Y                           | 2      | 2                    | Υ   | Υ                         | Y                     | Ι                    |

| PIC18(L)F27K40 | (3)              | 128k                            | 3728                 | 1024                   | 25       | 4             | 2           | 24                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Y                           | 2      | 2                    | Υ   | Υ                         | Υ                     | I                    |

| PIC18(L)F45K40 | (2)              | 32k                             | 2048                 | 256                    | 36       | 4             | 2           | 35                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Y                           | 2      | 2                    | Υ   | Υ                         | Υ                     | Ι                    |

| PIC18(L)F46K40 | (2)              | 64k                             | 3728                 | 1024                   | 36       | 4             | 2           | 35                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Y                           | 2      | 2                    | Υ   | Υ                         | Υ                     | Ι                    |

| PIC18(L)F47K40 | (3)              | 128k                            | 3728                 | 1024                   | 36       | 4             | 2           | 35                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Υ                           | 2      | 2                    | Υ   | Υ                         | Υ                     | Ι                    |

**Note 1:** Debugging Methods: (I) – Integrated on Chip.

Data Sheet Index: (Unshaded devices are described in this document.)

1. DS40001843 PIC18(L)F24/25K40 Data Sheet, 28-Pin, 8-bit Flash Microcontrollers

2. DS40001816 PIC18(L)F26/45/46K40 Data Sheet, 28/40/44-Pin, 8-bit Flash Microcontrollers

3. DS40001844 PIC18(L)F27/47K40 Data Sheet, 28/40/44-Pin, 8-bit Flash Microcontrollers

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

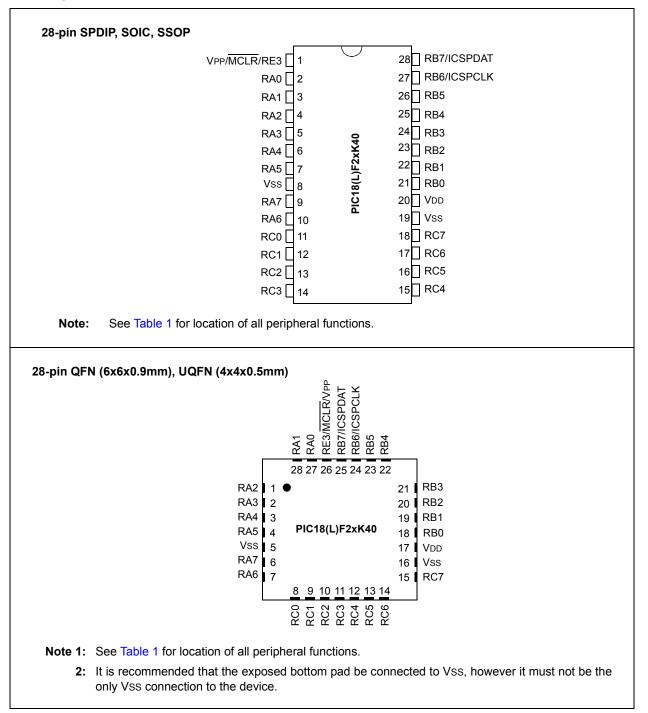

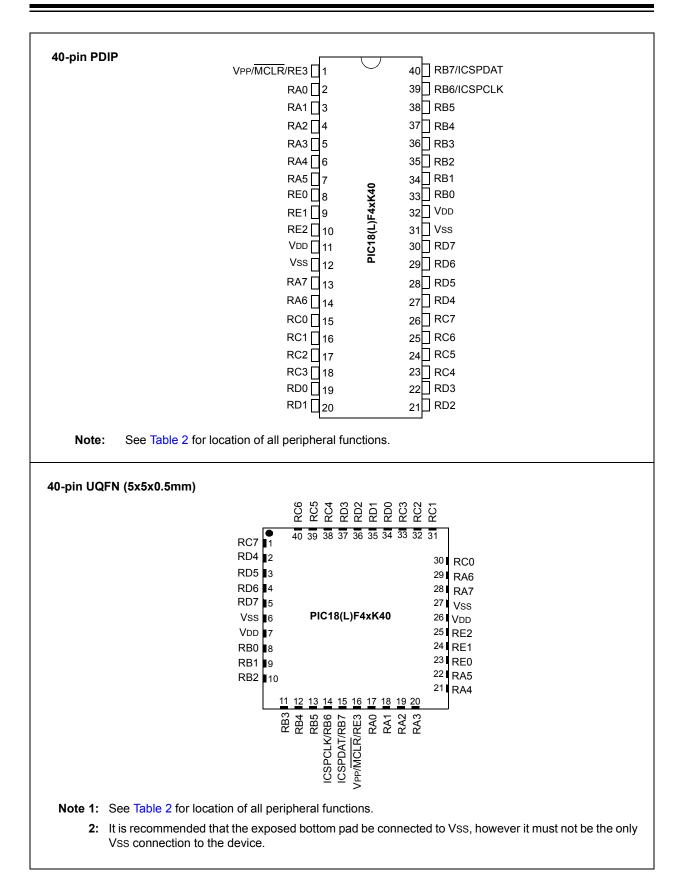

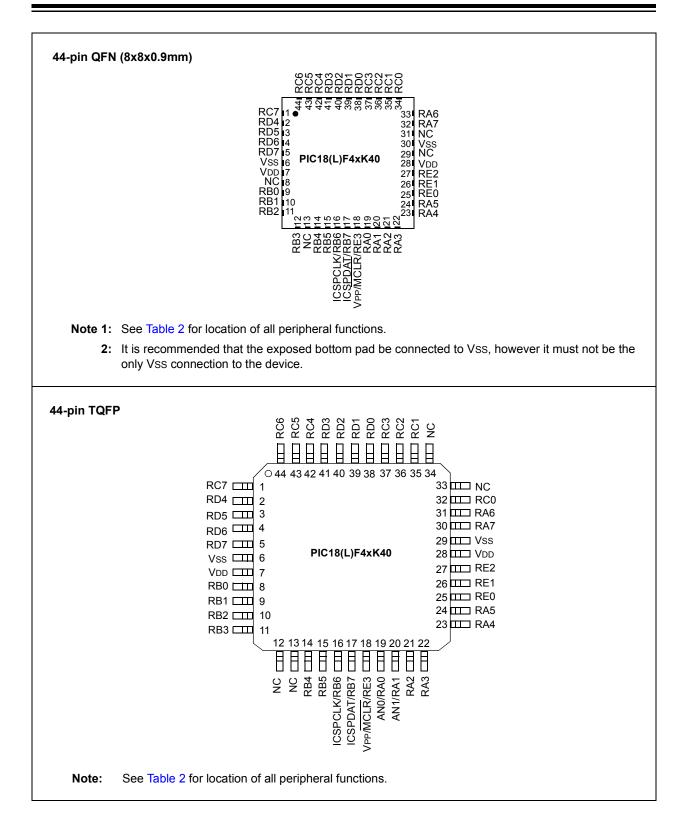

### **Pin Diagrams**

### Pin Allocation Tables

### TABLE 1: 28-PIN ALLOCATION TABLE (PIC18(L)F26K40)

| I/O <sup>(2)</sup> | 28-Pin SPDIP, SOIC, SSOP | 28-Pin (U)QFN | AD   | Reference                              | Comparator       | Timers               | ССР | CWG                 | ZCD   | Interrupt                    | EUSART                 | WSQ                   | MSSP                                         | Pull-up | Basic          |

|--------------------|--------------------------|---------------|------|----------------------------------------|------------------|----------------------|-----|---------------------|-------|------------------------------|------------------------|-----------------------|----------------------------------------------|---------|----------------|

| RA0                | 2                        | 27            | ANA0 | —                                      | C1IN0-<br>C2IN0- | —                    |     |                     |       | IOCA0                        | —                      | —                     | _                                            | Y       | —              |

| RA1                | 3                        | 28            | ANA1 | _                                      | C1IN1-<br>C2IN1- | _                    | -   | -                   | _     | IOCA1                        | —                      | _                     | _                                            | Y       | —              |

| RA2                | 4                        | 1             | ANA2 | DAC1OUT1<br>VREF- (DAC)<br>VREF- (ADC) | C1IN0+<br>C2IN0+ | _                    | -   | -                   | Ι     | IOCA2                        | _                      |                       |                                              | Y       | -              |

| RA3                | 5                        | 2             | ANA3 | Vref+ (DAC)<br>Vref+ (ADC)             | C1IN1+           | —                    |     | _                   | _     | IOCA3                        | —                      | MDCIN1 <sup>(1)</sup> | —                                            | Y       | —              |

| RA4                | 6                        | 3             | ANA4 | _                                      | _                | T0CKI <sup>(1)</sup> | _   | _                   | _     | IOCA4                        | _                      | MDCIN2 <sup>(1)</sup> | _                                            | Y       | _              |

| RA5                | 7                        | 4             | ANA5 | _                                      | _                | _                    | _   | -                   | -     | IOCA5                        | _                      | MDMIN <sup>(1)</sup>  | SS1 <sup>(1)</sup>                           | Y       | _              |

| RA6                | 10                       | 7             | ANA6 | —                                      | —                | -                    | _   | -                   | _     | IOCA6                        | —                      | —                     | _                                            | Y       | CLKOUT<br>OSC2 |

| RA7                | 9                        | 6             | ANA7 | _                                      | _                | _                    | _   |                     | _     | IOCA7                        | —                      | _                     | _                                            | Y       | OSC1<br>CLKIN  |

| RB0                | 21                       | 18            | ANB0 | —                                      | C2IN1+           | —                    | _   | CWG1 <sup>(1)</sup> | ZCDIN | IOCB0<br>INT0 <sup>(1)</sup> | —                      | —                     | SS2 <sup>(1)</sup>                           | Y       | —              |

| RB1                | 22                       | 19            | ANB1 | _                                      | C1IN3-<br>C2IN3- | —                    | _   | _                   | _     | IOCB1<br>INT1 <sup>(1)</sup> | —                      | _                     | SCK2 <sup>(1)</sup><br>SCL2 <sup>(3,4)</sup> | Y       | —              |

| RB2                | 23                       | 20            | ANB2 | —                                      | —                | —                    | _   | _                   | —     | IOCB2<br>INT2 <sup>(1)</sup> | —                      | —                     | SDI2 <sup>(1)</sup><br>SDA2 <sup>(3,4)</sup> | Y       | —              |

| RB3                | 24                       | 21            | ANB3 | —                                      | C1IN2-<br>C2IN2- | —                    | -   | -                   |       | IOCB3                        | —                      | _                     | _                                            | Y       | —              |

| RB4                | 25                       | 22            | ANB4 | _                                      | —                | T5G <sup>(1)</sup>   | _   | _                   | _     | IOCB4                        | _                      | _                     | _                                            | Y       | _              |

| RB5                | 26                       | 23            | ANB5 | _                                      | _                | T1G <sup>(1)</sup>   |     |                     | _     | IOCB5                        | —                      | _                     | _                                            | Y       | _              |

| RB6                | 27                       | 24            | ANB6 | _                                      |                  | —                    |     |                     | -     | IOCB6                        | CK2 <sup>(1)</sup>     |                       | _                                            | Y       | ICSPCLK        |

| RB7                | 28                       | 25            | ANB7 | DAC1OUT2                               | _                | T6AIN <sup>(1)</sup> |     |                     | _     | IOCB7                        | RX2/DT2 <sup>(1)</sup> | _                     | _                                            | Υ       | ICSPDAT        |

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers (Register 17-1).

2: All pin outputs default to PORT latch data. Any pin can be selected as a peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: These pins are configured for I<sup>2</sup>C logic levels; The SCLx/SDAx signals may be assigned to any of these pins. PPS assignments to the other pins (e.g., RB1) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

### TABLE 1: 28-PIN ALLOCATION TABLE (PIC18(L)F26K40) (CONTINUED)

| IADLE              | 1. 20                    |               | LOOAN            |           | 1010(L)        | 1 201140)                                                          | (00111                       | NOLD,                            |     |           |                                                                                              |     |                                              |         |                 |

|--------------------|--------------------------|---------------|------------------|-----------|----------------|--------------------------------------------------------------------|------------------------------|----------------------------------|-----|-----------|----------------------------------------------------------------------------------------------|-----|----------------------------------------------|---------|-----------------|

| I/O <sup>(2)</sup> | 28-Pin SPDIP, SOIC, SSOP | 28-Pin (U)QFN | A/D              | Reference | Comparator     | Timers                                                             | CCP                          | CWG                              | ZCD | Interrupt | EUSART                                                                                       | MSQ | MSSP                                         | Pull-up | Basic           |

| RC0                | 11                       | 8             | ANC0             | Ι         | —              | T1CKI <sup>(1)</sup><br>T3CKI <sup>(1)</sup><br>T3G <sup>(1)</sup> | _                            |                                  | -   | IOCC0     |                                                                                              | _   | —                                            | Y       | SOSCO           |

| RC1                | 12                       | 9             | ANC1             | _         | —              | —                                                                  | CCP2 <sup>(1)</sup>          | —                                | _   | IOCC1     | —                                                                                            | _   | —                                            | Y       | SOSCIN<br>SOSCI |

| RC2                | 13                       | 10            | ANC2             | _         | _              | T5CKI <sup>(1)</sup>                                               | CCP1 <sup>(1)</sup>          | _                                | _   | IOCC2     | _                                                                                            | _   | _                                            | Y       | _               |

| RC3                | 14                       | 11            | ANC3             | _         | —              | T2AIN <sup>(1)</sup>                                               | —                            | —                                | _   | IOCC3     | —                                                                                            | _   | SCK1 <sup>(1)</sup><br>SCL1 <sup>(3,4)</sup> | Y       | _               |

| RC4                | 15                       | 12            | ANC4             | _         | —              | —                                                                  | —                            | —                                | —   | IOCC4     | —                                                                                            | _   | SDI1 <sup>(1)</sup><br>SDA1 <sup>(3,4)</sup> | Y       | —               |

| RC5                | 16                       | 13            | ANC5             | _         | _              | T4AIN <sup>(1)</sup>                                               | _                            | _                                | —   | IOCC5     | —                                                                                            | _   | _                                            | Y       | _               |

| RC6                | 17                       | 14            | ANC6             | _         | _              | _                                                                  | _                            | _                                | _   | IOCC6     | CK1 <sup>(1)</sup>                                                                           | _   | _                                            | Y       | _               |

| RC7                | 18                       | 15            | ANC7             |           | _              | _                                                                  | —                            | _                                | _   | IOCC7     | RX1/DT1 <sup>(1)</sup>                                                                       | —   | —                                            | Y       | _               |

| RE3                | 1                        | 26            | _                | —         | _              | _                                                                  | _                            | _                                | —   | IOCE3     | _                                                                                            | _   | —                                            | Y       | VPP/MCLR        |

| Vss                | 19                       | 16            | —                | —         | _              | —                                                                  | —                            | —                                | —   | —         | —                                                                                            | _   | —                                            | —       | Vss             |

| VDD                | 20                       | 17            | _                | _         | —              | —                                                                  | —                            | _                                | —   | —         | —                                                                                            | —   |                                              | _       | Vdd             |

| Vss                | 8                        | 5             | —                | —         | _              | —                                                                  | —                            | —                                | —   | —         | —                                                                                            | _   | —                                            | —       | Vss             |

| OUT <sup>(2)</sup> | _                        | —             | ADGRDA<br>ADGRDB | Ι         | C1OUT<br>C2OUT | TMR0                                                               | CCP1<br>CCP2<br>PWM3<br>PWM4 | CWG1A<br>CWG1B<br>CWG1C<br>CWG1D | _   | _         | TX1/CK1 <sup>(3)</sup><br>DT1 <sup>(3)</sup><br>TX2/CK2 <sup>(3)</sup><br>DT2 <sup>(3)</sup> | DSM | SDO1<br>SCK1<br>SDO2<br>SCK2                 | _       | _               |

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers (Register 17-1).

2: All pin outputs default to PORT latch data. Any pin can be selected as a peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: These pins are configured for I<sup>2</sup>C logic levels; The SCL/SDAx signals may be assigned to any of these pins. PPS assignments to the other pins (e.g., RB1) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

| TABLE              | = 2:        | 40/         | 44-PIN /   | ALLO        | CATION | N TABLE (PI                             | C18(L)F          | -45/46K4                                                           | 40)                 |                     |       |                              |                        |                       |                                              |         |                 |

|--------------------|-------------|-------------|------------|-------------|--------|-----------------------------------------|------------------|--------------------------------------------------------------------|---------------------|---------------------|-------|------------------------------|------------------------|-----------------------|----------------------------------------------|---------|-----------------|

| I/O <sup>(2)</sup> | 40-Pin PDIP | 40-Pin UQFN | 44-Pin QFN | 44-Pin TQFP | A/D    | Reference                               | Comparator       | Timers                                                             | ССР                 | ЭМЭ                 | ZCD   | Interrupt                    | EUSART                 | MSD                   | MSSP                                         | dn-llud | Basic           |

| RA0                | 2           | 17          | 19         | 19          | ANA0   |                                         | C1INO-<br>C2IN0- | —                                                                  | —                   |                     |       | IOCA0                        | —                      | Ι                     |                                              | Y       |                 |

| RA1                | 3           | 18          | 20         | 20          | ANA1   | _                                       | C1IN1-<br>C2IN1- | —                                                                  | —                   |                     |       | IOCA1                        | —                      | Ι                     | —                                            | Y       | -               |

| RA2                | 4           | 19          | 21         | 21          | ANA2   | DAC1OUT1<br>VREF- (DAC5)<br>VREF- (ADC) | C1IN0+<br>C2IN0+ | -                                                                  | -                   | _                   | _     | IOCA2                        | _                      | _                     | _                                            | Y       | _               |

| RA3                | 5           | 20          | 22         | 22          | ANA3   | VREF+ (DAC5)<br>VREF+ (ADC)             | C1IN1+           | —                                                                  | —                   |                     |       | IOCA3                        | —                      | MDCIN1 <sup>(1)</sup> | —                                            | Y       | -               |

| RA4                | 6           | 21          | 23         | 23          | ANA4   | _                                       | _                | T0CKI <sup>(1)</sup>                                               | _                   | _                   | _     | IOCA4                        | _                      | MDCIN2 <sup>(1)</sup> | _                                            | Y       |                 |

| RA5                | 7           | 22          | 24         | 24          | ANA5   | _                                       | _                | _                                                                  | _                   | _                   | _     | IOCA5                        | _                      | MDMIN <sup>(1)</sup>  | SS1 <sup>(1)</sup>                           | Y       | _               |

| RA6                | 14          | 29          | 33         | 31          | ANA6   | _                                       | —                | —                                                                  | —                   |                     | _     | IOCA6                        | —                      | —                     | _                                            | Y       | CLKOUT<br>OSC2  |

| RA7                | 13          | 28          | 32         | 30          | ANA7   |                                         | _                |                                                                    | _                   |                     |       | IOCA7                        | _                      | _                     |                                              | Y       | OSC1<br>CLKIN   |

| RB0                | 33          | 8           | 9          | 8           | ANB0   |                                         | C2IN1+           |                                                                    | _                   | CWG1 <sup>(1)</sup> | ZCDIN | IOCB0<br>INT0 <sup>(1)</sup> | —                      | _                     | SS2 <sup>(1)</sup>                           | Y       | —               |

| RB1                | 34          | 9           | 10         | 9           | ANB1   |                                         | C1IN3-<br>C2IN3- | —                                                                  | —                   |                     | _     | IOCB1<br>INT1 <sup>(1)</sup> | _                      | _                     | SCK2 <sup>(1)</sup><br>SCL2 <sup>(3,4)</sup> | Y       | —               |

| RB2                | 35          | 10          | 11         | 10          | ANB2   | _                                       | —                | —                                                                  | —                   | _                   | _     | IOCB2<br>INT2 <sup>(1)</sup> | —                      | —                     | SDI2 <sup>(1)</sup><br>SDA2 <sup>(3,4)</sup> | Y       | —               |

| RB3                | 36          | 11          | 12         | 11          | ANB3   | _                                       | C1IN2-<br>C2IN2- | —                                                                  | —                   | _                   | —     | IOCB3                        | —                      | —                     | _                                            | Y       | —               |

| RB4                | 37          | 12          | 14         | 14          | ANB4   | _                                       | _                | T5G <sup>(1)</sup>                                                 | _                   | _                   | _     | IOCB4                        | _                      | _                     | _                                            | Y       | _               |

| RB5                | 38          | 13          | 15         | 15          | ANB5   |                                         | _                | T1G <sup>(1)</sup>                                                 | —                   |                     | _     | IOCB5                        | _                      | _                     | _                                            | Y       | _               |

| RB6                | 39          | 14          | 16         | 16          | ANB6   |                                         | _                | —                                                                  | _                   |                     | _     | IOCB6                        | CK2 <sup>(1)</sup>     | _                     | _                                            | Y       | ICSPCLK         |

| RB7                | 40          | 15          | 17         | 17          | ANB7   | DAC1OUT2                                | _                | T6AIN <sup>(1)</sup>                                               | —                   |                     | _     | IOCB7                        | RX2/DT2 <sup>(1)</sup> | _                     | -                                            | Y       | ICSPDAT         |

| RC0                | 15          | 30          | 34         | 32          | ANC0   | _                                       | —                | T1CKI <sup>(1)</sup><br>T3CKI <sup>(1)</sup><br>T3G <sup>(1)</sup> | _                   |                     | _     | IOCC0                        | —                      | _                     | _                                            | Y       | SOSCO           |

| RC1                | 16          | 31          | 35         | 35          | ANC1   | _                                       | —                | _                                                                  | CCP2 <sup>(1)</sup> | _                   | _     | IOCC1                        | _                      | —                     | _                                            | Y       | SOSCIN<br>SOSCI |

TABLE 2: 40/44-PIN ALLOCATION TABLE (PIC18(L)F45/46K40)

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers (Register 17-1).

2: All pin outputs default to PORT latch data. Any pin can be selected as a peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: These pins are configured for I2C logic levels; The SCLx/SDAx signals may be assigned to any of these pins. PPS assignments to the other pins (e.g., RB1) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I2C specific or SMBus input buffer thresholds.

| TABLE              | = 2:        | 40          | 44-PIN A         | ALLO        | CATIO          | N TABLE (PI | C10(L)                       | -45/40N4                         | +U) (CON            |     | )                                                                                                    |           |                              |     |                                              |                    |          |

|--------------------|-------------|-------------|------------------|-------------|----------------|-------------|------------------------------|----------------------------------|---------------------|-----|------------------------------------------------------------------------------------------------------|-----------|------------------------------|-----|----------------------------------------------|--------------------|----------|

| I/O <sup>(2)</sup> | 40-Pin PDIP | 40-Pin UQFN | 44-Pin QFN       | 44-Pin TQFP | A/D            | Reference   | Comparator                   | Timers                           | ссР                 | CWG | ZCD                                                                                                  | Interrupt | EUSART                       | WSQ | MSSP                                         | Pull-up            | Basic    |

| RC2                | 17          | 32          | 36               | 36          | ANC2           | _           | _                            | T5CKI <sup>(1)</sup>             | CCP1 <sup>(1)</sup> |     | _                                                                                                    | IOCC2     | _                            |     | _                                            | Y                  | _        |

| RC3                | 18          | 33          | 37               | 37          | ANC3           | —           | —                            | T2AIN <sup>(1)</sup>             | _                   | _   | —                                                                                                    | IOCC3     | —                            | —   | SCK1 <sup>(1)</sup><br>SCL1 <sup>(3,4)</sup> | Y                  | —        |

| RC4                | 23          | 38          | 42               | 42          | ANC4           | _           | —                            | —                                | —                   | —   | —                                                                                                    | IOCC4     | —                            | _   | SDI1 <sup>(1)</sup><br>SDA1 <sup>(3,4)</sup> | —                  | —        |

| RC5                | 24          | 39          | 43               | 43          | ANC5           | —           | _                            | T4AIN <sup>(1)</sup>             | _                   | _   | _                                                                                                    | IOCC5     | _                            | _   | —                                            | Y                  | _        |

| RC6                | 25          | 40          | 44               | 44          | ANC6           | _           | _                            | _                                | _                   | _   | _                                                                                                    | IOCC6     | CK1 <sup>(1)</sup>           | _   | —                                            | Y                  | _        |

| RC7                | 26          | 1           | 1                | 1           | ANC7           | —           | _                            | _                                | _                   | _   | _                                                                                                    | IOCC7     | RX1/DT1 <sup>(1)</sup>       | _   | —                                            | Y                  | _        |

| RD0                | 19          | 34          | 38               | 38          | AND0           | _           | _                            | _                                | _                   | _   | _                                                                                                    | IOCD0     | _                            | _   | —                                            | Y                  | _        |

| RD1                | 20          | 35          | 39               | 39          | AND1           | —           | _                            | _                                | _                   | _   | _                                                                                                    | IOCD1     | _                            | _   | —                                            | Y                  | _        |

| RD2                | 21          | 36          | 40               | 40          | AND2           | _           | _                            | _                                | _                   | _   | _                                                                                                    | IOCD2     | _                            | _   | —                                            | Y                  | _        |

| RD3                | 22          | 37          | 41               | 41          | AND3           | —           | _                            | _                                | _                   | _   | _                                                                                                    | IOCD3     | _                            | _   | —                                            | Y                  | _        |

| RD4                | 27          | 2           | 2                | 2           | AND4           | _           | —                            | _                                | _                   | _   | _                                                                                                    | IOCD4     | _                            | _   | —                                            | Y                  | _        |

| RD5                | 28          | 3           | 3                | 3           | AND5           | —           | _                            | _                                | _                   | _   | _                                                                                                    | IOCD5     | _                            | _   | —                                            | Y                  | _        |

| RD6                | 29          | 4           | 4                | 4           | AND6           | —           | _                            | _                                | _                   | _   | _                                                                                                    | IOCD6     | _                            | _   | —                                            | Y                  | _        |

| RD7                | 30          | 5           | 5                | 5           | AND7           | —           | —                            | —                                | -                   | I   | —                                                                                                    | IOCD7     | —                            | —   | —                                            | Y                  | —        |

| RE0                | 8           | 23          | 25               | 25          | ANE0           | _           | —                            | —                                | _                   |     | —                                                                                                    | —         | —                            | —   | —                                            | Y                  | —        |

| RE1                | 9           | 24          | 26               | 26          | ANE1           | —           | —                            | —                                |                     |     | —                                                                                                    | —         | —                            | —   | _                                            | Y                  | —        |

| RE2                | 10          | 25          | 27               | 27          | ANE2           | —           | —                            | —                                | —                   | -   | —                                                                                                    | —         | —                            | —   | —                                            | Y                  | —        |

| RE3                | 1           | 16          | 18               | 18          | —              | —           | —                            | —                                | —                   | -   | —                                                                                                    | IOCE3     | —                            | —   | —                                            | Y                  | VPP/MCLR |

| Vss                | 12          | 6           | 6                | 6           |                | _           | —                            | —                                | —                   | _   | —                                                                                                    | —         | —                            | _   | _                                            | —                  | Vss      |

| VDD                | 11          | 7           | 7                | 7           | —              | _           | —                            | —                                | _                   | _   | —                                                                                                    | —         | —                            | _   | _                                            | —                  | Vdd      |

| VDD                | 32          | 26          | 28               | 28          | —              | _           | —                            | —                                | _                   | _   | —                                                                                                    | _         | —                            | _   | _                                            | —                  | Vdd      |

| Vss                | 31          | 27          | 30               | 29          | —              | _           | —                            | —                                | _                   | _   | —                                                                                                    | —         | —                            | _   | _                                            | —                  | Vss      |

| OUT <sup>(2)</sup> | _           | _           | ADGRDA<br>ADGRDB | _           | C1OUT<br>C2OUT | TMR0        | CCP1<br>CCP2<br>PWM3<br>PWM4 | CWG1A<br>CWG1B<br>CWG1C<br>CWG1D | _                   | _   | TX1/<br>CK1 <sup>(3)</sup><br>DT1 <sup>(3)</sup><br>TX2/<br>CK2 <sup>(3)</sup><br>DT2 <sup>(3)</sup> | DSM       | SDO1<br>SCK1<br>SDO2<br>SCK2 | _   | _                                            | OUT <sup>(2)</sup> | _        |

### TABLE 2: 40/44-PIN ALLOCATION TABLE (PIC18(L)F45/46K40) (CONTINUED)

**Note** 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers (Register 17-1).

2: All pin outputs default to PORT latch data. Any pin can be selected as a peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: These pins are configured for I2C logic levels; The SCLx/SDAx signals may be assigned to any of these pins. PPS assignments to the other pins (e.g., RB1) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I2C specific or SMBus input buffer thresholds.

### **Table of Contents**

| 1.0  | Device Overview                                                           |     |

|------|---------------------------------------------------------------------------|-----|

| 2.0  | Guidelines for Getting Started with PIC18(L)F27/47K40 Microcontrollers    |     |

| 3.0  | Device Configuration                                                      |     |

| 4.0  | Oscillator Module (with Fail-Safe Clock Monitor)                          |     |

| 5.0  | Reference Clock Output Module                                             |     |

| 6.0  | Power-Saving Operation Modes                                              |     |

| 7.0  | Peripheral Module Disable (PMD)                                           |     |

| 8.0  | Resets                                                                    |     |

| 9.0  | Windowed Watchdog Timer (WWDT)                                            |     |

| 10.0 | Memory Organization                                                       |     |

| 11.0 | Nonvolatile Memory (NVM) Control                                          | 124 |

| 12.0 | 8x8 Hardware Multiplier                                                   | 148 |

| 13.0 | Cyclic Redundancy Check (CRC) Module with Memory Scanner                  | 150 |

| 14.0 | Interrupts                                                                | 167 |

| 15.0 | I/O Ports                                                                 | 197 |

| 16.0 | Interrupt-on-Change                                                       |     |

| 17.0 | Peripheral Pin Select (PPS) Module                                        | 213 |

|      | Timer0 Module                                                             |     |

|      | Timer1/3/5 Module with Gate Control                                       |     |

| 20.0 | Timer2/4/6 Module                                                         | 243 |

| 21.0 | Capture/Compare/PWM Module                                                |     |

| 22.0 | Pulse-Width Modulation (PWM)                                              |     |

| 23.0 | Zero-Cross Detection (ZCD) Module                                         | 289 |

| 24.0 | Complementary Waveform Generator (CWG) Module                             | 296 |

| 25.0 | Data Signal Modulator (DSM) Module                                        | 323 |

|      | Master Synchronous Serial Port Module                                     |     |

| 27.0 | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | 391 |

| 28.0 | Fixed Voltage Reference (FVR)                                             | 422 |

| 29.0 | Temperature Indicator Module                                              |     |

| 30.0 | 5-Bit Digital-to-Analog Converter (DAC) Module                            | 426 |

|      | Analog-to-Digital Converter with Computation (ADC2) Module                |     |

| 32.0 | Comparator Module                                                         |     |

|      | High/Low-Voltage Detect (HLVD)                                            |     |

|      | In-Circuit Serial Programming™ (ICSP™)                                    |     |

|      | Instruction Set Summary                                                   |     |

|      | Development Support                                                       |     |

|      | Electrical Specifications                                                 |     |

|      | DC and AC Characteristics Graphs and Tables                               |     |

|      | Packaging Information                                                     |     |

|      | endix A: Revision History                                                 |     |

|      | endix B: Device Differences                                               |     |

|      | Microchip Website                                                         |     |

|      | omer Change Notification Service                                          |     |

|      | omer Support                                                              |     |

| Prod | uct Identification System                                                 | 597 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

# 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

- PIC18F26K40

PIC18LF26K40

- PIC18F45K40 PIC18LF45K40

- PIC18F46K40 PIC18LF46K40

This family offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of high-endurance, Program Flash Memory. In addition to these features, the PIC18(L)F2x/4xK40 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power sensitive applications.

### 1.1 New Core Features

### 1.1.1 XLP TECHNOLOGY

All of the devices in the PIC18(L)F2x/4xK40 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the secondary oscillator or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- Multiple Idle Modes: The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further, to as little as 4% of normal operation requirements.

- On-the-fly Mode Switching: The powermanaged modes are invoked by user code during operation, allowing the user to incorporate power-saving ideas into their application's software design.

- **Peripheral Module Disable:** Modules that are not being used in the code can be selectively disabled using the PMD module. This further reduces the power consumption.

### 1.1.2 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18(L)F2x/4xK40 family offer several different oscillator options. The PIC18(L)F2x/4xK40 family can be clocked from several different sources:

- HFINTOSC

- 1-64 MHz precision digitally controlled internal oscillator

- LFINTOSC

- 31 kHz internal oscillator

- EXTOSC

- External clock (EC)

- Low-power oscillator (LP)

- Medium power oscillator (XT)

- High-power oscillator (HS)

- SOSC

- Secondary oscillator circuit operating at 31 kHz

- A Phase Lock Loop (PLL) frequency multiplier (4x) is available to the External Oscillator modes enabling clock speeds of up to 64 MHz

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the LFINTOSC. If a clock failure occurs, the controller is switched to the internal oscillator block, allowing for continued operation or a safe application shutdown.

# 1.2 Other Special Features

- **Memory Endurance:** The Flash cells for both program memory and data EEPROM are rated to last for many thousands of erase/write cycles up to 10K for program memory and 100K for EEPROM. Data retention without refresh is conservatively estimated to be greater than 40 years.

- Self-programmability: These devices can write to their own program memory spaces under internal software control. By using a boot loader routine located in the protected Boot Block at the top of program memory, it becomes possible to create an application that can update itself in the field.

- Extended Instruction Set: The PIC18(L)F2x/ 4xK40 family introduces an optional extension to the PIC18 instruction set, which adds eight new instructions and an Indexed Addressing mode. This extension, enabled as a device configuration option, has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as C.

- Enhanced Peripheral Pin Select: The Peripheral Pin Select (PPS) module connects peripheral inputs and outputs to the device I/O pins. Only digital signals are included in the selections. All analog inputs and outputs remain fixed to their assigned pins.

- Enhanced Addressable EUSART: This serial communication module is capable of standard RS-232 operation and provides support for the LIN bus protocol. Other enhancements include automatic baud rate detection and a 16-bit Baud Rate Generator for improved resolution. When the microcontroller is using the internal oscillator block, the EUSART provides stable operation for applications that talk to the outside world without using an external crystal (or its accompanying power requirement).

- **10-bit A/D Converter with Computation:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period and thus, reduce code overhead. It has a new module called ADC<sup>2</sup> with computation features, which provides a digital filter and threshold interrupt functions.

- Windowed Watchdog Timer (WWDT):

- Timer monitoring of overflow and underflow events

- Variable prescaler selection

- Variable window size selection

- All sources configurable in hardware or software

# 1.3 Details on Individual Family Members

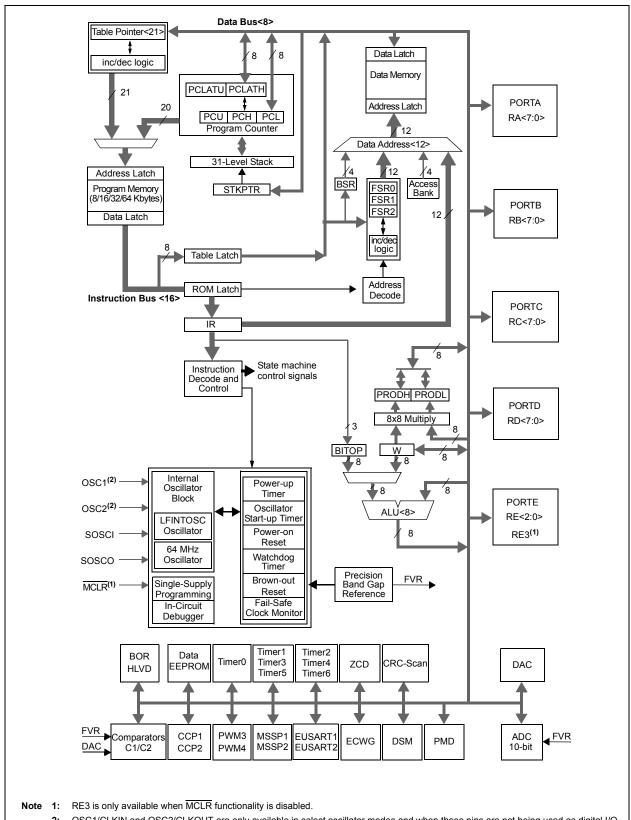

Devices in the PIC18(L)F2x/4xK40 family are available in 28-pin and 40/44-pin packages. The block diagram for this device is shown in Figure 1-1.

The devices have the following differences:

- 1. Program Flash Memory

- 2. Data Memory SRAM

- 3. Data Memory EEPROM

- 4. A/D channels

- 5. I/O ports

- 6. Enhanced USART

- 7. Input Voltage Range/Power Consumption

All other features for devices in this family are identical. These are summarized in Table 1-1.

The pinouts for all devices are listed in the pin summary tables (Table 1 and Table 2).

| Features                                                                         | PIC18(L)F26K40                                                          | PIC18(L)F45K40                                                                                     | PIC18(L)F46K40                                          |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Program Memory (Bytes)                                                           | 65536                                                                   | 32768                                                                                              | 65536                                                   |

| Program Memory (Instructions)                                                    | 32768                                                                   | 16384                                                                                              | 32768                                                   |

| Data Memory (Bytes)                                                              | 3720                                                                    | 2048                                                                                               | 3720                                                    |

| Data EEPROM Memory (Bytes)                                                       | 1024                                                                    | 256                                                                                                | 1024                                                    |

| I/O Ports                                                                        | A,B,C,E <sup>(1)</sup>                                                  | A,B,C,D,E                                                                                          | A,B,C,D,E                                               |

| Capture/Compare/PWM Modules (CCP)                                                | 2                                                                       | 2                                                                                                  | 2                                                       |

| 10-Bit Pulse-Width Modulator (PWM)                                               | 2                                                                       | 2                                                                                                  | 2                                                       |

| 10-Bit Analog-to-Digital Module (ADC <sup>2</sup> ) with Computation Accelerator | 4 internal<br>24 external                                               | 4 internal<br>35 external                                                                          | 4 internal<br>35 external                               |

| Packages                                                                         | 28-pin SPDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN<br>28-pin UQFN | 40-pin PDIP<br>40-pin UQFN<br>44-pin QFN<br>44-pin TQFP                                            | 40-pin PDIP<br>40-pin UQFN<br>44-pin QFN<br>44-pin TQFP |

| Interrupt Sources                                                                |                                                                         | 36                                                                                                 |                                                         |

| Timers (16-/8-bit)                                                               |                                                                         | 4/3                                                                                                |                                                         |

| Serial Communications                                                            |                                                                         | 2 MSSP,<br>2 EUSART                                                                                |                                                         |

| Enhanced Complementary Waveform<br>Generator (ECWG)                              |                                                                         | 1                                                                                                  |                                                         |

| Zero-Cross Detect (ZCD)                                                          |                                                                         | 1                                                                                                  |                                                         |

| Data Signal Modulator (DSM)                                                      |                                                                         | 1                                                                                                  |                                                         |

| Peripheral Pin Select (PPS)                                                      |                                                                         | Yes                                                                                                |                                                         |

| Peripheral Module Disable (PMD)                                                  |                                                                         | Yes                                                                                                |                                                         |

| 16-bit CRC with NVMSCAN                                                          |                                                                         | Yes                                                                                                |                                                         |

| Programmable High/Low-Voltage Detect (HLVD)                                      |                                                                         | Yes                                                                                                |                                                         |

| Programmable Brown-out Reset (BOR)                                               |                                                                         | Yes                                                                                                |                                                         |

| Resets (and Delays)                                                              |                                                                         | POR, BOR,<br>RESET Instruction,<br>Stack Overflow,<br>Stack Underflow<br>(PWRT, OST),<br>MCLR, WDT |                                                         |

| Instruction Set                                                                  | 83 with                                                                 | 75 Instructions;<br>Extended Instruction Se                                                        | et enabled                                              |

| Operating Frequency                                                              |                                                                         | DC – 64 MHz                                                                                        |                                                         |

# TABLE 1-1: DEVICE FEATURES

Note 1: PORTE contains the single RE3 read-only bit.

FIGURE 1-1: PIC18(L)F2X/4XK40 FAMILY BLOCK DIAGRAM

OSC1/CLKIN and OSC2/CLKOUT are only available in select oscillator modes and when these pins are not being used as digital I/O. Refer to Section 4.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional information.

# 1.4 Register and Bit naming conventions

### 1.4.1 REGISTER NAMES

When there are multiple instances of the same peripheral in a device, the peripheral control registers will be depicted as the concatenation of a peripheral identifier, peripheral instance, and control identifier. The control registers section will show just one instance of all the register names with an 'x' in the place of the peripheral instance number. This naming convention may also be applied to peripherals when there is only one instance of that peripheral in the device to maintain compatibility with other devices in the family that contain more than one.

### 1.4.2 BIT NAMES

There are two variants for bit names:

- Short name: Bit function abbreviation

- Long name: Peripheral abbreviation + short name

### 1.4.2.1 Short Bit Names

Short bit names are an abbreviation for the bit function. For example, some peripherals are enabled with the EN bit. The bit names shown in the registers are the short name variant.

Short bit names are useful when accessing bits in C programs. The general format for accessing bits by the short name is *RegisterName*bits.*ShortName*. For example, the enable bit, EN, in the COG1CON0 register can be set in C programs with the instruction COG1CON0bits.EN = 1.

Short names are generally not useful in assembly programs because the same name may be used by different peripherals in different bit positions. When this occurs, during the include file generation, all instances of that short bit name are appended with an underscore plus the name of the register in which the bit resides to avoid naming contentions.

### 1.4.2.2 Long Bit Names

Long bit names are constructed by adding a peripheral abbreviation prefix to the short name. The prefix is unique to the peripheral thereby making every long bit name unique. The long bit name for the COG1 enable bit is the COG1 prefix, G1, appended with the enable bit short name, EN, resulting in the unique bit name G1EN.

Long bit names are useful in both C and assembly programs. For example, in C the COG1CON0 enable bit can be set with the G1EN = 1 instruction. In assembly, this bit can be set with the BSF COG1CON0, G1EN instruction.

### 1.4.2.3 Bit Fields

Bit fields are two or more adjacent bits in the same register. Bit fields adhere only to the short bit naming convention. For example, the three Least Significant bits of the COG1CON0 register contain the mode control bits. The short name for this field is MD. There is no long bit name variant. Bit field access is only possible in C programs. The following example demonstrates a C program instruction for setting the COG1 to the Push-Pull mode:

COG1CONObits.MD = 0x5;

Individual bits in a bit field can also be accessed with long and short bit names. Each bit is the field name appended with the number of the bit position within the field. For example, the Most Significant mode bit has the short bit name MD2 and the long bit name is G1MD2. The following two examples demonstrate assembly program sequences for setting the COG1 to Push-Pull mode:

Example 1:

MOVLW ~(1<<G1MD1) ANDWF COG1CON0,F MOVLW 1<<G1MD2 | 1<<G1MD0 IORWF COG1CON0,F

#### Example 2:

| BSF | COG1CON0,G1MD2 |

|-----|----------------|

| BCF | COG1CON0,G1MD1 |

| BSF | COG1CON0,G1MD0 |

# 1.4.3 REGISTER AND BIT NAMING EXCEPTIONS

### 1.4.3.1 Status, Interrupt, and Mirror Bits

Status, interrupt enables, interrupt flags, and mirror bits are contained in registers that span more than one peripheral. In these cases, the bit name shown is unique so there is no prefix or short name variant.

### 1.4.3.2 Legacy Peripherals

There are some peripherals that do not strictly adhere to these naming conventions. Peripherals that have existed for many years and are present in almost every device are the exceptions. These exceptions were necessary to limit the adverse impact of the new conventions on legacy code. Peripherals that do adhere to the new convention will include a table in the registers section indicating the long name prefix for each peripheral instance. Peripherals that fall into the exception category will not have this table. These peripherals include, but are not limited to, the following:

- EUSART

- MSSP

# 2.0 GUIDELINES FOR GETTING STARTED WITH PIC18(L)F26/45/46K40 MICROCONTROLLERS

### 2.1 Basic Connection Requirements

Getting started with the PIC18(L)F26/45/46K40 family of 8-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

These pins must also be connected if they are being used in the end application:

- PGC/PGD pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.4 "ICSP<sup>™</sup> Pins")

- OSCI and OSCO pins when an external oscillator source is used (see Section 2.5 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

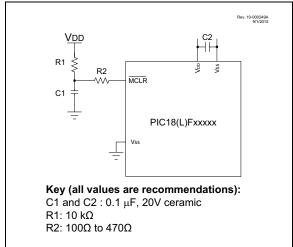

The minimum mandatory connections are shown in Figure 2-1.

### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTIONS

# 2.2 Power Supply Pins

## 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins (VDD and VSS) is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

# 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

# 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: Device Reset, and Device Programming and Debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

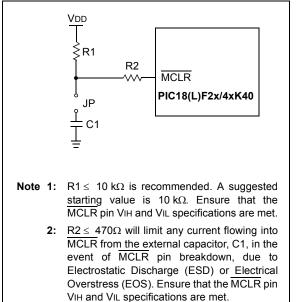

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the MCLR pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

# 2.4 ICSP™ Pins

The PGC and PGD pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .